(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ОБЪЕКТАМИ УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2011 |

|

RU2444052C1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИЗОБРАЖЕНИЯ В ЭВМ | 2000 |

|

RU2166790C1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления вводом-выводом осуществляющим связь ЭВМ с объектами управления.

Известны устройства управления блоками вычислительной системы, выполненные в виде специализированных схем связи с периферийными устройствами, включающие в себя блок связи с ЭВМ, блок ввода, блок вывода, блок задания режимов работы 1.

Недостатком этих устройств является ограниченная область применения из-за наличия аппаратных блоков ввода-вывода, которые даже при незначительной модификации периферийного устройства не могут быть использованы.

Наиболее близким по технической сущности к предлагаемому является устройство параллельного ввода-вывода, осуществляющее программный доступ к регистрам и содержащее счетчик синхроимпульсов, многофункциональные регистры ввода-вывода информации, обеспечивающие возможность смены направления передачи, передачи данных с хранением или без хранения в синхронном или асинхронном режиме и соединенные с управляемым объектом и через магистраль данных - ЭВМ, управляющие регистры, соединенные по выходам с многофукциональными регистрами, а по входам - с магистралью данных, блок управления чтением-записью, соединенный по входам с управляющими шинами ЭВМ, а по выходу с соответствующими входами с много-Oфункциональных регистров ввода-вывода и управляющих регистров 2.

Недостатком этого устройства является ограниченные функциональные возможности так как оно не позволяет подключать к ЭВМ периферийные устройства, имекяцие последовательный ввод-вывод информации.

Цель изобретения - расширение функциональных возможностей уст0ройства за счет обеспечения возможности совмещения параллельного и последовательного ввода-вывода.

Поставленная цель достигается Тем, что в устройство, содержащее

5 четыре регистра приема-передачи, первые входы-выходы которых являются первой группой входов-выходов устройства, два управляющих регистра, первые входы которых соединены 0 с магистралью данных устройства и

nepBfcviM входом буферной памяти данных, счетчик синхроимпульсов и блок связи с вычислительной машиной, группа входов-выходов которого является второй группой входов-выходов устройства, а первый выход подключен ко вторым входам управляющих регистров и буферной памяти данных, соединенной входом-выходом со вторым входом-выходом четвертого регистра приема-передачи, группа входов которого подключена к первой группе выходов второго управляющего регистра, втора группа выходов которого подключена к группе входов третьего регистра приема-передачи, первая и вторая группа выходов первого управляющего регистра соединена соответственно с группами входов первого и второго регистров приема-передачи-, вторые входы-выходы которых и второй вход-выход третьего регистра-приема-передачи подключены к магистрали данных устройства, введены блок прерываний, блок выбора адреса и блок формирования управляющих сигналов, причем первая и вторая группы входов блоков прерывания являются соответственно первой и второй группами управляющих входов устройства, а выход - выходом устройства, группа входов блока выбора адреса является группой адресных входов устройства, группа выходов подключена к третьим входам управляющих регистров и буферной памяти данных, входам первого, второго и третьего регистров приема-передачи и к первому входу четвертого регистра приема-передачи, а вход - ко вторму выходу блока связи с вычислительной машиной, группа выходов второго управляющего регистра подключена к группе входов блока формирования управляющих сигналов и к первому входу счетчика синхроимпульсов, вторым входом соединенного со входом синхроимпульсов устройства и первым входом блока формирования управляющих сигналов, первый и второй выходы которого подсоединены соответственно ко второму и третьему входам четвертого регистра приема-передачи; третий и,четвертый выходы - соответственно к четвертому входу буферной памяти данных и входу блока прерываний, а второй вход - к выходу счетчика синхроимпульсов.

При этом блок формирования управляющих сигналов содержит восемь элементов И, три элемента ИЛИ и элемент задержки, причем выход первого элемента И через элемент задержки соединен с первым входом первого элемента ИЛИ, первый вход - с первыми входами второго и третьего элементов И, второй вход с первыми входами четвертого и пятого элементов И и первым входом блока, а третий вход - с первыми входс1ми шестого и седьмого

элементов И и первым входом второго элемента ИЛИ, выход которого является вторым выходом блока, а второй вход подключен к выходу второго элемента И, вторым входом соединенного с четвертым выходом блока, вторым входом седьмого элемента и выходом пятого элемента И, второй вход которого является вторым входом блока, второй вход четвертого элемента И соединен с третьим входом седьмого элемента И, выходом подключенного к первому входу третьего элемента ИЛИ, выход которого является третьим выходом блока, второй вход соединен с выходом третьего и первым входом восьмого Элементов И, а третий вход с выходом шестого элемента И, второй вход которого подключен к выходу четвертого элемента И и второму входу первого элемента ИЛИ, третьим входом соединенного с выходом восьмого элемента И, а выходом - с первым выходом блока, вторые входы третьего, восьмого, четвертого и первый, третий входы первого элементов И являются входами из группы входов блока.

Кроме того, блок прерываний содержит два триггера, элемент ИЛИ и элемент И, причем первый вход элемента И подключен к выходу элемента ИЛИ, группа входов и вход которого являются соответственно второй группой входов и входом блока, выход первого триггера является выходом блока, а первый вход подключен к выходу элемента И, звторым входом соединенного с выходом второго триггера, первый и второй входы которого и второй вход первого триггера соединены с соответствующими входами первой группы входов блока, третьи входы триггеров соединены с земляной шиной блока.

Блок выбора адреса содержит схему сравнения и дешифратор адреса, первые входы которых соединены с группой входов блока, второй вход схемы сравнения является входом блока, а выход соединен со вторым входом дешифратора, группа выходов которого является группой выходов блока.

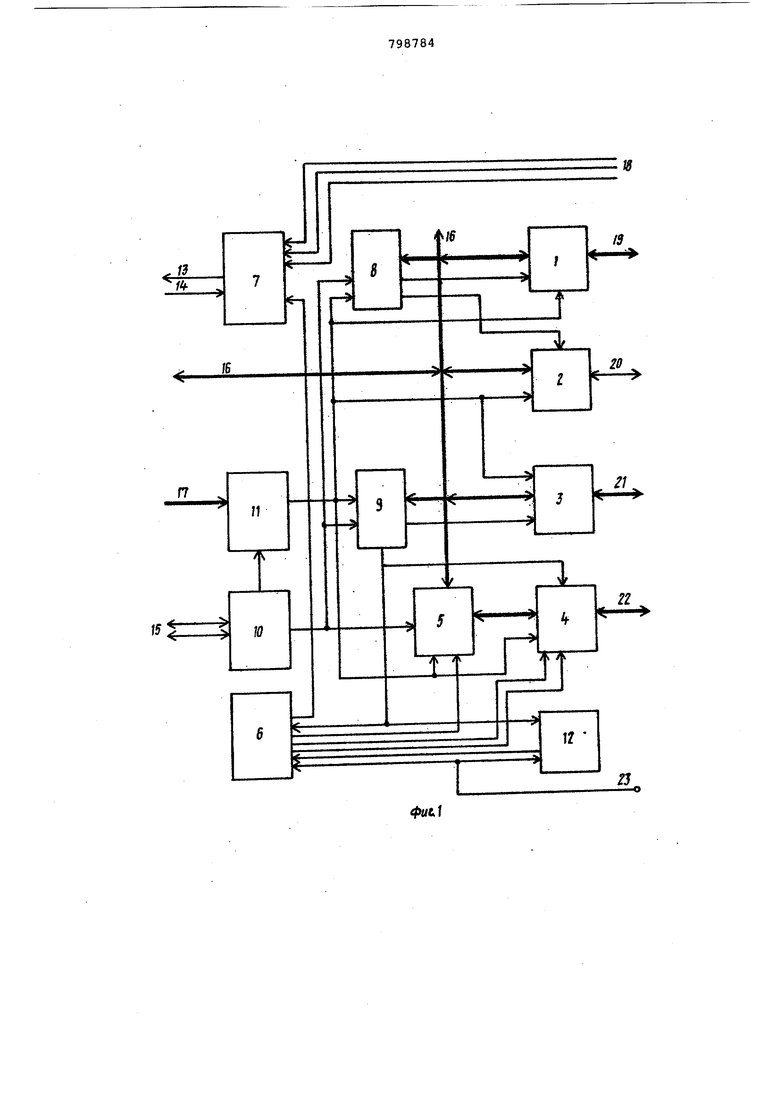

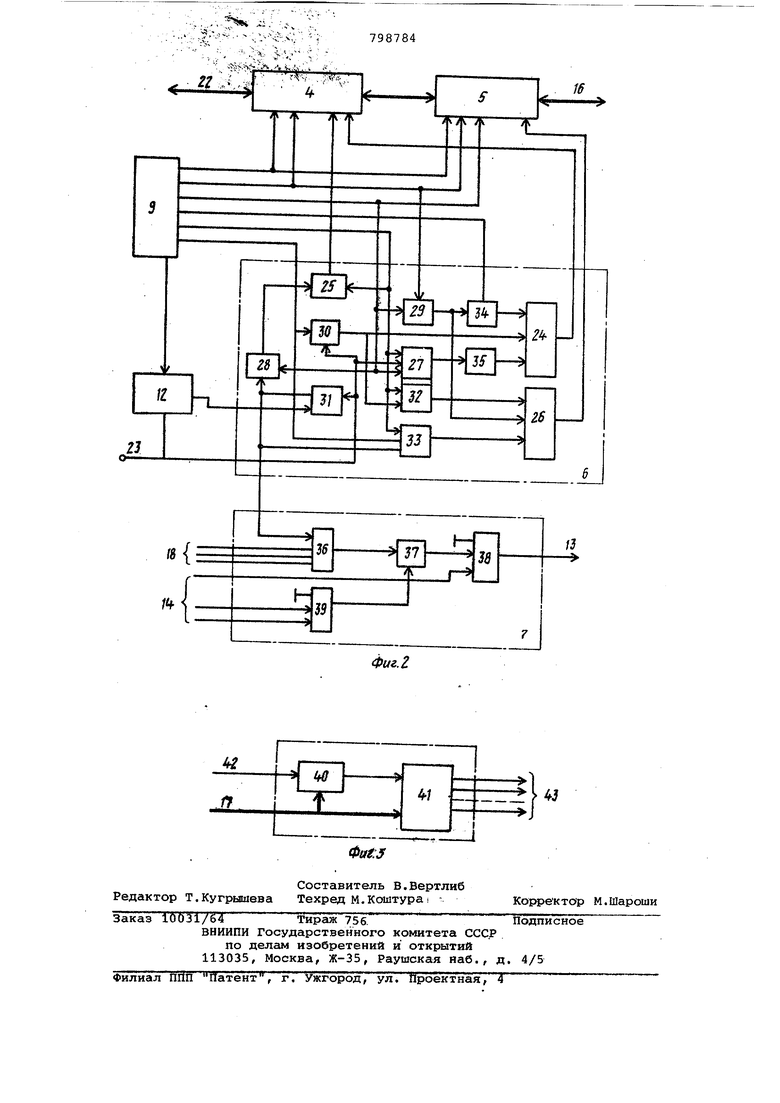

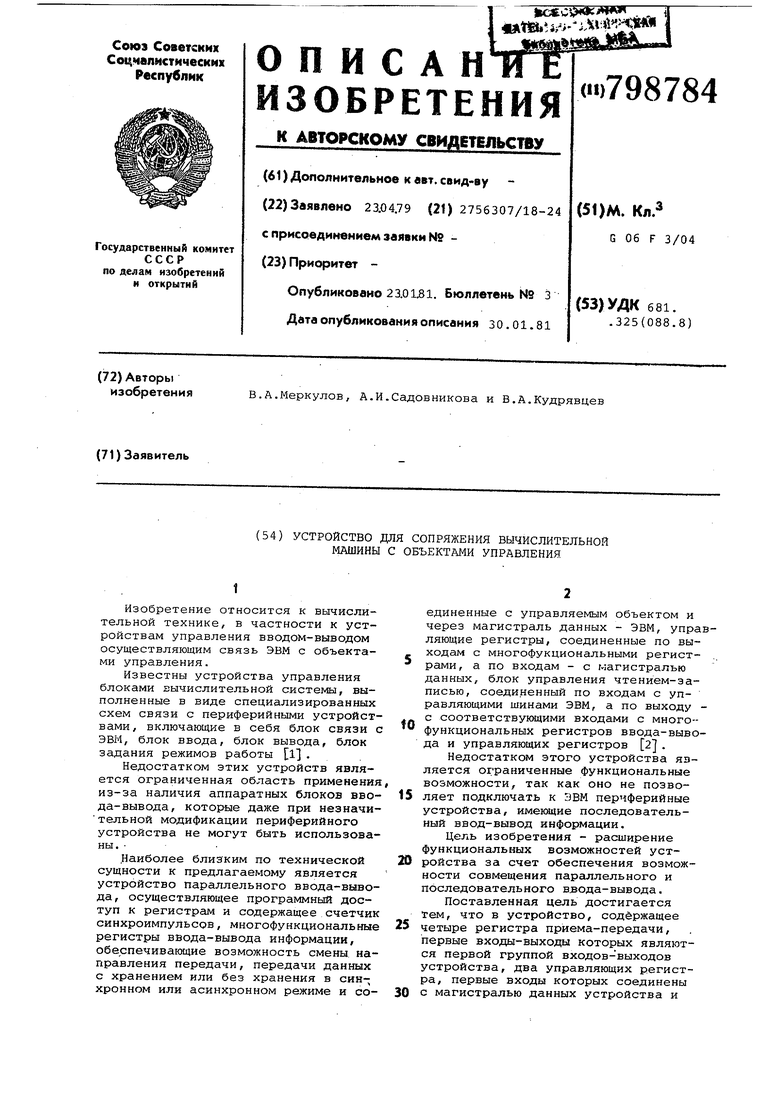

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема блоков формирования управляквдих сигналов и прерываний; на фиг. 3 - функциональная схема блока вьабора адреса.

Устройство содержит регистры 1-4 приема-передачи, буферную память 5 данных, блок б формирования управляющих сигналов, блок 7 прерываний, управляющие регистры 8 и 9, блок 10 связи с вычислительной машиной, блок 11 выбора адреса, счетчик 12 синхроимпульсов ,. выход 13 устройства, выходы 14 первой группы входов, вторап

группа входов 15 устройства, магистраль 16 данных, входы 17 адресной группы входов, входы 18 второй группы входов, входы-выходы 19-22 второй группы входов-выходов устройства, вход 23 синхроимпульсов.

.Блок б формирования управляющих сигналов (фиг. 2) содержит элементы ИЛИ 24-26 , элементы И 27-34 и элемент 35 задержики. Блок 7 прерываний включает элемент ИЛИ 36, элемент И 37 и. триггеры 38 и 39, а блок 11 выбора адреса (фиг. З) - схему 40 сравнения, дешифратор 41 адреса, вход 42 и выход 43 группы выходов блока.

Устройство работает следующим образом.

В режиме последовательного синхронного ввода данные от управляемого объекта поступают на второй вход многофункционального регистра 4, причем каждый бит информации сопровождается синхроимпульсом,-поступающим через вход 23, элементы И 37, 34, ИЛИ 24 на регистр 4. На регистре происходит преобразование последовательных данных в параллельные байты. Каждый восьмой синхроимпульс, поступающий на вход счетчика 12, устанавливает последний в нулевое состояние, причем по заднему фронту . синхроимпульса с помощью элементов И 31, 33 и через элемент ИЛИ 26 на входе буферной памяти 5 формируется положительный перепад, по которому информация в параллельном виде из регистра 4 переписывается в буфере памяти 5 и запоминается в нем. Вычислительная машина,- адресуясь к буферной памяти, производит считывание информации.

В режиме последовательного синхронного вывода при наличии положительного импульса с соответствующего выхода управляющего регистра 9, обеспечивающего подключение буферной памяти 5 к ЭВМ, выполняется запись данных из ЭВМ в буферную память синхронно с положительным фронтом сигнала, поступающего с выхода элемента ИЛИ 26 в буферную память.. На регистре 4 происходит преобразование параллельной информации в последовательную синхронно с положительньпл перепадом сигнала на выходе элемента 24, который формируется элементом И 27 и элемент 35 задержки из отрицательного перепада синхроимпульса.

Каждый восьмой синхроимпульс, устанавливающий счетчик 12 в нулевое состояние, формирует через элемент И 31 и 28 и элемент ИЛИ 25 высокий уровень сигнала на соответствующем входе регистра 4, разрешающего параллельный прием информации из буферной памяти в регистр 4 по положительнму фронту сигнала на выходе элемента ИЛИ 24.

В режиме параллельного синхронного ввода данные из управляемого объекта заносятся на регистр 4 положительному фронту на выходе элемента ИЛИ 24, сформированного через элемент И 30.

Отрицательный фронт синхроимпульса череэ элементы И 30, 32 и элемент Q ИЛИ 26 формирует на входе буферной памяти 5 положительный перепад сигнала, по крторому данные из регистра 4 заносятся в буферную память. Прием информации в ЭВМ из буферной памяти 5 осуществляется по высокому

5 уровню сигнала на выходе управляющего регистра 9, поступающего на первый вход элемента И 29.

В режиме параллельного синхронного вывода данные из ЭВМ по этому же

0 сигналу управляющего регистра 9 заносятся в буферную память, а по отрицательному фронту этого сигнала данные заносятся на регистр 4, поскольку на выходе элемента ИЛИ 24

5 элементами И 20 и 34 формируется положительный перепад сигнала управления записью.

В процессе работы блок 7 вырабсдтывает сигнал прерывания ЭВМ при поступлении сигналов на один из вхо0дов 18 от управляемых объектов или с выхода элемента И 31. Дешифратор 41 формирует управляющий сигнал разрешения работы по соответствующему коду адреса на своем входе и упра5вляющем входе с выхода схемы 40 сравнения.

- Таким образом, устройство обеспечивает обмен либо в параллельных кодах, либо в последовательных, что в

0 конечном счете позволяет сократить аппаратные затраты вычислительной системы.

Формула изобретения

Устройство для сопряжения вычислительной машины с-объектами управления, содержащее четыре регистра приема-передачи,:первые входы-выходы которых являются первой группой входов-выходов устройства, два управляющих регистра, первые входы которых соединены с магистралью данных устройства и первым входом буферной памяти данных, счетчик синхроимпульсов и блок связи с вычислительной машиной, группа входов-выходов которого является второй группой входов-выходов устройства,, а первый выход подключен ко вторым входам управляющих регистров и буферной паяти данных, соединенной.входом-выходом со вторым входом-выходом четвертого регистра приема-передачи, группа входов которого подключена к

первой группе выходов второго управляющего регистра, вторая группа выходов которого подключена к группе входов третьего регистра приема-передачи, первая и вторая группа выходов первого управляющего регистра соединена соответственно с группами входов первого и второго регистров приема-передачи, вторые вход-выходы которых и второй вход-выход третьего регистра приема-передачи, подключены к магистрали данных устройства, о т личающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения возможности обмена параллельно-последовательными кодами, в него введены блок прерывания, блок выбора адреса и блок формирования управляющих сигналов, причем первая и вторая группы входов блоков прерывания являются соответственно первой и второй группами управляющих входов устройства, а выход - выходом устроства, группа входов блока выбора адреса является группой адресных входов устройства, группа выходов подключена к третьим входам управляющих регистров и буферной памяти данных, входам первого, второго и третьего регистров приема-передачи и к первому входу четвертого регистра приема-передачи, а вход - ко второму выходу блока связи с вычислительной машиной, группа выходов второго управляющего регистра подключена к группе входов блока формирования управляющих сигналов и к первому входу счетчика синхроимпульсов вторым входом соединенного со входом синхроимпульсов устройства и первым входом блока формирования управляющих сигналов , первый и второй выходы которого подсоединены соответственно ко второму и третьему входам четвертого регистра приема-передачи, третий и четвертые .выходы - соответственно к четвертому входу буферной памяти данных и входу блока прерываний, а второй вход к выходу счетчика синхроимпульсов.

шестого и седьмого элементов И и первым входом второго элемента ИЛИ, выход которого является вторым выходом блока, а второй вход подключен к выходу второго элемента И, вторым входом соединенного с четвертым выходом блока, вторым входом седьмого элемента И и выходом пятого элемента И, второй вход которого является вторым входом блока, второй вход четвертого элемента И соединен с третьим входом седьмого элемента И, выходом подключенного к первому входу третьего элемента ИЛИ, выход которого является третьим выходом блока, второй вход соединен с выходом третьего и первым входом восьмого элементов И, а третий вход - с выходом шестого элемента И, второй вход которого подключен к выходу четвертого элемента И и второму входу первого элемента ИЛИ, третьим в.ходом соединенного с выходом восьмого элемента И, а выходом - с первым выходом блока, вторые входы третьего, восьмого четвертого и первый , третий входы первого элемента И являются входами из группы входов блока.

Источники информации, принятые во внимание при экспертизе

2,Тарроу и др. Суперкомпонент: компьютер на одной плате с программируемым интерферейсами ввода-вывода. - Электроника,1976, № 3, (прототип) .

Авторы

Даты

1981-01-23—Публикация

1979-04-23—Подача