(5) ПРЕОБРАЗОВАТЕЛЬ КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1979 |

|

SU834693A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1983 |

|

SU1161944A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для ввода информации | 1983 |

|

SU1117628A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

I

Изобретение относится к вычислительной технике и может быть использовано для контроля работы преобразователя кодов, формирующего адресночисловую или командную информацию, выдаваемую в магистраль обмена.

По основному авт.св. № известен преобразователь кодов, содержащий датчик кодов, коммутатор, per гйстры числа и адреса, усилители,, блок анализа признаков, распределитель сигналов, логические элементы И и ИЛИ, причем один из выходов датчика кодов подключен к входу коммутатора, управляемого по другим входам от блока анализа признаков, а выходы коммутатора подключены к регистрам адреса и числа, которые через соответствующие усилители подключены к выходам преобразователя кодов 1.

Преобразователь обеспечивает формирование адресно-числовой информации и выдачу ее в магистраль обмена. Однако достоверность формирования в

нем адреса недостаточна высока ввиду отсутствия средств контроля правильности работы регистра адреса в счетном режиме. В ряде ситуаций это может привести как к нарушению работы магистральной системы, так и к потере исходных данных вследствие размещения их в другой зоне адресов.

Цель изобретения - повышение на10дежности преобразования адресов массива.

Поставленная цель достигается тем, что в преобразователь кодов введены схема сравнения и пятый эле15мент И, причем первый и второй входы схемы сравнения соединены соответственно с выходами регистра числа и регистра адреса, выход схемы сравнения соединен с первым входом пятого

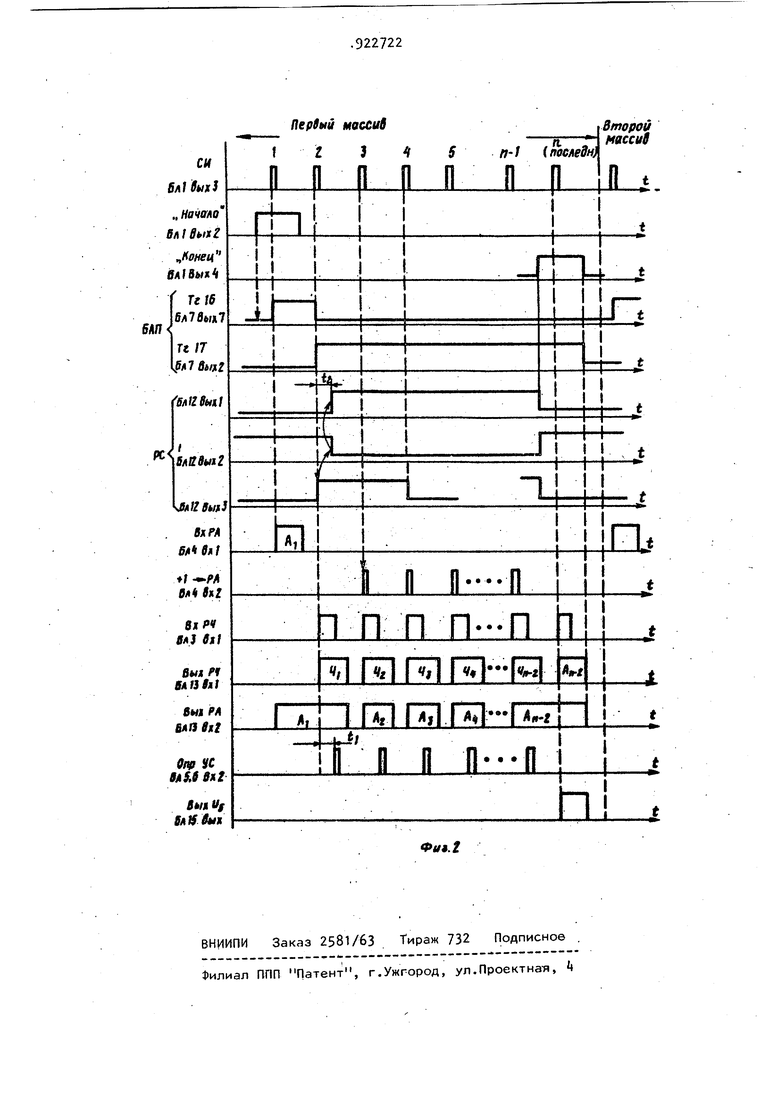

20 элемента И, выход которого соединен с входом датчика кодов, четвертый выход датчика кодов соединен с вторым входом пятого элемента И. На фиг.1 представлена блок-схема предлагаемого преобразователя; на фиг.2 - временная диаграмма его работы. Преобразователь кодов содержит да чик 1 кодов, коммутатор 2, регистр числа, регистр k адреса, усилители 5 и 6, блок 7 анализа признаков, сл жащий для управления коммутатором 2 первый элемент 8 задержки, элемент ИЛИ 9, первый и второй элементы И 1 и И 11, распределитель 12 сигналов, управляющий элементами И 10 и И 11, схему 13 сравнения, выходы преоб разователя и элемент И 15Первый выход датчика 1 кодов сое динен с первым входом коммутатора 2 выходы которого подключены через ре гистр 3 числа и регистр Ц адреса со ответственно к входам усилителей 5 и 6, выходы которых являются выходами преобразователя. Первый и второй выходы блока 7 связаны соответственно с вторыми третьим входами коммутатора 2. Второй выход датчика 1 кодов соединен с первым входом блока 7 третий выход датчика 1 связан с вторым входом блока 7 первыми входами pacпpeдeлиfеля 12 и элемента И 10,четвертый выход датчика 1 соеди нен с первым входомэлемента И 15, вторым входом распределителя 12 и третьим входом блока 7- Первый, второй и третий выходы распределителя связаны соответственно с вторым входом элемента И 10, первым и вторым входами элемента И 11. Выход элемента И 11 подключен к второму входу элемента ИЛИ 9, первый вход которого соединен с вторым входом регистра 4 и выходом элемента И 10. Выход элемента ИЛИ 9 через элемент 8 соединен с вторыми входами усилителей 5 и 6. Выходы регистров 3 и 4 соединены соответственно с первым и вторым входами схемы 13, выход которой соединен с вторым входом элемента И 15. Выход элемента И 15 соединен с входом датчика 1. Блок 7 анализа признаков содержит два триггера 16 и 17 а также элементы И 18, И 19 и НЕ 20. Выходы триггеров 16 и 17 связаны с входами коммутатора 2. Вторые входы элементов И 18 и И 19 обьединены и подключены третьему выходу датчика 1. Первый вход элемента И 18 объединен с входом элемента НЕ 20 и подключен к второму выходу датчика 1, выход эле9мента НЕ 20 соединен с первым.входом элемента И 19, выход которого подключен к второму . входу триггера 16 и первому входу триггера 17. Третий вход триггера 16 объединен с вторым входом триггера 17 и подключен к третьему входу блока 7. Выход элемента И 18 соединен с первым входом триггера 16. Распределитель 12 сигналов содержит счетчик 21, два триггера 22 и 23 и элемент 2 задержки. Первый вход счетчика 21 связан с третьим выходом датчика 1, первые входы триггеров 22 и 23 объединены с вторым входом счетчика 21 и связаны с четвертым выходом датчика 1. Выход счетчика 21 связан с вторым входом элемента И 11 и вторым входом триггера 22, выход которого через элемент 2 задержки подключен к второму входу элемента И 10 и второму входу триггера 23,ьыход которого связан с первым входом элемента И 11, Преобразователь работает следующим образом. Информация, представленная в, двоичном коде, с выхода датчика 1 поступает на вход коммутатора 2, который о сигналам из блока 7 производит ее распределение на адресную и,числовую. Каждое информационное слово, приходящее на вход коммутатора, сопровождается син7 роимп льсом, формируемым в датчике 1 кодов и снимаемым с третьего его выхода. При этом перед первым и последним передаваемыми словами датчиком 1 вырабатываются соответственно сигналы Начало и Конец (см.фиг.2). Эти сигналы соответственно снимаются с второго и четвертого выходов датчика 1 кодов. Блок 7 анализирует наличие этих сигналов на своих входах. В исходном состоянии перед началом поступления очередной части массива информации с выходов блока 7, первого и третьего выходов распределителя 12 поступают соответственно в коммутатор 2 и на элементы И 10 и 11 потенциалы, запрещающие прохождение информации через коммутатор 2 и синхроимпульсов через элементы И 10 и 11, с второго выхода распределителя 12 поступает разрешающий потенциал. При появлении на втором выходе датчика 1 сигнала Начало на втором входе элемента И.18 формируется разрешающий потенциал, на первом входе элемента И 19 - запрещающий. В результате при наличии первого синхроимпульса триггер 16 изменяет свое состояние, и на второй вход коммутатора 2 поступает разрешение напрохождение слова от датчика 1 на регистр k адреса.

Перед выдачей второго слова от датчика 1 кодов сигнал Начало на первом входе блока 7 анализа признаков снимается, соответственно этому второй- синхроимпульс проходит через элемент И 19- В результате триггеры 16 и 17 изменяют свое состояние, и на втором входе коммутатора 2 вырабатывается запрет, а на третьем входе разрешение. При этом передача слова от датчика 1 кодов происходит на регистр 3 числа. Одновременно от второго синхроимпульса на выходе счетчика 21 формируется импульс, который, благодаря наличию разрешающего потенциала на втором выходе распределителя 12 сигналов, проходит через второй элемент И 11, элемент ИЛИ 9 и первый элемент 8 задержки на вторые входы усилителей 5 и 6. В результате числовая и адресная информация с регистров 3 и t через усилители 5 и 6 поступает на выход 1 преобразователя. Импульс, сформированный на выходе счетчика 21, изменяет также состояние триггера 22, в результате чего через некоторый интервал времени, определяемый элементом задержки , до прихода очередного синхроимпульса триггер 23 изменяет свое состояние,и на входах первого 10 и второго 11 элементов .И формируются соответственно потенциалы разрешения и запрета прохождению импульсов.

При поступлении третьего и последующих слов, кроме последнего, и сопровождающих их синхроимпульсов соетояние блока 7 анализа признаков и, распределителя 12 сигналов не меняется, в результате происходит передача третьего и последующих слов, кроме последнего, от датчика 1 кодов на регистр 3 числа. Одновременно каждый синхроимпульс с третьего выхода датчика 1 кодов через первый элемент И 10 проходит на второй вход регистра k, адреса, что вызывает увеличение адреса на единицу, и через элемент ИЛИ 9 и элемент 8 задержки на вторые входы усилителей 5 и 6. В результате ПРОИСХОДИТ передача сформированного

адреса и соответствующего ему числа с регистров адреса k и числа 3 на выход устройства.

Перед поступлением последнего слова передаваемого массива на четвертом выходе датчика 1 кодов формируется сигнал Конец, который снимается после передачи этого слова.

Сигнал Конец приводит в исходное состояние распределитель 12 сигналов по переднему фронту, а по заднему фронту - блок 7 анализа признаков. Состояние блока 7 при появлении сигнала Конец не меняется в течение длительности этого сигнала (см. фиг.2) и последнее слово массива, являющееся адресом последнего числа, переданного по предыдущему синхроимпульсу, поступает на регистр 3 числа. При этом синхроимпульс, сопровождающий последнее слово, вследствие появления запрещающего потенциала на входах элементов И 10 и И 1 не проходит на второй вход регист адреса и вторые входы усилителей 5 и 6о На регистре адрес сохраняется адрес, соответствующий последнему числу, переданному по предшествующему синхроимпульсу, и значения кодов с регистров 3 и не передаются на выход устройства.

В результате, после поступления от датчика 1 кодов последнего слова массива, при условии правильности формирования адресов массива в процессе передачи предшествующих слов, на регистрах 3 и 4 должен находить.ся код адреса последнего числа массива: на регистре k- код адреса, сформированный в процессе передачи чисел, на регистре 3 числа - код адреса, полученный в последней передаче от датчика 1 кодов.

Схема 13 сравнения анализирует значения кодов на своих входах и при их совпадении передает сигнал на первый вход элемента И 15, на второй вход которого поступает сигнал Конец.

Таким образом, если к моменту времени формирования сигнала Конец коды на регистрах 3 и совпадают, то с выхода элемента И 15 на вход датчика 1 поступает разрешение на продолжение передачи информации и последующего обмена.

Использование новых элементов схемы сравнения и элемента И позво ляет повысить надежность работы преобразователя за счет введения аппаратурных средств , которые обеспечивают оперативный контроль формирова ния адресов массива в процессе передачи информации, не ухудшая быстродействие обмена. Формула изобретения Преобразователь кодов по авт.ев, № отличающийся тем, что, с целью повышения надежно ти преобразования, в него введены схема сравнения и пятый.элемент И, причем первый и второй входы схемы сравнения соединены соответственно с выходами регистра числа и регистра адреса, выход схемы сравнения соединен с первым входом пятого элемента И, выход которого соединен с входом датчика кодов, четвертый выход датчика кодов соединен с вторым входом пятого элемента И, Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР № , кл. G Об F 5/00, 1979 (прототип).

Первый массив

си

блГ Suxl

„ Начало

пКонец

is А ВыяI

Тг1б б 706 7

TtIT ffTBtijiZ

СИлК8м1

РСЛ

SAliewZ

ПВылЗ

8яРА

Г-ЯД вл 8к2

8хРЧ вл) it I

ВылП iAlSht

8м fA

илавхг

.f впг

Вш Vf

SAtSfH

Bmopou

Авторы

Даты

1982-04-23—Публикация

1980-07-01—Подача