блока формирования топологии, выход которого подключен к третьему входу второго элемента И блока моделей ветвей по числу работ и к третьему входу блока управления, третий выход которого соединен со вторым входоц тре.тьего элемента ИЛИ блока формирования топологии, четвертый выход блока управления подключен ко второму входу четвертого элемента ИЛИ блока формирования топологии, выход пятого элемента ИЛИ блока формирования топологии соединен со вторым входом четвертого элемента И блока формирования топологии, выход третьего триггера блока )модёлей ветвей по числу работ подключен к соответствующему входу первого элемента ИЛИ блока формирования топологии, выход элемента ИЛИ блока моделей ветвей по числу работ соединен с соответствую.щим входом третьего элемента И блока формирования топологии,выход первого задатчика адресов соединен с первым входом пятого элемента и блока моделей ветвей по числу работ, выход которого подключен к соответствующему входу пятого элемента ИЛИ блока формирования топологии, о т л и ч а ю |д е е с я тем, что, с целью повышения коэффициента использования оборудования модели ветви, в каждую

модель ветви введены дополнительные элементы ИЛИ, И и НЕ, выход третьего элемента НЕ подключен к первому входу дополнительного элемента И блока моделей ветвей по числу работ, выход которого соединен с первым входом третьего триггера блока моделей ветвей по числу работ, выход которого подключен ко второму входу пятого элемента И блока моделей ветвей по числу работ, выход второго элемента И блока моделей ветвей по числу работ соединен с первым входом до- . полнительного элемента ИЛИ блока моделей ветвей по числу работ, второй вход которого подключен к выходу формирователя временных интервалов блока моделей ветвей по числу работ, выход дополнительного элемента ИЛИ блока моделей ветвей по числу работ соединен со вторым входом третьего триггера блока моделей ветвей по числу рарот,йыход второго задатчика адресов блока моделей ветвей по числу работ подключен ко второму входу дополнительного элемента И блока моделей -ветвей по числу работ, выход четвертого элемента ИЛИ блока формирования топологии соединен с входом дополнительного элемента НЕ блока моделей ветвей по числу работ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетевого графика | 1985 |

|

SU1374252A1 |

| Устройство для моделирования сетевых графиков | 1985 |

|

SU1300481A2 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1128272A2 |

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1119024A1 |

| Вычислительное устройство для решения задач сетевого планирования | 1978 |

|

SU750503A1 |

| Устройство для моделирования сетевого графика | 1975 |

|

SU608169A1 |

| Устройство для моделированияСЕТЕВОгО гРАфиКА | 1980 |

|

SU849232A2 |

| Устройство для моделирования сетевых графиков | 1977 |

|

SU708367A1 |

| Устройство для моделирования сетевых графиков | 1977 |

|

SU636635A2 |

| Модель ветви сетевого графика | 1978 |

|

SU723594A1 |

УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СЕТЕВОГО ГРАФИКА, содержащее блок управления, генератор импульсов, блок формирования топологии, включающий пять элементов ИЛИ, четыре элемента И и элемент НЕ, и блок моделей ветвей по числу работ, каждая аз которых включает задатчики адресов, первый, второй и третий триггеры, элементы И, формирователь временных интервалов, эле. менты НЕ и элемент ИЛИ, причем выход первого задатчтлка адресов подключен к первому входу первого элемента И, выход которого соединен с первым входом формирователя временных интервалов, выход которого подключен ко входу первого триггера и к первому входу второго триггера, выход которого соединен с первым входом второго элемента И, выход второго з датчика адресов подключен к первЪму входу третьего эле- мента И, ко второму входу второго элемента И, к первым входам первого элемента НЕ и четвертого элемента И, выходы которых соединены соответственно с входами элемента ИЛИ, первый выход первого триггед)а подключен ко второму входу четвертого элемента И, выход второго элемента НЕ соединён со вторым входом третьего элемента И, выход которого подключен ко второму входу второго триггера, второй выход первого триггера соединен с вторым входом первого элемента И блока моделей ветвей по числу работ, в блоке формирования топологии выход первого элемента ИЛИ подключен ко лходу элемента НЕ и к первому входу первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого подключен к входам первого и второго задатчиков адресов блока моделей ветвей по числу работ, выход (О С элемента НЕ блока формирования топологии соединен с первым входом второго элемента И блока формирования топологии, выход которого подключен ко второму входу формирователя временных интервалов блока моделей зветвей по числу работ, первый выход геР нератора импульсов соединен с вторым, входом второго элемента И блока формирования топологии, второй выход генератора импульсов подключен к второму входу первого элемента И блока формирования топологии и к первому входу блока управления, первый выход которого соединен со вторым входом второго элемента ИЛИ блока формирова- ния топологии, выход третьего элемента И которого подключен к первому , входу третьего элемента ИЛИ, выход которого соединен со входом второго элемента НЕ блока моделей ветвей по числу работ, с третьим входом первого элемента И блока моделей- ветвей по числу работ и со вторым входом блока управления, второй выход которого подключен к первому входу четвертого элемента И блока формирования топологии,- выход которого соединен с первым входом четвертого элемента ИЛИ

Изобретение относится к электронному моделированию,- в частности оно может быть использовано при построении специализированных вычислительных машин. .

Известно устройство для моделирования сетевого графика, содержащее блок управления, генератор импульсов , блок формирования топологии и блок моделей ветвей по числу работ каждая из которых содержит задат чики адресов, элементы И, инвертор, элемент ИЛИ, формирователь временных интервалов/ триггеры, блок формирования топологии содержит элементы И, элементы ИЛИ, инвертор ij.

Недостатком устройства является невозможность определения конфигураций длиннейшего пути.

Наиболее близким по технической сущности к изобретению является устройс ево для моделирования сетевого графика, содержащее блок моделей ветвей, блок формирование топологии, блок управления, генератор импульсов, каждая модель ветви содержит задатчики адресой, формирователь

временных ийтервалов, триггер), элементы И, элементы НЕ, элемент ИШ1, блок формирования топологии содержит элементы И, элементы ИЛИ, элемент НЕ р..

Недостатком данного устройства является низкий коэффициент использования оборудованиямодели ветви.

обусловленный тем, что для индикации состояния принадлежности ветви сетевого графика длиннейшему пути каждая модель ветви устройства содержит отдельный триггер, который блокируется в течение процесса определения величины длиннейшего пути и дерева максимальных путей сетевого графика. Между тем, непосредственно в процессе формирования конфигурации длиннейшего пути сетевого

0 графика триггер прерывания модели ветви не выполняет каких-либо функций и его состояние не влияет на ход этого процесса, что создает возможность использования данного

5,триггера в качестве элемента яндикадии гфинадпежности ветви длиннейшему пути.

Цель изобретения - повышение коэффициента использования оборудования модели ветви. .

Указанная цель достигается тем, что в устройство для моделирования сетевого графика, содержащее блок управления, генератор импульсов, блок формирования топологии, вклю- . чающий пять элементов ИЛИ, четыре элемента И и элемент НЕ, и блок моделей ветвей по числу работ, каждая из которых включает задатчики адресов, первый, второй.и третий триггеры, элементы И, формирователь временных интервалов, элементы НЕ и элемент ИЛИ, причем вуход первого задатчика адресов подключен к первому входу первого элемента И, выход которого соединен с первьол входом формирователя временных интервалов, выход которого подключен ко входу первого триггера и к первому входу второго триггера, выход которого

соединён с первым входом второго элемента И, выход второго задатчика адресов подключен к первому входу третьего элемента И, ко второму входу второго элемента И, к первым входам первого элемента НЕ и четвертого элемента И, выходы которых соединены соответственно с входами элемента ИЛИ, первый выход первого триггера подключен ко второму входу четвертого элемента И, выход второго элемента НЕ соединен со вторым входом третьего элемента И,выход которого подключен ко второму

ВХОДУ второго триггера, второй выход первого Tij rrepa соединен с в-ворьш входом первого элемента И блока моделей ветвей по числу работ, в. блоке, формирования топологии первого элемента ИЛИ подключен,. ко входу элемента НЕ и к первому входу первого элемента И, выход которого соединен е первьм входом второго элемента ИЛИ, выход которого подключен к входам первого и второго эадатчиков адресов блока моделей ветвей по числу pa6ot, выход элемента НЕ блока формирования то пологий соединен с первым входом второго элемента И блока формирования топологии, выход которого подключен ко второму, входу формирователя временных интервалов блока моделей ветвей по числу работ, первый выход генератора импульсов срединен с вторым входом второго элемента И блока -формирования топологии , выход генератора импульсов подключен к второму входу первого элемента И блока формирова- . ния топологии и к первому входу блока управления, первый выход которого соединен со вторым входом втброго элемента ИЛИ блока формирования топологии, выход третьего элемента И которого подключен ,к первому входу третьего элемента ИЛИ, выход которого соединен со входом второго элемента НЕ блока моделей ветвей по числу работ, с третьим входом первого элемента И блока моделей ветвей по числу работ и со вторым входом блока управления, второй выход которого подключен к первому входу четвертого элемента И блока

0 формирования топологии, выход которого соединен с первым входом чет|вертого элемента ИЛИ блока формирования топологии, выход которого подключен к третьему входу второго элемента И блока моделей ветвей по

5 числу работ и -к третьему входу блока Vпpaвлeния, третий выход которого соединен со вторым входом третьего элемента ИЛИ блока формирования топологий, четвертый выход

0 блока управления подключен ко второму входу четвертого элемента ИЛИ блока формирования топологии, выход пятого элемента ИЛИ блока формирования топологии соединен со .вто5рым входом четвертого элемента И блока формирования топологии, выход третьего триггера блока моделей ветвей по числу работ подключен к соответствующему входу первого эле0мента .ИЛИ блока формирования топологии, выход элемента ИЛИ блока моделей ветвей по числу работ соединен с соответствующим входом третьего элемента И блока формирования

5 топологии, выход первого задатчика адресов соединен с первым входсм пятого элемента И блока моделей ветвей по числу работ, выход которого подключен к соответствующему входу пятого элемента ИЛИ блока форми0рования топологии, в каждую модель ветви введены дополнительные элементы ИЛИ, Ни НЕ, выход третьего элемента НЕ подключен к первому входу дополнительного элемента И блока

5 моделей ветвей по числу работ, выход которого соединен с первым входом третьего триггера блока моделей ветвей по числу работ, выход которого подключен ко второму вхо0ду пятого элемента И блока моделей ветвей по числу работ, выход второго элемента И блока моделей ветвей по числу работ соединен с первым входом дополнительного элемёнта ИЛИЦ

5 блока моделей ветвей по числу работ, второй вход которого подключен к выходу формирователя временных интервалов блока моделей ветвей ПО числу работ, выхс дополнительного элемента ИЛИ блока моделей

0 ветвей по числу работ соединен со вторым входом третьего триггера блока моделей ветвей по числу работ, выход второго задатчика адресов блока моделей ветвей по числу работ

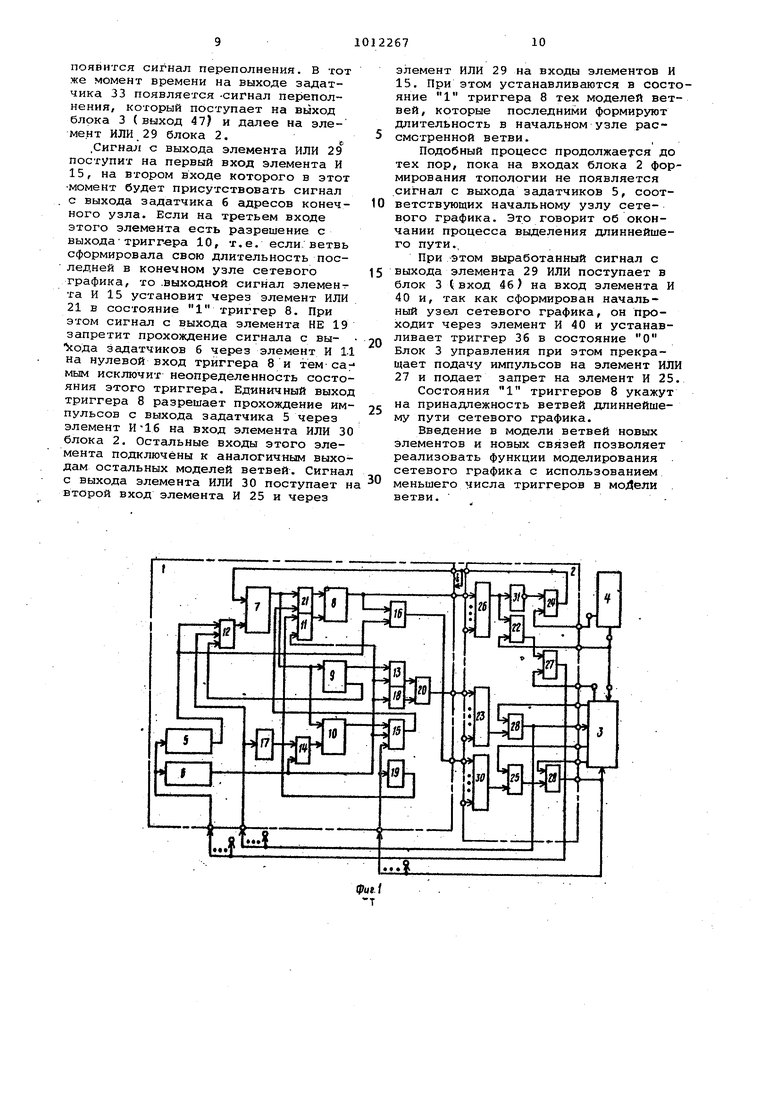

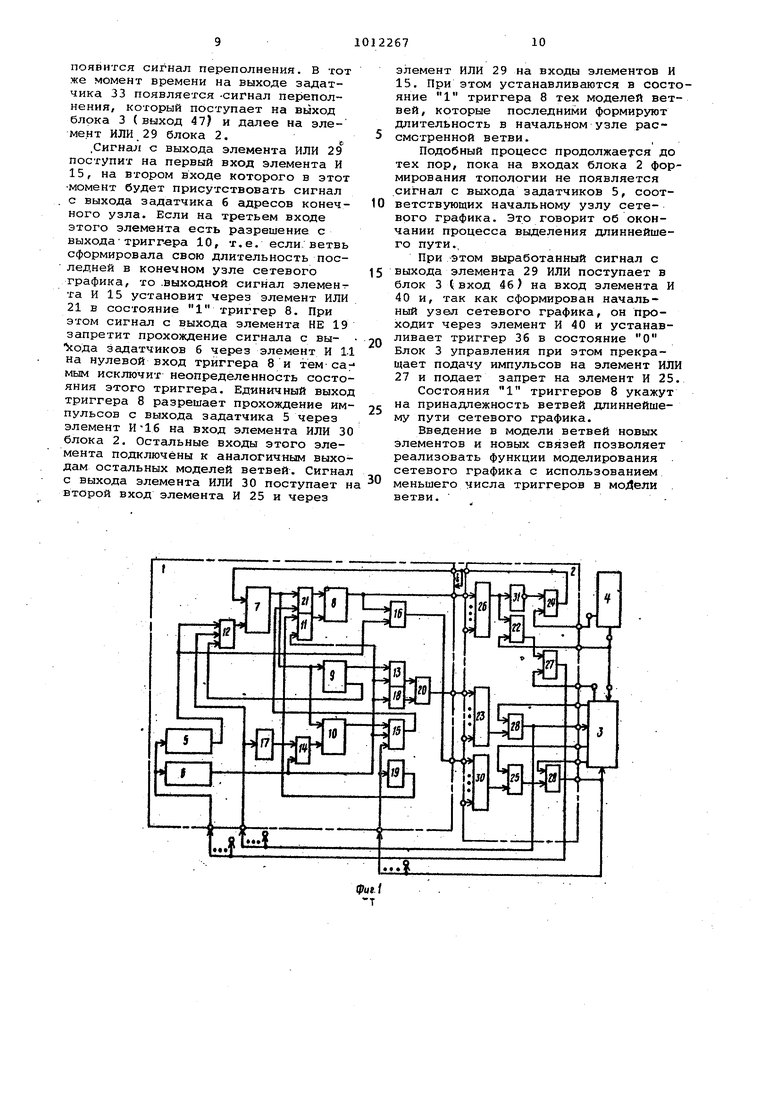

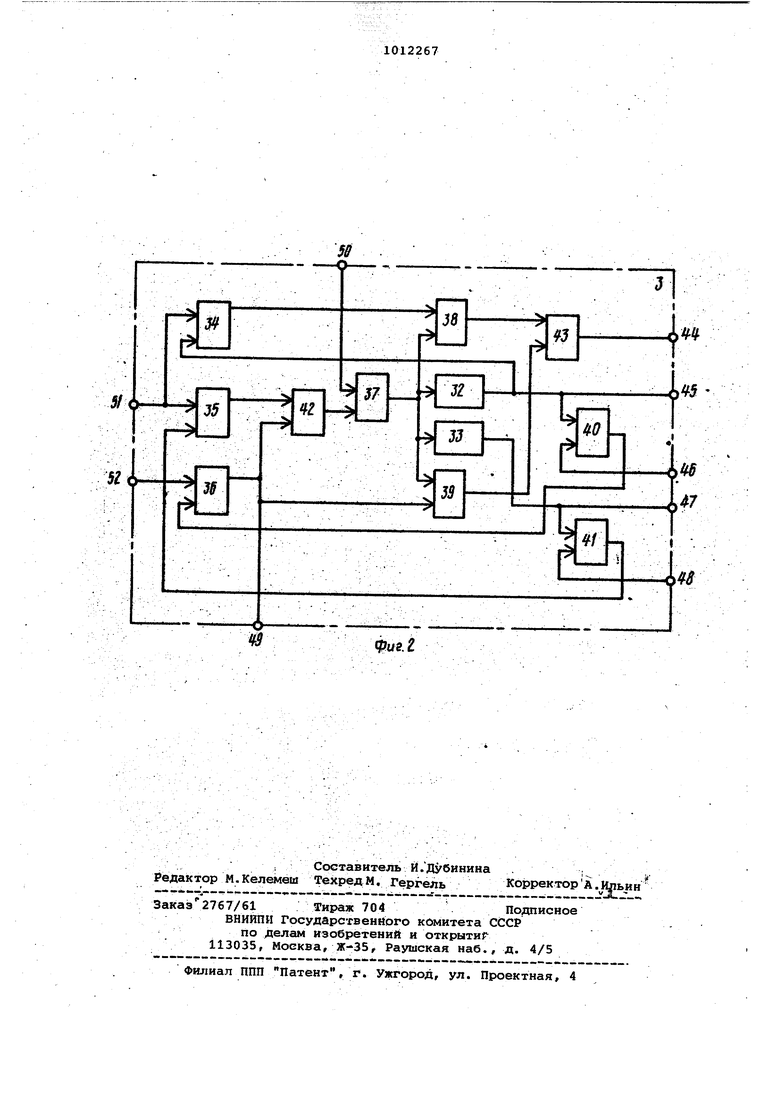

5 подключен ICO второму входу дополнительного элемента И блока моделей ветвей по числу работ, выход четвер того элемента ИЛИ блока форми ювания топологии соединен с входом дополнительного элемента НЕ блока м делей ветвей по числу работ. На фиг. 1 приведена функциональная схема предложенного устройства; на фиг. 2 - одна из схем вьшолнения блока управления. Устройство для моделирования . сетевого графика состоит из блока 1 моделей ветвей, блока 2 формировани топологии, блока 3 управления и генератора 4 импульсов. Каждая модель 1 ветви содержит з датчики 6 адресов, формирователь 7 временных .интервалов, тригге ры. 8 - 10, элементы И 11-16, элемен ты НЕ 17-19, э лементы ИЛИ 20-21. В качестве задатчиков 5 и 6 используются счетчики импульсов. Блок 2 формирования топологии со держит элементы И 22-25, элементы И 26-30, элемент НЕ 31. Блок 2, соединенный с бл9ком 1 м делей ветвей, обеспечивает взаимодействие моделей ветвей сетевого гр фика по временному принципу на осно вании адресов начального и конечног событий для каждой ветви,, занесенны в задатчики 5 и 6. Блок 3 управле ния состоит из задатчиков 32 и 33 начального И конечного узлов сетевого графика соответственно, выполненных аналогично задатчикам 5 и 6, триггеров 34-36, элементов И 37-41 и элементов ИЛИ 42 и 43, входы и вы ходы блока управления 44-51. Блок 3 управления предназначе н для осуществления первоначального запуска всего устройства и организации взаимосвязанной работы блоков устройства. Устройство работает следующим образом. Предварительно в зещатчики 5 и 6 заносятся соответственно адреса начального и конечного узлов ветвей сетевого д рафика. В формирователи 7 временных интервалов заносятся длительности ветвей, а триггеры 8, 9 и 10 устанавливаются в состояние О (соответствующие цепи не показаны) . в блоке 3 управления предварительно в задатчики 32 и 33 заносятся соответственно адреса начального и конечного узлов сетевого графика триггеры 34-36 устанавливгаются в состояния О. Для запуска всех моделей 1 ветвей на вход 51 блока 3 подается сигнал Пуск, который устанавливает в состояния 1 триггеры 34 и 35. Последний через элемент 42 ИЛИ выдает разрешение на вход элемент;а И 37 и импульсы с генератора 4 ( вход 50/ через элемент И 37 начинают поступать на входы заатчиков 32 и 33. Импульсы также с выхода элемента И 37 проходят через элемент И.38, на втором входе которого присутствует разрешение.с единичного выхода триггера 34, даее через элемент ИЛИ 43 на выход 44 блока 3 управления и поступают на вход элемента ИЛИ. 27 блока 2 формирования топологии. Импульсы с выхода элемента ИЛИ 27 п.оступают на входы задатчиков 5 и 6 всех моделей 1 ветвей до тех пор, пока на выходах задатчиков 5 адресов, в которых записан адрес начального узла сетевого графика, не появится сигнал переполнения. В этот же момент времени на выходе задатчика 32 начального узла сетевого графика в блоке 3 также появляется.сигнал переполнения, который через выход 45 блока 3 поступает йа вход элемента ИЛИ 28 блока 2. Кроме того, сигнал С- выхода задатчика 32 поступает на нулевой вход триггера 34 и устанавливает, его в состояние О в результате этого со второго входа элемента И 38 снимается разрешение, а поэтому прекращается подача импульсов с блока 3 (выход 44) на. вход элемента 27 ИЛИ блока 2. Сигнал с выхода элемента ИЛИ 28 блока 2 поступает на вход элемента И 12 моделей 1 и на вход блока 3 (вход 48. Разрешающий сигнал появляется на выходах тех элементов И 12, на остальных входах которых присутствует разрешение с нулевого выхода триггера 9 и задатчика 5. В результате формирователи 7 этих моделей подготовлены сигналами с выходов элементов И 12 : отсчету импульсов, поступающих из блока 2. Отсчитав число импульсов, пропорциональное длительности данной ветви, формирователь 7выдает сигнал, который устанавливает в состояние 1 триггеры 8-10, Сигйал с единичного выхода триггера 8поступает на вход элемента ИЛИ 26 блока 2 и через элемент НЕ 31 запрещает прохождение импульсов через элементы И 22 и ИЛИ 27 на входы задатчиков 5 и б всех моделей 1. Сигнал с выхода задатчика 6, в котором записан адрес конечного узла ветви, устанавливает в состояние О триггер 8 (через элемент И 11, на втором входе которого есть разрешение от элемента НЕ 19), а также поступает на входы элементов И 13-15 и НЕ 18. Если ветвь, в которой появляется импульс на выходе задатчика 6, закончила формирование временного интервала, то сигнал с выхода триггера 9 пройдет через элементы И 13 и ИЛИ 20 к одному из входов .элемента И 23 блока 2. Остальные входы это-. го элемента подключены к аналогичным выходам других моделей 1 ветвей. - : Если временной интервал в данно ветви еще не сформирован, то триггер 9 находится в состоянии О и ка входе элемента И 13 присутств ет запрет с его единичного.выхода. В этом случае сигнал с выхода задатчика б не пройдет через элемент И 13 и на выходе элемента ИЛИ 20 и данный момент появится запрещающий сигнал, который поступит в .блок 2 на соответствукиций вход эле мента И 23. В случаях, когда импульсы на .вьйсоде задатчика 6 адресов отсутствуют на входе элемента ИЛИ 20 присутствует разрешающий сигнал с выхода элементна. НЕ 18. Таким образсйЛг запрет на входах элемента И 2 только от тех моделей ветвей, которые входят в рассматриваемый узе но не сформировали свою длительность. В этом случае запрещающий сигнал проходит на выход элемента И 23 и через элемент ИЛИ 28 на вхо ды всех моделей 1. Этот сигнал запрещает подготовку соответствующих формирователей 7 к отсчетуимпульсов с Генератора 4. На выходе элемента НЕ 17 возникает при этом раз решающий сигнал, который поступает на второй вход элемента И 14, и так как на первом его входе присутствует выходной сигнал задатчика б, триггер 10 устанавливается в состояние 1. Если все ветви, входящие в рассматриваемый узел, сформировали временной интервал, то на выходе элемента И 23., блока 2 появляется разрешающий сигнгш, который поступает .через элемент ИЛИ 28 на вхоДы моделей ветвей. Этот сигнал запрещает подготовку соответствующих фо1%шрО8ателёй 7 к отсчету импульсов с генератора 4. На выходе элемента НЕ 17 возникает при этом раз решающий сигнал, который поступает Ма второй вход элемента И 14, и, так как на первом его входе присут стзэует выходной сигнал эадатчика 6, триггер 10 устанавливается . в со тояние 1. Если все ветви, входящие в рассматриваемый узел, сформировали временной интервал то на выходе элемента И 23 блока 2 появляемся раэрешгиощий сигнал, который поступаетчерез-элемент ИЛИ 28 на входы Моделей ветвей. Разрешающий сиг нал згшрещаётчерез элемент НЕ 17 установку триггера ДО, в состояние О и также проходит на выход элемента И 12тех моделей, которые выходят из рассматриваемого узла, т.е. тех ветвей, где в данный момент времени есть сигнал на выходе задатчика 5. - . ; Импульсы с генератора 4 поступают на входы задатчиков 5 и б адресов до тех пор, пока хотя €ы iia од-. IHOM из входов блока 2 формирования топологии присутствует сигнал с выхода триггера 8 какой-либо модели 1 ветви. После того, как все триггесиы -8 установлены в состояние I О выходными сигналами сортйетст- вующих задатчиков адресов 6, блок 2 формирования топологии запрещает прохождение импульсов этой серии на входы задатчиков а; есов и разрешает поступление импульсов на входы формирователей йре- менных интервалов. . Когда сформирован конечный узел сетевого графика, все триггеры 8 моделей 1 устанавливаются в состояние О. После этого сигнал с выхода элемента ИЛИ 28 блока 2 поступает в блок 3 управления на вход элемента И 41, и, так как сфо1: 1ирован конечный узел сетевого графика, импульс переполнения с выхода задатчика 33 через элемент-И 41 устанавливает В; состояние О триггер 35. Суммарное количество импульсов, поступившее на входа блока формирования топологии с начала счета,, равно величине длиннейшего пути, а состояния 1 триггеров 10 .укажут, какие ветви принадлежат дереву максимальных путей. Для определения конфигурации длиннейших путей между начальным и конечным узлами сетевого графика в блоке 3 предварительно в задатчики 32 и 33 заносятся соответственно адреса начального иконечного узлов сетевого графика, триггеЕял 34-36 устанавливаются в состояние О. На вход 52 блока 3 -подается сигнал Пуск индикации, который устанавливает в состояние 1 . триггер 36. Последнее состояние триггера 36 выдает разрюзение на выход 49 блока 3, соединенного со входом элемента И 25, а также сигнал с еди;ничного выхода триггера 36 проходит через элемент ИЛИ 42 и разрешает прохождение цмпульсов с выхода генератора 4 через элементи 37 На входы задатчиков 32 к 33. Кроме того, импульсы с выхода элемента И 37 проходят через элемент И 39, на втором входе которого присутствует разрешение с выхода триггера 36, далее через элемент ИЛИ 43 на выход блока 3 (выход 44, где поступают на вход элемента ИЛИ 27. Itoi- V пульсы с выхода элемента ИЛИ 27 поступают на входы задатчиков 5 н 6 до тех пор, пока на выходах задатчиков б, в которых записан адрес ко.нечного узла....сетевого графика, не появится сигнал переполнения. В тот же момент времени на выходе задатчика 33 появляется -сигнал переполнения, который поступает на выход блока 3 ( выход 47 и далее на элемент ИЛИ 29 блока 2. .Сигнал с выхода элемента ИЛИ 29 поступит на первый вход элемента И 15, на втором входе которого в этот момент будет присутствовать сигнал с выхода задатчика б адресов конечного узла. Если на третьем входе этого элемента есть разрешение с выхода-триггера 10, т.е. если, ветвь сформировала свою длительность последней в конечном узле сетевого графика, то .выходной сигнал элемента И 15 установит через элемент ИЛИ 21 в состояние 1 триггер 8. При этом сигнал с выхода элемента НЕ 19 запретит прохождение сигнала с задатчиков 6 через элемент И 1 на нулевой вход триггера 8 и тем-са мым исключит неопределенность состо яния этого триггера. Единичный выход триггера 8 разрешает прохождение им пульсов с выхода задатчика 5 через элемент И-16 на вход элемента ИЛИ 30 блока 2. Остальные входы этого элемента подключены к аналогичным выходам остальных моделей ветвей. Сигнал с выхода элемента ИЛИ 30 поступает н второй вход элемента И 25 и через элемент ИЛИ 29 на входы элементов И 15. При этом устанавливаются в состояние 1 триггера 8 тех моделей ветвей, которые последними формируют длительность в начальном узле рассмотренной ветви. Подобный процесс продолжается до тех пор, пока на входах блока 2 формирования топологии не появляется .сигнал с выхода задатчиков 5, соответствующих начальному узлу сетевого графика. Это говорит об окончании процесса выделения длиннейшего пути., При этом выработанный сигнал с выхода элемента 29 ИЛИ поступает в блок 3 (вход 46) на вход элемента И 40 и, так как сформирован начальный узел сетевого графика, он проходит через элемент И 40 и устанавливает триггер 36 в состояние О Блок 3 управления при этом прекращает подачу импульсов на элемент ИЛИ 27 и подает запрет на элемент И 25. Состояния 1 триггеров 8 укажут на принадлежность ветвей длиннейшему пути сетевого графика. Введение в модели ветвей новых элементов и новых связей позволяет реализовать функции моделирования сетевого графика с использованием меньшего числа триггеров в моДели , ветви. 4S

диг.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 1972 |

|

SU422002A1 | |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР ,№608169, кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1983-04-15—Публикация

1981-07-24—Подача