Изобретение относится к устройствам умножения частоты электрического сигнала и может быть использовано в аналоговых вычислительных машинах.

Известен умножитель частоты импульсов,.содержавши счетный триггер, ключи, источники тока, усилительный блок, пороговые ..

Недостатками известного умножителя являются ограниченный диапазон коэффициента умножения частоты и малая точностьработы.

Наиболее близким к предложенному. являетЬя умножитель частоты импульсов в и раз, содержащий масштабные блоки, элемент ИЛИ, прроговые блоки, источник опорного напряжения, интегратор 2 J.

Недостатком данного умножителя частоты является малое быстродействи

Цель изобретения - повышение быстродействия.

С этой целью в умножитель частоты импульсов в h раз, содержгиций И-1 масштабных блоков, выходы которых соединены с первыми входами соответствующих пороговых блоков, выходы пороговых блоков подключены к входам элемента ИЛИ, выход которого являетс выходом умножителя, нторые входы пороговых блоков соединены с выходом источника onofiHoro напряжения, интегратор, выход которого подключен к первому входу первого масштабного блока, введены блок задержки и блок памяти, причем управлякяций вход блок памяти соединен с входом блока задержки, выход которого подключен к соответствующему входу элемента ИЛИ и входу установки нулевого 3rfkчения интегратора, вход которого соединен с выходом источника опорног напряжения, выход интегратора подключен к первым входам остальных масштабных блоков и к входу блока памяти выход которого соединен с вторыми входами всех масштабных блоков, вход блока задержки является входом умножителя.

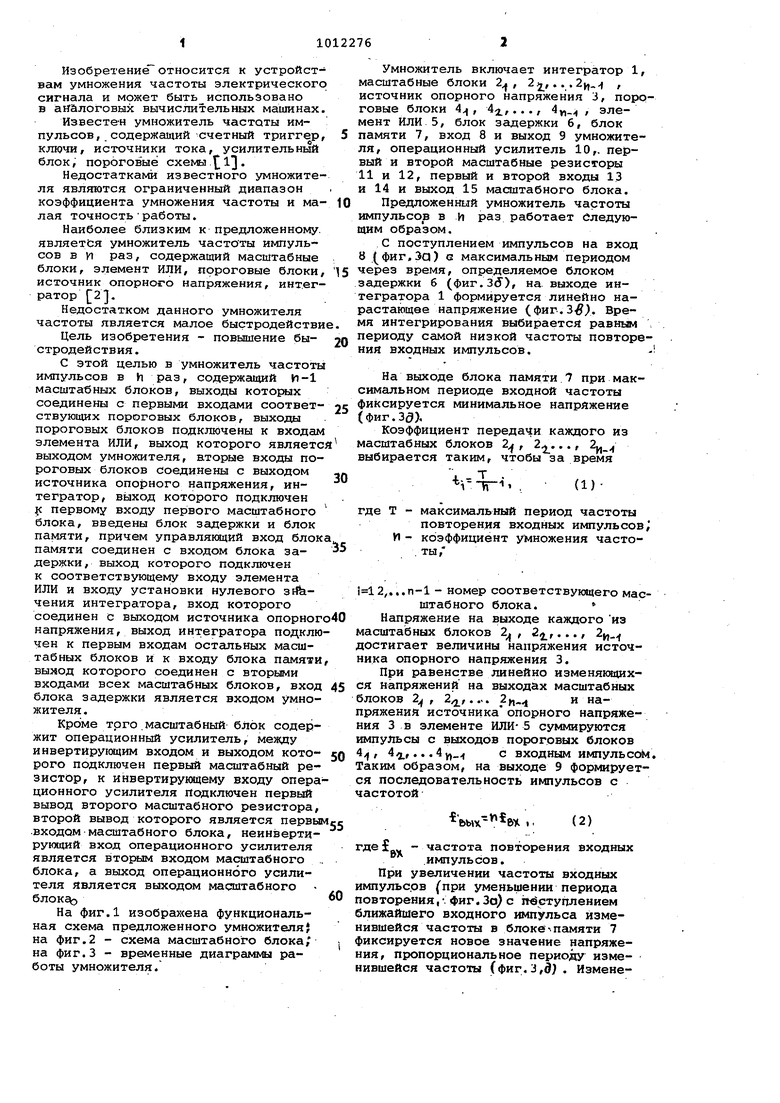

Кроме того.масштабный блок содержит операционный усилитель, между инвертирующим входом и выходом которого подключен первый масштабный резистор, к инвертирующему входу операционного усилителя подключен первый вывод второго масштабного резистора, второй вывод которого является первы входом масштабного блока, неинвертирующий вход операционного усилителя является втоЕндм входом масштабного . блока, а выход операционного усилителя является выходом масштабного

блок

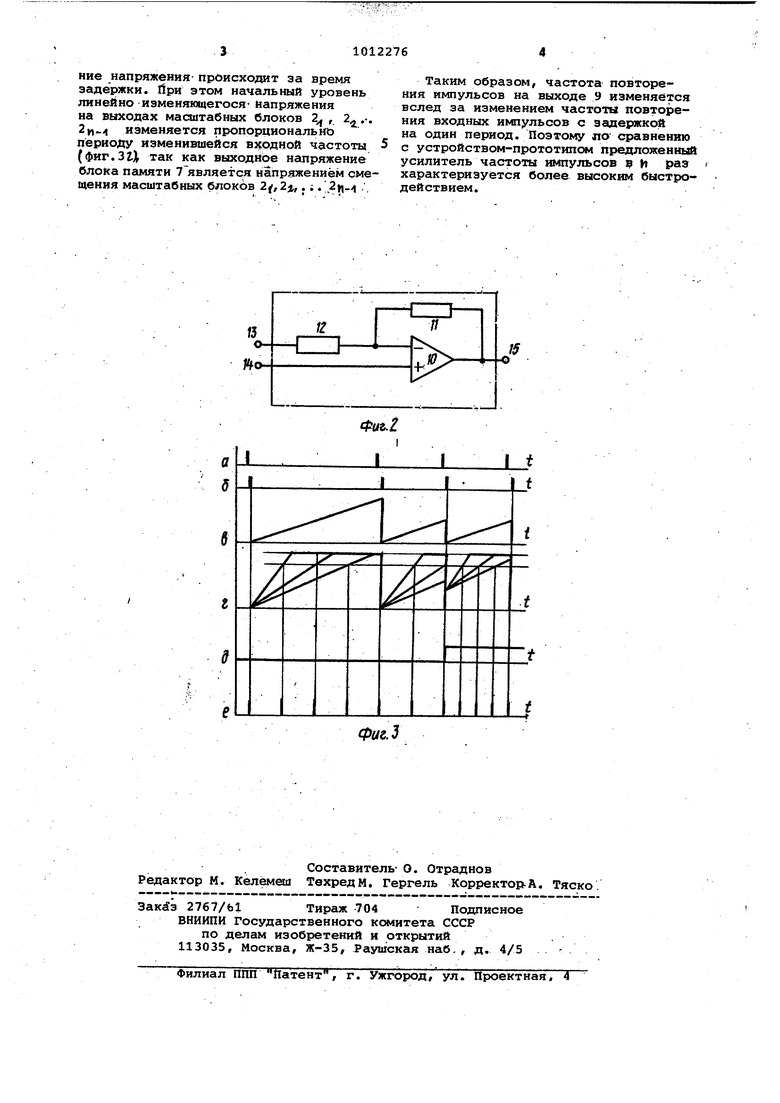

На фиг.1 изображена функциональная схема предложенного умножителя) на фиг.2 - схема масштабного блока, на фиг.З - временные диаграммы работы умножителя.

Умножитель включает интегратор 1 масштабные блоки 2, 2.,.. . 2|, , источник опорного напряжения 3, порговые блоки 4 , 4.,..., 4у, , элемент ИЛИ 5, блок задержки 6, блок памяти 7, вход 8 и выход 9 умножителя, операционный усилитель 10,. первый и второй масштабные резисторы 11 и 12, первый и второй входы 13 и 14 и выход 15 масштабного блока.

Предложенный умножитель частоты импульсов в и раз работает Следующим образом.

С поступлением импульсов на вход 8 (фиг.За) с максимальным периодом через время, определяемое блоком задержки б (фиг.Зб), на выходе интегратора 1 формируется линейно нарастающее напряжение (фиг. . Время интегрирования выбирается равным периоду самой низкой частоты повторния входных импульсов.

На выходе блока памяти 7 при максимальном периоде входной частоты фиксируется минимальное напряжение ( фиг. 3(Э).

Коэффициент передачи каждого из масштабных блоков 2 , 2,,., 2y выбирается таким, чтобы за время

brir

(1)где Т - максимальный период частоты

повторения входных импульсов; И - коэффициент умножения часто. ты,

,,..п-1 - номер соответствующего масштабного блока.

Напряжение на выходе каждого из масштабных блоков 2, 2,,.., 2, достигает величины напряжения источника опорного напряжения 3.

При равенстве линейно изменякицихся напряжений на выходах масштабных блоков 2 , .... 2f и напряжения источникаопорного напряжения 3 в элементе ИЛИ- 5 суммируются импульсы с выходов пороговых блоков 4 , 4,... 4 у, с входным импульсе Таким образом, на выходе 9 формируется последовательность импульсов с частотой

(2)

где - частота повторения входных

импульсов.

При увеличении частоты входных импульсов (при уменьшении периода повторения, . фиг. За) с пёступлением ближайшего входного импульса изменившейся частоты в блoкe пaмяти 7 фиксируется новое значение напряжения, пропорциональное периоду изменившейся частоты (фиг.3,д} . Изменение напряжения- происходит за время задержки, йри этом начальный уровень линейно изменяющегося- Напряжения на выходах масштабных блоков 2

f. 4 2и изменяется пропорционально периоду изменившейся взводной частоты (фпг.31 так как выходное напряжение блока памяти 7 являвтся напряжением смещения масштабных блоков 2,2,,. ; . .

Таким образом, частота повторения импульсов на выходе 9 изменяется вслед за изменением частоты повторения входных импульсов с задержкой на один период. Поэтому ло сравнению с устройством-прототипом предложенный усилитель частоты импульсов в И раз характеризуется более высоким быстродействием.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ИЗ СИГНАЛОВ ИНДУКЦИОННЫХ ДАТЧИКОВ ЧАСТОТЫ ВРАЩЕНИЯ | 2007 |

|

RU2352057C1 |

| Усредняющее устройство | 1981 |

|

SU1023345A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ИЗ СИГНАЛОВ ИНДУКЦИОННЫХ ДАТЧИКОВ ЧАСТОТЫ ВРАЩЕНИЯ | 2007 |

|

RU2353052C1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОДИЧЕСКОГО СИГНАЛА В ЧАСТОТУ И ПЕРИОД | 2012 |

|

RU2520409C2 |

| Устройство синхронизации электроразведочных приемников | 1987 |

|

SU1449961A1 |

| Множительно-делительное устройство | 1981 |

|

SU995098A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ АНАЛОГОВОГО СИГНАЛА ОПТИЧЕСКОГО ДАТЧИКА В ЦИФРОВОЙ КОД | 1995 |

|

RU2097915C1 |

1. УМНОЖИТ ВЛБ ЧАСТОЙ ИМ ПУЛЬСОВ В п РАЗ, содержа&Шй П -1 масштабных блоков, выходы которых соединены с первыми входами соотве ствующих пороговых блоков, выходы пороговых блоков подключены к входам элемента ИЛИ, выход которого является выходом умножителя, втор входы пороговых блоков соединены с выходом источника опорного напря жения, интегратор, выход которого подключен к первому входу первого масштабного блока, отличающийся тем, что, с целью повышения быстродействия, в него ввела г. ны блок задержки и блок памят и, при чем управляющий вход блока памяти. соединен с входом блока задержки-, выход которого подключен, к соответствуннцему входу элемента ИЛИ и входу установки нулевого значения интегратора, вход которого соединен с выходом источника опорного напряжения, выход интегратора подключен к первым входам остальных масштабных блоков и входу блока памяти, выход которого соединен с вторыми входами всех масштабных блоков, вход блока задержки является входом умножителя. 2. Умножитель поп.1, отлич а ю й1 и и с я тем, что масштабный блок содержит операционный усилитель, между инвертирующим входом и выходом котор.ого подключен первый масштаб- Л ный резистор, к инвертирующему входу операционного усилителя подключен первый вывод второго масштабного резистора, второй вывод которого яв- 2 ляется первым входом масштабного блока, неинвертирующий вход операционного усилителя является вторым входоМ; масштабного блока, а выход операцион- г | ного усилителя является выходом масш- .( табного блока.

А

/

Фиг.З

Авторы

Даты

1983-04-15—Публикация

1981-11-18—Подача