и третьим входами множительно-делительного устройства , второй вывод первого масштабирующего резистора соединен с инвертирующим входом первого логарифмирующего блока, выходы первого, второго и третьего интеграторов соединены с первыми управляющими входами соответственно первого, второго и третьего логарфмирующих блоков, выходы распределителя импульсов подключены соответственно к управляющим входам модулятора, фазочувствительного выпрямителя, коммутатора и к вторым управляющим входам первого, второго и третьего логарифмирующих блоков.

Логарифмирующий блок содержит соединенные последовательно модулятор, первый операционный усилитель, оптрон, второй операционный усилитель, логарифмирующий диод, второй вывод логарифмирующего диода подключен к входу первого операционного усилителя, выход которого является выходом логарифмирующего блока, между выходом и входом блока второго операционного усилителя подключен масштабный резистор отрицательной обратной связи, вход модулятора является неинвертирующим входом логарифмирующего блока, управляющий вход оптрона является первьлм управляющим входом логарифмирующего блока, вторы управляющим входом которого является управляющий вход модулятора, инвертирующий вход второго операционногоусилителя является инвертирующим входом логарифмирующего блока.

Причем модулятор содержит первый масштабный резистор, первый и второй выводы которого являются соответственно входом и выходом модулятора, параллельно первому масштабному резистору подключена цепь из соединенных последовательно второго масштабного резистора и ключа, управляющий вход ключа является управляющим входом модулятора.

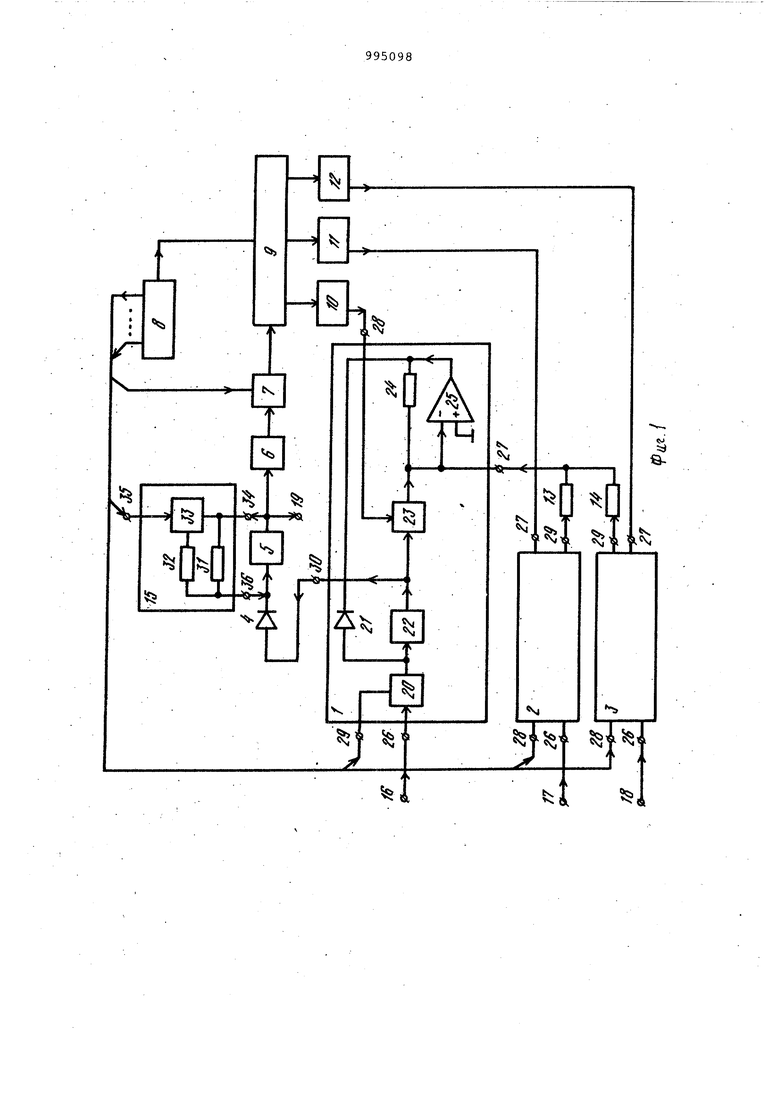

На фиг.1 изображены функциональные схемы множительно-делительного устройства и входящих в его состав логарифмирующего блока и модулйтора, на фиг.2 - сигналы,действующие во множительно-делительном устройстве.

Устройство включает первый, второй и третий логарифмирующие блоки 1-3, антилогарифмирующий диод 4, первый и второй операционные усилители 5 и 6, фазочувствительный выпрямитель 7, распределитель 8 импульсов, коммутатор 9, первый, второй и третий интеграторы 10-12, первый, и второй масштабирующие резисторы 13 и 14, модулятор 15, первый,второй и третий входы 16-18 и выход 19,

Логарифмирующий блок содержит модулятор 20, логарифмирующий диод 21, первый операционный усилитель

22, оптрон 23, масштабный резистор 24 отрицательной обратной связи, второй операционный усилитель 25, неинвертирующий вход 26, инвертирующий вход 27, первый и второй управляющие входы 28 и 29 и выход 30.

Модулятор включает первый и второй масштабные резисторы 31 и 32, ключ 33, вход 34, управляющий вход 35 и выход 36.

Множительно-делительное .устройство работает следующим образом.

На первый, второй и третий входы 16-18 подаются входные напряжения соответственно и2И и, например, на первый вход 16 - делимое, на второй вход 17 - делитель, на третий вход 18 - масштабный коэффициент (сомножитель) . С выходов распределителя 8 импульсов на вторые управляющие входы 29 первого, второго и третьего логарифмирующих блоков 1-3 поступают соответствующие управляющие сигналы и, и,;2 и ( (фиг.25, & ,1.) Эти сигналы представляют собой чередующиеся последовательности логических О и Ч, сдвинутые относительно друг друга на одинаковые интервалы времени , при этом управляющий сигнал является инверсным относительно управляющих сигналов и и Ол/з- Уровень логических и О соответствуют закрытому и открытому состояниям ключей модуляторов 15 и 20. Частота повторения управляющих сигналов Us;-), U и и у}, равна и значительно мёнвЛ

ше частоты управляющего сигнала Uy , поступающего на управляющие входы модулятора 15 и фазочувствительного выпрямителя 7.

Входные напряжения с первого, второго и третьего входов 16-18 преобразуются в первом, втором и третьем логарифмирующих блоках 1-3 так, что на их выходах формируются направле ния, пропорциональные логарифму входных напряжений.

В момент времени -tg - t на второй управляющий вход первого логарифмирующего блока 1 поступает управляющий сигнал- и-ч/1 (фиг.2 5 ) . Напряжение на выходе первого логарифмирующего блока 1 принимает два значения

КТ,

U.S

en-i-l; (1)

1

КТ„

-p,(2J N

где К - постоянная Больцмана; ( - заряд электрона Jo ток насыщения диода; Т - температура логарифмирующегодиода 21 первого логгфифмйрующего блока 1; S. крутизна преобразования дуляторов 15 и 20, когда их ключи замкнуты и разомкJ нуты соответственно; К-, - коэффициент передачи, первого логарифмирующегоблока 1. В момент времени t-, - i поступает управляющий сигнал U-yj (фиг,2в) на второй управляющий вход второго логарифмирующего блока 2, при этом напряжение на его выходе принимает два значения .где Kg - коэффициент передачи второго логарифмирующего блока 2; Т.2 температура логари 1я ирующего диода 21 второго логарифми- - рующего блока 2.В момент времени Ч2 - t поступает управляющий сигнал и, (фиг.2г) на второй управляющий вход третьего логарифмирующего блока. 3 и напряжение на его,выходе в этом интервале времени принимает два значения где Kj - коэффициент передачи третьего логарифмирующего блока. 3; температурка логарифмирующего диода 21 третьего логарифмирующего блока 3. Таким образом, на вькодах первого, второго и третьего логарифмирующих блоков 1-3 в течение времени (фиг.2 а , е ,ж) с периодом повторения ЗТ формируются пульсирующие напряжения, определяемые сортве-fcTвенно по формулам (1) - (6). Эти напряжения, суммируясь с учетом знака в первом логарифмирующем блоке 1, приводят к появлению на его выходе 30 напряжения, которое в йнto-t, при нюхает тервале времени четыре значения

A4r 2: 4% 5SlM-) J42-- 11-K4U22 5% 87

43 .i « U.U. + KjUj iClOj

11 тив рую но зи зна уси сум вог мак 45 -Выч (1 нап мир

Полученные величины приращений

60 напряжения для интервала ig -tj пропорциональны температурам логарифмирующих диодов 21 и обратнрпропорциональны коэФФициент и( передачи соответствующих логарифмирующих

65 блоков. 5 . коэффициенты,, равные отношению сопротивления оптрона 23 к сопротгивлёниям первого и второго масштгабирующих ре- зисторов 13, и 14 COOT-. ветственно.; При условии, что величины сопролений первого и второго масштабищих резисторов R-,j и масштабо резистора 24 отрицательной свяравны, выполняется равенство VKj. (11) Подставляя в выражения t7) - (10). чения напряжений из (1) - (6) и тывая (11J, получим Из выражений (12) -(15) видно, что марное выходное напряжение перо логарифмирующего блока 1 чмеет симальное значение.согласно (13). итая из - (13) поочередно (1.2), ) и (15) , получим приращение. ряжения на выходе первого логарифующего блока 1 Таким образом, на выходе первого логарифмирующего блока I напряжение имеет приращение в виде меандра (фиг.2и). Это напряжение поступает ,на антилогарифмирующий диод 4, вызывая через него соответствующий ток который подается на первый операционный усилитель 5 и модулятор 15, которые совместно выполняют функцию пре обраэователя ток - напряжение с переменной крутизной, изменяемой с частотой сигнала (фиг,2о|}. В результате чего на выходепервого операционного усилителя 5 появляется напряжение, имеющее переменную составляющую в виде меандра. Эта составляющая уЪйливается вторым операционным усилителем б и выпрямляется фазочувствительным выпрямителем 7. В интервале времени to -t к выход фазочувствительного выпрямителя 7 чёрез коммутатор 9 поочередно подключаются первый, второй и третий интег раторы 10-12. Выходные напряжения этих интеграторов подаются на первые управлякшие входы соответственно/ первого, второ го и третьего логарифмирующих блоков 1-3 и изменяют их коэффициенты передачи таким образом, что переменная составляющая в выходном напряжении первого операционного усилителя 5 уменьшается. Регулировка происходит до тех ПОР, пока переменная составля ющая не станет равной нулю. При этом напряжение на антилогарифмирующем ди оде 4, связанное с выходным напряжением логарифмической зависимостью в Ьз, принимаинтервале времени ет только -два значения . 120 6X2 где Т, - температура антилогарифмирутощего диода 4. Вычитая (20) из (19), получим ве-личину переменной составляющей ли„,и„, -и 5 В установившемся режиме величина переменной составляющей с выхода пер вого логарифмирующего блока 1 должна быть равна велич лне (21), т.е. Приравнивая (16) и (21), (17) и (21), (18) и (21), получим соотношения между температурами переходов огарифмирующих диодов 21 и антилоарифмирующёго диода 4 ., Из ЭТИХ выражений находятся знаения коэффициентов передачи первого, второго и третьего логарифмирующих блоков 1-3, после чего получим u...ue,.en|3.. Вычитая (21) из. (19) , получим u.. В установившемся режиме (26) равно (27) или V. КТ Откуда Из приведенного описания работы и доказательства следует, что различия в температурах диодов и их дрейф не влияют на точностные характеристики предлагаемого множительно-делит тельного утсройства, т.е. оно обладает более высокой точностью выполнения множительно-делительной операции. Формула изобретения : 1.Множительно-делительное устройство, содержащее первый, второй и третий логарифмирующие блоки, антилогарифмирующий диод, один вывод которого соединен с входом первого операционного усилителя, выход последнего является выходом множительно-делитеЛьного .устройства, выход второго логарифмирующего блока через соедит ненные последовательно первый и второй масштабирующие резисторы подключен к выходу третьего логарифмирующего блока, второй операционный усилитель, отличающееся тем, что,с целью повьв11ения точности высхлнения множительно-делительных операций, в него введены первый, второй и третий интеграторы, модулятор, фаэочувствительный выпрямитель, распределитель импульсов и коммутатор, причем входы первого, второго и третьего интеграторов подключены к соот ветствующим выходам коммутатора, выход первого операционного усилителя через второй операционный усилитель соединен с входом фаэочувствительного выпрямителя, выход которого подключён к управляющему входу коммутатора, вход модулятора соединен с выходом первого операционного усилителя вход которого подключен к выходу модуля тора , выход первого логари(1 1ируюцег6 блока соединен с вторьм выводом аитилогари ирующего диода, неинвертирукнаде входеа первого, второго и третьего логарифмирующих блоков являются соответственно первом, вторым и третьим входами множительно-делиЧ iтельного устройства, второй вывод первого масштабирующего резистора соединен с инвертирующим входом первого логарифмирующего блока, выходы первого, второго и третьего интеграторов соединены с первыми управляющими входами соответственно первого, второго и третьего логарифмирующих блоков, выходы распределителя импуль сов подключены соответственно к управлякидим входам модулято|)а, фазочувствительного выпрямителя, коммута тора и к вторым управляющим входам первогоj второго и третьего логарифмирующих блоков, 2. Устройс во по П.1, от л и ч а ю щ е е с я тем, что логарифмирующий блок содержит соединенные последовательно модулятор, первый операционный усилитель, оптрон, второй операционный усилитель, логарифмирующий диод, второй вывод логарифмирующего диода подключен к входу первого операционного усилителя, выход котоpordf является выходом логарифмирующего блока, между выходом и входом второго операционного усилителя ключей масштабный резистор отрицательной обратной связи, вход модулятора является неинвертирующим входом :логари4 1ирующего блока, управляющий вход оптрона является первьм управляющим входом логарифмируквдего блока, вторые управлякядим входом которого является управляющий вход модулятора, инвертирующий вход второго операционного усилителя является инвертирующим входсж логарифмирующего блока. 3, Устройство по П.1, отлич аю щ е е с я тем, что модулятор содержит первый масштабный резистор первый и второй выводы которого являются соответственно входом и выходом модулятора, параллельно первому масштабному резистору подключена цепь из соединенных последовательно второго масштабного резистора и ключа, управляющий вход ключа является управляющим входом модулятора. Источники информации, принятые во внимание при экспертизе 1.Алексеенко А.Г. и др. Применение прецизионных аналоговых ИС. М., Радио и связь, 1981, с. 95-96, рис. 3.17. 2.Жилинскас Р-П.П. Измерители отношения и их применение в радиоизмерительной технике. М., -Сов. радио, 1975, с. 85, рис. 3.26 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический усилитель | 1980 |

|

SU934500A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Аналоговый умножитель | 1981 |

|

SU995099A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Вычислительное устройство | 1987 |

|

SU1462364A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Вычислительное устройство | 1987 |

|

SU1539798A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Множительное устройств | 1979 |

|

SU824223A1 |

| ВОЛОКОННО-ОПТИЧЕСКИЙ ИЗМЕРИТЕЛЬ УГЛОВОЙ СКОРОСТИ | 2012 |

|

RU2497077C1 |

Авторы

Даты

1983-02-07—Публикация

1981-08-21—Подача