Изобретение относится k вычислительной и контрольно-измерительной технике и может быть использовано в устройствах обработки аналоговой информации.

Известно аналоговое запоминающее

устройство замкнутого типа с коррекцией аддитивных погрешностей, входящих в его состав усилителей

Недостатками этого устройства являются низкое быстродействие и большие аппаратурные затраты, приводящие к снижению надежности устройства.

Наиболее близким к предлагаемому является аналоговое запоминающее устройство, содержащее дифференциальный усилитель, первый и второй коммутаторы, накопительные элементы, выполненные в виде конденсаторов, повторители напряжения, резистивный делитель напряжения .

В этом устройстве также осуществляется коррекция аддитивных погрешнос тей, вносимых дифференциальным усилителем и повторителями напряжения, однако точность устройства недостаточно высока из-за погрешности, вносимой разбросом сопротивлений открытого ключа у коммутаторов; и изменяющей коэффициент передачи резистивного делителя.

Цель изобретения - увеличение точнести устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее первый и второй накопительные элементы, вьшо/шенные в виде конденсаторов, первые обкладки которых соединены с шиной нулевого потенциала, вторые обкладки - соответственно с первь1м и вторым выходами первого коммутатора, вторая обкладка первого конденсатора соединша с входом повторителя напряжения, выход которого С9единен с первым входом резистивного делителя напряжения, второй вход которого является первым входом устройства, второй коммутатор, введен дифференциальнодифференциальный усилитель, выход которого соединен с входом первого коммутатора, первый инвертирующий вход дифференциально-дифференциального усилителя соединен со средней точкой резистивного делителя напряжения и первым ъко. дом второго коммутатора, второй вход которого является вторым входом устройства, а выход подключен к первому нешгвертирующему входу дифференциальнодифференциального усилителя, второй инвертирующий и второй веинвертируюШий входы которого соединены соответственно с второй обкладкой второго конденсатора и с щиной пулевого потенциала, выход повторителя напряжения является выходом устройства.

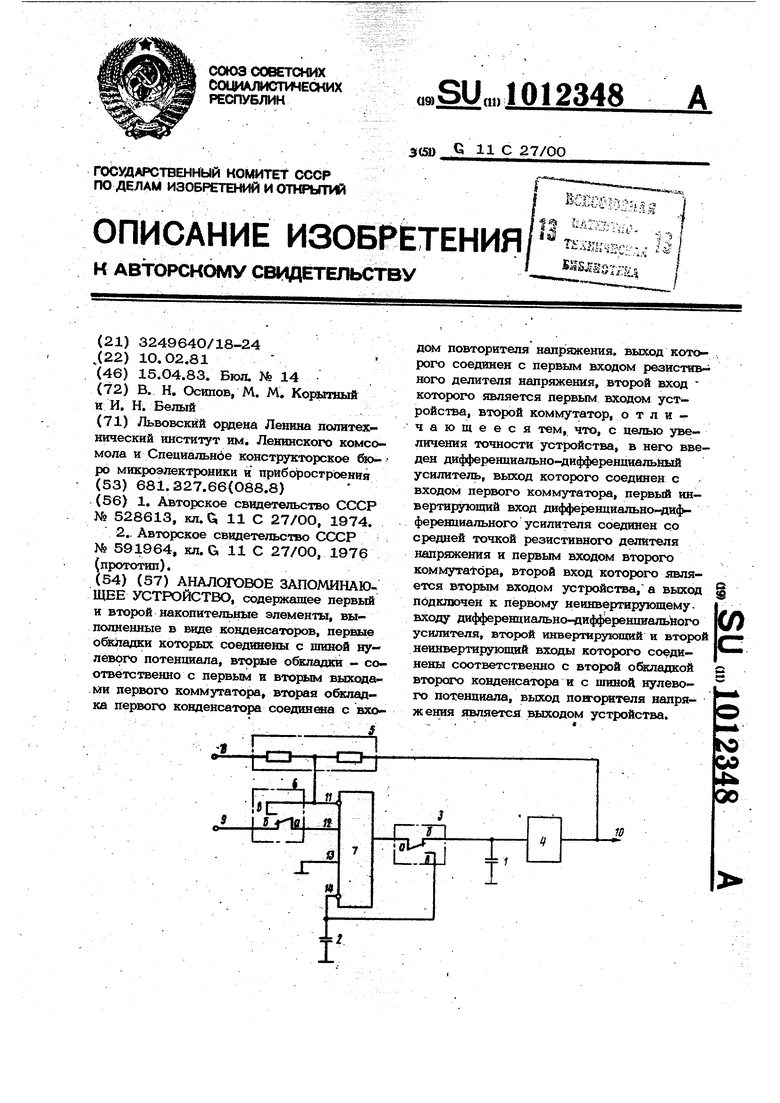

На чертеже представлена функциональная схема предлагаемого аналогового запоминающего устройства.

Устройство содержит первый конденсатор 1, второй конденсатор 2, первый коммутатор 3, повторитель напряжения 4 резистивный делитель напряжения 5, второй коммутатор 6 и дифференциальнодифференциальный усилитель 7, первый вход 8, второй вход 9 и выход устройства 10, входы 11-14 дифференциальнодифференциального усилителя 7.

Устройство работает следующим образом.

При коммутаторах 3 и 6 в положении а-в устройство находится в режиме хранен

Напряжение на первом конденсаторе 1 соответствует ранее зафиксированному мгновенному значению входного сигнала. Коммутатор 6 в положении d- Ъ закорачивает Еходы 11, 12, а коммутатор 3 замыкает цепь отрицательной обратной связи дифференциально-дифференциального усилителя 7. Этот усилитель обеспечивает усиление дифференциальных напряжений, приложенных между входами 11 и 1 а также между входами 13 и 14.

В режиме хранения конденсатор 2 заряжается до напряжения Uc2-

(Я

+ U

H-1t,

02

где UQ и (} - напряжения смещения нуля дифференциального усилителя 7 по входам 1114 соответственно;

1 И - коэффициенты усиления

входов 1144. При переходе в режим выборки коммутаторы 3 и 6 устанавливаются в положение а-б. На втором конденсаторе 2 напряжение Up2 фиксируется. Все устройство в целом схватывается через р)езистив- ный делитель напряжения 5 общей отрицательной обратной связью.

Тогда первый конденсатор 1 заряжается с выхода усилителя 7 до нового напряжения, а устанавливающееся на выходе устройства нап{ яжение может быть найден из выражения:. .

1i.

-и.

и„..и.

вых вхИ К р с21+1 р.

11

(2) + U.

+Ц

о- l + 02 . Значение fb определяется где R2 и сопротивления резисторо резистивном делителе напряжения 5. С учетом (1) равенство (2) может быть представлено в виде It. II -1 IА , 4с.. ъ. o-i (гидрйцр) vrtf «« л, V, 02 1+К2)(1+(Ы) Выражения, взятые в квадратные скобки, показывают степень подавления напряжений смещения нуля дифференциально-дифференциального усилителя 7 и могут быть преобразованы к виду Отсюда огч+1 2Р следует, что напряжение смещения нуля UQ и ® -1 f В (2) не учитываются погрещности повторителя 4, Однако их влияни на общую точность несущественны, Taic как повторитесь включен в режиме выборки в контур обратной связи. Если учесть также, чтр , то 4 После заряда первого конденсатора коммутаторы 3 и 6 вновь возвращаютс в положение а-в, соответствующее ре- |жиму хранения. Конденсатор 1 сохраняет напряжение, до которого он был заряжен, поскольку все возможные цепи разр$ща (через разомкнутый коммутатор 3, вьюокоомный вход повторителя напряжения) имеют весьма большие постоянные времени, а напряжение на выходе устройства определяется как и в режиме выборки выражением (4). Таким образом, в режиме хранения в устройстве не только осуществляется хранение полезной информации, но и коррекция аддитивных погрещностей, причем для ее осуществления не требуется дополнительного времени. Устройство достаточно просто реализуется. Дифференциально-дифференциальный усилитель 7 может быть собран на базе обычного операционного усилителя. Для этого выходы входного каскада операционного усилителя, которые предусмотрены во многих серийных операционных усилителях, например К 544 УД 2, соединяются с выходами дополнительно, введенного дифференциального каскада, входы которого вместе с входами операционного усилителя являются входами 11-14 дифференциально - дифференциального усилителя 7. Повторитель напряжения 4 может бь1ть вьшолнен ha схеме йстоко вого повторителя. Таким офазом, предложенное устройство характеризуется высокой точностью и, кроме того, его функциональные возможности шире, так как возможна передача входного сигнала к выходу и его запоминание с инвертированием или без инвертирования полярности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU966750A1 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1494042A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1157574A1 |

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1356000A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1152040A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU894795A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU938318A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1320847A1 |

АНАЛСЙГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее первый и второй накопительные элементы, выполненные в виде конденсаторов, первые обкладки которых соединены с шиной нулевого потенциала, вторые обкладки - соответственно с первьш Н вторым выхода .ми первого коммутатора, вторая обкладка первого конденсатора соединена с входом повторителя напряжения, выход кото- . рого соединен с первым входом резистивнего делителя напряжения, второй вход которого является первым входом устройства, второй коммутатор, отличающееся тем, что, с целью увеличения точности устройства, в него введен дифференциально-дифференциальный усилитель, выход которого соединен с входом первого коммутатора, первый инвертирующий вход дифферендиально- и ьференциально1х усилителя соединен со средней точкой резистивного делителя напряжения и первым входом второго коммутатора, второй вход которого является вторым входом устройства,а выход подключен к первому неинвертирующему Л входу дифференциально-дифференциального усилителя, второй инвертирующий и второй неинвертирующий входы которого соединены соответственно с второй обкладкой второго конденсатора и с щиной нулевого потенциала, выход понгорттеля напряжения является выходом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аналоговое запоминающее устройство | 1974 |

|

SU528613A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аналоговое запоминающее устройство | 1976 |

|

SU591964A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-04-15—Публикация

1981-02-10—Подача