2. Устройство по п,1, о т л и чающееся тем, что блок памяти выполнен на триггерах 1К-типа, последовательно соединенных по первым I и К-входам, причем прямой и инверсный выходы последнего триггера соединены соответственное первыми I и К-входами первого триггера, при

этом вторые I-входы триггеров подключены к входу блока памяти, вторые К-входы соединены с первым дополнительным входом блока памяти, второй дополнительный вход которого подключен к S-входу одного из триггеров и R-входам остальных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизацииСигНАлОВ | 1979 |

|

SU853789A1 |

| ФОРМИРОВАТЕЛЬ ПАЧКИ ИМПУЛЬСОВ | 1997 |

|

RU2121219C1 |

| Сумматор @ частотно-импульсных сигналов | 1982 |

|

SU1156068A1 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ И СИГНАЛИЗАЦИЕЙ | 1996 |

|

RU2097819C1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU940285A1 |

| Устройство для генерации пачек импульсов | 1980 |

|

SU884096A1 |

| Устройство для синхронизации сигналов | 1982 |

|

SU1069144A2 |

| Формирователь пачек импульсов | 1983 |

|

SU1150738A1 |

| Устройство для вывода информации | 1986 |

|

SU1322297A1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

Устройство для временной привязки асинхронного сигнала относится к устройствам преобразующим входные сигналы в импульсы, .выдаваемые в трв буемые интервалы времени, и предназначено для синхронизации сигналов с различных дискретных устройств.

Известно синхронизирующее устройство, содержащее входной, выходной триггеры, три элемента И-НЕ, инвертор, шины синхронизируемого, тактового и выходного сигналов, причем шина синхронизируемого сигнала подключена к входу первого элемента И-НЕ и .к нулевому входу выходного триггера, а шина тактового сигнала к входу второго элемента И-НЕ и через инвертор к входу первого элемента И-НЕ, выход которого соединен с единичным входом входного т.риггера, соединенного единичным выходом через второй элемент И-НЕ с единичным входом выходного триггера, шиной выходного сигнала и с входом треTtsero элемента И-НЕ, а единичный выход выходного триггера соединен с вторым входом третьего элемента И-НЕ выход которого подключен к третьему входу первого элемента И-НЕ и к .нулевому входу входного триггераfl.

Недостаток данного устройства заключается в том, что подача импульсов запроса с интервалом, равным или меньшим периода тактовых импульсов, приводит к их потере т.е. нарушению функционирования устройства, а контроль входных импульсов не осуществляется.

. Наиболе близким к предлагаемому является устройство для временной. привязки асинхронного сигнала, содержащее блок памяти синхронизируемых сигналов, блок памяти тактовых сигналов, анализатор нуля ( элемент 2И-ИЛИ-НЕ триггер, шины синхронизируемого, тактового и выходного сигналов, причем шина тактового сигнала соединена с С-входом триггера и с. первым входом блока памяти тактовых сигналов, а шина синхронизируемого сигнала - с входом блока памяти синхронизируемых сигналов, инверсный выход триггера соединен с вторым входо блока памяти тактовых импульсов, D-вход триггера соединен с выходом анализатора нуля, входы анализатора нуля соединены поразрядно с выходами каждого разряда блока памяти синхронизируемых сигналов и Слока- памяти тактовых импульсов .

Однако отсутствие контроля входных сигналов и возможность выдачи ложной информации снижают надежность работы известного устройства. Если на вход устройства с объемом блоков памяти ,равным п,поступают пачки с числом импульсов, равным или большим п, что может наблюдаться при неисправностях в канале передатчика информации, наложении на полезный сигнал высокочастотных помех, наличии колебаний на фронтах, например при дребезге механических контакто устройство будет выдавать ложную информацию. Действительно, если во ,время одного периода тактового сигнала на вход поступает п+1 импульс, то код А в блоке памяти синхронизируемых сигналов изменяется на величину п + 1 ,т.е. равен А + t 1 А + 1, а устройство вырабатывабт на серию из п+1 импульсов только один импульс, так как равенство кодов будет после прибавления к коду блока памяти тактовых импульсов единицы. При этом устройство не изменяет своего режима работы и не фиксирует наличие на входе ложных сигналов, так как в блоках памяти происходит изменение кодов/ по которым невозможно выявить факт появления в пачке лишних импульсов.

Цель изобретения - повышение надежности .

Эта цель достигается тем, что в устройство для временной привязки ассинхронного сигнала, содержащее входную шину, соединенную с входом блока памяти, выходы разрядов которого подключены к первым входам элементов И элемента 2И-ИЛИ-НЕ, выход которого подключен к О-входу триггера, С-вход которого подключен к шине тактовых импульсов, и выходную шину, введены шина сброса, шина контрольного сигнала, элемент И и элемент И-НЕ, входы которого соединены с выходами разрядов блока памяти, а выход подключен к шине контрольного сигнала и одному из входов элемента И, выход которого соединен с выходной шиной и первым дополнительным входом блока памяти, а другие входы элемент И подключены к инверсному выходу и С-входу триггера, 5-вход которого соединен с вторым дополнительным входом блока памяти и шиной сброса при этом второй вход каждого элемента И, элемента 2И-ИЛИ-НЕ соединен с первым входом его соседнего элемента И.

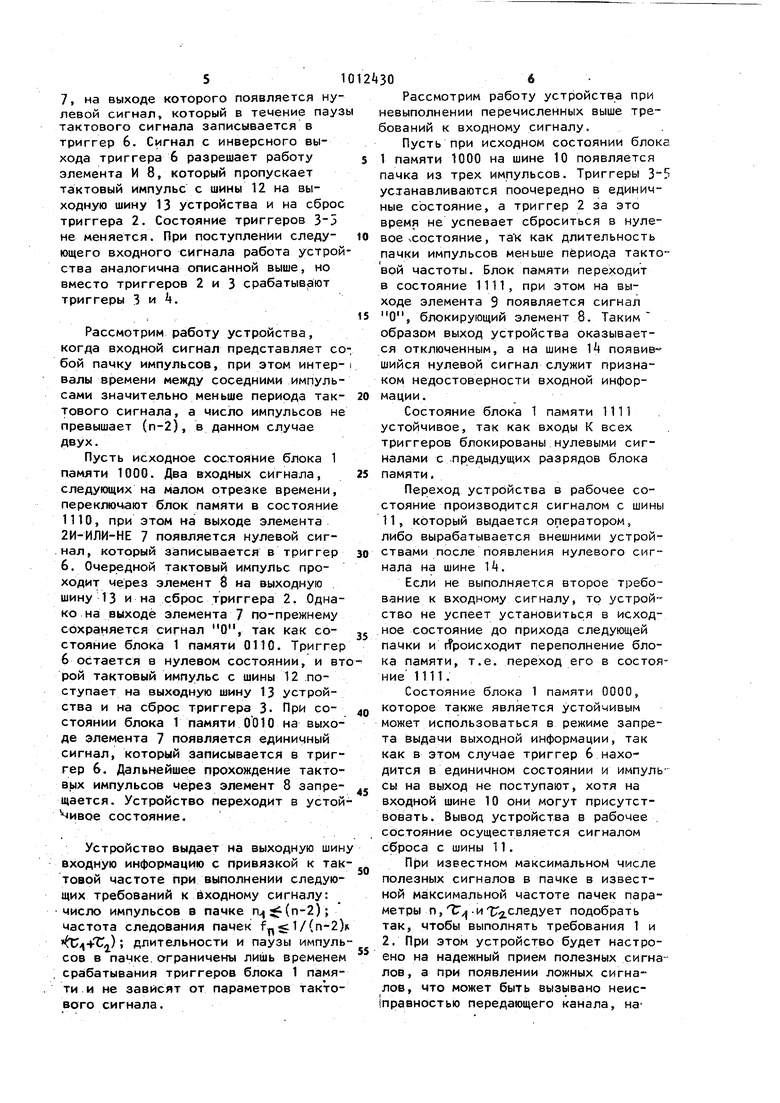

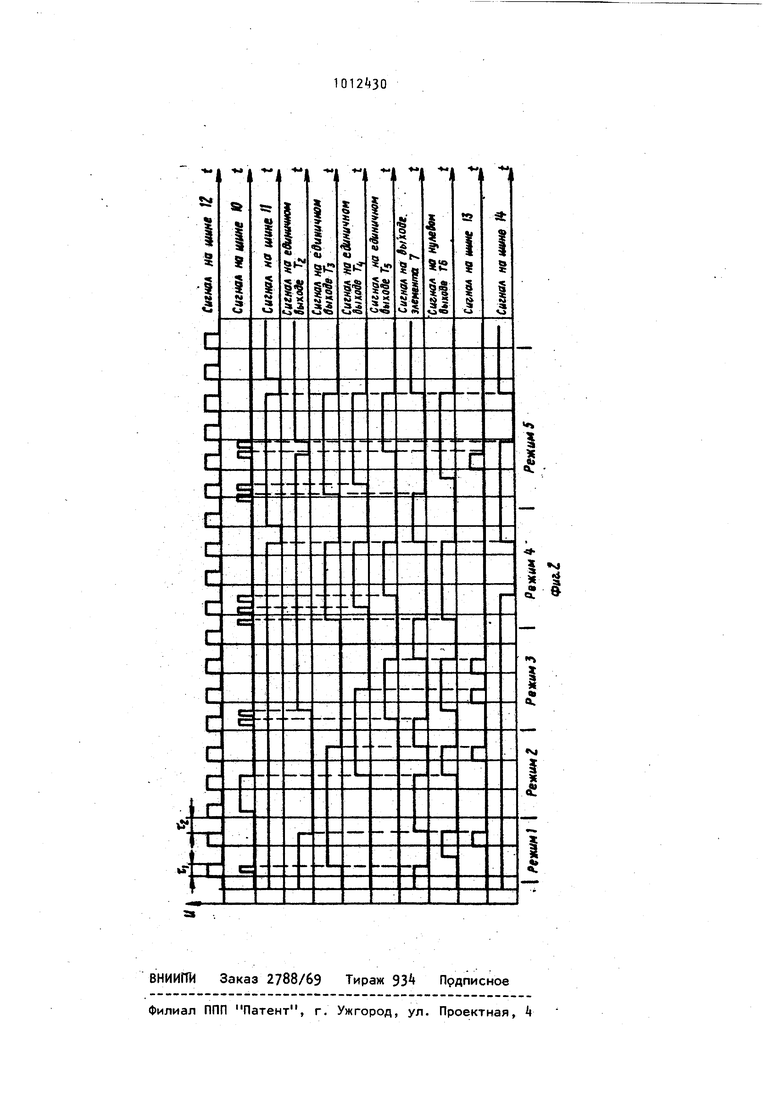

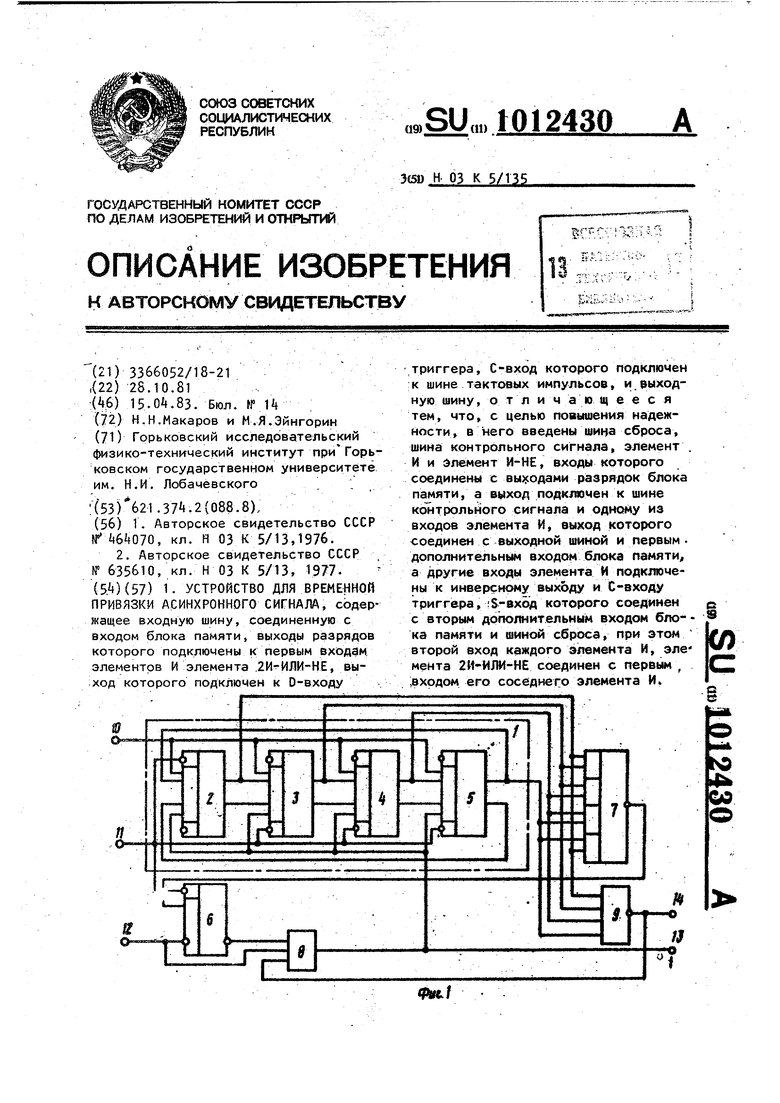

При этом блок памяти выполнен на триггерах .1К-типа, последовательно соединенных по первым I - и К-входам причем прямой и инверсный выходы последнего триггера соединены соответственно с первыми I - и К-входами первого триггера, при этом вторые 1-входы триггеров подключены к входу блока . памяти, вторые К-входы соединены с первым дополнительным входом блока памятиi второй дополнительный вход которого подключен к S-входу одного из триггеров и R-входам остальных. . На. фиг. 1 приведена принципиальная электрическая схема устройства для временной привязки асинхронного сигнала с четырехразрядным блоком памяти (); на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит блок памяти 1 выполненный на 1К-триггерах 2-5 триггер 6, элемент 2И-ИЛИ-НЕ 7, эле1мент И 8, элемент И-НЕ 9, входную

шину 10, шину сброса 11, шину тактовых импульсов 12, выходную шину 13 и шину контрольного сигнала 14.

Единичный и нулевой выходы триггера 2 соединены с первыми I- и К-входами. триггера 3, выходы триггера 3 с входами триггера 4, выходы триггера k - с входами триггера 5. выходы триггера 5 с входами триггера 2. Вторые 1-Еходы триггеров 2-5 соединены с шиной 10, а вторые К-входы - с шиной ТЗ и с выходом элемента И 8. Единичные выходы триггеров 2 и 3 соединены с входами первого элемента И элемента 2И-ИЛИ-НЕ 7. выходы триггеровЗ и4 -с входами второго, выходы триггеров и5 -с входами третьего, а выходы триггеров 5 и 2 - с входами четвертого элементов И элемента 7.

Выход элемента 7 соединен с D-BXOдом триггера 6, а шина 12 - с С-входом триггера 6 и входом элемента И 8. Единичный выход триггера 6 соединенс вторым входом элемента И 8, а единичные выходы триггеров 2-5 соединены с входами элемента И-НЕ 9. выход которого подключен к шине l4 и к третьему входу элемента И 8. Шина П соединена с S-входом триггера 2 и с R-входами триггеров ЗЗ, а также с S-входом триггера 6.

Устройство работает следующим обра зЬм.

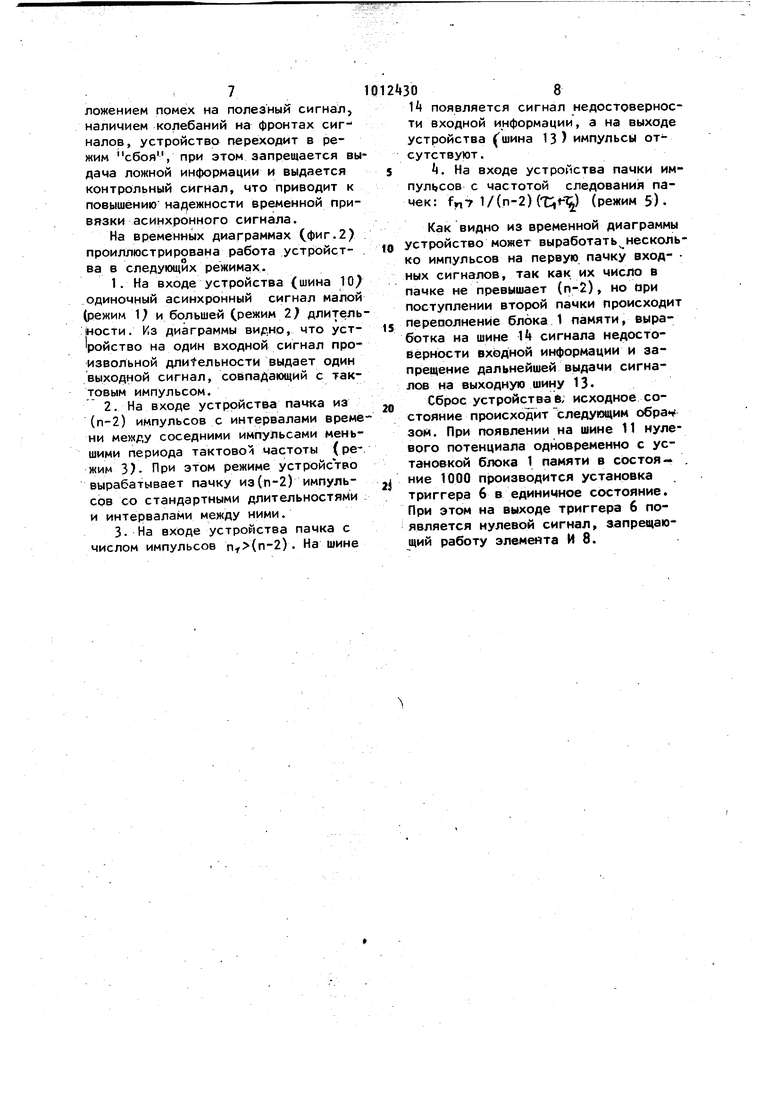

В исходном состоянии, при отсутствии сигнала на шине 10, один из триггеров 2-5 находится в единичном состоянии, а остальные - в нулевом. Это состояние является устойчивым.Триггер 6 находится в состоянии 1, так как на его О-вход поступает единичный сигнал с выхода элемента 2И-ИЛИ-НЕ 7. На шинах 11 и 1 единичный сигнал, на шине 13 - нулевой, на шине 12 - тактовые импульсы с длительностью импульса и длительностью паузыТГ Пусть в единичном состоянии находится триггер 2, а триггеры в нулевом. Входной сигнал на шине 10 устанавливает триггер 3, разрешенный по первому входу I сигналом с три1 гера 2, в единичное состояние, состояние остальных триггеров блока памяти не меняется, так как сигнал на выходе триггера 3 появляется с задержкой на длительность входного сигнала. Едининные сигналы с двух соседних триггеров 2 и 3 поступают на входы первого элемента И элемента 2И-ИЛИ-НЕ 7, на выходе которого появляется нулевой сигнал, который в течение пауз тактового сигнала записывается в триггер 6. Сигнал с инверсного выхода триггера 6 разрешает работу элемента И 8, который пропускает тактовый импульс с шины 12 на выходную шину 13 устройства и на сброс триггера 2. Состояние триггеров ЗЗ не меняется. При поступлении следующего входного сигнала работа устрой ства аналогична описанной выше, но вместо триггеров 2 и 3 срабатывают триггеры 3 и 4. , „ . , Рассмотрим работу устройства, когда входной сигнал представляет со бой пачку импульсов, при этом интервалы времени между соседними импульсами значительно меньше периода тактового сигнала, а число импульсов не превышает (п-2), в данном случае двух. Пусть исходное состояние блока 1 памяти 1000. Два входных сигнала, следующих на малом отрезке времени, переключают блок памяти в состояние 1110, при этом на выходе элемента 2И-ИЛИ-НЕ 7 появляется нулевой сигнал, который записывается в триггер 6. Очередной тактовый импульс проходит через элемент 8 на выходную шину 13 и на сброс триггера 2. Однако на выходе элемента 7 по-прежнему сохраняется сигнал О, так как состояние блока 1 памяти О МО. Триггер 6 остается в нулевом состоянии, и вт рой тактовый импульс с шины 12 поступает на выходную шину 13 устройства и на сброс триггера 3- При состоянии блока 1 памяти 0010 на выходе элемента 7 появляется единичный сигнал, который записывается в триггер 6. Дальнейшее прохождение тактов.ых импульсов через элемент 8 запрещается. Устройство переходит в устой состояние. Устройство выдает на выходную шин входную информацию с п ривязкой к так товой частоте при выполнении следующих требований к входному сигналу: число импульсов в пачке п(п-2); частота следования пачек (n-2) длительности и паузы импуль сов в пачке, ограничены лишь временем срабатывания триггеров блока 1 памяти и не зависят от параметров тактового сигнала. Рассмотрим работу устройства при невыполнении перечисленных выше требований к входному сигналу. Пусть при исходном состоянии блока 1 памяти 1000 на шине 10 появляется пачка из трех импульсов. Триггеры устанавливаются поочередно в единичные состояние, а триггер 2 за это время не успевает сброситься в нулевое состояние, так как длительность пачки импульсов меньше периода тактовой частоты. Блок памяти переходит в состояние 1111, при этом на выходе элемента 9 появляется сигнал О, блокирующий элемент 8. Таким образом выход устройства оказывается отключенным, а на шине 14 появившийся нулевой сигнал служит признаком недостоверности входной информации. Состояние блока 1 памяти 1111 устойчивое, так как входы К всех триггеров блокированы нулевыми сигналами с предыдущих разрядов блока памяти. Переход устройства в рабочее состояние производится сигналом с шины 11, который выдается оператором, либо вырабатывается внешними устройствами после появления нулевого сигнала на шине Ik. Если не выполняется второе требование к входному сигналу, то устрой™ ство не успеет установиться в исходное состояние до прихода следующей пачки и происходит переполнение блока памяти, т.е. переход его в состояние 1111. Состояние блока 1 памяти 0000, которое также является устойчивым может использоваться в режиме запрета выдачи выходной информации, так как в этом случае триггер 6 находится в единичном состоянии и импульсы на выход не поступают, хотя на входной шине 10 они могут присутствовать. Вывод устройства в рабочее . состояние осуществляется сигналом сброса с шины 11. При известном максимальном числе полезных сигналов в пачке в известной максимальной частоте пачек параметры п, ТГ -иТГ-г следует подобрать так, чтобы выполнять требования 1 и 2. При этом устройство будет настроено на надежный прием полезных сигналов, а при появлении ложных сигналов, что может быть вызывано неис правностью передающего канала, на

ложением помех на полезный сигнал, наличием колебаний на фронтах сигналов , устройство переходит в режим сбоя, при этом запрещается вы дача ложной информации и выдается контрольный сигнал, что приводит к повышению надежности временной привязки асинхронного сигнала.

На временных диаграммах (фиг.2) проиллюстрирована работа устройства в следующих режимах.

1 появляется сигнал недостоверности входной информации, а на выходе устройства (шина 13) импульсы отсутствуют.

Как видно из временной диаграммы to устройство может выработать несколько импульсов на первую пачку вход- ных сигналов, так как. их число в пачке не превышает (п-2), но ари поступлении второй пачки происходит ,5 переполнение блока 1 памяти, выработка на шине И сигнала недостоверности входной информации и запрещение дальнейшей выдачи сигналов на выходную шину 13.

Сброс устройства в; исходное состояние происходит следующим зом. При появлении на шине 11 нулевого потенциала одновременно с установкой блока 1 памяти в состоя . ние 1000 производится установка триггера 6 в единичное состояние. При этом на выходе триггера 6 появляется нулевой сигнал, запрещающий работу элемента И 8.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для временной привязки асинхронного импульса | 1977 |

|

SU635610A1 |

Авторы

Даты

1983-04-15—Публикация

1981-10-28—Подача