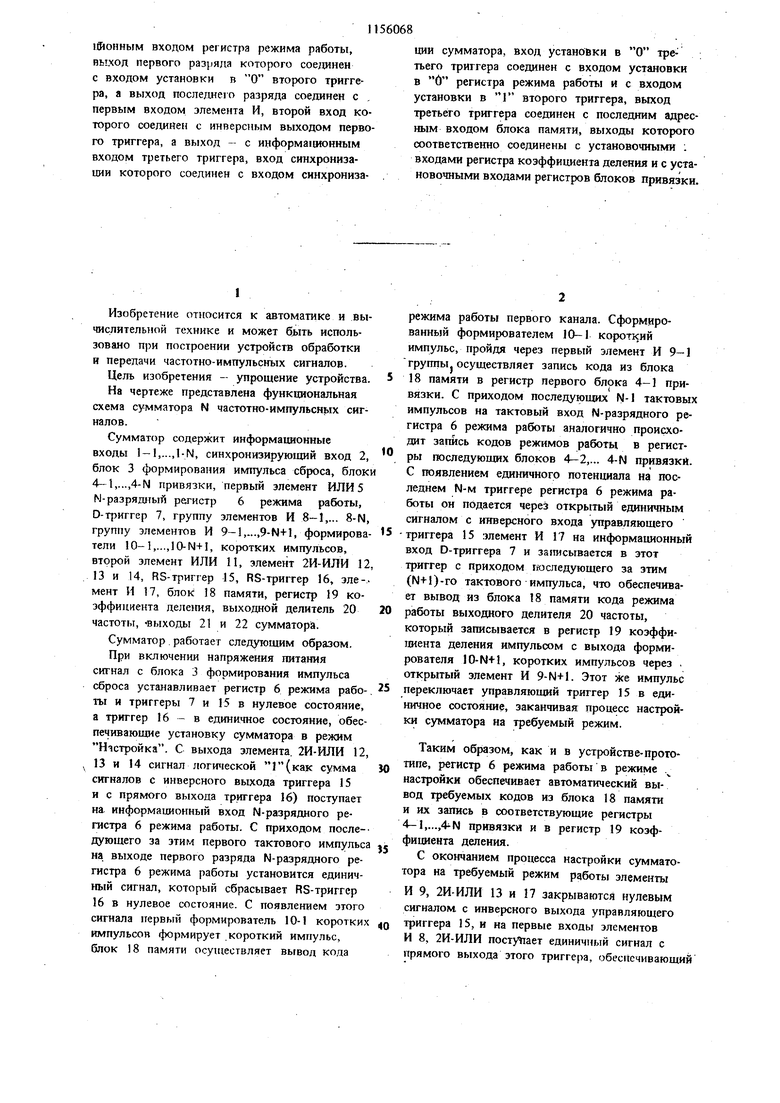

iffioHHbiM входом регистра режима работы, выход первого разряда которого соединен с входом установки в О второго триггера, а выход последае1о разряда соединен с , первым входом элемента И, второй вход которого соединен с инверсным выходом первого триггера, а выход - с информационным входом третьего триггера, вход синхронизации которого соединен с входом синхронизации сумматора, вход установки в О третьего триггера соединен с входом установки в U регистра режима работы и с входом установки в 1 второго триггера, выход третьего триггера соединен с последним адресным входом блока памяти, выходы которого соответственно соединены с установочными : входами регистра коэффициента деления и с установочными входами регистров блоков привязки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство задержки импульсов | 1980 |

|

SU869005A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Цифровой имитатор радиотелеграфного канала связи | 1985 |

|

SU1275465A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство программного управления антенной | 1988 |

|

SU1594487A1 |

| Устройство привязи к сигналам точного времени | 1987 |

|

SU1522146A1 |

| Устройство для контроля динамических параметров аналого-цифровых преобразователей | 1987 |

|

SU1474839A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2270527C1 |

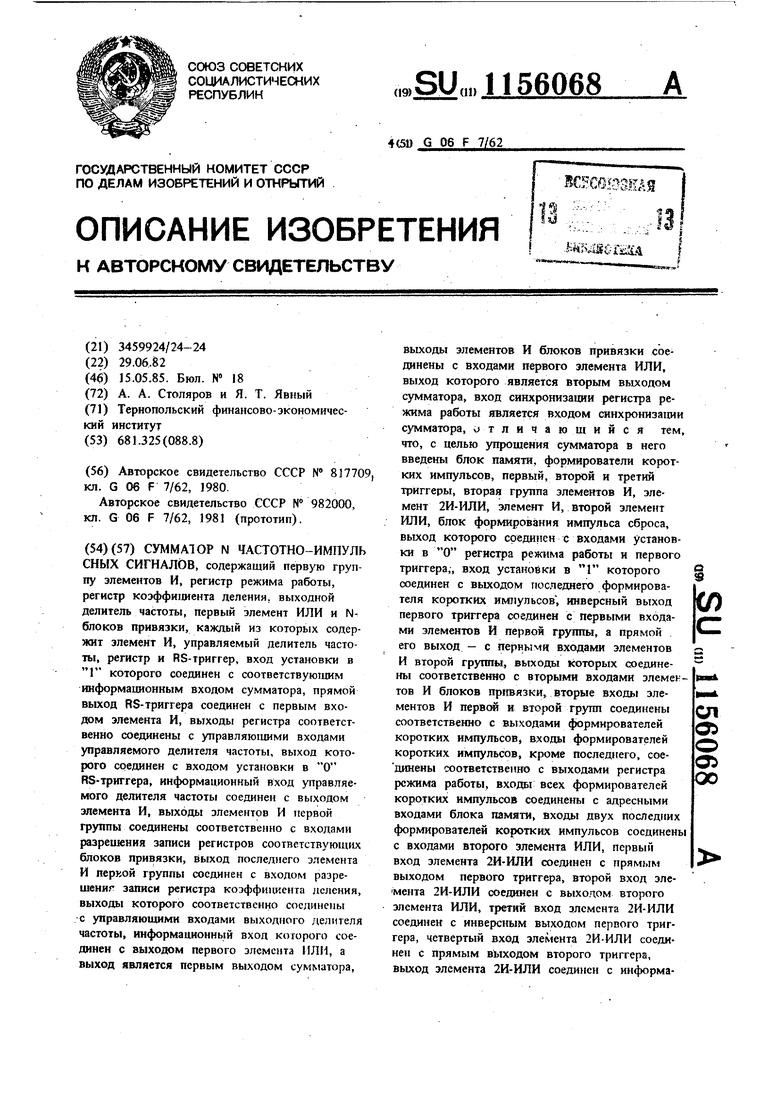

СУМММОР N ЧАСТОТНО-ИМПУЛЬ CHbfX СИГНАЛОВ, содержащий первую группу элементов И, регистр режима работы, регистр коэффициента деления, выходной делитель частоты, первый элемент ИЛИ и Nблоков привязки, каждый из которых содержит элемент И, управляемый делитель частоты, регистр и RS-триггер, вход установки в 1 которого соединен с соответствующим информационным входом сумматора, прямой выход RS-триггера соединен с первым входом элемента И, выходы регистра соответственно соединены с управляющими входами управляемого делителя частоты, выход которого соединен с входом установки в О RS-трштера, информационный вход управляемого делителя частоты соединен с вьгходом элемента И, выходы элементов И нервой грутты соединены соответственно с входами разрешения записи регистров соответствующих блоков привязки, выход последнего элемента И перкой группы соединен с входом раэрешениг записи регистра коэффициента деления, выходы которого соответственно соединены с управляющими входами выходного делителя частоты, информационный вход которого соединен с выходом первого элемента ПЛИ, а выход является первым выходом сумматора. выходы элементов И блоков привязки соединены с входами первого элемента ИЛИ, выход которого является вторым выходом сумматора, вход синхронизации регистра режима работы является входом синхронизации сумматора, ч тличающийся тем, что, с целью упрощения сумматора в него введены блок памяти, формирователи коротких импульсов, первый, второй и третий триггеры, вторая группа элементов И, элемент 2И-ИЛИ, элемйгг И, второй элемент ИЛИ, блок форкшровзния импульса сброса, выход которого среди11ен с входами установки в О регистра режима работы и первого триггера,, вход установки в 1 которого соединен с выходом последнего формирова(Л теля коротких импульсов , инверсный выход первого триггера соединен с первыми входами элементов И первой группы, а прямой . его выход - с nepHbiMH входами элементов И второй грутшы, выходы которых соединены соответственно с вторыми входами элементов И блоков привязки, вторые входы элементов И первш и второй групп соединены ел соответственно с выходами формирователей О5 коротких импульсов, входы формирователей о коротких импульсов, кроме последнего, соеGb динены соответственно с выходами регистра Оо режима работы, входы всех формирователей коротких импульсов соединены с адресными входами блока памяти, входы двух последних формирователей коротких импульсов соединены с входами второго элемента ИЛИ, первый вход элемента 2И-Ш1И соединен с прямым выходом первого триггера, второй вход элемента 2И-ИЛИ соединен с выходом второго элемента ИЛИ, третий вход элемента 2И-ИЛИ соединен с инве{кным выходом первого триггера, четвертый вход элемента 2И-ИЛИ соединен с прямым выходом второго триггера, выход элемента 2И-ИЛИ соединен с информа

I

Изобретение относится к автоматике и вычислительж1Й технике и может использовано П1)и построении устройств обработки и передачи частотно-импульсных сигналов.

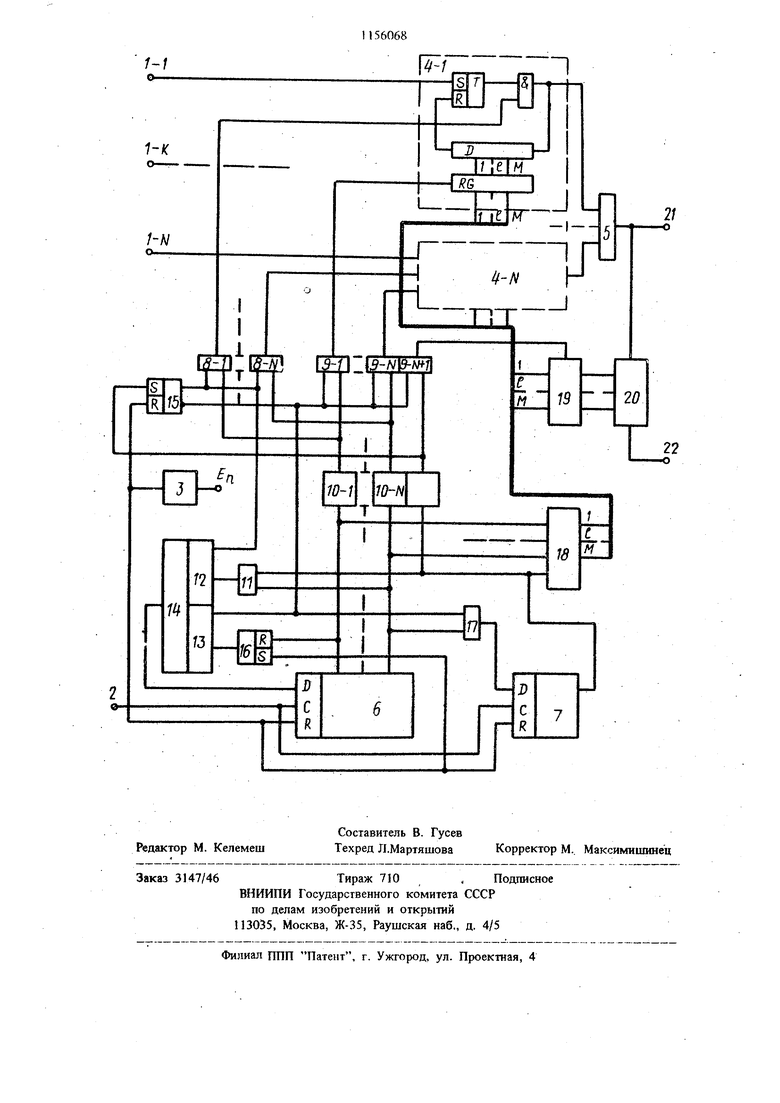

Цель изобретения -- упрощение устройства. На чертеже представлена функциональная схема сумматора N частотно-импульснь1х сигналов.

Сумматор содержит информационные входы 1-1,...,1-N, синхронизирующий вход 2, блок 3 формирования импульса сброса, блоки 4-l,...,4-N привязки, первый элемент ИЛИ5 N-разрядный регистр 6 режима работы, О-триггер 7, группу элементов И 8-1,... 8-N, группу элементов И 9-1,...,9-N+1, формирователи 10-1,...,10-N+I, коротких Импульсов, второй элемент ИЛИ 11, элемент 2И-ИЛИ 12, 13 и 14, RS-триггер 15, RS-триггер 16, эле-, мент И 17, блок 18 памяти, регистр 19 коэффициента деления, выходной делитель 20 частот., -выходы 21 и 22 сумматора. Сумматор. работает следующим образом. При включении напряжения питания сигнал с блока 3 формирования импульса сброса устанавливает регистр 6 режима рабо-. 1Ъ1 и триггеры 7 и 15 в нулевое состояние, а триггер 16 - в единичное состояние, обеспечивающие установку сумматора в режим Нчстройка. С выхода элемента. 2И-ИЛИ 12, 13 и 14 сигнал логической 1(как сумма сигналов с инверсного выхода триггера 15 и с прямого выхода триггера 16) поступает на информационный вход N-разрядного регистра 6 режима работы. С приходом после-дующего за этим первого тактового импульса на выходе первого разряда N-разрядного регистра 6 режима работы установится единичный сигнал, который сбрасывает RS-триггер 16 в нулевое состояние. С появлением этого сигнала первый формирователь 10-1 коротких импульсов формирует короткий импульс, блок 18 памяти осуществляет вывод кода

режима работы первого канала. Сформированный формирователем 10-1 короткий импульс, пройдя через первый элемент И 9-1 группыJ осуществляет запись кода из блока 18 памяти в регистр первого блока 4-1 привязки. С приходом последующих N-1 тактовы импульсов на тактовый вход N-разрядного регистра 6 режима работы аналогично проирсодит запись кодов режимов работы в регистры последующих блоков 4-2,... 4-N привязки С появлением единичного потенциала на последнем N-M триггере регистра 6 режима работы он подается через открытый единичным сигналом с инверсного входа управляющего триггера 15 элемент И 17 на информационны вход D-триггера 7 и за тисывается в этот триггер с приходом гюследующего за этим (N+l)-ro тактового импульса, что обеспечивает вывод из блока 18 памяти кода режима работы выходного делителя 20 частоты, который записывается в регистр 19 коэффициента деления импульсом с выхода формирователя 10-N+1, коротких импульсов через . открытый элемент И 9-N+1. Этот же импульс переключает управляющий триггер 15 в единичное состояние, заканчивая процесс настройки сумматора на требуемый режим.

Таким образом, как и в устройств е-прототипе, регистр 6 режима работы в режиме . настройки обеспечивает автоматический вывод требуемых кодов из блока 18 памяти и их запись в соответствующие регистры 4-1,..., привязки и в регистр 19 коэффициента деления.

С окончанием процесса настройки сумматотора на требуемый режим работы элементы И 9, 2И-ИЛИ 13 и 17 закрываются нулевым сигналом с инверсного выхода управляющего триггера 15, и на первые входы элементов И 8, 2И-ИЛИ постучпает единичный сигнал с прямого выхода этого триггера, обеспечивающ установку сумматора в режим. Работа. На вход элемента ИЛИ 11 поступает нулевой сиг нал с N-ro выхода регистра 6 режима работы и единичный сигнал с выхода О-триггера 7, поэтому сумма единичных сигналов с прямого выхода управляющею триггера 15 и с выхода второго элемента ИЛИ 11 череэ элемент 2И-ИЛИ 12, 13 и 14 поступает на информационный вход регистра 6 режима работы. С приходом первого эа этим моментом тактово го импульса происходит запись логической Г в первый разряд регистра 6 режима рабо ты, а О-триггер 7 устанавливается в нулевое состояние, обеспечивая через элементы ИЛИ 11 и2И-ИЛИ 12, 13 и 14 установку логического О на информационном входе регистра 6 режима работы. С приходом последующих тактовых импульсов происходит сдвиг записанной в первый разряд регистра 6 режимов работы логической 1 вплоть до ее появления на N-триггере регистра 6 режимов работы, что вьрывает появление этого же сигнала на его информационном входе через элементы ИЛИ 1 и 2И-ИЛИ 12, 13 и 14. В дальнейщем процесс повторяется, причем с каждым тактовым импульсом логическая 1 возникает на одном и N-триггеров регистра 6 режима работы, т.е. он работает как N-разрядный регистр сдвига логической 1. Формирователи 10-1,...,10-N+ коротких импульсов выделяют короткий импульс из каждого положительного перепада и (так как регистр 6 режима работы работает, как кольцевой регистр сдвига логической 1 их выходные импульсы не совпадают во време а часть этих импульсов определяется вьгражени (f) 1 14 где f. - частота повторения импульсов на выходе i-ro формирователя коротких импульсов i 1-N; f - частота повторения тактовых сигналов ; N - число разрядов регистра 6 режима работы или суммируемых сигналов, Из этого следует, что в режиме Работа регистр 6 режима работы обеспечивает подачу на синхронизирующие входы блоков 4-l,...,4-N привязки не совпадающих во времени коротких импульсов с одинаковыми частотами (1). т.е. выполняет функции многофазного генератора коротких импульсов, имеющегося в известном устройстве, выбранном в качестве прототипа. Суммирование N частот осуществляется как и в устройстве-прототипе путем привязки импульсов каждой нз входных последовательностей, поступающих с входов 1 -,...,-N сумматора на информационные входы блоков 4-l,...,4-N привязки, к несовпадающим во вре-мени импульсам с (J), подаваемым на синхронизующие входы блоков 4-1,..,,4-N привязки. При этом должно соблюдаться условие fi-fn,/ где fgj( . - частота повторения входаого сигнала на i-M входе. На выходах блоков привязки вьзделяются не совпадающие во времени пачки коротких импульсов, число которых может изменяться в пределах от 1 до к , где к „„, - мак ПТОГХт X симальныи коэффициент деления -делителя частоты, входящих в состав блоков 4-l,...,4-N привязки, причем пропорциональный коду, записанному в регистры блоков 4-1,...,4-N привязки. Частота повторения пачек импульсов равна частотам входных сигналов fg.;. Полученные не совпадающие во времени пачки коротких импульсов просуммируются элементом ИЛИ 5, что обеспечивает получение неравномерной последовательности импульсов на выходе 21, средняя частота которых равна fcp k,f, -н k, ... + (3) где k ,..., коэффициенты деления соответствующих делителей частоты блоков 4-1 4-N привязки;f -, частоты входных сигналов. Равномерные импульсы на выходе 22 получают с частотой k,....fe,f. где k - коэффициент выходного делителя частоты. Таким образом, предлагаемый сумматор выполняет, функции устройства-прототипа, так как производит автоматическую настройку требуемого режима работы при включении напряжения питания в режиме Настройка и подачу не совпадающих во времени последоательностей коротких импульсов на синхронизирующие входы блоков привязки в ре- ; жиме Работа(1)/ что обеспечивает выполнение функций пропорционального и непроорционального суммирования частот входных мпульсов последовательностей в соответстии с выражениями (3) и (4). При этом алгоитм управления предлагаемого -сумматора прощен, так как для его управления требуетя лищь один сигнал - тактовый, подаваемый а вход 2. Кроме того, предлагаемое устройтво проще устройства-прототипа, так как ля его реализации требуется лишь один реистр сдвига.

/-f

о-

/-Л/ о

П

ff

Г

1/.еГМ

J

J

2/

пгтг

-пп

А/Н

.J

тлт

га

/5

R

20

75

«

10-N

4J

п

п

гз

| -Канальное устройство дляСуММиРОВАНия чАСТОТ | 1979 |

|

SU817709A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| N-канальное устройство суммирования | 1981 |

|

SU982000A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1982-06-29—Подача