Изобретение относится к устройствам управления и может применяться в системах автоматизации технологическим оборудованием.

Известно устройство, содержащее входной блок, блок коммутации, подключенный выходом к вычислительному блоку, выход которого связан с блоком оперативной памяти и выходным блоком, программный блок, выходы которого подключены через командные и адресные шины к входам всех перечисленных выше блоков, генератор импульсов (авт.св. N 1652964, кл. G 05 B 19/08, 1991).

Недостатком данного устройством является сложность коммутационного и вычислительного блоков.

Наиболее близким по технической сущности является устройство, содержащее входной и выходной блоки, блоки оперативной памяти и синхронизации, адресные шины, генератор импульсов, программный блок, блок коммутации и вычисления, состоящий из трехвходового дешифратора, двухвходовых элементов И, элементов ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и управляемой ячейки памяти, командные шины, соединяющие программный блок с соответствующими входами трехвходового дешифратора, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и ячейки памяти (заявка СССР N 4860077/24 от 15.08.90, положительное решение от 30.08.91, патент СССР N 1801223, кл. G 05 B 19/08, 1992).

К недостаткам этого устройства можно отнести относительно низкое быстродействие.

Целью изобретения является повышение быстродействия устройства.

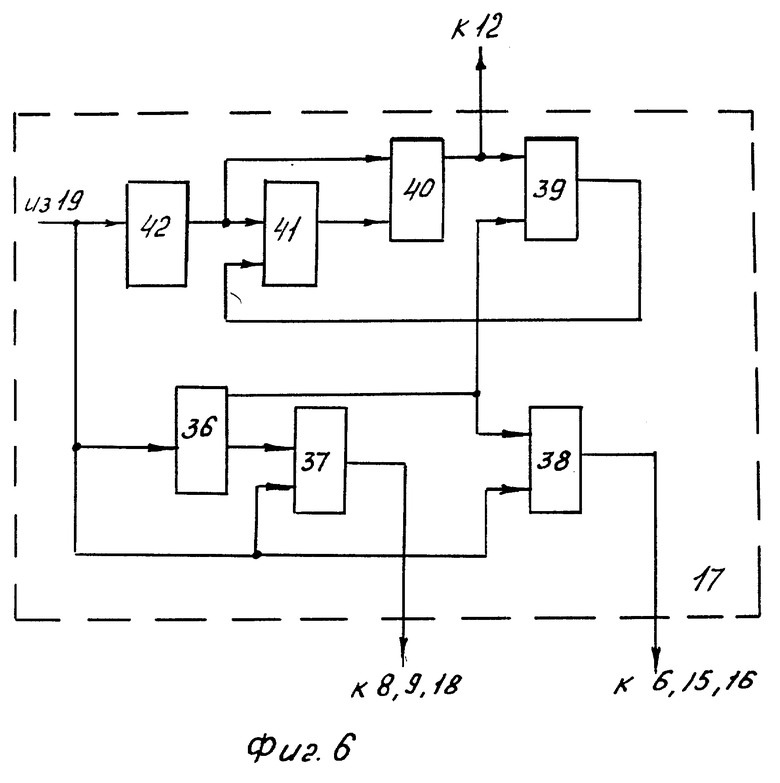

На фиг.1 представлена схема программируемого устройства.

Программируемое устройство состоит из входного блока 1, входы которого подключены к адресным шинам и первичным датчикам, с которых поступают сигналы X1 Xn, а выход связан с коммутационно-вычислительным блоком (далее БКВ)2, содержащим дешифратор 3, связанный входами с командными шинами, а двумя выходами соответственно с входами элемента 2-2И-2ИЛИ 4, выход которого через первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и элемент И 6 подключен к первому входу первой управляемой ячейки памяти 7, второй и третий входы которой соединены с трехвходовыми элементами 8 и 9, а выход с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, выход которого через элементы ИЛИ 11 и И 12 подключен к информационному входу второй управляемой ячейки памяти 13, управляющий вход которой соединен с выходом элемента НЕ 14, а выход с соответствующими входами выходного блока 15 и блока оперативной памяти 16, своим входом связанного с блоком синхронизации 17, выход которого подключен к выходу программного блока 18, а вход к генератору импульсов 19.

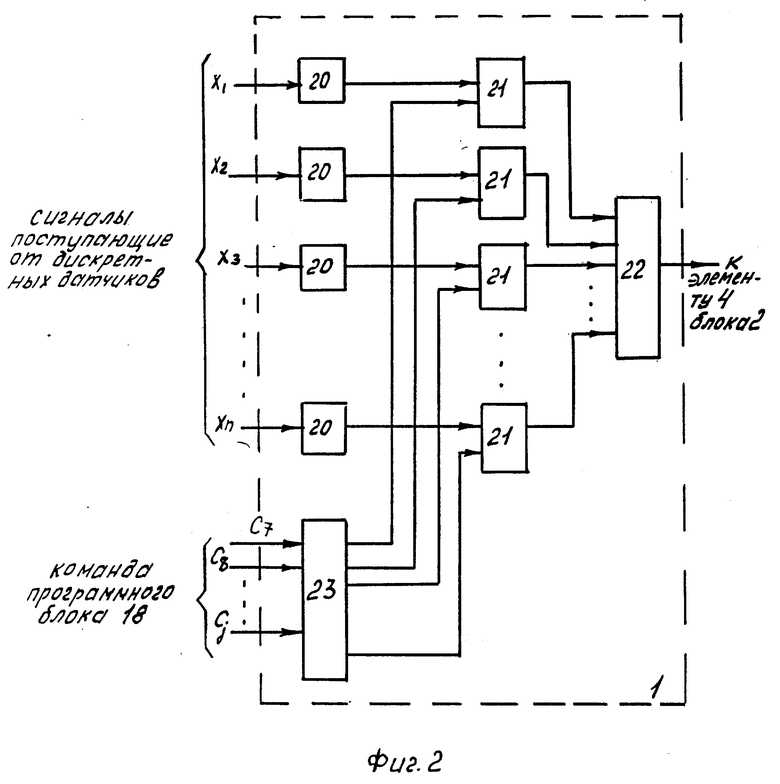

На фиг.2 представлен входной блок 1 известной конструкции. Он состоит из элементов согласования 20, в качестве которых могут быть и аналоговые нуль-органы, на входы которых поступают двоичные сигналы от дискретных датчиков X1 X или соответствующие аналоговые сигналы в случае нуль-органов, а с выхода снимаются унифицированные сигналы, соответствующие логическим сигналам "0" и "1", элементов считывания 21, в качестве которых можно использовать двухвходовые элементы И, связанного с ними элемента ИЛИ 22 и дешифратора 23, управляющего элементами 21 по адресным командам C7 Cj из программного блока.

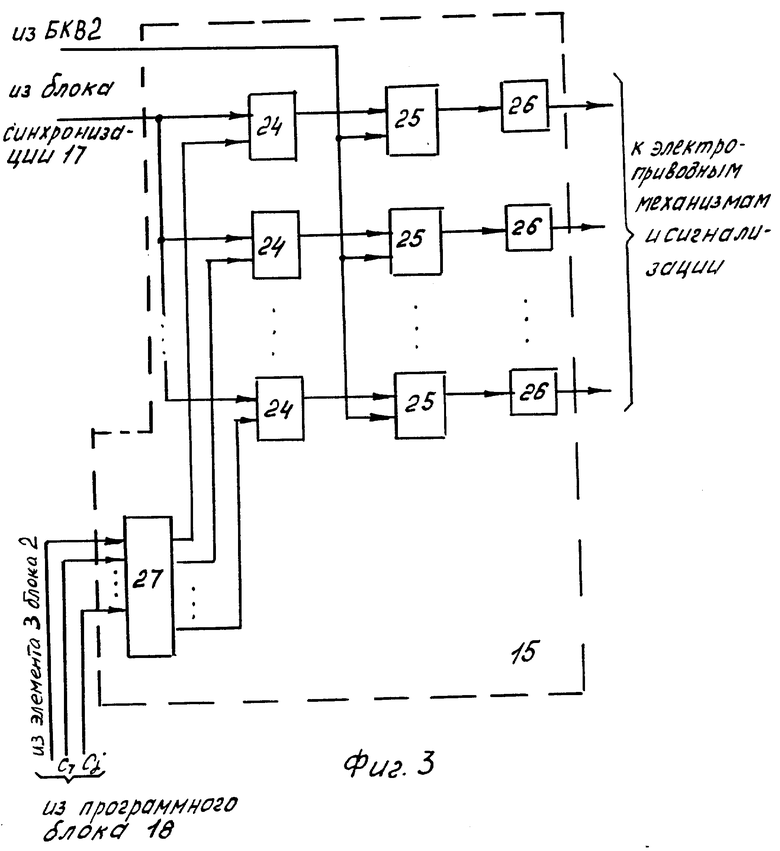

На фиг. 3 представлен выходной блок 15, который состоит из элементов И 24, стандартных ячеек памяти (триггеров) 25, куда заносится информация из блока БКВ 2 и соответствующих усилителей 26, передающих логические сигналы из ячеек памяти на электроприводные механизмы или световую индикацию, по адресным и управляющим командам из программного блока 18 и БКВ 2, поступающих на дешифратор 27.

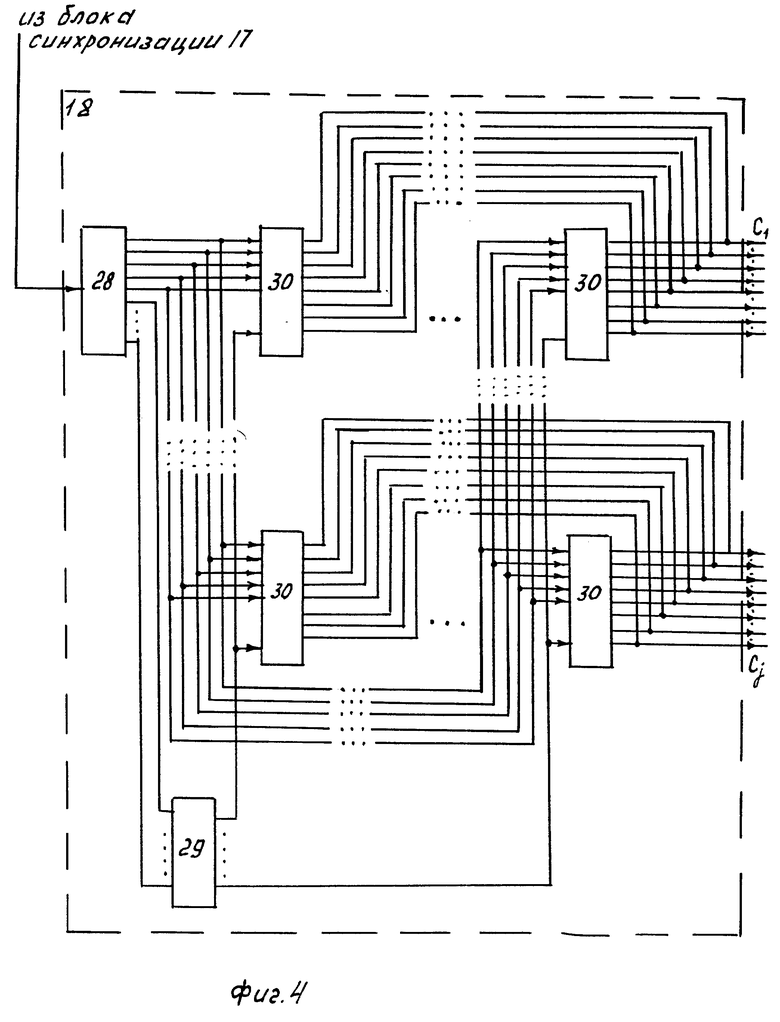

На фиг.4 в качестве примера изображена функциональная схема программного блока 18 известной конструкции. Программный блок 18 (фиг.4) состоит из стандартных элементов: счетчика импульсов 28, дешифратора 29, распределяющего импульсы во времени и по направлению, двойной матрицы с горизонтальными и командными шинами, диодов и инверторов (не показаны) или как в примере на фиг. 4 стандартных ППЗУ 30, выполненных, например, на микросхемах серии 155РЕЗ, К573РФ1 и так далее, в которых записана программа работы всего устройства.

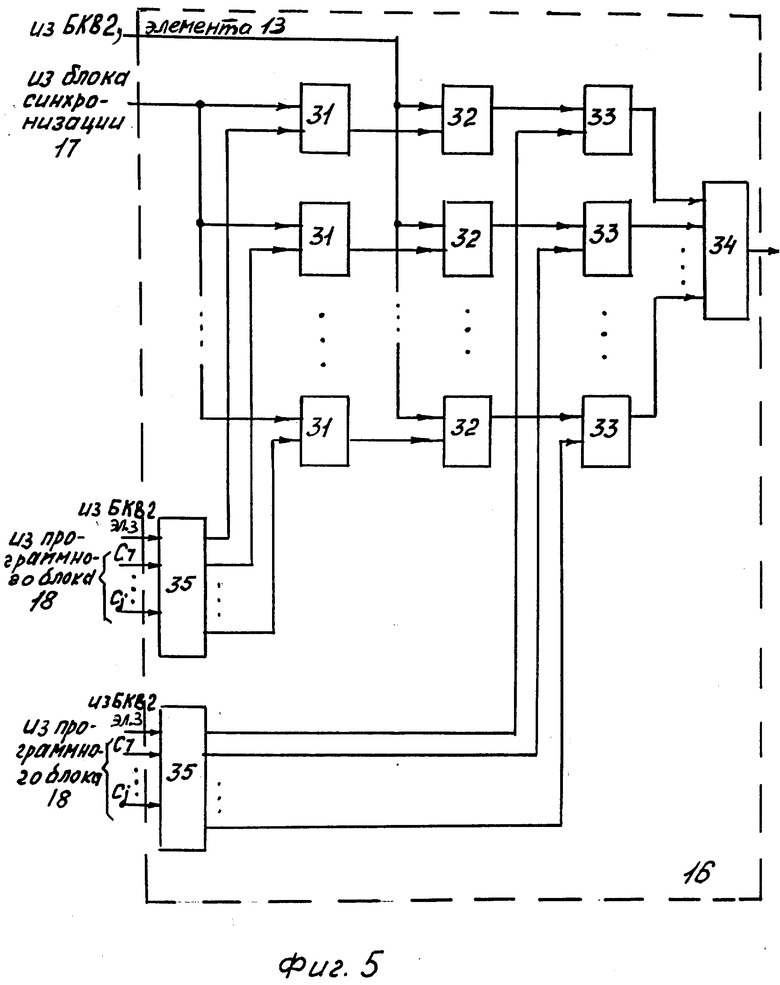

Блок оперативной памяти 16, который состоит из ячеек памяти, элементов записи и считывания и в качестве которого могут быть использованы стандартные ОЗУ (оперативные запоминающие устройства) или как в примере, приведенном на фиг.5, блок оперативной памяти содержит элементы 31 обращения к ячейкам памяти, в качестве которых могут быть использованы элементы И, ячейки памяти 32, элементы считывания 33, в качестве которых могут быть использованы элементы И, элемент ИЛИ 34 и первый и второй дешифраторы 35. По командам, поступающим из БКВ 2 и программного блока 18, первый дешифратор 35 через соответствующий элемент 31 заносит в соответствующую ячейку памяти информацию, поступающую из БКВ 2, а второй дешифратор 35 по командам из БКВ 2 и программного блока 18 считывает информацию через элемент считывания 33 из соответствующей ячейки 32, которая через элемент ИЛИ 34 поступает на вход БКВ 2.

В качестве ячеек памяти 7 и 13 (фиг.1) можно использовать стандартный двухтактный D-триггер, например, типа К17ТМ2 с входами сброса в "0" или "1", при этом на тактовый вход С подается сигнал с выхода элемента И 6 и И 12, а на D вход подается информационный сигнал C5 или  из программного блока 18. Перед работой триггеры устанавливаются в исходное, например, единичное (нулевое) состояние путем подачи соответствующих сигналов на установочные входы сброса в "0" или "1".

из программного блока 18. Перед работой триггеры устанавливаются в исходное, например, единичное (нулевое) состояние путем подачи соответствующих сигналов на установочные входы сброса в "0" или "1".

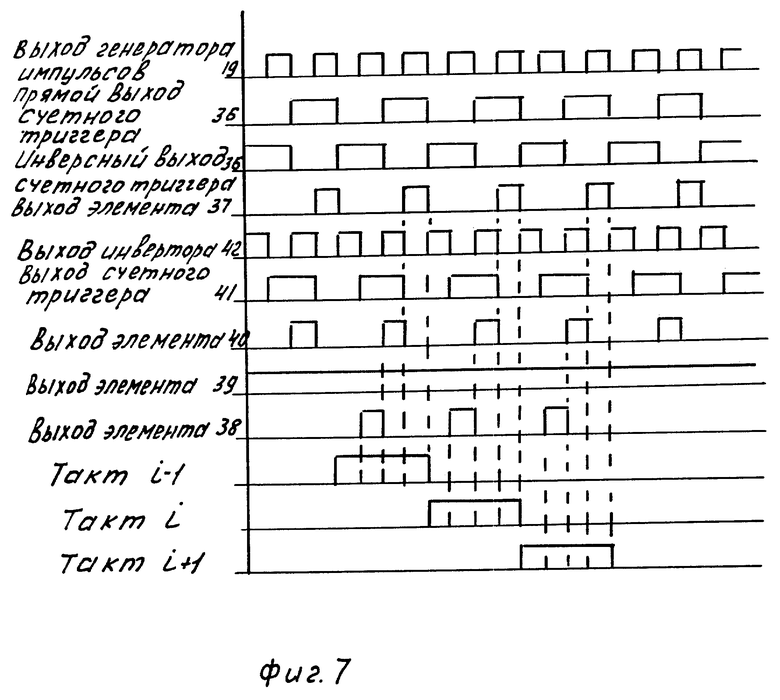

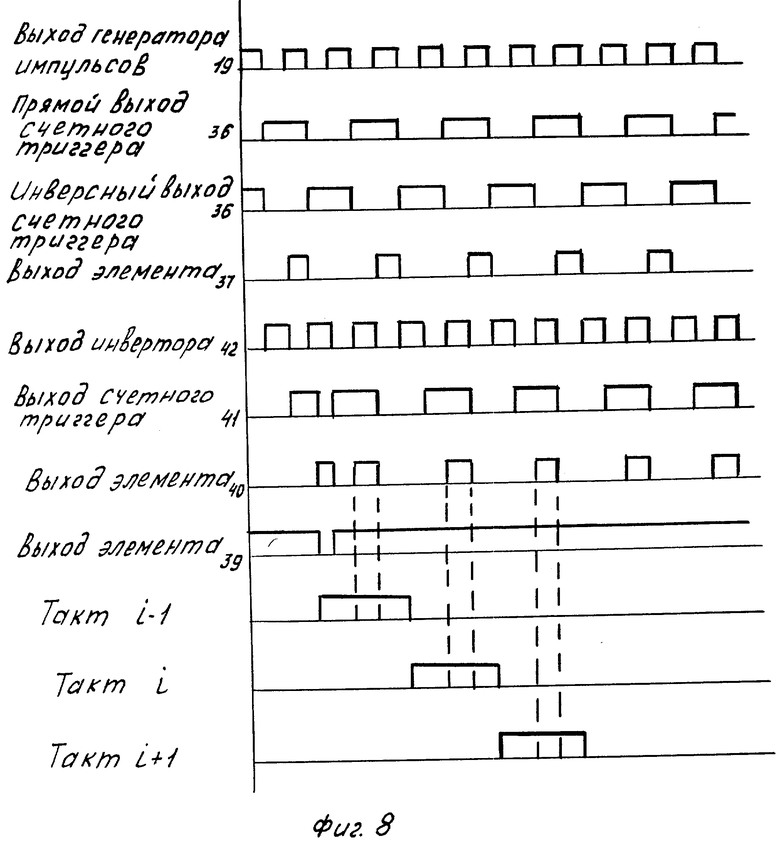

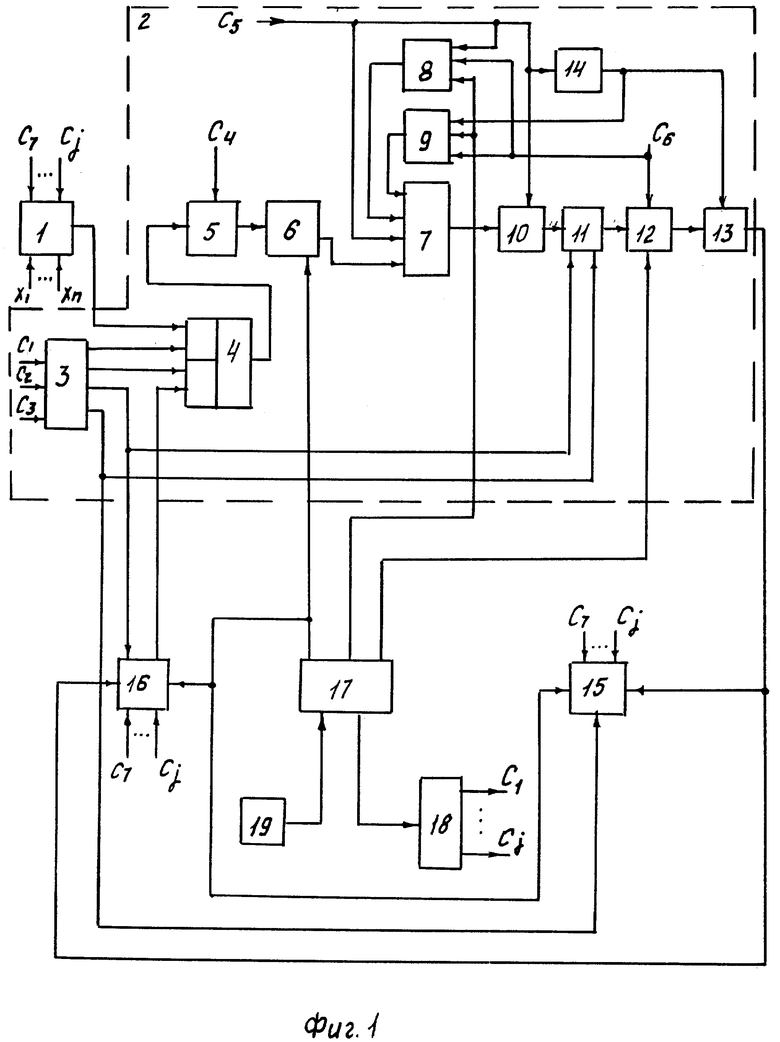

Надо также учесть, что выход элемента И 38 в блоке синхронизации 17 (фиг. 6) соединен с элементом И 6 (фиг.1), с блоками выходным 15 и оперативной памяти 16 и обеспечивает запись информации в ячейки памяти всех блоков и ячейку памяти 7 (фиг.1) во второй четверти такта, выход элемента 40 обеспечивает запись информации в ячейку памяти 13 (фиг.1) в третьей четверти такта, что следует из приведенных диаграмм работы блока синхронизации 17 на фиг.7, где четверти обозначены через а, б, в, г. Это позволяет на одном такте вначале (во второй четверти такта) записывать информацию из ячейки памяти 13 в блоки 15 и 16 и ячейку памяти 7, а затем записывать информацию в триггер 13 в третьей четверти такта и сбрасывать триггер 7 в "0" или "1" в четвертой четверти такта. Работа блока синхронизации аналогична его работе в прототипе. Генератор импульсов 19 формирует непрерывную последовательность импульсов, которые поступают на вход, счетного триггера 36. С прямого выхода счетного триггера 36 импульсы поступают на вход элемента И 37, который по их совпадению с импульсами генератора импульсов 19 выдает тактовые импульсы, поступающие на вход программного блока 18, который на основе этих тактовых импульсов формирует команды управления и к элементам 8 и 9 блока БКВ 2. Причем в результате возможного сбоя синхроимпульса относительно тактового импульса элемент И-НЕ 39 сформирует импульс сброса, который обнулит счетный триггер 41, связанного счетным входом с элементом НЕ 42 и положение синхроимпульса восстановится (диаграмма на фиг.8).

Все счетные триггеры срабатывают по заднему фронту импульсов. Стрелками, направленными к элементам и блокам, помечены входы всех элементов и блоков.

C1 C6 командные сигналы, управляющие работой блока БКВ 2.

C7 Cj адресные командные сигналы, определяющие необходимую ячейку памяти в блоках 15 и 16 или определенный вход в блоке 1.

Принцип работы предлагаемого устройства покажем на примере вычисления фрагмента логической функции  содержащего функционально полный набор булевых функций, т.е. И, НЕ, ИЛИ. Причем переменная X4 была записана ранее в ячейку памяти блока 16.

содержащего функционально полный набор булевых функций, т.е. И, НЕ, ИЛИ. Причем переменная X4 была записана ранее в ячейку памяти блока 16.

Перед началом работы триггер 7 устанавливается в единичное состояние (т. е. на его выходе будет присутствовать логическая "1"), а триггер 13 в нулевое.

Будем считать, что при сочетании командных сигналов C1, C2, C3 на дешифраторе 3 соответственно 100 активизируется первый верхний выход дешифратора 3, при 010 активизируется второй выход, при 110 активизируется третий выход, а при 001 активизируется четвертый нижний выход дешифратора 3. Оговоримся, что запись значения C4 и C5 происходит в триггеры 7 и 13, когда на его управляющем входе находится логическая единица.

На первом такте из программного блока поступают сигналы C1=1, C2=0, C3= 0, C4= 1, C5=0, C6=0. При этом значение X1 из блока 1 поступает на верхний вход элемента 4, инвертируется в элементе 5 и поступает через элемент 6 во второй четверти такта на управляющий вход триггера 7 и, если X1=1, то триггер 7 останется в прежнем состоянии, если X1=0, то триггер 7 перейдет в нулевое состояние, так как C5=0. На следующем (втором) такте во второй его четверти под действием команд C1 C6 (100101) переменная X2 из блока 1, определяемой значениями адресных сигналов (как и в случае X1) C7 Cj, поступит с инверсией на управляемый вход триггера 7, и, если X1=1, триггер 7 не изменит своего единичного или нулевого состояния, а если X2=0 то триггер 7 обязательно окажется в нулевом состоянии. На втором также в третьей его четверти значение функции X1•X2 под действием сигналов C4=0 и C6=1 поступит на управляющий вход триггера 13 и, если X1•X2=1, то триггер 13 перейдет в единичное состояние, так как C5=1. В противном случае триггер 13 останется в нулевом состоянии, одновременно в четвертой четверти такта триггер 7 под действием единичного сигнала с выхода элемента 9 перейдет в состояние "1", если был в состоянии "0".

На третьем такте под действием команд C1 C6 (100000) переменная X3 из блока 1 поступает на управляемый вход триггера 7 и, если X3 0, то триггер 7 останется в состоянии "1", а если X3=1, то триггер 7 перейдет в состояние "0". На четвертом такте под действием команд C1 C6 (010101) переменная X4 из блока 16 появится на входе триггера 7 во второй четверти такта и, если X4=1, то триггер 7 останется в прежнем состоянии, а если X4=0, триггер перейдет в нулевое состояние. В третьей четверти такта под действием команды C6 значение функции X3•X4 появится на управляемом входе триггера 13 и, если оно равно 1, то триггер 13 перейдет (или останется) в состоянии "1", а если  то триггер 13 не изменит своего состояния. Таким образом, на выходе триггера 13 будет присутствовать результат вычисления функции

то триггер 13 не изменит своего состояния. Таким образом, на выходе триггера 13 будет присутствовать результат вычисления функции

На следующем также результат вычисления функции может быть записан в блок оперативной памяти 16 или выходной блок 15 под действием команд C1 C3 110 или 001 соответственно при C6=0.

Таким образом, для вычисления заданной функции предлагаемым устройством понадобилось четыре такта. В устройстве, представленном в прототипе, функция была бы вычислена лишь за восемь тактов. Это объясняется тем, что после вычисления функций X1 • X2 необходимы дополнительные такты для обращения в блок оперативной памяти и для подготовки триггера в блоке БКВ 2 для последующих операций. Естественно, чем длиннее вычисляемая функция, тем эффективнее применение предлагаемого устройства.

Повышение быстродействия устройства позволяет быстрее реагировать на изменение параметров технологического оборудования, что обеспечивает более точное и качественное управление технологическими процессами, алгоритм функционирования которых может быть выражен в функциях алгебры Буля. В этом состоит технико-экономический эффект от применения предлагаемого устройства по сравнению с прототипом.

Изобретение относится к системам программного управления. Цель: повышение быстродействия. Устройство содержит входной блок 1, коммутационно-вычислительный блок 2, в состав которого входят дешифратор 3, элемент 2-2И-2ИЛИ 4, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и 10, элементы И 6, 8, 9 и 12, ячейки памяти (триггеры) 7 и 13, элемент ИЛИ 11, элемент НЕ 14, а также выходной блок 15, блок 16 оперативной памяти, блок 17 синхронизации, программный блок 18, генератор 19 импульсов. Быстродействие устройства повышается за счет сокращения числа тактов при вычислении логических функций. 8 ил.

Программируемое устройство для логического управления электроприводами и сигнализацией, содержащее входной и выходной блоки, блок оперативной памяти, генератор импульсов, подключенный выходом к входу блока синхронизации, коммутационно-вычислительный блок, содержащий трехвходовый дешифратор, соединенный входами с соответствующими адресными командными выходами программного блока, элемент 2 2И 2ИЛИ, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый элемент И и первую управляемую ячейку памяти, первые входы элемента 2 - 2И 2ИЛИ соединены соответственно с первым и вторым выходами дешифратора, вторые входы элемент 2 2И 2ИЛИ подключены соответственно к выходу входного блока, соединенного первой и второй группами входов соответственно с группой информационных входов устройства и соответствующими адресными командными входами программного блока, и к выходу блока оперативной памяти, выход элемента 2 2И 2ИЛИ подключен к первому входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с соответствующим командным выходом программного блока, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом первого элемента И, подключенного вторым входом к первому выходу блока синхронизации, соединенному с первыми управляющими входами блока оперативной памяти и выходного блока, группы адресных входов которых соединены с группой адресных командных выходов программного блока, а информационные входы объединены, выход первого элемента И подключен к управляющему входу первой управляемой ячейки памяти, второй выход блока синхронизации соединен со счетным входом программного блока, третий и четвертый выходы дешифратора соединены соответственно с вторыми управляющими входами блока оперативной памяти и выходного блока, отличающееся тем, что командно-вычислительный блок содержит второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вторую управляемую ячейку памяти, элемент ИЛИ, элемент НЕ и элементы И с второго по четвертый, причем первый вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом первой управляемой ячейки памяти, его второй вход соединен с соответствующим командным выходом программного блока, первым входом второго элемента И, входом данных первой управляемой ячейки памяти и через элемент НЕ с входом данных второй управляемой ячейки памяти и первым входом третьего элемента И, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к первому входу элемента ИЛИ, второй и третий входы которого подключены соответственно к третьему и четвертому выходам дешифратора, выход элемента ИЛИ подключен к первому входу четвертого элемента И, второй вход которого подключен к соответствующему командному выходу программного блока и вторым входам второго и третьего элементов И, третьи входы которых подключены к третьему выходу блока синхронизации, четвертый выход которого соединен с третьим входом четвертого элемента И, выход которого подключен к управляющему входу второй управляемой ячейки памяти, выход которой соединен с объединенными информационными входами блока оперативной памяти и выходного блока, выходы второго и третьего элементов И соединены соответственно с входами сброса в "1" и "0" первой управляемой ячейки памяти.

| SU, авторское свидетельство, 1801223, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1997-11-27—Публикация

1996-03-22—Подача