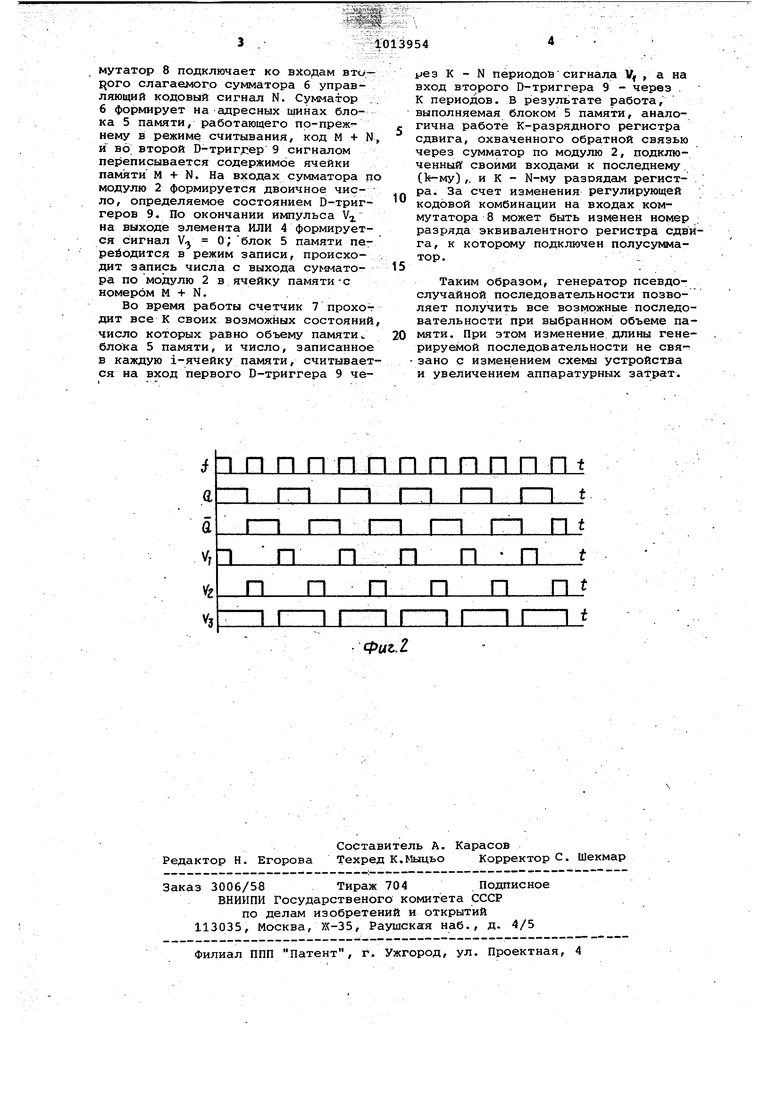

Изобретение относится к вычисли тельной технике и может быть испол зовано для решения вероятностных задач методом моделирования. .Известен .генератор псевдослучай ной последовательности двоичных чисел, содержащий регистр сдвига с сумматором по модулю 2 в цепи обратной связи, генератор тактовых импульсов, выход которого соединен со входом регистра сдвига, а также счетчик и блок сумматоров 11 Недостатком данного устройства является малое значение периода пс дослучайной последовательности, ог- раниченное разрядностью регистра сдвига. Увеличение периода последовательности, за счет разрядности регистра приводит к усложнению схемы и снижению её надежности. Наиболее близким по техническому решению к изобретению является гене ратор псевдослучайной последователь ности, содержащий тактовый генератор, счетчик импульсов, блок памяти и сумматор по модулю 2. В данной схеме работа, выполняемая блоком памяти, аналогична работе многоразрядного регистра сдвига. За счет увеличения объема памяти длина генерируемой последовательности увеличивается без значительного усложнения схемы C2j. Недостатком известного устройства является сложность изменения характеристик генерируемой псевдослучайной последовательности. Изменение последовательности возможно за счет изменения временного сдвига мезхду сигналами на входах сумматора по модулю 2 путем увеличения или уменьшения разрядности регистра сдвига. Однако это приводит к изменению общего числа разрядов генератора и связано со значительным изменением схемы. Цель изобретения - расширение функционирования возможностей генератора за счет обеспечения изменения характеристик формируемой последовательности. Для достижения поставленной цели в генератор псевдослучайной последовательности, содержащий генератор тактовых импульсов, счетчик, сумматор по модулю два, выход которого соединен с инфЬрмационным входом блока памяти, введены коммутатор, параллельный сумматор, два D-триггера, Т-триггер, два элемента И и элемент ИЛИ, выход которого соединен с управляющим входом блока памяти, выход которого соединен с D-входами D-триггеров, выходы которых соединены со входами сумматора по модулю два соответственно, выход генератора .тактовых импульсов соединен со входом Т-триггера и с первыми входами первого и второго элементов И, выходы которых соединены с С-входами соответствующих D-триггеров, прямой выход Т-триггера соединен с управляющим входом коммутатора, с первым входом элемента ИЛИ и со вторым входом первого элемента И, выход которого соединен со счетным входом счетчика, разрядные выходы которого соединены с первой группой входов параллельного сумматора соответственно, выходы которого соединены с соответствующими адресными входами блока памяти, инверсный выход Т-триггера соединен со вторым входом второго элемента И, выход которого соединен со вторым входом элемента ИЛИ, выход второго D-триггера является выходом генератора, группой входов которого является группа входов коммутатора, группа выходов которого соединена со второй группой входов параллельного cyMNfaTopa соответственно. На фиг. 1 дана блок-схема генератора; на фиг. 2 - диаграмма его работы. Генератор псевдослучайной последовательности содержит генератор 1 тактовых импульсов, Т-триггер 2f элементы ИЗ, элемент ИЛИ 4, блок 5 памяти, параллельный сумматор 6, счетчик 7, коммутатор 8, D-триггеры 9 и сумматор 10 по модулю два. Генератор работает следующим образом. Сигнал f с выхода генератора 1 поступает на вход триггера2 и элементы И 3. На прямом и инверсном выходах триггера 2 формируются сигналы Q и 9 формы меандр (фиг. 2), а на выходах элементов И 3 - несовпадающие последовательности импульсов V|, и V (фиг. 2) с частотой ,-1 Каждый импульс сигнала V , поступающий на вход счетчика 7, увеличивается на код М на его.разрядных выходах, соединенных со входами первого слагаемого параллельного сумматора 6. При достоянии Q 1 коммутатором 8 подключается ко всем входам второго слагаемого ксэдовый сигнал логического нуля. Сумматор 6 формирует на адресных шинах блока памяти 5 код М, определяющий адрес опрашиваемой ячейки памяти. Элемент ИЛИ, формирующий сигнал V Q V V/j, воздействуя на вход управления режимом работы блока 5 памяти, устанавливает блок памяти в режим считывания, и в первый D-триггер 9 сигналом переписывается содержимое ячейки памяти с адресом М. С приходом следующего импульса f триггер 2 переходит в состояние Q О, коммутатор 8 подключает ко входам вто- Е{ого слагаемого сумматора 6 управляющий кодовый сигнал N. Сумматор 6 формирует на -адресных шинах блока 5 памяти, работающего пр-преж нему в режиме считывания, код М + N и во; второй D-TpHrj ep 9 сигналом переписывается содержимое ячейки памяти М + N. На входах сумматора по модулю 2 формируется двоичное число, определяемое состоянием D-триггеров 9, По окончании импульса V на выходе элемента ИЛИ 4 формируется сигнал V о; блок 5 памяти переводится в режим записи, происходит запись числа с выхода сумматора по модулю 2 в ячейку памяти-с номером М + N.

Во время работы счетчик 7 проходит все К своих возможных состояний число которых равно объему памяти и блока 5 памяти, и число, записанное в каждую i-ячейку памяти, считывается на вход первого D-триггера 9 чеtie3 К - N периодовсигнала V , а на вход второго D-триггера 9 - через . К периодов. В результате работа, выполняемая блоком 5 памяти, аналогична работе К-разрядного регистра сдвига, охваченного обратной связью через сумматор по модулю 2, подключенный своими входами к последнему. (k-му) ,. и К - N-му разрядам регистра. За счет изменения регулирующей кодовой комбинации на входах коммутатора 8 может быть изменен номер разряда эквивалентного регистра сдвига, к которому подключен полусумматор.

Таким образом, генератор псевдослучайной последовательности позволяет получить все возможные последовательности при выбранном объеме памяти. При этом изменение, длины генерируемой последовательности не связано с изменением схемы устройства и увеличением аппаратурных затрат.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Генератор псевдослучайных последовательностей импульсов | 1981 |

|

SU978147A1 |

| Генератор псевдослучайной последовательности | 1987 |

|

SU1528770A1 |

| Генератор псевдослучайных последовательностей | 1990 |

|

SU1758851A2 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1267595A2 |

ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОС П1, содержащий гене ратор тактовых импульсов, счетчик., сумматор по модулю два, выход которого соединен о информационным входом блока памяти, о т л и чаю г щи и с я тем, что, с целью расширения функодюнальных возможностей генератора обеспечения изменения статистических характеристик формируемой последовательности, он содержит коммутатор, паралдель иЫ1й сумматор,, два D-триггера, Т-триггер два 31лемента И и элемент ИЛИ, выход которого соединен с управляю1цим вхо дом блока памяти, вiыxoд которого соединен с D-входами D-триггеров, выходы которых соединены с входами сумматора по модулю два соответственно, выходгенератора тактовых импульсов соединен с входом Т-триггера и с первыми входами первого и второго элементов И выходы которых соединены с С-входами соотвеТствуняцих D-триггеров, прямой выход Т-триггера соединен с управлякицим входом коммутатора, с первым входом элемента ИЛИ и с вторьйвходом перг вого элемента И, выход которого соединен со счетным входом счетчика, разрйдные .выходы которого соединены, с первой группой входов параллельного сумматора соответственно, выходы которого соединены с соответствщ)адами адресны

Фиг,2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Генератор псевдослучайных чисел | 1975 |

|

SU524175A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3243239/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-23—Публикация

1981-12-11—Подача