Изобретение относится к импульсной технике.

Целью изобретения является повы шение точности формирования распределения последовательности чисел.

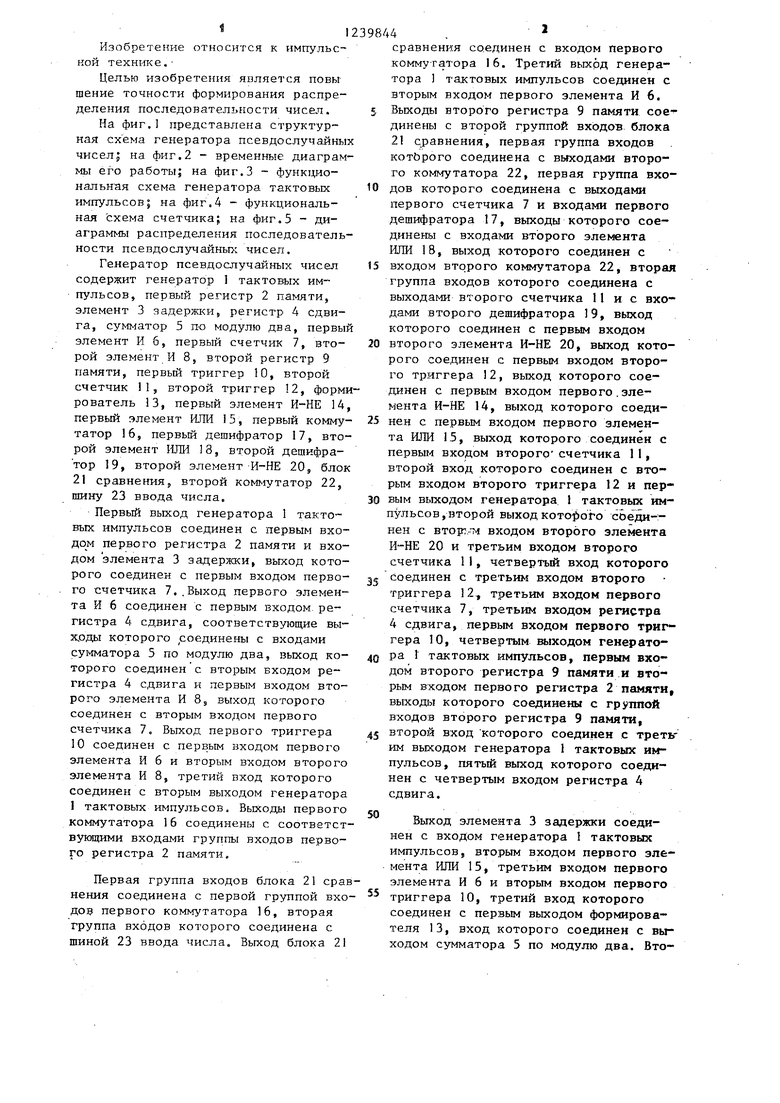

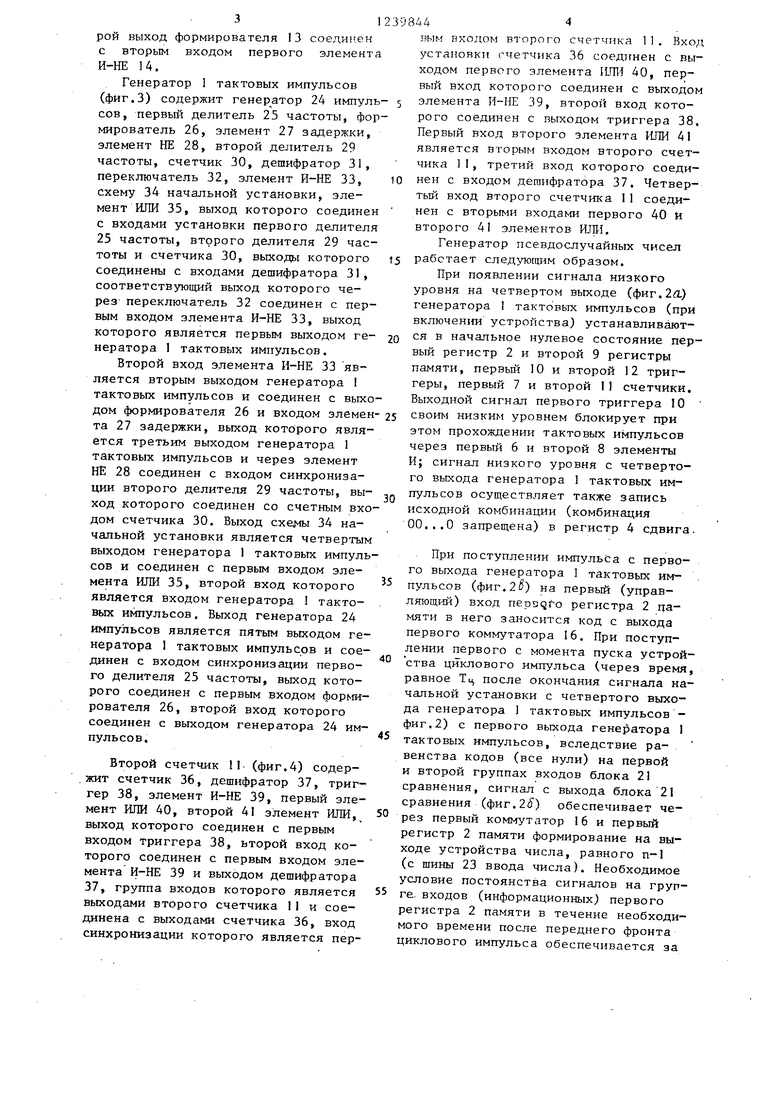

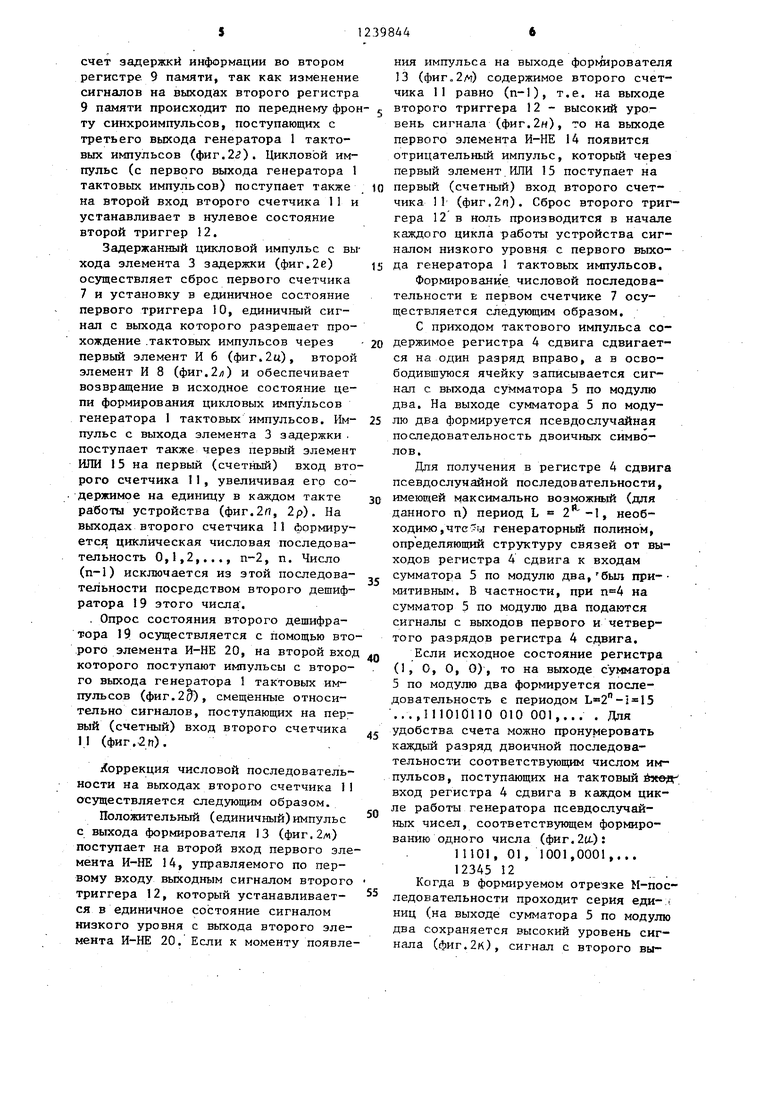

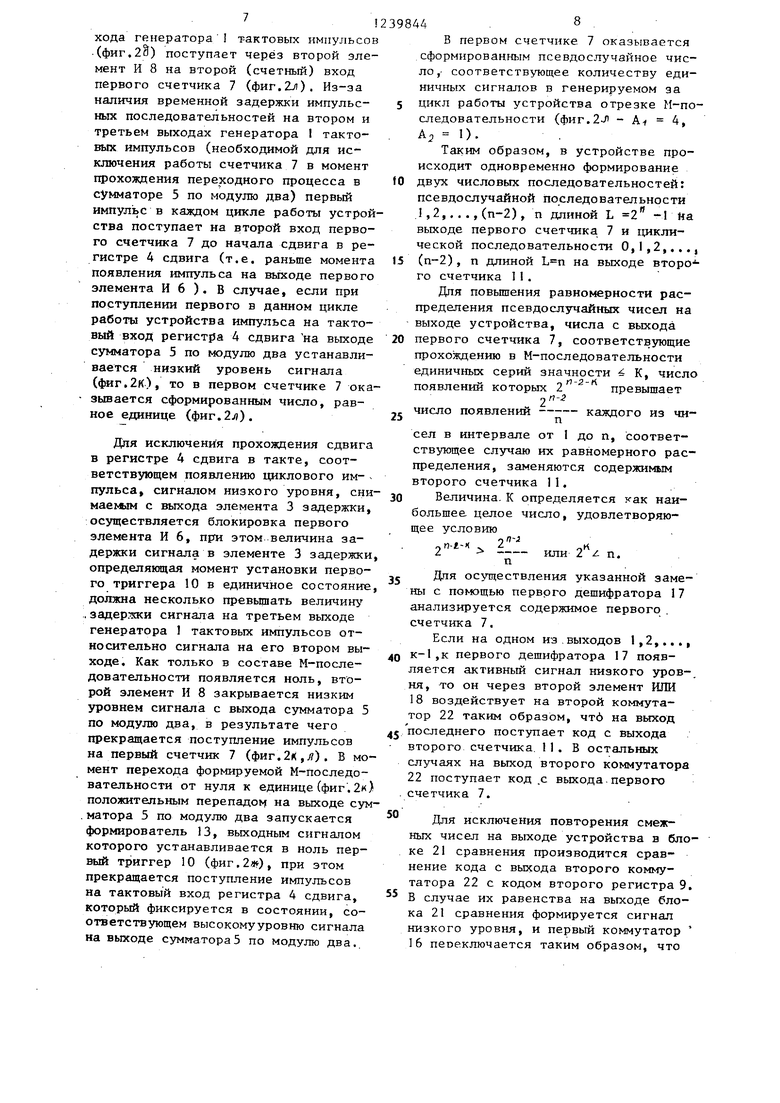

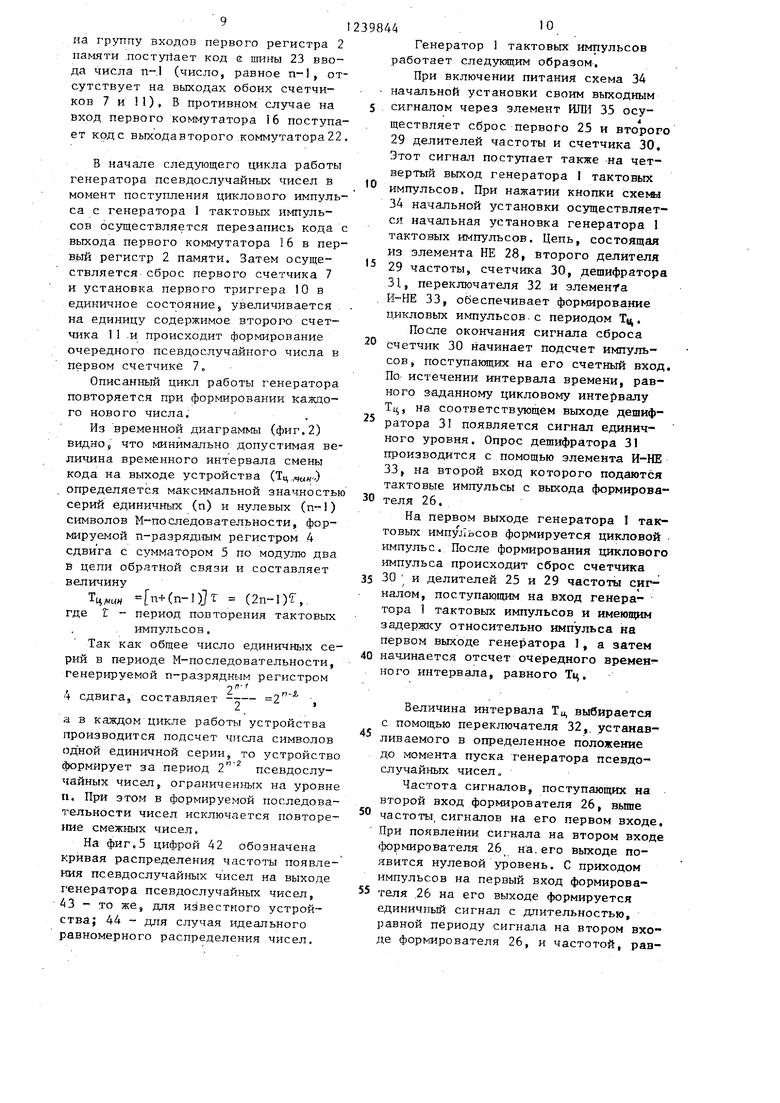

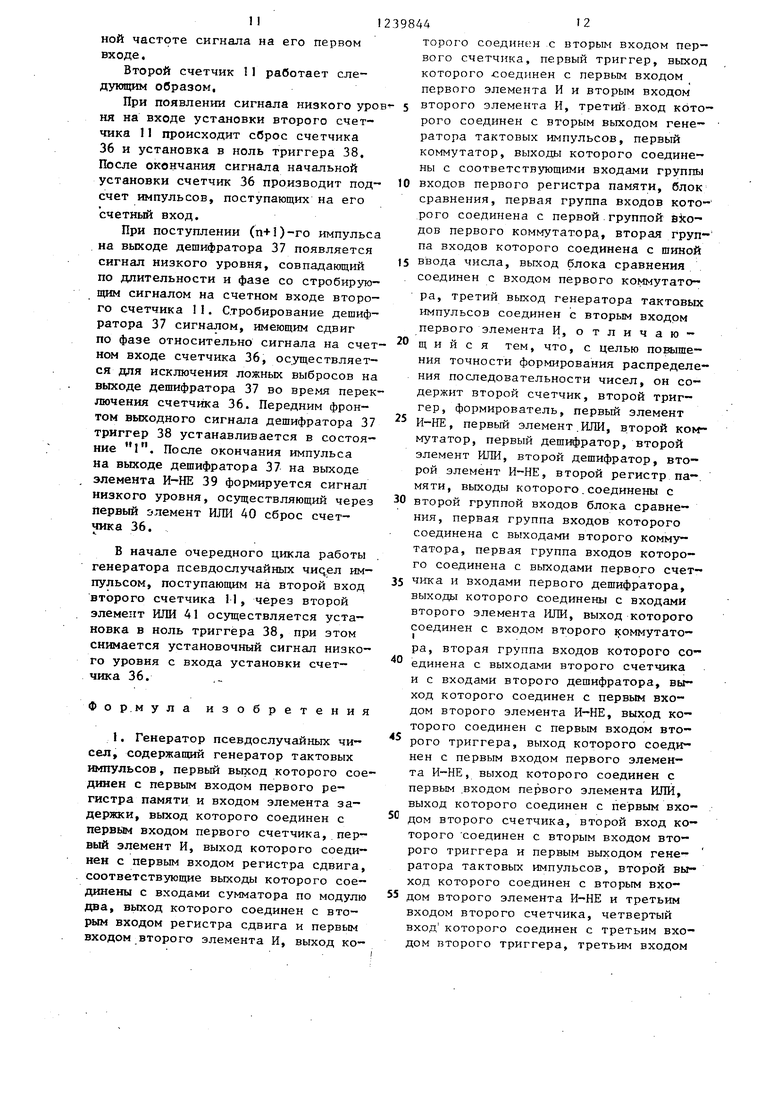

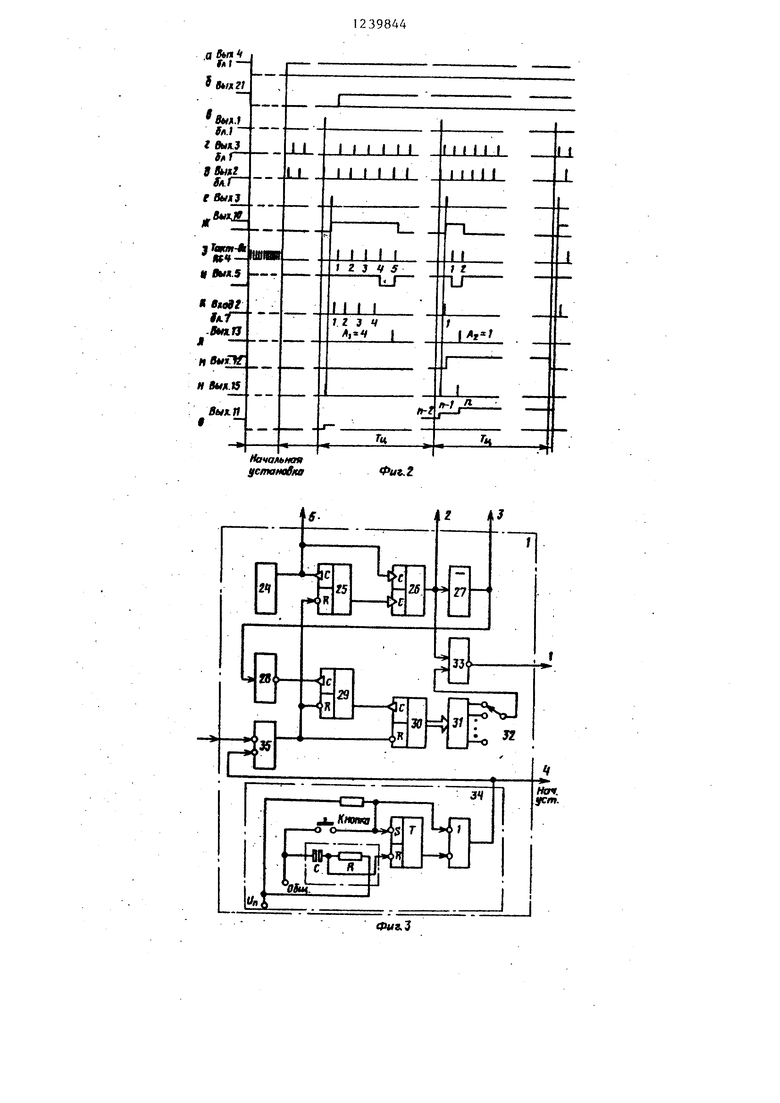

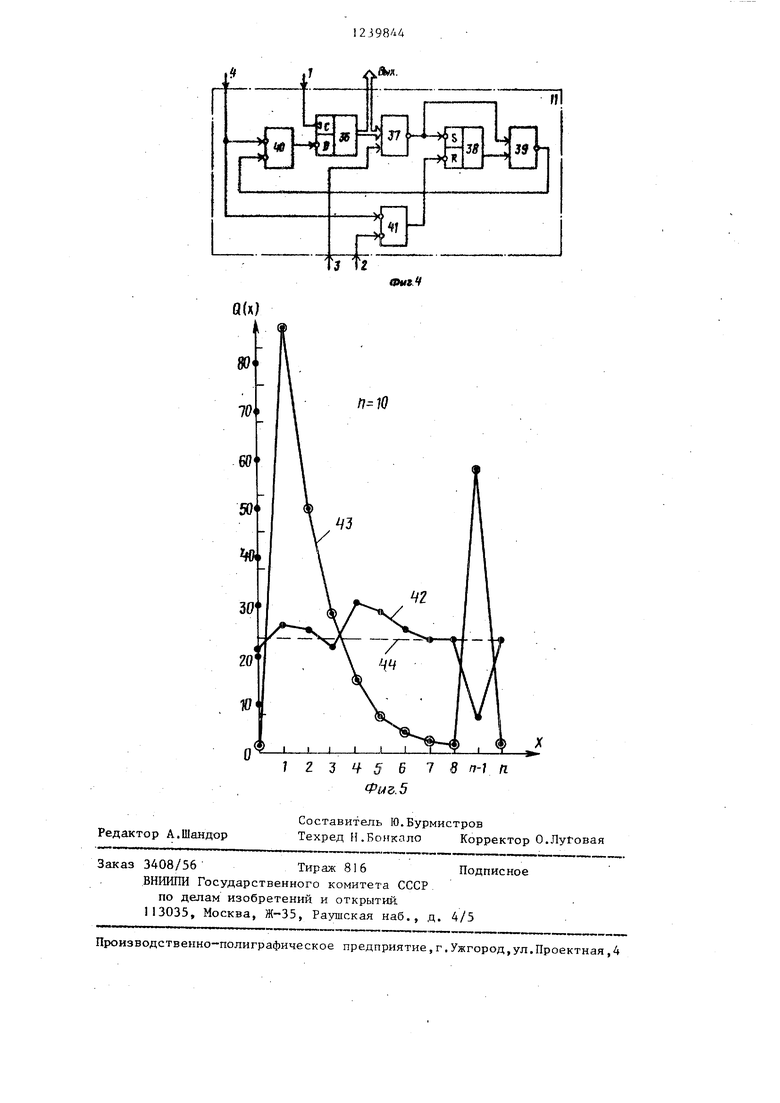

На фиг. представлена структурная схема генератора псевдослучайных чисел; на фиг.2 - временные диаграммы его работы; на фиг.З функщ-ю- нальная схема генератора тактовых импульсов; на фиг.4 - функциональная схема счетчика; на фиг.З - диаграммы распределения последовательности псевдослучайных чисел.

Генератор псевдослучайных чисел содержит генератор 1 тактовых импульсов, первый регистр 2 памяти, элемент 3 задержки, регистр 4 сдвига, сумматор 5 и-о модулю два, первый элемент И б, первый счетчик 7, второй элемент И 8, второй регистр 9 памяти, первый триггер 10, второй счетчик 1, второй триггер 12, формирователь 13, первый элемент И-НЕ 14, первый элемент ИЛИ 15, первый коммутатор 16, первый дешифратор 17, второй элемент 1ШИ 18, второй дешифратор 19, второй элемент И-НЕ 20, блок 21 сравнения, второй коммутатор 22, шину 23 ввода числа,

Первый выход генератора 1 тактовых импульсов соединен с первым входом первого регистра 2 памяти и входом элемента 3 задержки, выход которого соединен с первым входом первого счетчика 7..Выход первого элемента И 6 соединен с первым входом, регистра 4 сдвига, соответствующие вы- ЗС.ОДЫ которого соединены с входами сумматора 5 по модулю два, выход которого соединен с вторым входом регистра 4 сдвига и первым входом второго элемента И В, выход которого соединен с вторым входом первого счетчика 7, Выход первого триггера 10 соединен с первым входом первого элемента И 6 и вторым входом второго элемента И 8, третий вход которого соединен с вторым выходом генератора 1 тактовых импульсов. Выходы первого коммутатора 16 соединены с соответствующими входами группы входов первого регистра 2 памяти.

Первая группа входов блока 21 сранения соединена с первой группой входов первого коммутатора 16, вторая группа входов которого соединена с шиной 23 ввода числа. Выход блока 21

сравнения соединен с входом первого коммутатора 16. Третий выход генератора 1 тактовых импульсов соединен с вторым входом первого элемента И 6. Выходы второго регистра 9 памяти сое- динены с второй группой входов блока 21 сравнения, первая группа входов котЬрого соединена с выходами второго коммутатора 22, первая группа вхо- дов которого соединена с выходами первого счетчика 7 и входами первого дешифратора 17, выходы которого соединены с входа:ми второго элемента ИЛИ 18, выход которого соединен с входом BTQporo коммутатора 22, вторая группа входов которого соединена с выходами второго счетчика 11 и с входами второго дешифратора 19, выход которого соединен с первым входом второго элемента И-НЕ 20, выход которого соединен с первым входом второго триггера 12, выход которого соединен с первым входом первого.элемента И-НЕ 14, выход которого соеди- нен с первым входом первого элемента ИЛИ 15, выход которого соединен с первым входом второго счетчика 11, второй вход которого соединен с вторым входом второго триггера 12 и пер- вым выходом генератора I тактовых импульсов, второй выход которого соединен с BTOjn- M входом второго элемента И-НЕ 20 и третьим входом второго счетчика 11, четвертый вход которого соединен с третьим входом второго триггера 12, третьим входом первого счетчика 7, третьим входом регистра 4 сдвига, первым входом первого триггера 10, четвертым И)1ходом генерато- ра 1 тактовых импульсов, первьш входом второго регистра 9 памяти и вторым входом первого регистра 2 памяти, выходы которого соединены с группой входов второго регистра 9 памяти, второй вход которого соединен с третьим выходом генератора 1 тактовых импульсов, пятый выход которого соединен с четвертым входом регистра 4 сдвига.

Выход элемента 3 задержки соединен с входом генератора 1 тактовых импульсов, вторым входом первого элемента ИЛИ 15, третьим входом первого элемента И 6 и вторым входом первого триггера 10, третий вход которого соединен с первым выходом формирователя 13, вход которого соединен с выходом сумматора 5 по модулю два. Вто31

ой выход формирователя 13 соединен вторым входом первого элемента -НЕ 14.

Генератор 1 тактовых импульсов (фиг.З) содержит генер атор 24 импуль сов, первый делитель 25 частоты, формирователь 26, элемент 27 задержки, элемент НЕ 28, второй делитель 29 частоты, счетчик 30, дешифратор 31, переключатель 32, элемент И-НЕ 33, схему 34 начальной установки, элемент ШШ 35, выход которого соединен с входами установки первого делителя 25 частоты, второго делителя 29 частоты и счетчика 30, выходы которого соединены с входами дешифратора 31, соответствующий выход которого через переключатель 32 соединен с первым входом элемента И-НЕ 33, выход которого является первым выходом генератора 1 тактовых импульсов.

Второй вход элемента И-НЕ 33 является вторым выходом генератора I тактовых импульсов и соединен с выходом формирователя 26 и входом элемента 27 задержки, выход которого является третьим выходом генератора 1 тактовых импульсов и через элемент НЕ 28 соединен с входом синхронизации второго делителя 29 частоты, выход которого соединен со счетным входом счетчика 30. Выход cxe№i 34 начальной установки является четвертым выходом генератора 1 тактовых импульсов и соединен с первым входом элемента ИЛИ 35, второй вход которого является входом генератора I тактовых импульсов, Выход генератора 24 импульсов является пятым выходом генератора 1 тактовых импульсов и соединен с входом синхронизации первого делителя 25 частоты, выход которого соединен с первым входом формирователя 26, второй вход которого соединен с выходом генератора 24 импульсов.

Второй счетчик 11 (фиг.4) содер- жит счетчик 36, дешифратор 37, триггер 38, элемент И-НЕ 39, первый элемент ИЛИ 40, второй 41 элемент ИЛИ, выход которого соединен с первым входом триггера 38, второй вход которого соединен с первым входом элемента И-НЕ 39 и выходом дешифратора 37, группа входов которого является выходами второго счетчика 11 и соеинена с выходами счетчика 36, вход синхронизации которого является пер,398444

вым входом второго счетчика 11. Вход установки счетчика 36 соединен с выходом первого элемента 1ШИ 40, первый вход которого соединен с выходом 5 элемента И-НЕ 39, второй вход которого соединен с выходом триггера 38. Первый вход второго элемента ИЛИ 41 является вторым входом второго счетчика 1, третий вход которого соеди-

10 нен с входом дешифратора 37. Четвертый вход второго счетчика 11 соединен с вторыми входами первого 40 h второго 4 элементов ИЛИ.

Генератор псевдослучайных чисел

15 работает следующим образом.

При появлении сигнала низкого уровня на четвертом выходе (фиг.) генератора 1 тактбввгх импульсов (при включении устройства) устанавливают20 ся в начальное нулевое состояние первый регистр 2 и второй 9 регистры памяти, первый 10 и второй 12 триггеры, первый 7 и второй 11 счетчики, Выходной сигнал первого триггера 10

25 своим низким уровнем блокирует при этом прохождении тактовых импульсов через первый 6 и второй 8 элементы И; сигнал низкого уровня с четвертого выхода генератора 1 тактовьсх импульсов осуществляет также запись исходной комбинации (комбинация 00...О запрещена) в регистр 4 сдвига.

30

При поступлении импульса с первого выхода генератора 1 тактовых импульсов (фиг.2) на первый (управляющий) вход первого регистра 2 памяти в него заносится код с выхода первого коммутатора 16. При поступлении первого с момента пуска устрой ства цй клового импульса (через время, равное Ти, после окончания сигнала начальной установки с четвертого выхода генератора 1 тактовых импульсов - фиг.2) с первого выхода генератора 1

тактовых импульсов, вследствие равенства кодов (все нули) на первой и второй группах входов блока 21 сравнения, сигнал с выхода блока 21 сравнения (фиг. 2(5) обеспечивает через первый коммутатор 16 и первый регистр 2 памяти формирование на выходе устройства числа, равного п-1 (с шины 23 ввода числа). Необходимое условие постоянства сигналов на гругге. входов (информационных) первого регистра 2 памяти в течение необходимого времени после переднего фронта циклового импульса обеспечивается за

счет задержки информации во втором регкстре. 9 памяти, так как изменение сигналов на выходах второго регистра 9 памяти происходит по переднему фрон ту синхроимпульсов, поступающих с третьего выхода генератора 1 тактовых импульсов (фиг.21). Цикловой импульс (с первого выхода генератора 1 тактовых импульсов) поступает также на второй вход второго счетчика 11 и устанавливает в нулевое состояние второй триггер 12.

Задержанный цикловой импульс с выхода элемента 3 задержки (фиг.2е) осуществляет сброс первого счетчика 7 и установку в единичное состояние первого триггера 10, единичный сигнал с выхода которого разрешает прохождение .тактовых импульсов через первый элемент И 6 (фиг.2ц), второй элемент И 8 (фиг.2л) и обеспечивает возвращение в исходное состояние цепи формирования цикловых импульсов генератора 1 тактовых импульсов. Им- пульс с выхода элемента 3 задержки . поступает также через первый элемент ИЛИ 15 на первый (счетный) вход второго счетчика 11, увеличивая его содержимое на единицу в каждом такте работы устройства (фиг.2г(, 2р). На выходах второго счетчика 11 формируется циклическая числовая последовательность 0,1,2,..., п-2, п. Число (п-1) исключается из этой последовательности посредством второго дешифратора 19 этого числа .

. Опрос состояния второго дешифратора 19 осуществляется с помощью второго элемента И-НЕ 20, на второй вход которого поступают импульсы с второго выхода генератора 1 тактовых импульсов (фиг.29), смещенные относительно сигналов, поступающих на первый (счетный) вход второго счетчика 1.1 (фиг.2п).

Коррекция числовой последовательности на выходах второго счетчика 11 осуществляется следующим образом.

Положительный (единичный)импульс с выхода формирователя 13 (фиг. 2/4) поступает на второй вход первого элемента И-НЕ 14, управляемого по первому входу выходным сигналом второго триггера 12, который устанавливает- ся в единичное состояние сигналом низкого уровня с выхода второго элемента И-НЕ 20. Если к моменту появле

ния импульса на выходе фор ирователя 13 (фиг „2AT) содержимое второго счетчика 11 равно (n-i), т.е. на выходе второго триггера 12 - высокий уровень сигнала (фиг.2н), то на выходе первого элемента И-НЕ 14 появится отрицательный импульс, которьй через первый элемент.ИЛИ 15 поступает на первый (счетный) вход второго счетчика II (фиг,2п). Сброс второго триггера 12 в ноль производится в начале каждого цикла работы устройства сигналом низкого уровня с первого выхода генератора 1 тактовых импульсов.

Формирование числовой последовательности Е первом счетчике 7 осуществляется следующим образом.

С приходом тактового импульса содержимое регистра 4 сдвига сдвигается на один разряд вправо, а в освободившуюся ячейку записывается сигнал с выхода сумматора 5 по модулю два. На выходе сумматора 5 по модулю два формируется псевдослучайная последовательность двоичных символов.

Для получения в регистре 4 сдвига псевдослучайной последовательности, имеющей максимально возможный (дпя данного п) период L 2 -1, необходимо ,чтс7ы генераторный полином, определяющий структуру связей от выходов регистра 4 сдвига к входам сумматора 5 по модулю два, был при- митивным. В частности, при на сумматор 5 по модулю два подаются сигналы с выходов первого и четвертого разрядов регистра 4 сдвига.

Если исходное состояние регистра (1, О, О, О), то на выходе сумматора 5 по модулю два формируется последовательность с периодом L«2 -I 15 ...,111010110 010 001,... . Для удобства счета можно пронумеровать каждьий разряд двоичной последовательности соответствующим числом импульсов, поступающих на тактовый йэдад- вход регистра 4 сдвига в каждом цикле работы генератора псевдослучайных чисел, соответствующем формированию одного числа (фиг.2и-):

11101, 01, 1001,0001,... 12345 2

Когда в формируемом отрезке М-пос- ледовательности проходит серия еди-: ниц (на выходе сумматора 5 по модулю два сохраняется высокий уровень сигнала (фиг.2л), сигнал с второго выхода генератора I тактовых импульсов .(фиг,23) поступает через второй элемент И 8 на второй (счетный) вход первого счетчика 7 (фиг,). Из-за наличия временной задержки импульсных последовательностей на втором и третьем выходах генератора I тактовых импульсов (необходимой для исключения работы счетчика 7 в момент прохождения переходного процесса в сумматоре 5 по модулю два) первый импульс в каждом цикле работы устройства поступает на второй вход первого счетчика 7 до начала сдвига в регистре 4 сдвига (т.е. раньше момента появления импульса на выходе первого элемента И 6 ). В случае, если при поступлении первого в данном цикле работы устройства импульса на тактовый вход регистра 4 сдвига на выходе сумматора 5 по модулю два устанавливается низкий уровень сигнала (фиг.2к), то в первом счетчике 7 оказывается сформированным число, равное единице (фиг.2л).

Для исключения прохождения сдвига в регистре 4 сдвига в такте, соответствующем появлению циклового им- пульса, сигналом низкого уровня, сни с выхода элемента 3 задержки, осуществляется блокировка первого элемента И 6, при этом величина задержки сигнала в элементе 3 задержки определяющая момент установки первого триггера 10 в единичное состояние должна несколько превышать величин

.задержки сигнала на третьем выходе генератора 1 тактовых импульсов относительно сигнала на его втором выходе. Как только в составе М-после- довательности появляется ноль, второй элемент И 8 закрывается низким уровнем сигнала с выхода сумматора 5 по модулю два, в результате чего прекращается поступление импульсов на первый счетчик 7 (фиг,2«,л). В момент перехода формируемой М-последо- вательности от нуля к единице (фиг.2« положительным перепадом на выходе сум,матора 5 по модулю два запускается формирователь 13, выходным сигналом которого устанавливается в ноль первый триггер 10 (фиг,2), при этом прекращается поступление импульсов на тактовый вход регистра 4 сдвига, который фиксируется в состоянии, соответствующем высокомууровню сигнала на выходе сумматора5 по модулю два..

0

5

0

В первом счетчике 7 оказывается сформированным псевдослучайное число,- соответствующее количеству единичных сигналов в генерируемом за цикл работы устройства отрезке М-по- следовательности (фиг.2-/ - А 4,

А 1).

Таким образом, в устройстве происходит одновременно формирование двух числовых последовательностей: псевдослучайной последовательности 1,2,...,(п-2), п длиной L 2 -I На выходе первого счетчика 7 и циклической последовательности 0,1,2,,,,, (п-2), п длиной на выходе второ го счетчика I1.

Для повышения равномерности распределения псевдослучайных чисел на выходе устройства, числа с выхода первого счетчика 7, соответствующие прохождению в М-последовательности единичных серий значности К, число появлений которых 2 превышает

число появленийкаждого из чи-

п

сел в интервале от 1 до п, соответствующее случаю их равномерного распределения, заменяются содержимым второго счетчика 11,

Величина. К определяется как наибольшее целое число, удовлетворяющее условию

,м-г-н

или

2 п.

Для осуществления указанной замены с помощью первого дешифратора 17 анализируется содержимое первого . счетчика 7.

Если на одном из.выходов 1,2,,,,,

к-1,к первого дешифратора 17 появляется активный сигнал низкого уров-, ня, то он через второй элемент ИЛИ 18 воздействует на второй коммутатор 22 таким образом, чтб на выход

последнего поступает код с выхода второго счетчика. 11, В остальных случаях на выход второго коммутатора 22 поступает код .с выхода.первого счетчика 7,

Для исключения повторения смежных чисел на выходе устройства в блоке 21 сравнения производится сравнение кода с выхода второго коммутатора 22 с кодом второго регистра 9, В случае их равенства на выходе блока 21 сравнения формируется сигнал низкого уровня, и первый коммутатор 16 переключается таким образом, что

на группу входов первого регистра 2 памяти поступает код е шины 23 ввода числа П-.1 (число, равное п-, отсутствует на выходах обоих счетчиков 7 и 1), В противном случае на вход первого коммутатора 16 поступает коде выходавторого .коммутатора 22 ,

В начале следующего цикла работы генератора псевдослучайных чисел в момент поступления циклового импульса с генератора 1 тактовых импульсов осуществляется перезапись кода с выхода первого коммутатора 6 в пер- вьтй регистр 2 памяти. Затем осуществляется сброс первого счетчика 7 и установка первого триггера 10 в единичное состояние, увеличивается на единицу содержимое второго счетчика 11 .и происходит формирование очередного псевдослучайного числа в первом счетчике 7.

Описанный цикл работы генератора повторяется при формировании каладо- го нового числа.,

Из временной диаграммы (фиг.2) видно, что минимально допустимая величина временного интервала смены кода на выходе устройства (Тц../чы« .) определяется максимальной значностью серий единичных (п) и нулевых (п-) символов М-последовательности, формируемой п-раэрядным регистром .4 сдви га с сумматором 5 по модулю два в цепи обратной связи и составляет величину

Тц/«ич (п-1)г (2п-1)Т,. где t - период повторения тактовых импульсов,

Так как общее число единичных серий в периоде М-последовательности,

генерируемой п-разрядным регистром

пП-1

4 сдвига, составляет 2 ,

а в каждом цикле работы устройства производится подсчет числа символов од ной единичной серии, то устройство формирует за период псевдослучайных чисел, ограниченгшх на уровне п. При этом в формируемой последовательности чисел исключается повторе- 1гие смежных чисел.

На фиг,5 цифрой 42 обозначена кривая распределения частоты появления псевдослучайных чисел на выходе генератора псевдослучайных чисел, 43 - то же, для известного устройства; 44 - для случая идеального равномерного распределения чисел.

to

15

20

39844 °Генератор 1 тактовых импульсов работает следующим образом,

При включении питания схема 34 начальной установки своим выходным 5 сигналом через элемент ИПИ 35 осуществляет сброс первого 25 и второго 29 делителей частоты и счетчика 30, Этот сигнал поступает также на четвертый выход генератора I тактовых импульсов. При нажатии кнопки схегвл 34 начальной установки осуществляется начальная установка генератора 1 тактовых импульсов. Цепь, состоящая из элемента НЕ 28, второго делителя

29частоты, счетчика 30, дешифратора 31, переключат(шя 32 и элемента И-НЕ 33, обесп€ чивает формирование цикловых импульсов.с периодом Тц.

Посхле окончания сигнала сброса счетчик 30 начинает подсчет импульсов, поступающих на его счетный вход. По истечении интервала времени, равного заданному цикловому интервалу Тц, на соответствующем выходе дешифратора 31 появляется сигнал единичного уровня. Опрос дещифратора 31 производится с помощью элемента И-НЕ 33, на второй вход которого подаются тактовые импульсы с выхода формирователя 26,

На первом выходе генератора 1 тактовых импyJiьcoв формируется цикловой . импульс. После формирования циклового импульса происходит сброс счетчика

30 и делителей 25 и 29 частоты сигналом, поступавдщим на вход генератора 1 тактовых импульсов и имеющим задержку относительно импульса на первом выходе генератора 1, а затем

40 начинается отсчет очередного временного интервала, равного Тц,

25

30

35

45

50

Величина интервала Тц выбирается с помощью переключателя 32,. устанавливаемого в определенное положение до момента пуска генератора псевдо- схсучай йгх чисел,.

Частота сигнгшов, поступающих на второй вход формирователя 26, выше частоты, сигналов на его первом входе, При появлении сигнала на втором входе формирователя 26 на.его выходе появится нулевой уровень. С приходом импульсов на первый вход формирова- 55 теля .26 на его выходе формируется единичный сигнал с длительностью, равной периоду сигнала на втором входе форь ирователя 26, и частотой, рав

1 I

ной частоте сигнала на его первом входе,

Второй счетчик 11 работает следующим образом.

При появлении сигнала низкого уров ня на входе установки второго счетчика 11 происходит сброс счетчика 36 и установка в ноль триггера 38, После окончания сигнала начальной установки счетчик 36 производит подсчет импульсов, поступающих на его счетный вход.

При поступлении (п+1)-го импульса на выходе дешифратора 37 появляется сигнал низкого уровня, совпадающий по длительности и фазе со стробирую- щим сигналом на счетном входе второго счетчика 1. Стробирование дешифратора 37 сигналом, имеющим сдвиг по фазе относительно сигнала на счетном входе счетчика 36, осуществляется для исключения ложных выбросов на выходе дешифратора 37 во время переключения счетчика 36. Передним фронтом выходного сигнала дешифратора 37 триггер 38 устанавливается в состояние 1. После окончания импульса на выходе дешифратора 37 на выходе элемента И-НЕ 39 формируется сигнал низкого уровня, осуществляющий через первый элемент ИЛИ 40 сброс счетчика 36.

12

В начале очередного цикла работы генератора псевдослучайных импульсом, поступающим на второй вход второго счетчика 11, через второй элемент ИЖ 41 осуществляется установка в ноль триггера 38, при этом снимается установочный сигнал низкого уровня с входа установки счетчика 36.

Формула изобретения

I, Генератор псевдослучайных чисел, содержащий генератор тактовых импульсов, первый выход которого соединен с первым входом первого регистра памяти и входом элемента задержки, выход которого соединен с первым входом первого счетчика, первый элемент И, выход которого соединен с первым входом регистра сдвига, соответствующие выходы которого соединены с входами сумматора по модулю два, выход которого соединен с вторым входом регистра сдвига и первым входом второго элемента И, выход ко-

10

20

- 5

25

239844 2

торого соединен .с вторьш входом первого счетчика, первый триггер, выход которого соединен с первым входом первого элемента И и вторым входом второго элемента И, третий вход которого соединен с вторым выходом гене- ратора тактовых импульсов, первый коммутатор, выходы которого соединены с соответствующими входами группы входов первого регистра памяти, блок сравнения, первая группа входов кото- рого соединена с первой группой Вводов первого коммутатора,, вторая труп- па входов которого соединена с шиной

15 ввода числа, выход блока сравнения соединен с входом первого коммутатора, третий выход генератора тактовых импульсов соединен с вторым входом первого элемента И, отличающийся тем, что, с целью повышения точности формирования распределения последовательности чисел, он содержит второй счетчик, второй триггер, формирователь, первый элемент И-НЕ, первый элемент.ИЛИ, второй мутатор, первый дешифратор, второй элемент ИЛИ, второй дешифратор, второй элемент И-НЕ, второй регистр па-. мяти, вьсходы которого,соединены с второй группой входов блока сравнения, первая группа входов которого соединена с выходами второго коммутатора, первая группа входов которого соединена с выходами первого счет-

35 чика и входами первого дешифратора, выходы которого соединены с входами второго элемента ИЛИ, выход которого соединен с входом второго коммутатора, вторая группа входов которого соединена с выходами второго счетчика и с входами второго дешифратора, выход которого соединен с первым входом второго элемента И-НЕ, выход которого соединен с первым входом второго триггера, выход которого соединен с первым входом первого элемента И-НЕ, выход которого соединен с первым .входом первого элемента ИЛИ, выход которого соединен с первым входом второго счетчика, второй вход которого соединен с вторым входом второго триггера и первым выходом генератора тактовых импульсов, второй выход которого соединен с вторым вхо-

55 дом второго элемента И-НЕ и третьим входом второго счетчика, четвертый вход которого соединен с третьим входом второго триггера, третьим входом

30

40

45

50

П1

первого счетчика, треть 1м входом регистра сдвига, первым входом .первого триггера, четвертым выходом генератора тактовых импульсов 5 первым входом второго регистра памяти и вторым входом первого регистра памяти, выходы которого соединены с группой входов втс-рого регистра памяти, второй вход которого соединен с третьим выходом генератора тактовых импульсов , пятый выход которого соединен с четвертым входом регистра сдвига, выход элемента задержки соединен с входом генератора тактовых импульсов вторым входом первого элемента ИЛИ, третьим входом первог о элемента И и вторьм входом первого триггера, третий вход которого соединен с первым выходом формирователя вход которого соед} нен с выходом сумматора по модулю два, второй выход формирователя соединен с вторым входом первого элемента И-НЕ.

2,,Генератор по п,1j о т л и ч, а- ю щ и и с я тем, что генератор тактовых импульсов содержит генератор импульсов, первый делитель частоты формирователь., элемент задержки/ элемент НЕ, второй делитель частотыj счетчик5 дешифратору переключатель,, элемент И-НЕ; схему начальвюй установки, элемент ИЛИ выход которого соединен с входами установки первого делителя частоты, второго делителя частоты и счетчика, выходы которого соединены с входами дешифра.тора, со- ответств-ующий выход которого через переключаталь соединен с первым вхо Дом эле.мента выход которого является первым выходом генератора тактовых тампульсоВэ второй вход элемента И-ЫЕ является вторым выходом генератора тактовых импульсов и соединен с выходом формирователя и входом элемента задержки, выход которо4 1го яр ляется третьим выходом генератора тактовых импульсов и через элемент НЕ соединен с входом синхронизации второго делителя частоты, вы- ход которого соединен со счетным входом счетчика, выход схемы начальной установки является четвертым выходом генератора тактовых импульсов и соединен с первым входом элемента ИЛИ,

второй вход которого является входом генератора тактовых импульсов, выход генератора импульсов является пятым вьгходом генератора тактовых импульсов и соединен с входом синхрониза-

ции первого делителя частоты, выход которого соединен с первым входом формирователя, второй.вход которого соединен с выходом генератора импульсов .

3, Генератор по п,, о т л и - чающийся тем, что второй счетчик содержит счетчик, дешифратор, триггер, элемент И-НЕ, первый эле-

мент HJWl, второй элемент ИЛИ, выход которого соединен с первым входом триггера 5 второй вход которого соединен с первым входом элемента И-НЕ и выходом дешифратора, группа входов

которого является выходами второго счетчика и соединена с выходами счетчика, вход синхронизации которого является первым входом второго счетчика, вход установки счетчика соединен с выходом первого элемента ИЛИ, первый Бход которого соединен с выходом элемента И-НЕ, второй вход которого соединен с выходом триггера, первый вход второго элемента ИЛИ является вторым входом второго счетчика.

третий вход которого соединен с

входом дешифратора, четвертый вход второго счетчика соединен с вторыми входами первого и второго элемен- , тов ИЛИ.

Начальная устамвт

Фиг.2

Ч 9

а

38

I

ш

Wb

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1986 |

|

SU1324091A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1101825A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU942014A1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2020766C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

Изобретение относится к импульсной технике. Цель изобретения - повышение точности формирования распределения последовательности чисел. Устройство содержит генератор 1 тактовых импульсов, регистр 2 памяти, элемент 3 задержки, регистр 4 сдвига, сумматор 5 по модулю два, элементы И 6 ii 8, счетчик 7, триггер 1C, коммутаторы 16 и 22, дешифратор 17, элемент ИЛИ 18, блок 21 сравнения. Достижению поставленной цели способствует введение в устройство регистра 9 памяти, счетчика 11, триггера 12, формирователя 13, элементов И-НЕ 14 и 20, элемента ИЛИ 15, дешифратора 19, образование новых связей между элементами устройства и конкретное выполнение генератора тактовых импульсов. 2 з.п. ф-лы, 5 ил. § (Л со со сэо 4 4

Редактор А.Шандор

2 3 5 6 7 .8 /7-; д Фиг. 5

Составитель Ю.Бурмистров

Техред Н.Боикало Корректор 0.Луговая

Заказ 3408/56Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

| Яковлев В.В., Федоров Р.Ф | |||

| Стохастические вычислительные машины -Л.:Машиностроение, 1974, с.247-253 | |||

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-23—Публикация

1984-12-25—Подача