Изобретение относится к вычислительной технике и предназначено для спектрального анализа сигналов в реальном масштабе времени.

Целью изобретения является упрощение устройства,

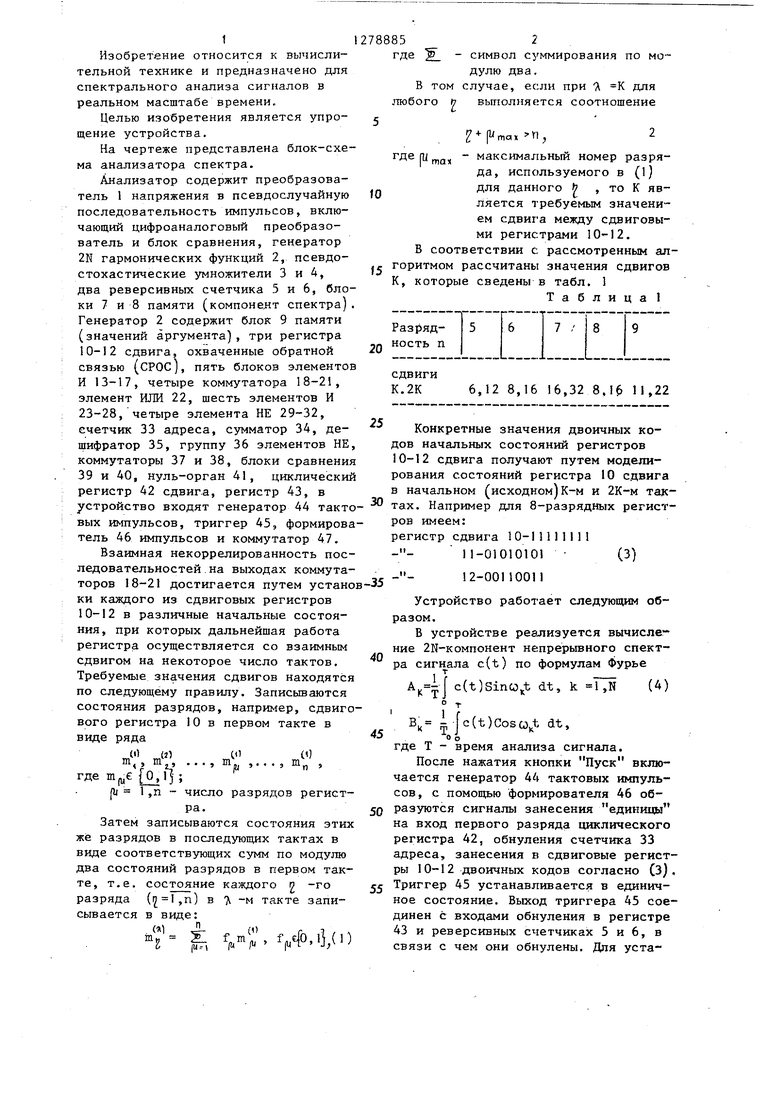

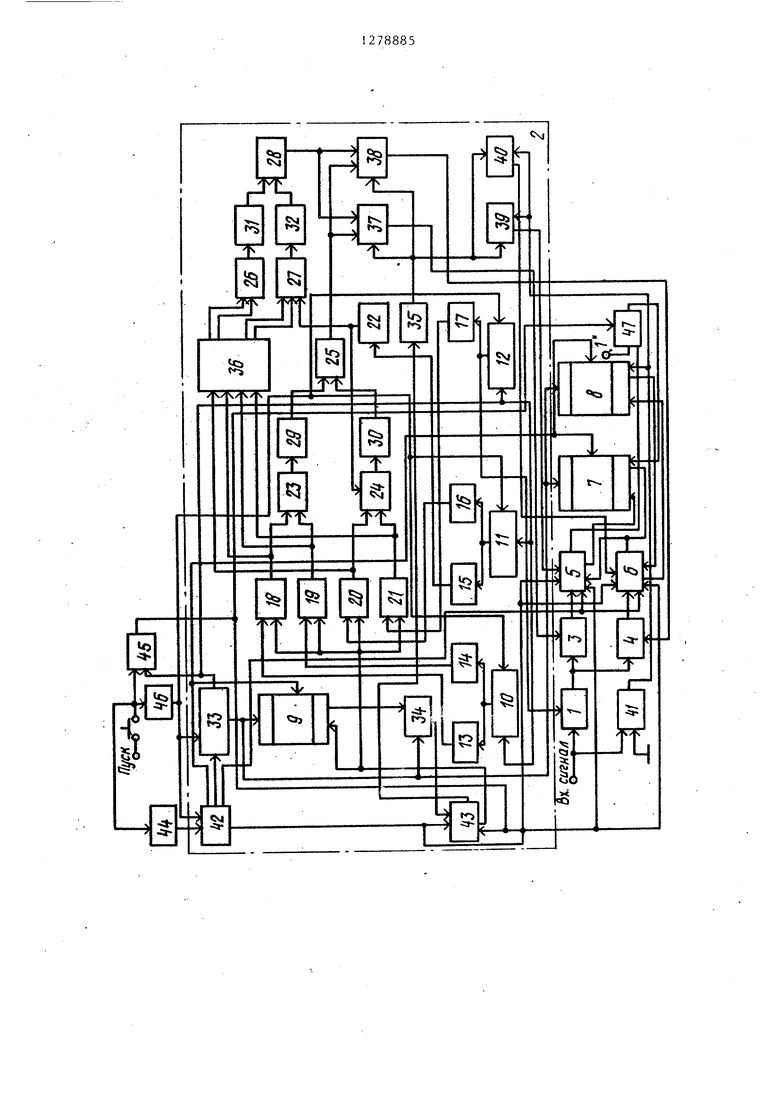

На чертеже представлена блок-схема анализатора спектра.

Анализатор содержит преобразователь 1 напряжения в псевдослучайную последовательность импульсов, включающий цифроаналоговый преобразователь и блок сравнения, генератор 2N гармонических функций 2, псевдостохастические умножители 3 и 4, два реверсивных счетчика 5 и 6, блоки 7 и 8 памяти (компонент спектра). Генератор 2 содержит блок 9 памяти (значений аргумента), три регистра 10-12 сдвига, охваченные обратной связью (СРОС), пять блоков элементов И 13-17, четыре коммутатора 18-21, элемент ИЛИ 22, шесть элементов И 23-28, четыре элемента НЕ 29-32, счетчик 33 адреса, сумматор 34, дешифратор 35, группу 36 элементов НЕ, коммутаторы 37 и 38, блоки сравнения 39 и 40, нуль-орган 41, циклический регистр 42 сдвига, регистр 43, в устройство входят генератор 44 тактовых импульсов, триггер 45, формирователь 46 импульсов и коммутатор 47.

Взаимная некоррелированность последовательностей . на выходах коммутаторов 18-21 достигается путем устано ки каждого из сдвиговых регистров 10-12 в различные начальные состояния, при которых дальнейшая работа регистра осуществляется со взаимным сдвигом на некоторое число тактов. Требуемые значения сдвигов находятся по следующему правилу. Записываются состояния разрядов, например, сдвигового регистра 10 в первом такте в виде ряда

т , т , .., , , ,,. . , т„ , где (0,15;

flj 1 ,п - число разрядов регистра.

Затем записываются состояния этих же разрядов в последующих тактах в виде соответствующих сумм по модулю два состояний разрядов в первом такте, т.е, состояние каждого о разряда (,п) в -м такте записывается в виде:

i ,}/)

1278885 где

W - символ суммирования по модулю два.

В том случае, если при А К для любого J7 выполняется соотношение

гр.

п

где

Р

max

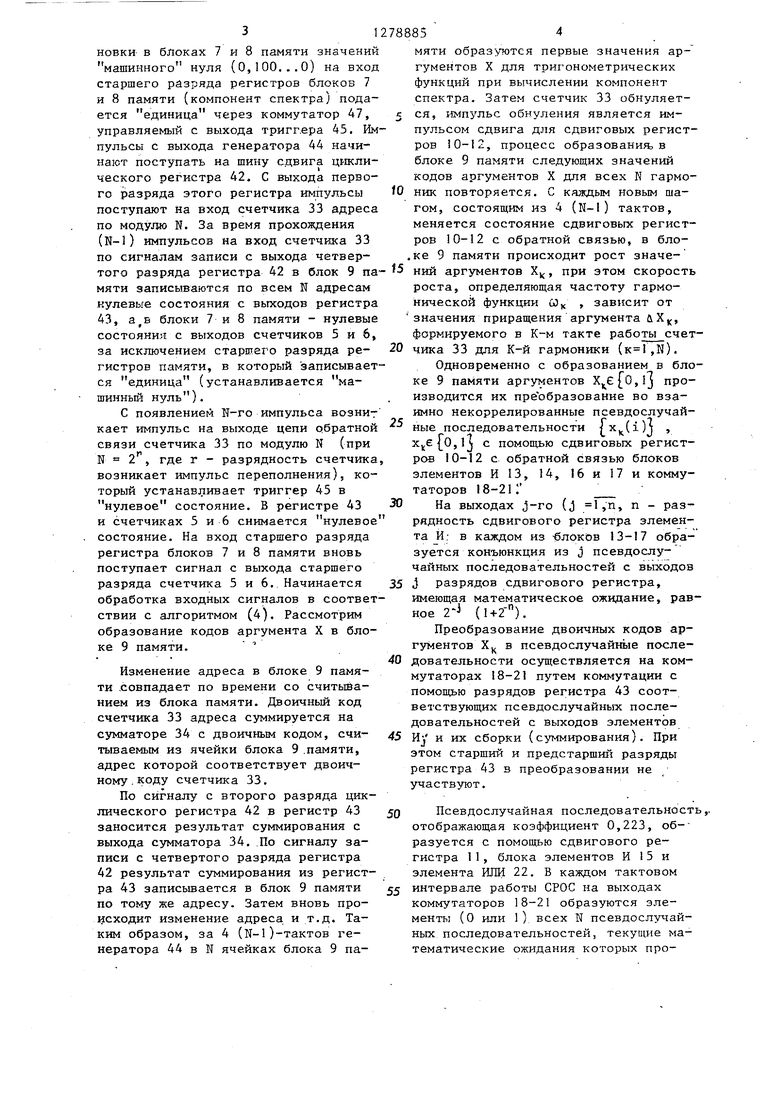

- максимальный номер разряда, используемого в (1) для данного , то К является требуемым значением сдвига между сдвиговыми регистрами 10-12. В соответствии с рассмотренным алгоритмом рассчитаны значения сдвигов К, которые сведены в табл. 1

Таблица 1

5

35

30

0

50

Конкретные значения двоичных кодов начальных состояний регистров 10-12 сдвига получают путем моделирования состояний регистра 10 сдвига в начальном (исходном)К-м и 2К-м так тах. Например для 8-разрядных регистров имеем:

регистр сдвига 10-11111111 11-01010101 (3)

- -12-00110011

Устройство работает следующим образом.

В устройстве реализуется вычисление 2Ы-компонент непрерывного спектра сигнала c{t) по формулам Фурье

(4)

45

c(t)sinco t dt, k 1,N

° т В 1 jc(t) dt.

0 о

где Т - время анализа сигнала.

После налатия кнопки Пуск включается генератор 44 тактовых импульсов, с помощью формирователя 46 образуются сигналы занесения единицы

на вход первого разряда циклического регистра 42, обнуления счетчика 33 адреса, занесения в сдвиговые регистры 10-12 двоичных кодов согласно (З). Триггер 45 устанавливается в единичное состояние. Выход триггера 45 соединен с входами обнуления в регистре 43 и реверсивных счетчиках 5 и 6, в связи с чем они обнулены. Для установки в блоках 7 и 8 памяти значений машинного нуля (0,100..,0) на вход старшего разряда регистров блоков 7 и 8 памяти (компонент спектра) подается единица через коммутатор 47, управляемый с выхода триггера 45, Импульсы с выхода генератора 44 начинают поступать на шину сдвига циклического регистра 42, С выхода первого разряда этого регистра ш-шульсы поступают на вход счетчика 33 адреса по моду/ио N. За время прохождения () импульсов на вход счетчика 33 по сигналам записи с выхода четвермяти образуются первые значения ар- гументов X для тригонометрических функций при вычислении компонент спектра. Затем счетчик 33 обнуляет5 ся, импульс обнуления является импульсом сдвига для сдвиговых регистров 10-12, процесс образования в блоке 9 памяти следующих значений кодов аргументов X для всех И гармоfO ник повторяется. С каждым новым шагом, состоящим из 4 (N-1) тактов, меняется состояние сдвиговых регистров 10-12 с обратной связью, в бло- .ке 9 памяти происходит рост значетого разряда регистра 42 в блок 9 па- 5 ний аргументов Х, при этом скорость

мяти записываются по всем Я адресам нулевые состояния с выходов регистра 43, а,Б блоки 7 и 8 памяти - нулевые состояния с выходов счетчиков 5 и 6, за исключением старшего разряда регистров памяти, в который записывается единица (устанавливается машинный нуль).

С появлением N-ro импульса возниг кает импульс на выходе цепи обратной связи счетчика 33 по модулю N (при N 2, где г - разрядность счетчика возникает импульс переполнения), который устанавливает триггер 45 в нулевое состояние. В регистре 43 и счетчиках 5 и 6 снимается нулевое состояние. На вход старшего разряда регистра блоков 7 и 8 памяти вновь поступает сигнал с выхода старшего разряда счетчика 5 и 6. Начинается обработка входных сигналов в соответствии с алгоритмом (4). Рассмотрим образование кодов аргумента X в блоке 9 памяти.

Изменение адреса в блоке 9 памяти .совпадает по времени со считыванием из блока памяти. Двоичный код счетчика 33 адреса суммируется на сумматоре 34 с двоичным кодом, считываемым из ячейки блока 9 .памяти, адрес которой соответствует двоичному .коду счетчика 33.

По сигналу с второго разряда циклического регистра 42 в регистр 43 заносится результат суммирования с выхода сумматора 34..По сигналу записи с четвертого разряда регистра 42 результат суммирования из регистра 43 записьшается в блок 9 памяти по тому же адресу. Затем вновь происходит изменение адреса и т.д. Таким образом, за 4 (Н-1)-тактов генератора 44 в N ячейках блока 9 памяти образуются первые значения ар- гументов X для тригонометрических функций при вычислении компонент спектра. Затем счетчик 33 обнуляется, импульс обнуления является импульсом сдвига для сдвиговых регистров 10-12, процесс образования в блоке 9 памяти следующих значений кодов аргументов X для всех И гармоник повторяется. С каждым новым шагом, состоящим из 4 (N-1) тактов, меняется состояние сдвиговых регистров 10-12 с обратной связью, в бло- ке 9 памяти происходит рост значероста, определяющая частоту гармонической функции СО,

зависит от

значения приращения аргумента и X,j, формируемого в К-м такте работы счет- чика 33 для К-й гармоники (,К).

Одновременно с образованием в блоке 9 памяти аргументов ,Ij производится их преЪбразование во взаимно некоррелированные псевдослучайные последовательности |хк. х,,е ,1 с помощью сдвиговых регистров 10-12 с обратной связью блоков элементов И 13, 14, 16 и 17 и коммутаторов 18-211

На выходах j-ro (j 1,п, п - разрядность сдвигового регистра элемента И; в каждом из -блркбв 13-17 образуется конъюнкция из j псевдослучайных последовательностей с выходов j разрядов сдвигового регистра.

0

5

0

5

имеющая математическое ожидание, равное 2 (1+2 ).

Преобразование двоичных кодов аргументов Х в псевдослучайньш последовательности осуществляется на коммутаторах 18-21 путем коммутации с помощью разрядов регистра 43 соответствующих псевдослучайных последовательностей с выходов элементов Иу и их сборки (суммирования). При этом старший и предстарший разряды регистра 43 в преобразовании не участвуют.

Псевдослучайная последовательность,, отображающая коэффициент 0,223, об- разуется с помощью сдвигового регистра 11, блока элементов И 15 и элемента ИЛИ 22. В каждом тактовом интервале работы СРОС на выходах коммутаторов 18-21 образуются элементы (о или 1), всех N псевдослучайных последовательностей, текущие математические ожидания которых пропорциональны текущим значениям аргументов Х. Последовательности с выходов коммутаторов 18-21 поступают соответственно на входы элементов И 23 и 24, причем на первый вход И 24 поступает последовательность с выхода элемента ИЛИ 22, Так как последовательности на входах этих элементов И взаимно некоррелированы, то на их выходах образуются последовательности с математическими ожиданиями, пропорциональными соответственно значениям Х и 0,223 Х.

После инвертирования с помощью элементов НЕ 29 и 30 последовательности, представляющие значения (1 - Х) и (1-0,223 Х), поступают на входы умножителя, роль которого выполняет элемент И 25.

На выходе И 25 образуется последовательность с математическю ожиНа выходах коммутаторов 37 и 38 образуются псевдослучайные последовательности с математическими ожиданиями, пропорциональными значениям модулей тригонометрических функций. Знак гармонической функции формируется на выходах дешифратора 35. Модуль исследуемого сигнала /c(t)/ преобразуется в псевдослучайную последовательность C(i), C(i),lj с помощью входного преобразователя I, в котором производится сравнение значений /c(t)/ с напряжением на выходе цифроаналогового преобразователя, подключенного к разрядам сдвигового регистра 12. Знак входного сигнала в виде нулей и единиц фиксируется на выходе нуль-органа 41.

данием, пропорциональным Cos . Аналогичным образом на выходе элемента И 28 формируется последовательность с математическим ожиданием Sin хХ

Cos (1-х), при этом инвертирование

аргумента X осуществляется с помощью группы элементов НЕ 36. Формирование последовательностей, представляющих значения тригонометрических функций в диапазоне (0,), осуществляется с помощью дешифратора 35, управляющего коммутаторами 37 и 38, на входы которых поступают последовательности с выходов И 25 и 28.

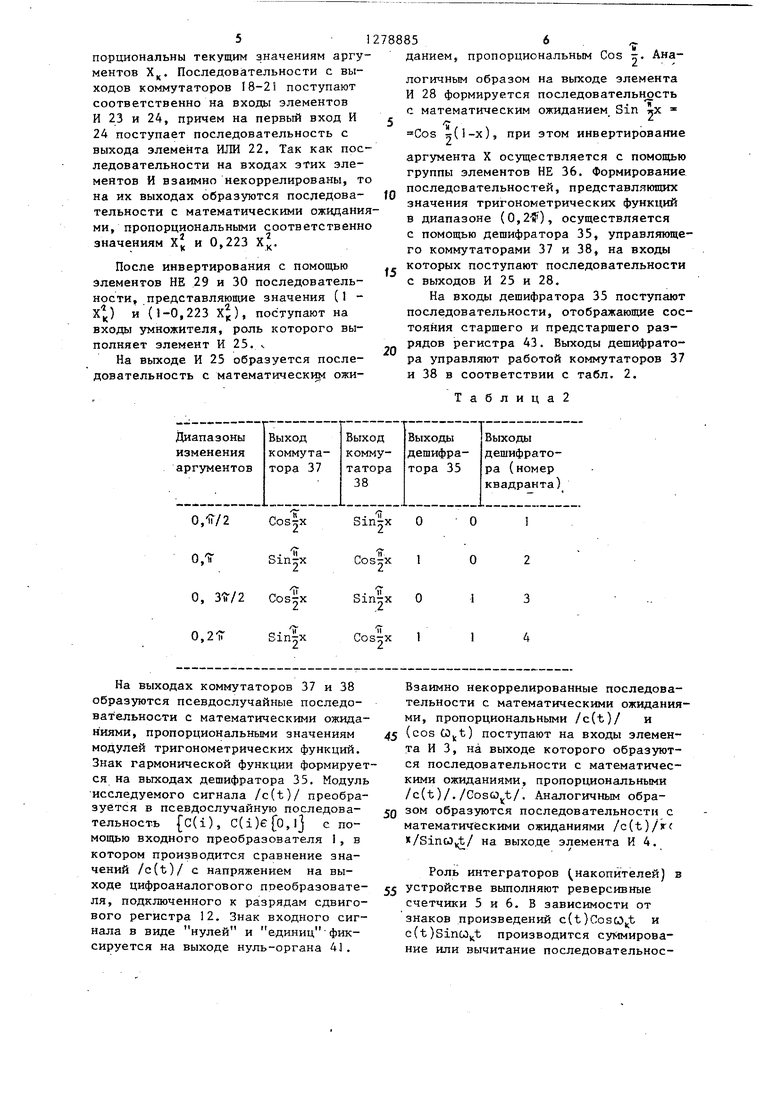

На входы дешифратора 35 поступают последовательности, отображающие состояния старшего и предстарщего разрядов регистра 43. Выходы дешифратора управлгшт работой коммутаторов 37 и 38 в соответствии с табл. 2.

Таблица2

Взаимно некоррелированные последовательности с математическими ожиданиями, пропорциональными /c(t)/ и 45 (cos ) поступают на входы элемента И 3, на выходе которого образуются последовательности с математическими ожиданиями, пропорциональными /c(t)/./GosOj,t/. Аналогичным образом образуются последовательности с

50

математическими ожиданиями /c(t)(

)t/Sinco.,t/ на выходе элемента И 4.

- . /

Роль интеграторов накопителей) в jjl устройстве выполняют реверсивные счетчики 5 и 6. В зависимости от знаков произведений c(t)CoscOj,t и c(t)SinQ,,t производится суммирование или вычитание последовательное7

тей, поступающих с выходов элементов И 3 и 4.

Знаки произведений определяются с помощью блоков 39 и 40 сравнения, входы которых подключены к выходу нуль-органа 41 и дешифратора 35, а выходы - к щинам управления счетом в реверсивных счетчиках 5 и 6.

За данный тактовый интервал ftt работы СРОС на выходах И 3 и 4 образуются элементы псевдослучайных последовательностей, представляющих произведения модуля входного сигнала на модули всех 2N гармонических функций.

Формирование компонент спектра в блоках 7 и 8 памяти происходит сле-i дующимобра3ом.

Перед началом вычислений во всех ячейках блоков 7 и 8 памяти записаны состояния машинного нуля (0,100...0). Изменение адреса в блоке 7 памяти совпадает по времени со считыванием из блока памяти по сигналу с первого разряда циклического регистра 42.

. По сигналу с второго разряда циклического регистра 42 в реверсивиый счетчик 5 заносится состояние ячейки блока памяти, адрес которой соответствует двоичному коду счетчика 33

Если иа выходе элемента И 3 образуется I, то производится увеличение или умеиьшение иа 1 содержимого реверсивного счетчика 5 в зависимости от значения сигнала (О или 1) на выходе блока 39 сравнения. Указанная операция производится по сигналу с выхода третьего разряда циклического регистра 42, подаваемого, на тактовый вход счетчика 5.

По сигиалу записи с выхода четвертого разряда регистра 42 новое значение кода счетчика 5 записывается в ту же ячейку блока 7 памяти. Затем вновь происходит изменение адреса и т.д. Таким образом, за 4 (N-1) тактов работы генератора 44 в N ячейках блока 7 памяти образуются первые значения В согласно (4). Затем счет чик 33 обнуляется и иачинается формирование новых значений В, для всех

N гармоник.

Аналогичным образом функционирует

счетчик 6, блок 8 памяти и блок 40 сравнения при вычислении А. В течение времени анализа Т в блоках 7 и 8 памяти накапливаются значения Фурье - компонент А и Вц.

278885

Формула

8

изобретения

5

Ю

J5

20

25

30

35

40

45

50

55

Псевдостохастический анализатор спектра, содержащий генератор тактовых импульсов, вход запуска которого объединен с входом формирователя IJM- пульсов и является входом запуска анализатора, первый и второй реверсивные счетчики, счетные входы которых подключены к выходам соответственно первого и второго псевдостохастического умножителей, первые входы которых подключены к выходу преобразователя напряжения в псевдослучай- ную последовательность импульсов, информационный вход которого является информационным входом анализатора, первый и второй регистры сдвига, выход первого регистра сдвига подключен к выходам первого и второго блоков элементов И, выходы которых подключены к информационным входам соответственно первого и второго коммутаторов, выход второго регистра сдвига подключен к входу третьего и четвертого блоков элементов И, выходы третьего блока элементов И подключены к соответствующим входам элемента ИЛИ, элемент НЕ, о т л и- чающийся тем, что, с целью упрощения анализатора, он содержит RS-триггер, группу элементов НЕ, циклический регистр сдвига, регистр, третий регистр сдвига, пятый блок элементов И, два блока сравнения, счетчик адреса, три блока памяти, сумматор, пять коммутаторов, дешифратор, второй, третий и четвертый элементы НЕ, шесть элементов И и, иуль-орган, выход которого подключен к первым входам первого и второго блоков сравнения, выходы которых подключены к входам управления направлением счета соответственно первого и второго реверсивных счетчиков, информационные выходы которых подключены к информационным входам соответственно первого и второго блоков памяти, выходы которых подключены к информационным входам соответственно первого и второго реверсивных счетчиков,- выходы старших разрядов которых объединены и подключены к первому информационному входу третьего коммутатора, выход которого подключен к информационньм входам первого разряда первого и второго блоков памяти, адресные входы которых объединены с адресным входом

91

третьего блока памяти, первым входом сумматора и подключены к информационному выходу счетчика адреса, выход переполнения которого подключен к тактовым входам первого, второго и третьего регистров сдвига и R-входу RS-триггера, выход которого подключен к входам обнуления регистра, первого и второго реверсивных счетчиков и управляющему входу третьего коммутатора, второй информационный вход которого является входом задания логической единицы анализатора, выход генератора тактовых импульсов подключен к тактовому входу циклического регистра сдвига, выход первого разряда которого подключен к счетному входу счетчика адреса, установочный .вход которого объединен с установочными входами первого, второго и третьего сдвиговых регистров с входом разрешения записи циклического регистра сдвига и подключен к выходу формирователя импульсов, выход второго разряда циклического регистра сдвига подключен к установочным входам первого и второго реверсивных счетчиков и установочным входом регистра, информационньй выход которого подключен к управляющим входам первого, второго, четвертого и пятого коммутаторов и информационному входу третьего блока памяти, выход которого подключен к второму входу сумматора, выход которого подключен к информационному входу регистра, выходы двух старших разрядов которого подключены к соответствующим входам дешифратора, выход которого подключен к вторым входам первого и второго блоков сравнения и управляющим входам шестого и седьмого коммутаторов, выходы которых подключены к вторым входам соответственно первого и второго псевдостохастических умножителей, выход третьего регистра сдвига подключен к входу пятого блока элементов И и входу уп- равления преобразованием преобразователя Напряжения в псевдослучайную последовательность импульсов, информационный вход которого объединен с

78885 .

первым входом нуль-органа, второй вход которого является входом зада- ния логического нуля анализатора, выходы четвертого и пятого блоков

g элементов И подключены к информационным входам соответственно четвертого и пятого коммутаторов, S-вход RS триггера объединен с входом формирователя импульсов, выход третьего

10 .разряда циклического регистра сдвига подключен к входам синхронизации первого и второго реверсивных счет- чикоЬ, выход четвертого разряда циклического регистра сдвига подключеJ5 ны к входам чтения/записи первого, второго и третьего блоков памяти, выходы второго и первого коммутаторов, подключены к входам соответственно первого и второго элементов НЕ

20 группы и соответственно первому и второму входам первого элемекта И, выход которого подключен к входу первого элемента НЕ, выход которого подключен к первому входу второго

5 элемента И, выходы четвертого и пятого коммутаторов подключень) к входам соответственно третьего и четвертого элементов НЕ группы, и соответственно первому и второму входам

30 третьего элемента И, выход которого подключен к входу второго элемента НЕ, выход . которого подключен к второму входу второго элемента И, выход которого подключен к первым информа35 ционным входам шестого и седьмого коммутаторов, вторые информационные входы которых подключены к выходу четвертого элемента И, первый и второй входы которого подключены к вы40 ходам соответственно третьего и четвертого элементов НЕ, входы которых подключены к выходам соответственно пятого и шестого элементов И, выход элемента ИЛИ подключен к третьему

45 входу третьего элемента И и первому входу шестого элемента И, второй и третий входы которого подключены к выходам соответственно второго и четвертого элементов НЕ группы, выхода

50 первого и третьего элементов НЕ группы подключены соответственно к первому и второму входам пятого элементам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты погружного электродвигателя от анормальных режимов | 1985 |

|

SU1302369A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Псевдостохастический интегратор | 1981 |

|

SU962938A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Псевдостохастическое устройство для выполнения математических операций | 1983 |

|

SU1233151A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Устройство для извлечения корня @ -й степени | 1984 |

|

SU1223225A2 |

| УСТРОЙСТВО для ПРОСТРАНСТВЕННО-ВРЕМЕННОГО СЕЙСМИЧЕСКОГО АНАЛИЗА | 1973 |

|

SU393742A1 |

| Устройство для защиты погружного электродвигателя от анормальных режимов | 1986 |

|

SU1453511A1 |

Изобретение относится к вычислительной технике и предназначено для спектрального анализа сигналов в реальном масштабе времени. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что анализатор состоит из преобразователя напряжения в псевдослучайную последовательность импуль сов, двух псевдостохастических умножителей, двух реверсивных счетчиков, трех блоков памяти, трех регистров сдвига, пяти блоков элементов И, семи коммутаторов, элемента ИЛИ, шести элементов И, четырех элементов НЕ, счетчика адреса, с мматора, дешифратора, группы элементов ИЕ, двух блоков сравнения, нуль-органа, циклического регистра сдвига, регистра, генератора тактовых импульсов, триггера, формирователя импульсов. 1 ил. с S 1Чд 00 00 00 ел

| СПОСОБ ТОПОМЕТРИИ ДЛЯ РЕНТГЕНОТЕРАПЕВТИЧЕСКОГО ЛЕЧЕНИЯ ПАНКРЕАТИТА | 2004 |

|

RU2277377C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения прессовочного кускового сахара | 1948 |

|

SU75997A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-12-23—Публикация

1985-04-11—Подача