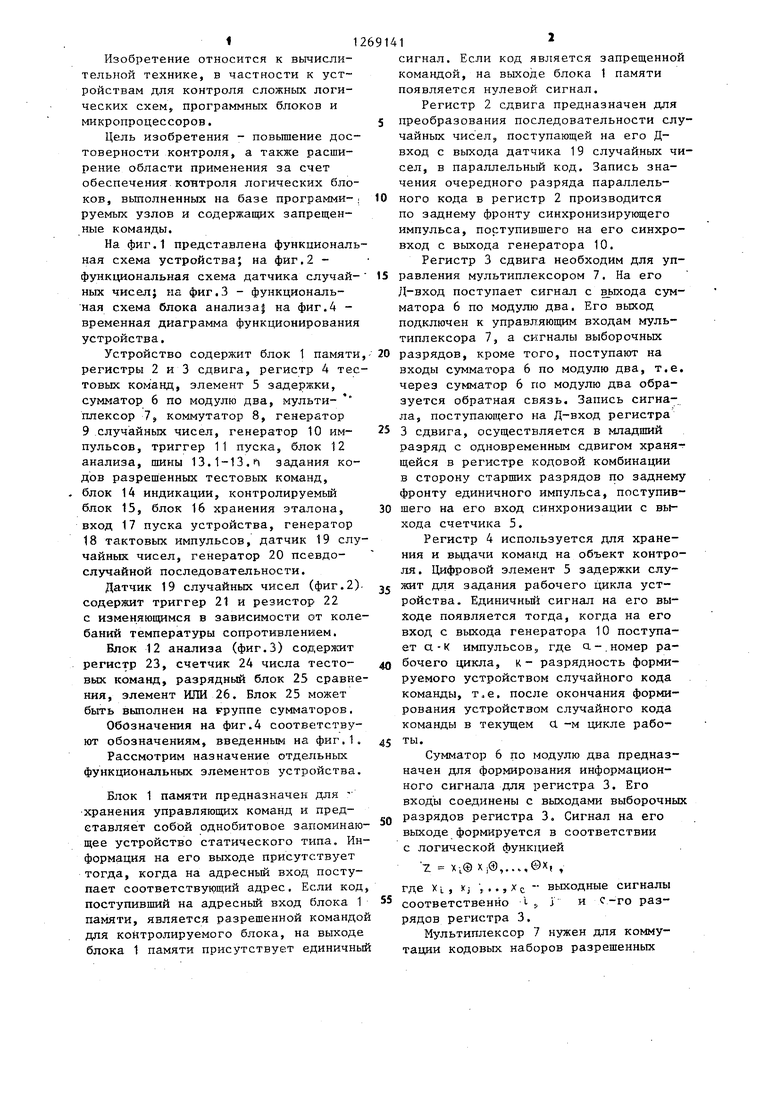

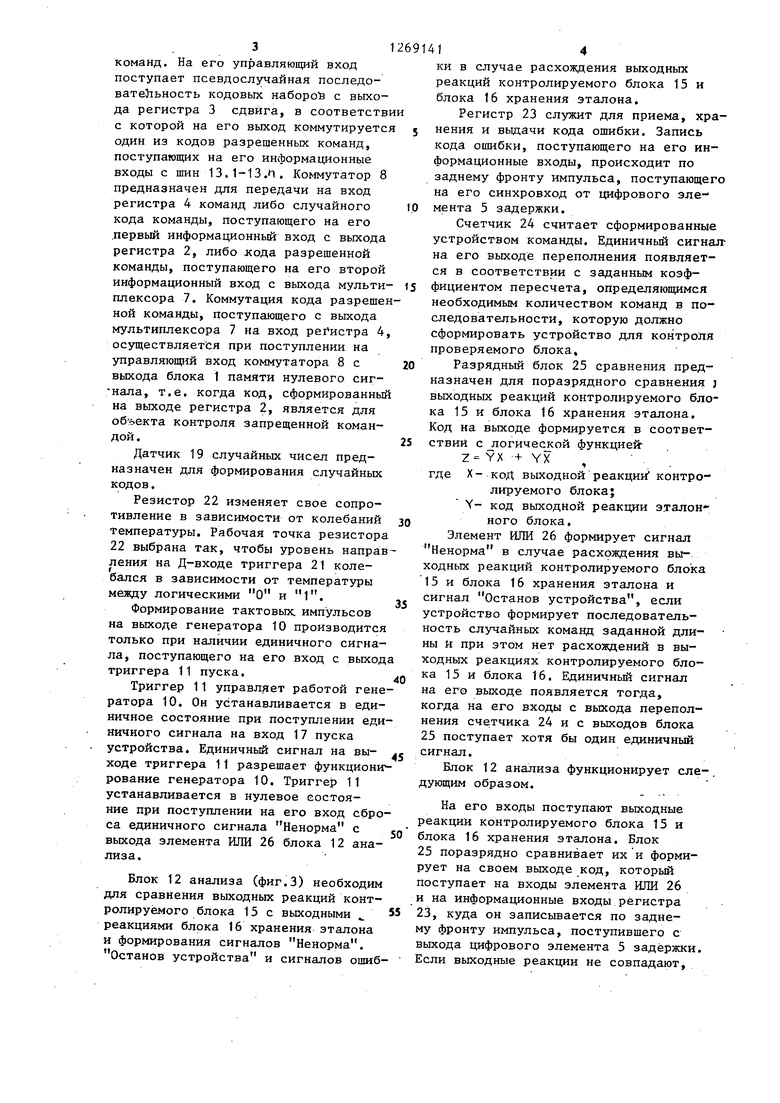

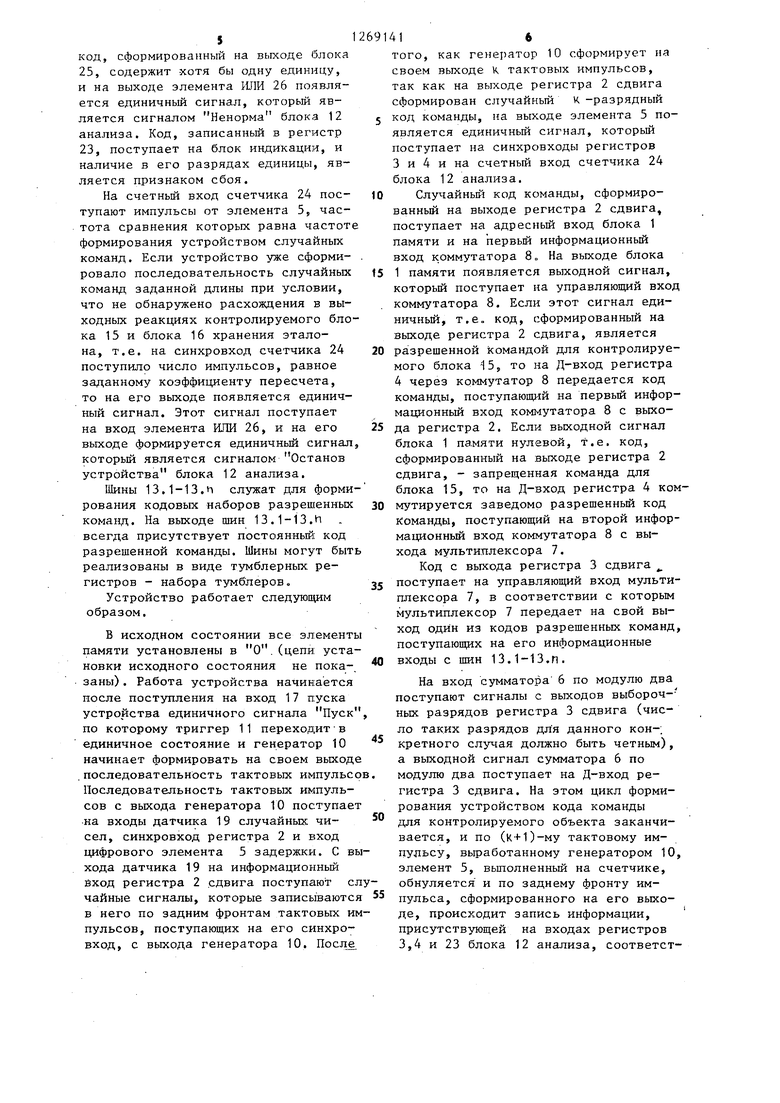

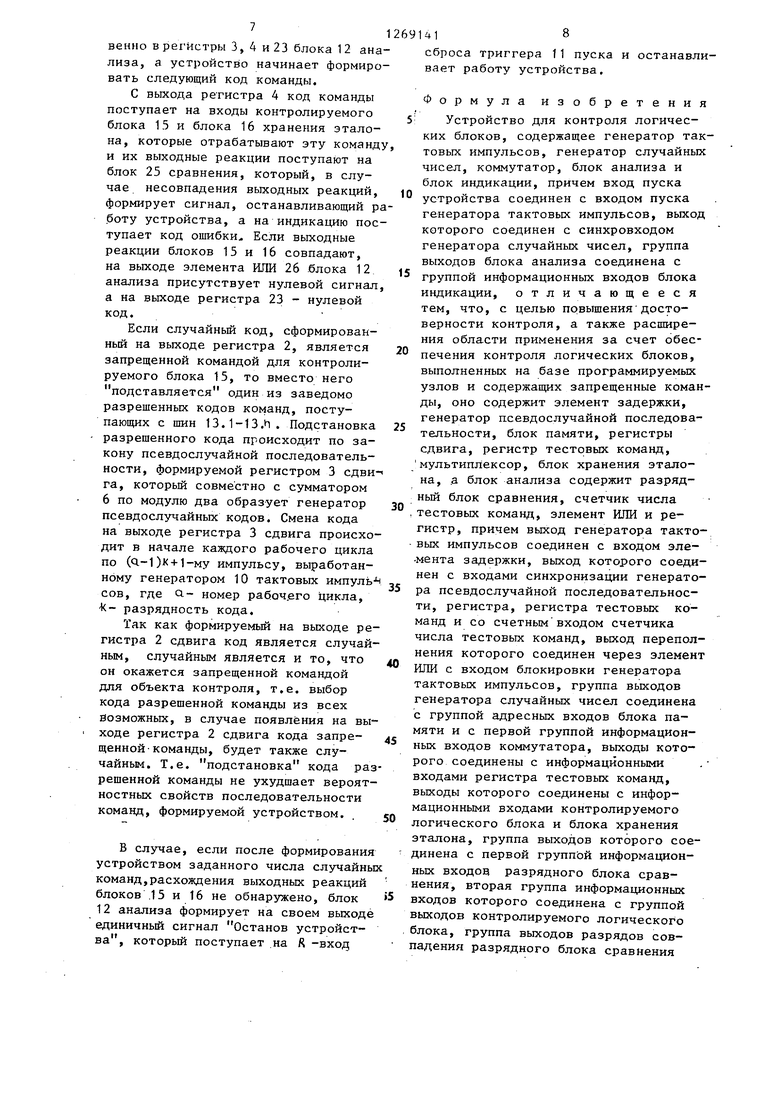

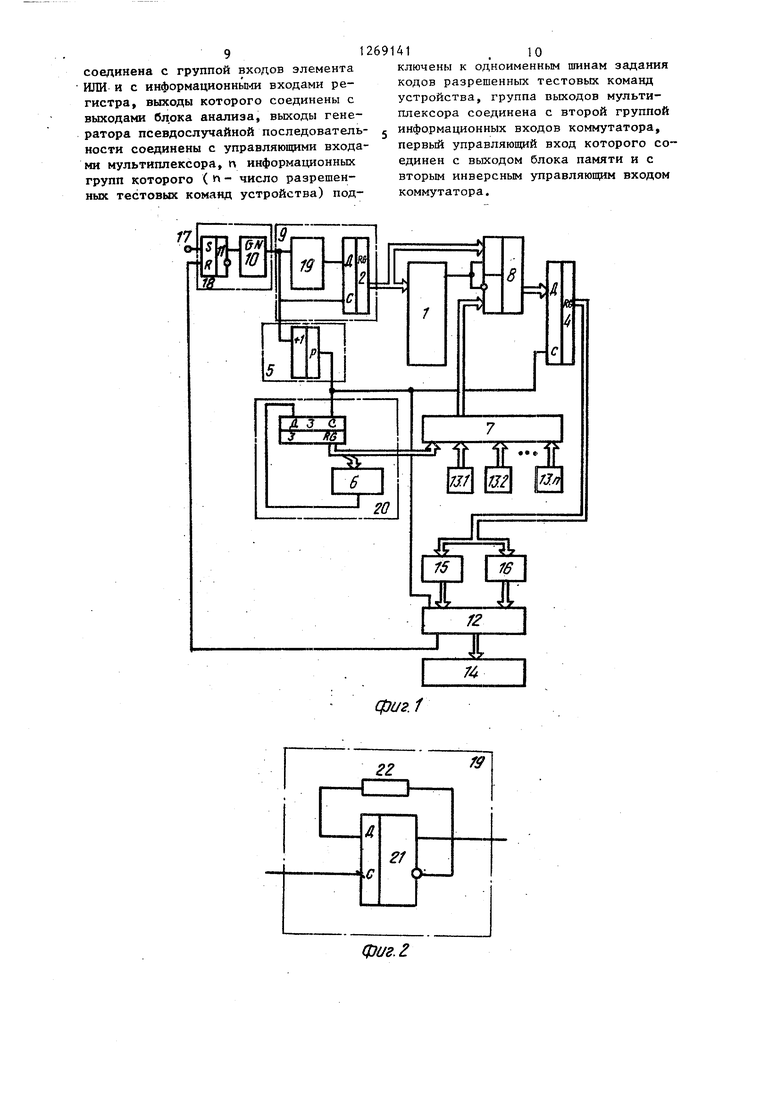

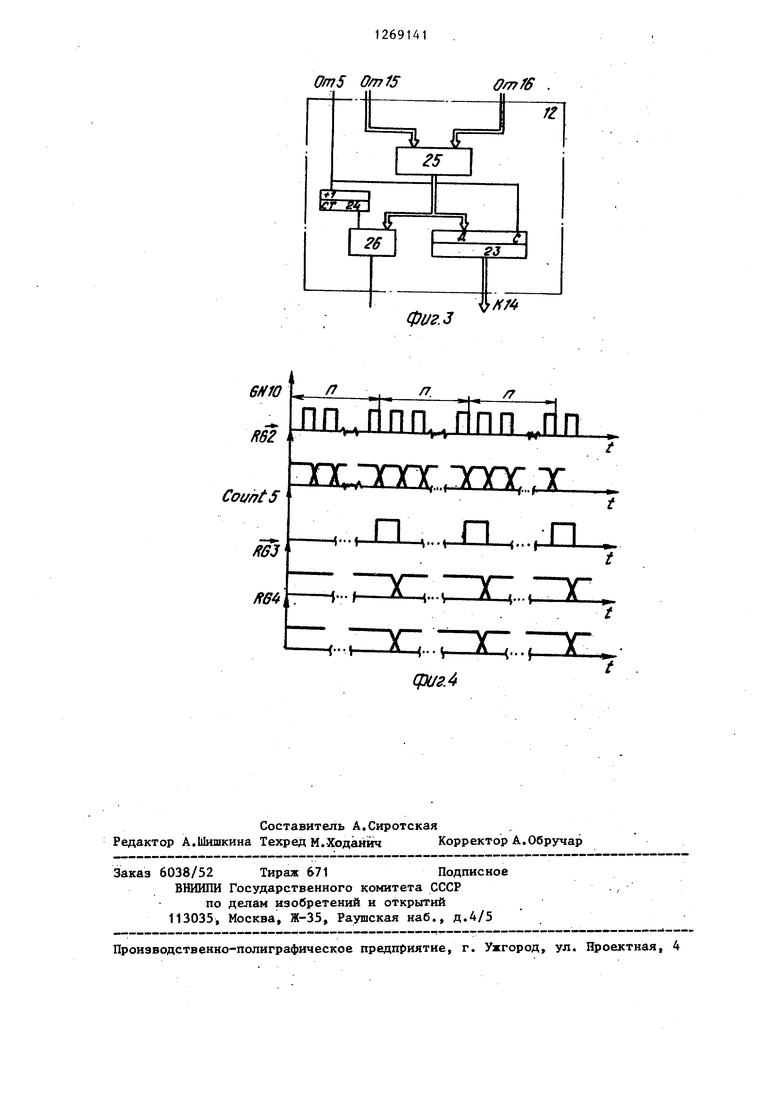

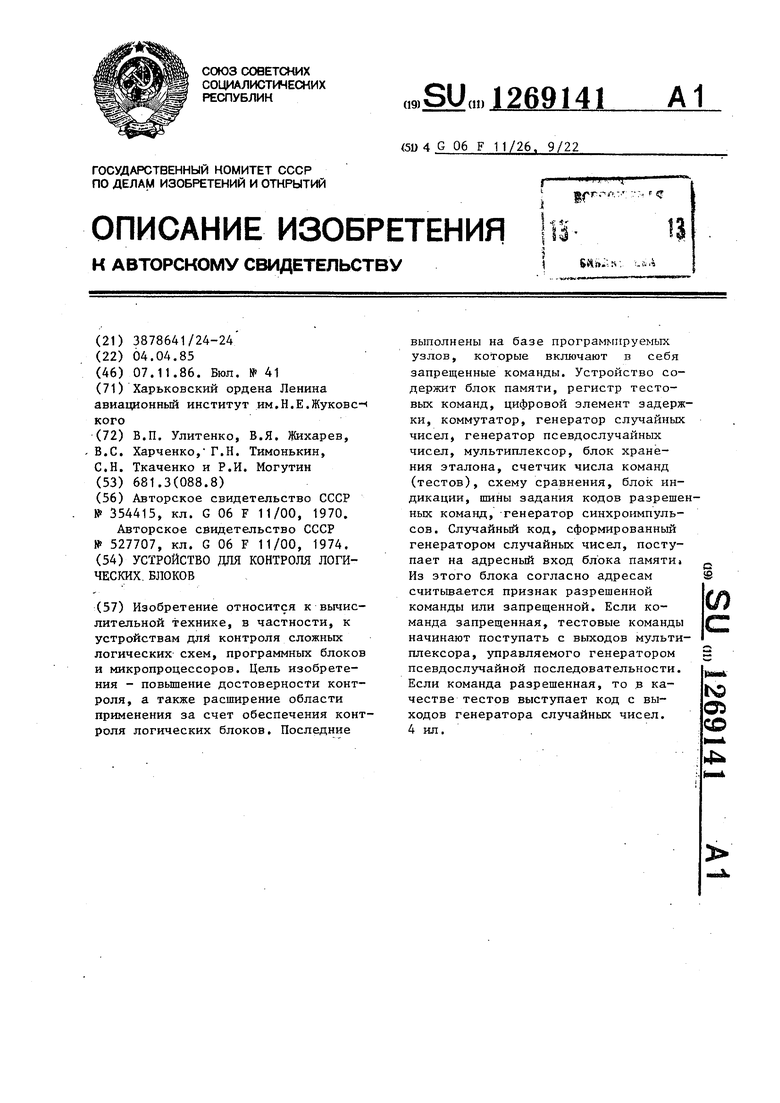

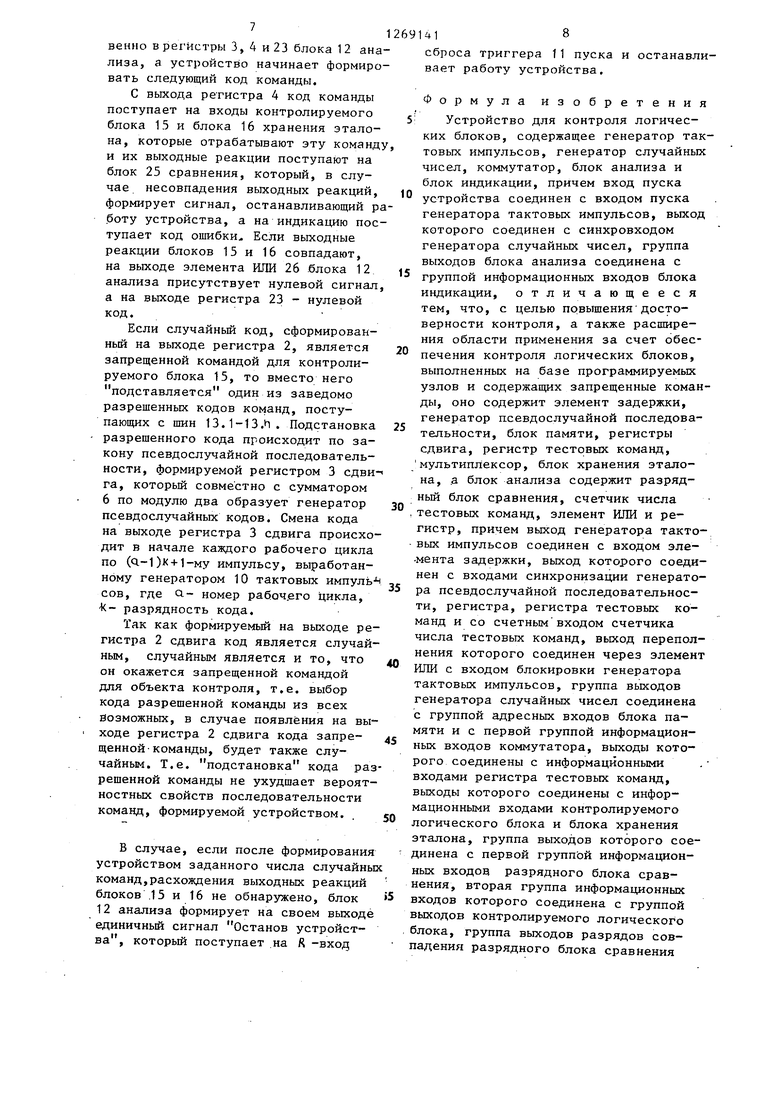

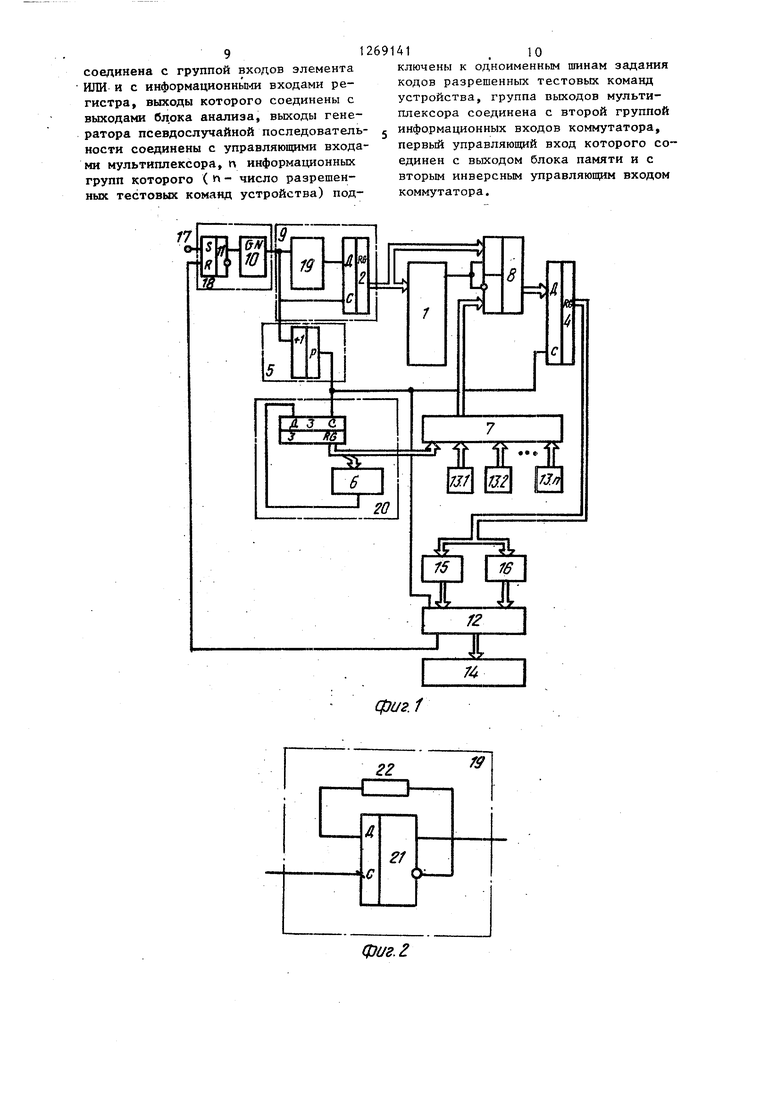

Изобретение относится к вычислительной технике, в частности к устройствам для контроля сложных логических схем, программных блоков и микропроцессоров. Цель изобретения - повьшение дос товерности контроля, а также расширение области применения за счет обеспечения контроля логических бло ков, вьтолненных на базе программируемых узлов и содержащих запрещенные команды. На фиг.1 представлена функционал ная схема устройства; на фиг.2 функциональная схема датчика случай ных чисел} на фиг.З - функциональная схема блока анализа| на фиг.4 временная диаграмма функционировани устройства. Устройство содержит блок 1 памяти,- 20 регистры 2 и 3 сдвига, регистр 4 тес товых команд, элемент 5 задержки, сумматор 6 по модулю два, мультиплексор 7, коммутатор 8, генератор 9 случайных чисел, генератор 10 импульсов, триггер 11 пуска, блок 12 анализа, шины 13.1-13.il задания кодов разрешенных тестовых команд, блок 14 индикации, контролируемый блок 15, блок 16 хранения эталона, вход 17 пуска устройства, генератор 18 тактовых импульсов, датчик 19 слу чайных чисел, генератор 20 псевдослучайной последовательности. Датчик 19 случайных чисел (фиг.2). содержит триггер 21 и резистор 22 с изменяющимся в зависимости от коле баний температуры сопротивлением. Блок 12 анализа (фиг.З) содержит регистр 23, счетчик 24 числа тестовых команд, разрядный блок 25 сравне ния, элемент ИЛИ 26. Блок 25 может быть выполнен на группе сумматоров. Обозначения на фиг.4 соответствуют обозначениям, введенным на фиг.1, Рассмотрим назначение отдельных функциональных элементов устройства. Блок 1 памяти предназначен для хранения управляющих команд и представляет собой однобитовое запоминаю щее устройство статического типа. Ин формация на его выходе присутствует тогда, когда на адресный вход поступает соответствующий адрес. код поступивший на адресньш вход блока 1 памяти, является разрешенной командо для контролируемого блока, на выходе блока 1 памяти присутствует единичньй сигнал. Если код является запрещенной командой, на выходе блока 1 памяти появляется нулевой сигнал. Регистр 2 сдвига предназначен для преобразования последовательности случайных чисел, поступающей на его Двход с выхода датчика 19 случайных чисел, в параллельный код. Запись значения очередного разряда параллельного кода в регистр 2 производится по заднему фронту синхронизирующего импульса, поступившего на его синхровход с выхода генератора 10. Регистр 3 сдвига необходим для управления мультиплексором 7. На его Д-вход поступает сигнал с вькода сумматора 6 по модулю два. Его выход подключен к управляющим входам мультиплексора 7, а сигналы выборочных разрядов, кроме того, поступают на входы сумматора 6 по модулю два, т.е. через сумматор 6 по модулю два образуется обратная связь. Запись сигнала, поступающего на Д-вход регистра 3 сдвига, осуществляется в младший разряд с одновременным сдвигом хранящейся в регистре кодовой комбинации в сторону старших разрядов по заднему фронту единичного импульса, поступившего на его вход синхронизации с выхода счетчика 5. Регистр 4 используется для хранения и выдачи команд на объект контроля. Цифровой элемент 5 задержки служит для задания рабочего цикла устройства. Единичный сигнал на его выходе появляется тогда, когда на его вход с выхода генератора 10 поступает а -К импульсов, где а- номер рабочего цикла, к- разрядность формируемого устройством случайного кода команды, т.е. после окончания формирования устройством случайного кода команды в текущем О. -м цикле работы. Сумматор 6 по модулю два предназначен для формирования информационного сигнала для регистра 3. Его входы соединены с выходами выборочных разрядов регистра 3. Сигнал на его выходе формируется в соответствии с логической функцией Z х-,® Xi@©X, , где XL, Xj ,..jXc выходные сигналы и с-го разсоответственнорядов регистра 3. Мультиплексор 7 нужен для коммутации кодовых наборов разрешенных команд. На его управляющий вход поступает псевдослучайная последоватейьность кодовых наборов с выхода регистра 3 сдвига, в соответств с которой на его выход коммутируетс один из кодов разрешенных команд, поступаязщих на его информационные входы с шин 13.1-13.1 . Коммутатор 8 предназначен для передачи на вход регистра 4 команд либо случайного кода команды, поступающего на его .первьй информационньй вход с выхода регистра 2, либо кода разрешенной команды, поступающего на его второй информационный вход с выхода мульти плексора 7. Коммутация кода разреше ной команды, поступаюш.его с выхода мультиплексора 7 на вход рех истра 4 осуществляется при поступлении на управляющий вход коммутатора 8с выхода блока 1 памяти нулевого сигнала, т.е. когда код, сформированньш на выходе регистра 2, является для объекта контроля запрещенной командой . Датчик 19 случайных чисел предназначен для формирования случайных кодов. Резистор 22 изменяет свое сопротивление в зависимости от колебаний температуры. Рабочая точка резистор 22 выбрана так, чтобы уровень напра ления на Д-входе триггера 21 колебался в зависимости от температуры между логическими О и 1. Формирование тактовых, импульсов на выходе генератора 10 производится только при наличии единичного сигнала, поступающего на его вход с выход триггера 11 пуска. Триггер 11 управляет работой гене ратора 10. Он устанавливается в единичное состояние при поступлении еди ничного сигнала на вход 17 пуска устройства. Единичный сигнал на выходе триггера 11 разрешает функциони рование генератора 10. Триггер 11 устанавливается в нулевое состояние при поступлении на его вход сбро са единичного сигнала Ненорма с выхода элемента ИЛИ 26 блока 12 анализа. Блок 12 анализа (фиг.З) необходим для сравнения выходных реакций контролируемого блока 15 с выходными реакциями блока 16 хранения эталона и формирования сигналов Ненорма. Останов устройства и сигналов ошиб ки в случае расхождения выходных реакций контролируемого блока 15 и блока 16 хранения эталона. Регистр 23 служит для приема, хранения и выдачи кода ошибки. Запись кода ошибки, поступающего на его информационные входы, происходит по заднему фронту импульса, поступающего на его синхровход от цифрового элемента 5 задержки. Счетчик 24 считает сформированные устройством команды. Единичный сигнална его выходе переполнения появляется в соответствии с заданным коэффициентом пересчета, определяющимся необходимым количеством команд в последовательности, которую должно сформировать устройство для контроля проверяемого блока. Разрядный блок 25 сравнения предназначен для поразрядного сравнения j выходных реакций контролируемого блока 15 и блока 16 хранения эталона. Код на выходе формируется в соответствии с лoгичecJкoй функциейZ YX + YX , где Х- код выходной реакций контролируемого блока; Y- код выходной реакции эталонного блока. Элемент ИЛИ 26 формирует сигнал Ненорма в случае расхождения выходных реакций контролируемого блока 15 и блока 16 хранения эталона и сигнал Останов устройства, если устройство формирует последовательность случайных команд заданной длины и при этом нет расхождений в выходных реакциях контролируемого блока 15 и блока 16. Единичный сигнал на его выходе появляется тогда, когда на его входы с выхода переполнения счетчика 24 и с выходов блока 25 поступает хотя бы один единичный сигнал. Блок 12 анализа функционирует еле-. дукицим образом. На его входы поступают выходные реакции контролируемого блока 15 и блока 16 хранения эталона. Блок 25 поразрядно сравнивает их и формирует на своем выходе код, который поступает на входы элемента ИЛИ 26 на информационные входы регистра 23, куда он записывается по заднеу фронту импульса, поступившего с выхода цифрового элемента 5 задержки. сли выходные реакции не совпадают. код, сформированный на выходе блока 25, содержит хотя бы одну единицу, и на выходе элемента Ш1И 26 появляется единичный сигнал, который является сигналом Ненорма блока 12 анализа. Код, записанный в регистр 23, поступает на блок индикации, и наличие в его разрядах единицы, является признаком сбоя. На счетный вход счетчика 24 поступают импульсы от элемента 5, частота сравнения которых равна частот формирования устройством случайных команд. Если устройство уже сформировало последовательность случайных команд заданной длины при условии, что не обнаружено расхождения в выходных реакциях контролируемого бло ка 15 и блока 16 хранения эталона, т.е. на синхровход счетчика 24 поступило число импульсов, равное заданному коэффициенту пересчета, то на его выходе появляется единичный сигнал. Этот сигнал поступает на вход элемента ИЛИ 26, и на его выходе формируется единичный сигнал который является сигналом Останов устройства блока 12 анализа. Шины 13.1-13.h служат для форми рования кодовых наборов разрешенных команд. На выходе шин 13.1-i3.h всегда присутствует постоянный код разрешенной команды. Шины могут быт реализованы в виде тумблерных регистров - набора тумблеров. Устройство работает следующим образом. В исходном состоянии все элемент памяти установлены в О.(цепи уста новки исходного состояния не показаны) . Работа устройства начинается после поступления на вход 17 пуска устройства единичного сигнала Пуск по которому триггер 11 переходитв единичное состояние и генератор 10 начинает формировать на своем выход .последовательность тактовых импульс Последовательность тактовых импульсов с выхода генератора 10 поступае на входы датчика 19 случайных чисел, синхровход регистра 2 и цифрового элемента 5 задержки. С в хода датчика 19 на информационньй йход регистра 2 сдвига поступают с чайные сигналы, которые записываютс в него по задним фронтам тактовых и пульсов, поступающих на его синхровход, с выхода генератора 10. Посл того, как генератор 10 сформирует на своем выходе к тактовых импульсов, так как на выходе регистра 2 сдвига сформирован случайный К -разрядный код команды, на выходе элемента 5 появляется единичньш сигнал, который поступает на синхровходы регистров 3и 4 и на счетный вход счетчика 24 блока 12 анализа. Случайный код команды, сформированный на выходе регистра 2 сдвига, поступает на адресный вход блока 1 памяти и на первый информационньй вход коммутатора 8. На выходе блока 1 памяти появляется выходной сигнал, который поступает на управляющий вход коммутатора 8. Если этот сигнал единичньй, т.е. код, сформированный на выходе регистра 2 сдвига, является разрешенной командой для контролируемого блока 15, то на Д-вход регистра 4через коммутатор 8 передается код команды, поступающий на первый информационный вход KOMJ iyTaTopa 8 с выхода регистра 2. Если выходной сигнал блока 1 памяти нулевой, т.е. код, сформированный на выходе регистра 2 сдвига, - запрещенная команда для блока 15, то на Д-вход регистра 4 коммутируется заведомо разрешенный код Команды, поступающий на второй информационный вход коммутатора 8 с выхода мультиплексора 7. Код с выхода регистра 3 сдвига поступает на управляющий вход мультиплексора 7, в соответствии с которым мультиплексор 7 передает на свой выход один из кодов разрешенных команд, поступающих на его информационные входы с шин 13.1-13.п. На вход сумматора 6 по модулю два поступают сигналы с выходов выборочных разрядов регистра 3 сдвига (число таких разрядов для данного кон-; кретного случая должно быть четным), а выходной сигнал сумматора 6 по модулю два поступает на Д-вход регистра 3 сдвига. На этом цикл формирования устройством кода команды для контролируемого объекта заканчивается, и по (к+1)-му тактовому импульсу, вьфаботанному генератором 10, элемент 5, выполненный на счетчике, обнуляется и по заднему фронту импульса, сформированного на его выходе, происходит запись информации, присутствующей на входах регистров 3,4 и 23 блока 12 анализа, соответственно в регистры 3, 4 и 23 блока 12 ана лиза, а устройство начинает формиро вать следующий код команды. С выхода регистра 4 код команды поступает на входы контролируемого блока 15 и блока 16 хранения эталона, которые отрабатывают эту команд и их выходные реакции поступают на блок 25 сравнения, который, в случае несовпадения выходных реакций, формирует сигнал, останавливающий р боту устройства, а на индикацию пос тупает код ошибки Если выходные реакции блоков 15 и 16 совпадают, на выходе элемента ИЛИ 26 .блока 12 анализа присутствует нулевой сигнал а на выходе регистра 23 - нулевой код. Если случайньй код, сформированный на выходе регистра 2, является запрещенной командой для контролируемого блока 15, то вместо него подставляется один из заведомо разрешенных кодов команд, поступающих с шин 13.1-13.h . Подстановка разрешенного кода происходит по закону псевдослучайной последовательности, формируемой регистром 3 сдви га, который совместно с сумматором 6 по модулю два образует генератор псевдослучайных кодов. Смена кода на выходе регистра 3 сдвига происхо дит в начале каждого рабочего цикла по (о.-1)к + 1-му импульсу, выработанному генератором 10 тактовых импуль сов, где о.- номер рабоч.его цикла, -К- разрядность кода. Так как формируемый на вькоде ре гистра 2 сдвига код является случай ным, случайным является и то, что он окажется запрещенной командой для объекта контроля, т.е. выбор кода разрешенной команды из всех Возможных, в случае появления на вы ходе регистра 2 сдвига кода запрещенной -команды, будет также случайным. Т.е. подстановка кода ра решенной команды не ухудшает вероят ностных свойств последовательности команд, формируемой устройством. . В случае, если после формирования устройством заданного числа случайны команд,расхождения выходных реакций блоков .15 и 16 не обнаружено, блок 12 анализа формирует на своем выходе единичный сигнал Останов устройства, который поступает .на Я сброса триггера 11 пуска и останавливает работу устройства. Формула изобретения Устройство для контроля логических блоков, содержащее генератор тактовых импульсов, генератор случайных чисел, коммутатор, блок анализа и блок индикации, причем вход пуска устройства соединен с входом пуска генератора тактовых импульсов, выход которого соединен с синхровходом генератора случайных чисел, группа выходов блока анализа соединена с группой информационных входов блока индикации, отличающееся тем, что, с целью повышениядостоверности контроля, а также расширения области применения за счет обеспечения контроля логических блоков, выполненных на базе программируемых узлов и содержащих запрещенные команды, оно содержит элемент задержки, генератор псевдослучайной последовательности, блок памяти, регистры сдвига, регистр тестовых команд, мультиплексор, блок хранения эталона, а блок анализа содержит разрядный блок сравнения, счетчик числа тестовых команд, элемент ШШ и регистр, причем выход генератора тактовых импульсов соединен с входом элемента задержки, выход которого соединен с входами синхронизации генератора псевдослучайной последовательности, регистра, регистра тестовых команд и со счетньмвходом счетчика числа тестовых команд, выход переполнения которого со.единен через элемент ИЛИ с входом блокировки генератора тактовых импульсов, группа выходов генератора случайных чисел соединена с группой адресных входов блока памяти и с первой группой информационных входов коммутатора, выходы которого соединены с информационными входами регистра тестовых команд, выходы которого соединены с информационными входами контролируемого логического блока и блока хранения эталона, группа выходов которого соединена с первой группой информационных входов разрядного блока сравнения, вторая группа информационных входов которого соединена с группой выходов контролируемого логического блока, группа выходов разрядов совпадения разрядного блока сравнения

91

соединена с группой входов элемента ИЛИ и с информационньп ш входами регистра, выходы которого соединены с выходами блока анализа, выходы генератора псевдослучайной последовательности соединены с управляющими входами мультиплексора, rv информационных групп которого (- число разрешенных тестовых команд устройства) под69141 10

ключены к одноименным шинам задания кодов разрешенных тестовых команд устройства, группа выходов мультиплексора соединена с второй группой

с информационных входов коммутатора, первый управляющий вход которого соединен с выходом блока памяти и с вторым инверсным управляющим входом коммутатора.

фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

Изобретение относится к вычислительной технике, в частности, к устройствам для контроля сложных логических схем, программных блоков и микропроцессоров. Цель изобретения - повьшение достоверности контроля, а также расширение области применения за счет обеспечения контроля логических блоков. Последние выполнены на базе программируемых узлов, которые включают в себя запрещенные команды. Устройство содержит блок памяти, регистр тестовых команд, цифровой элемент задержки, коммутатор, генератор случайных чисел, генератор псевдослучайных чисел, мультиплексор, блок хранения эталона, счетчик числа команд (тестов), схему сравнения, блок индикации, шины задания кодов разрешенных команд, -генератор синхроимпульсов. Случайный код, сформированный генератором случайных чисел, поступает на адресный вход блока памяти. Из этого блока согласно адресам считьшается признак разрешенной команды или запрещенной. Если команда запрещенная, тестовые команды начинают поступать с выходов мультиплексора, управляемого генератором псевдослучайной последовательности. Если команда разрешенная, то в честве тестов выступает код с выО5 ходов генератора случайных чисел. СО 4 ил. 4

fff

Л .С

фиг. г

От 5 От 15

- U :J :J

пп,, ,,f1n

л Лу- Д Aj.i.f 1-f...Ли...Д1....Д1

OmfS .

фиг.з

ф{/.4

| УСТРОЙСТВО для ПРОВЕРКИ ФУНКЦИОНИРОВАНИЯ ЛОГИЧЕСКИХ СХЕМ | 0 |

|

SU354415A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для статистического контроля логических блоков | 1974 |

|

SU527707A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1985-04-04—Подача