блока запуска соединены соответственно с вторыми входами третьего, пятого и седьмого элементов ИЛИ второго блока запуска.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля времени выполнения программ | 1982 |

|

SU1059575A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для выбора работоспособной структуры вычислительного комплекса | 1980 |

|

SU1037256A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Устройство для отладки и контроля хода программ | 1988 |

|

SU1529227A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

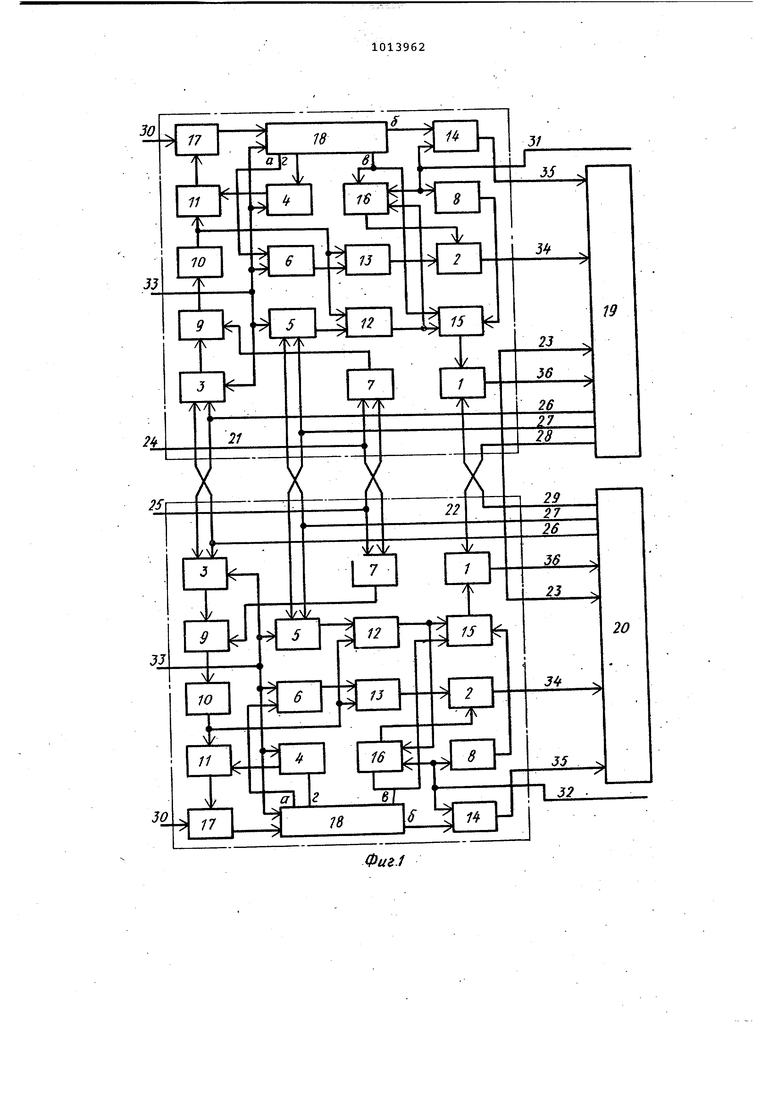

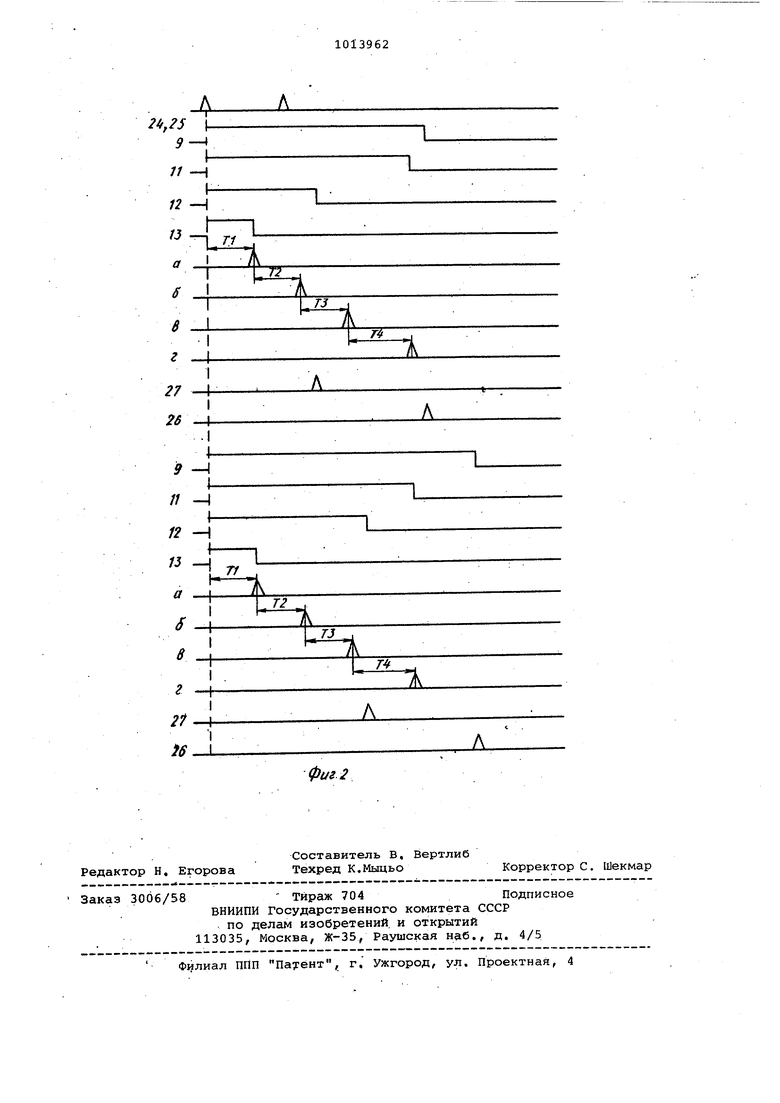

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВУХПРОЦЕССОРНОЙ СИСТЕМЫ, содержащее два блока запуск.а, каждый из которых содержит счетчик времени,четыре элемента И, два -элемента ИЛИ, элемент .НЕ, триггер начального пуска, триггер контроля пуска и триггер сброса процессора, причем первый выход счетчика времени соединен.с первых входом первого-элемента И, выход которого и выход триггера сб1роса процессора подключены соответственно к первому и второму входам первого элемента ИЛИ, а выход элемента НЕ подключен К первому входу . второго эле1мента И, о т л и ч а ющ е е с я тем, что, с целью расширения области применения устрой.ства, в каждый блок запуска введены пять элементов ИЛИ, триггер пуска счетчика времени и формирователь одиночного импульса, причем в каждом блоке запуска второй выхрд счетчика времени соединен с первым .входом третьего элемента И, выход которого соединен с соответствуют щей выходной шиной начального пуска контролируемого процессора, а второй вход - с соответствующей входной шиной установки режима контролируемого процессора, вторым входом первого элемента И и входом элемента НЕ, первый выход счетчика времени подключен к второму входу второго элемента И, третий вход которого соединен с третьим входом первого элемента И и выходим.триггера, контроля пуска, а выход - с перВЕлм вхо.дом второго элемента ИЛИ, выходом ; соединенного с сеответствующей выходной шиной пуска после отказа устройства, а вторым входом - с соответствующей .входной шиной отказа . контролируелюго пр.оцёссора:, выход первого элемента ИЛИ соединен с соответствующей цшной:сброса контролируемого/процессора, счётный . . вход с етчика времени подключён к выходу четвертого элемента И, первым входом соединенного с соответствующей входной шиной тактовых импуль- сов устройства, вход сброса счетСО чика времени подключен к входной шине начального сброса устройства и первым входам третьедо, четвертого, пятого и шестого элементов ИЛИ,, выход третьего элемента ИЛИ подключен к первому, входу триггера начальног о пуска, второй вход KOTojSoro соединен с выходом седьмого элемента ИЛИ, а выход - через формирователь одиночного, импульса - с первыми входами триггера пуска счетчика времени, триггера сброса процессора и триггера ы Ф Ф to контроля йуска, вторые входы котррых подключены соответственно к выходам четвертого, шестого и пятого элемен- . тов. ИЛИ, третий и четвертый выходы счетчика времени соответственно соединены с вторыми входами шестого и четвертого элементов ИЛИ, выход триггера пуска -счетчика времени соединен .с вторым входом четвертого элемента И, вторые входы третьего и пятого элементов ИЛИ подключены к соответствующей группе входных шин синхронизации устройства, первый вход седьмого элемента ИЛИ соединен с соответствующей шиной пуска устройства, трбтьи входы третьего, пятого и второй вход седьмого элементов ИЛИ первого

Изобретение относится к вычислительной технике и может быть исполь зовано в системах обработки данных. Известно устройство контроля и повторного пуска ЦВМ, содержащее пр цессор, декодер, мультиплексор, два узла синхронизации, счетчик времени таймер сторожа и временной делитель и осуществляющее проверку наличия периодически выдаваемых выходных сигналов от ЦВМ при правильном выполнении программы. При отсутствии определенного числа этих периодичес ких сигналов вырабатывается сигнал повторного пуска этой же ЦВМ, Одновременно начинается отсчёт времен ного интервала, в конце которого вырабатывается сигнал управления, выдача которого (с одновременной периодической выдачей выходных сигналов означает нормальное функционирование ЦВМ после повторного запуск Если же в схеме контроля и повторно го пуска ЦВМ продолжается пропадани выходных сигналов во время отсчета временного интервала, то отсчет это временного интервала прекращается и блокируется выработка сигнала упр ления, что служит сигнализацией неправильной работы ЦВМ Cl. Недостаток этого устройства состо ит в низкой надежности, так как оно не обеспечивает продолжения нормального функционирования этой ЦВМ после возникновения отказа, а также при возникновении неисправности в цепи пуска ЦВМ, Наиболее близким к предлагаемому по технической сущности является устройство для синхронизации двухпроцессорной системы обработки данных, содержащее два блока синхронизации, соединенных управляющими выходами со входами первого и второго процессоров, входами - с соответствующими выходами блока переключения конфигурации,причем группа, выходов одного блока синхронизации подключена к группе синхронизирующих входов другого блока синхронизации. Каждый блок синхронизации содержит генератор синхросигналов, га.нератор часов, узел переключения генераторов, узел формирования син- хросерий и узел пересчета, причем первый и второй входа узла переключения генер&торов соответственно подключены к выходам генераторов синхросигнсшов первого и второго блоков синхронизации, третий и четвертый входы - соответственно к выходам генераторов часов первого и второго блоков синхронизации, пятый и шестой входы - к соответствующим входам блока переключения конфигураций , первый и второй выходы и седьмой и восьмой входы - соответственно к первым входам и выходам узла формирования синхросерий и узла пересчета того же блока синхронизации, вторые входы которых являются выходами блока синхронизации. Каждый узел переключения содержит шесть элементов и, два элемента ИЛИ, элемент задержки, элемент.НЕ, элемент И-НЕ, триггер ввода конфигураций, триггер подключения чужого процессора и триггер подключения своего процессора 2 , Недостаток известного устройства состоит в его ограниченной.области применения, так как оно не может обеспечить переключения процессоров, при их отказах или отказах цепей запуска. Целью изобретения является расширение области применения устройства. Поставленная цель достигается тем, что в устройство, содержащее два блока запуска, каждый из которых содержит счетчик времени, четыре эле мента И, два элемента ИЛИ, элемент НЕ, триггер начального пуска, триггер контроля пуска и триггер сброса процессора, причемпервый выход счетчика времени соединен с первым входом первого элемента И, выход которого и выход триггера сброса процессора подключены соответственно к первому и второму входам .первого элемента ИЛИ, а выход элемента НЕ подключен к первому входу второго элемента И, в каждый блок запуска введены пять элементов ИЛИ, триггер пуска счетчика времени и формирователь одиночного импульса, причем в каждом блоке запуска второй выход счетчика времени соединен с первым входом третьего элемента И, выход которого соединен с соответствующей выходной шиной начального пуска контролируемого процессора, а второй вход - с соответствующей входной шиной установки режима контролируемого процессора, вт.орым входом первого элемента И и входом элемента НЕ, первый выход счетчика времени подключен ко второму входу второго элемента И, третий вход которого соединен с третьим входом первого элемента И и выходом триггера контроля пуска, а вы ход - с первым входом второго элемента ИЛИ, выходом соединенного с соответствующей выходной шиной пуска после отказа устройства, а вторым входом - с соответствующей входной шиной отказа контролируемого процессора, выход первого элемента ИЛИ соединен -с соответствующей шиной сброса контролируемого процессора, счетный вход счетчика времени подключен к выходу четвертого элемента И, первым входом соединенного с соответствукяцей входной шиной тактовых импульсов устройства, вход сброса счетчика времени подключен ко входной шине начального сброса устройства и первым входам третьего четвертого, пятого и шестого элемен тов ИЛИ, выход третьего элемента ИЛИ подключе« к первому входу триггера начального пуска, второй вход которого соединен с выходом седьмог элемента ИЛИ, а выход - через форми рователь одиночного импульса - с первыми входами триггера пуска счет чика времени, триггера сброса проце сора и триггера контроля пуска, вторые входы которых подключены соответст.венно к выходам-четвертого, ше стого и пятого элементов ИЛИ, трети и четвертый выходы счетчика времени соответственно соединены со вторыми входами шестого и четвертого элемен тов ИЛИ, выход триггера пуска счетчика времени соединен со вторым вхо дом четвертого элемента И, вторые входы третьего и пятого элементов ИЛИ подключены к соответствующей группе входных шин синхронизации ус ройства, первый вход седьмого элемента ИЛИ соединен с соответствующей шиной пуска устройства, третьи входы третьего пятого и второй вхо седьмого элементов ИЛИ первого блока запуска соединены соответственно со вторыми входами третьего, пятого и седьмого элементов ИЛИ. второго блока запуска. На фиг, 1 представлена блок-схем .устройства; на фиг, 2 - временная диаграмма, поясняющая работу устрой ства. Устройство содержит в каждом бло ке запуска второй, первый, третий седьмой элементы ИЛИ 1-7, элемент Н 8, триггер 9 начального пуска, формирователь 10 одиночного импульса, триггер 11 пуска счётчика времени, триггер 12 контроля пуска, триггер 13 сброса процессора, третий, второй, первый и четвертый элементы И. 14-17, счетчик 18 времени, первый и второй процессоры 19 и 20, первый и второй блоки 21 и 22 запуска, шину 23 взаимодействия процессоров 19 и 20, входные шины 24 и 25 пуска устройства, шины 26 и 27 групп входных шин синхронизации устройства, входные шины 28 и 29 отказа процессора устройства, входные шины 30 тактовых импульсов устройства, входные шины 31 и 32 установки режима процессоров устройства, выходную шину 33 начального сброса устройства, выходные шины 34 сброса процессора устройства, выходные шины 35 начального пуска процессора устройства и выходные шины 36 пуска после отказа процессора устройства, CJ, 5,-в ,г - третий, четвертый, первый и второй выходы счетчиков 18 времени соответственно. Ось абсцисс (фиг, 2) обозначает текущее время, а по оси ординат показаны состояния выходов элементов, позиции которых соответствуют обозначениям элементов, указанным на фиг, 1, Устройство работает следующим образом. После включения питания триггеры 9, 11, 12 и 13, счетчик 18 устанавливаются в исходное состояние {состояние 0 сигналом, приходящим по шине 33, Сигнал начального пуска по шине 24 либо по шине 25 через элементы ИЛИ 7 устанавливает в единичное состояние триггеры 9 блоков 21 и 22, Для повышения надежности запуска процессоров 19 и 20 шины 24 и 25 выполнены раздельно и независимо друг от друга. Максимально допустимый временной интервал между поступлением сигналов по этим шинам закладывается в nporpaivwy процес- . соров, и триггеры 9 блоков 21 и 22 устанавливаиотся в исходное состояние после поступления сигнала по шине 26, выработанного программой одного из процессоров, В каждом блоке 21 или 22 формирователь 10 вырабатывает одиночный импульс от переднего фронта при срабатывании триггера 9, Этим одиночным импульсом производится установка в единичное состояние триггеров 11, 12 и 13. Блок 21 работает следующим образом, V При этом номер блока 21 или 22 указывается только в тех случаях, когда может возникнуть неоднозначность) , Триггер 11 сигналом со своего единичного выхода открывает элемент И 17, и тактовые сигналы с шины 30 . поступают на счетный вход счетчика 18, который через определенные временные интервалы, показанные на :временной диаграмме фиг, 2, выраба:тывает управляющие сигналы а. S по и и о- 1 .Ofv., С ..единичного выходи триггера J.2 : сигнал подается на входы элементов ;И 15 и 16. : С единичного выхода триггера 13 сигнал подается на вход элемента ИЛ 2f с выхода которого этот сигнал поступает по шине 34 на входустановки своего процессора 19 в и.с ходное состояние, причем триггер 13 устанавливается в О через элемент ;ИЛЙ б сигналом а, выработанным счетчиком 18 через интервал времени :Т1 от момента появления первого сиг нала ria шине 24 либо на шине 25, ;Этот интервал времени должен быть Достаточен для надежного окончания всех переходных процессов.в процессоре по сигналу на шине 34. . Через интервал времени Т2 от мо мента выдачи сигнала « счетчик 18 вырабатывает сигнал d, который поступает на вход эд емента И 14, и, если на другом е1ю входе установ лен разрешающий потенциала с шины 31 сигнал начального пуска с выхода элемента И 14 по шине 35 поступает -В процессор 19 и производит его первоначальный запуск, В процессор. 20 аналогичный сигнал S в блоке 22 не пройдет, так как элемент И| 14 блока 22 закрыт зап|)ещатщим потенциалом с шины 32, Бели процессор 19, назначенный-о :новным, запущен сигналом 5 и выполнять рабочую программу, то до момента.выработки счетчиком 18 сигнала , т.е, истечении интервала времени ТЗ от момента выработки сигнала 5 t в работающем про цессоре 19 вырабатывается программный сигнал., который со второго син хронизирующегЪ;выхода процессора по шине 27 устанавливает в. нулевое состояние триггеры 12 блоков 21 и 22, В результате в момент выработки сче чиком 18 сигнала -5 прохождение это го сигнала будет блокировано на эле ментах И 15 6JJOKOB 21 и.22, закрытых .запрещающими по тенци алами с единич;ных выходов триггеров 12, Если же процессор 19 не запустится сигналом по шине 35, не будет выполнять рабочую программу и не выдас сигнала на шину 27 к моменту выработки счетчиком 18 сигнала - , то |тригг;еры 12 блоков 21 и 22 будут на- i водиться .в единичном состоянии. Поэтому разрешающий потенциал с единичного.выхода триггера 12 откроет элемент И 15 блока 22, и сигнал счетчика 18 блока 22 через элемент ИЛИ 1 поступит нашину 35 и запустит процессор 20, При этом сигнал с-единичного выхода триггера 12 блока 21 разрешит прохождение сигнала через элементы-И 16 И ИЛИ 2 на шийу 34 для сброса процессора 19, который Не запустился от сигнала нач шьяого пуска, . . . . Таким .образом, в случае невыполнения рабочей, про граммы ..после прихода первого сигнала начального пуска по шинам .24 или 25 процессор 19 сбрасывается и исключается ир дальнейшей работа, а процессор 20 запускается по.цепи пуска после отказа сигналом -В счетчика 18 блока 22, После этого запуска процессор 20 переводится в рабочий режим и в нем начинает выполняться рабочая программа , вырабатывающая программный сигнал по шине 27, которым производит--ся сброс триггеров 12 блоков 21 и 22, Через интервал времени Т4 от момента выдачи сигнала - счетчик 18 вырабатывает сигнал , который устанавливает в О триггер 11, бло кируя тем самым поступление тактовых импульсов в счетчик 18 и прекращает его работу, /Процессор, в котором в результате начсшьного пуска либо пуска после отказа выполняется рабочая программа, производит выработку программного сигнала на шине 26, который производит установку в.исходное состояние блоков 21 и 22 путем сброса триггеров 9 через элемент ИЛИ 3, Выработка этого сигнала осуществляется рабочим процессором 19 или 20 по первому сигналу на шинах 24 или 25 с задержкой, например, равной 2-3-кратному максимальному интервалу времени задержки прихода одного сигнала начального пуска по отношению к Другому, чтобы гарантировать ложный запуск вследствие разброса сигналов на шинах 24 и 25, В случае отказа рабочего процессора 19 аппарату)а контроля процессора 19 формирует сигнал на шине 28 и через элемент ИЛИ 1 блока .22 по цепи пуска после отказа запускает процессор 20, При работе процессоров 19 и 20 , в составе системы они могут в соответствии со своими рабочими программами управлять работой друг друга, выдавая сигналы по шине 23, Таким образом, устройство обеспечивает автоматическое.включение резервного процессора, не требуя ручного вмешательства при неудачных.пус ках или от-казах рабочего процессора.

Фи.1

-А2i.,25 9

I11 12 /J

-LJl.

Т2

в

г

Л

27 26

7/

72

л

11

А

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4072852 кл.340172 | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-23—Публикация

1982-01-29—Подача