(54) ПРЕОБРАЗОВАТЕЛЬ КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода | 1981 |

|

SU1014144A1 |

| Функциональный преобразовательчиСлА иМпульСОВ B цифРОВОй КОд | 1979 |

|

SU807285A1 |

| Преобразователь постоянного напряжения в переменное программируемой формы | 1981 |

|

SU972650A1 |

| Масштабирующий преобразователь | 1982 |

|

SU1038880A1 |

| Преобразователь постоянного напряжения в переменное программируемой формы с блоком управления | 1982 |

|

SU1019566A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное | 1981 |

|

SU991564A2 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

Изобретение относится к импульсной технике, может быть использовано в устройствах кодирования, передачи данны и технике связи, и, в частности в устройствах компрессий сигнала методами адаптивной дельта - модуляции (АДМ) и дифференциальной импульсно-кодовой модуляции (ДИКМ) Известны устройства, содержащие сум матор-вычитатель и регистр, в которых на регистре с помощью сумматора-вычитателя накапливается последователь.- кость положительных и отрицательных кс довых приращений Г13. Однако эти устройства не обеспечивают экспоненциального преобразования накапливаемой суммы, что приводит к ухудш&нию помехоустойчивости при применении данного устройства (части комплексного устройства) в системе передачи с адап тивной дельта-модуляцией, являющейся комплексным устройством. Известен логарифмический преобразова тель числа импульсов, содержащий счетчики, выходы которых соединены с входами сравнивающего устройства, а выход последнего подключен к входу Сброс счетчика. Входная клемма преобразователя соединена со счетным входом счетчика через ключ, а с входом второго счетчика - через делитель частоты. Второй второго счетчика подключен к управляющему входу ключа Г2. Логарифмический преобразователь формирует логарифмическую зависимость времени появления импульсов на выходе устройства. Однако он не может быть использован в ряде устройств, где требуется накопление и экспоненциальная обработка последовательности различных по величине и знаку кодовых прирашений, нащя1мер в устройстве адаптивной дельтамодуляции (комплексное устройство.) Цель изобретения - расширение фунхцвовальвых возможностей за -счет обео печення ф()мировавия экспон ншюльного звЕОна стюда вакаплвваемой последовательHocTTi различных положительных и отрицательных кодовых приращений к среднему значению, что необходимо при работе данного устройства в комплексном устройстве стабилизированной адаптивной дельта-модуляции, в результате чего в комтьлексном устройстве обеспечивается повышение стабильности работы.

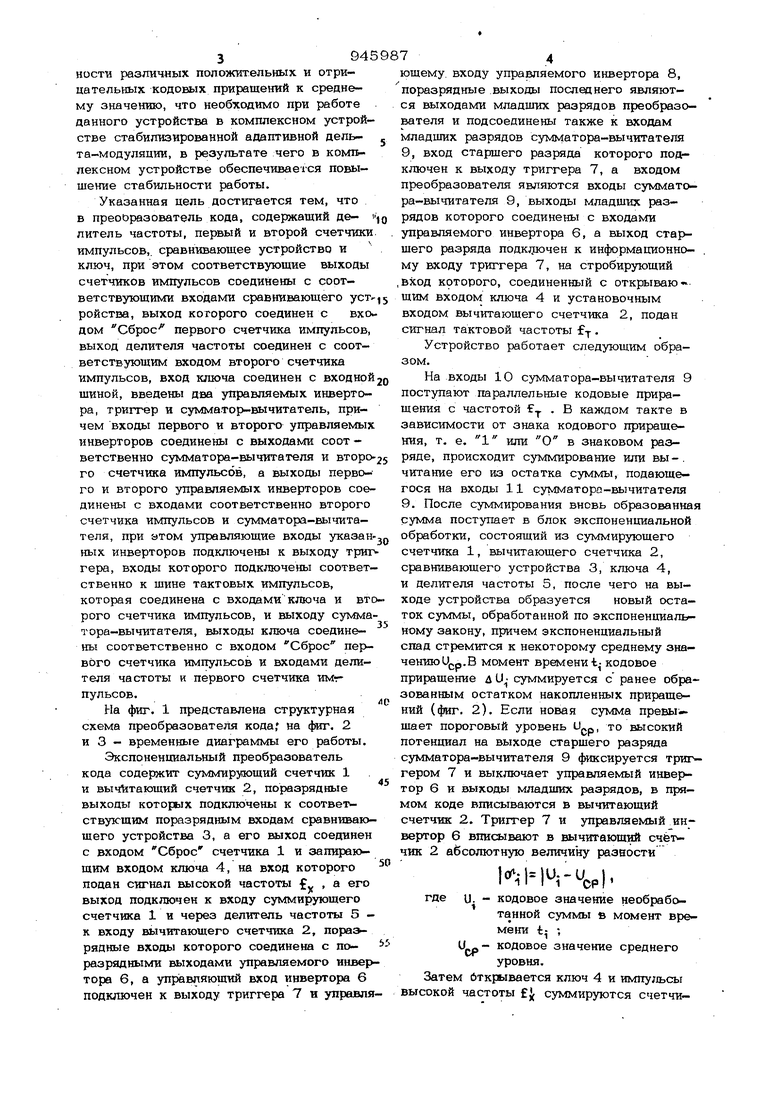

Указанная цель достигается тем, что в преооразователь кода, содержащий де- литель частоты, первый и второй счетчики импульсов,, сравнивающее устройство и ключ, при этом соответствующие выходы счетчиков импульсов соединены с соответствующими входами сравнивающего ройства, выход которого соединен с входом Сброс первого счетчика импульсов, выход делителя частоты соединен с соответствующим входом второго счетчика импульсов, вход ключа соединен с входной2о шиной, введены два управляемых инвертора, триггер и суммато1 -вычитатель, причем входы первого и второго управляемых инверторов соединены с выходами соот ветственно сумматора-вычитателя и второ- з го счетчика импульсов, а выходы первого и второго управляемых инверторов соединены с входами соответственно второго счетчика импульсов и сумматора-вычитателя, при этом управляющие входы указанных инверторов подключены к выходу триг гера, входы которого подключены соответственно к шине тактовых импульсов, которая соединена с входами ключа и вто рого счетчика импульсов, и выходу сумма тора-вычитателя, выходы ключа соединены соответственно с входом Сброс первого счетчика импульсов и входами делителя частоты и первого счетчика имгпульсов. На фиг. 1 представлена структурная схема преобразователя кода, на фиг. 2 и 3 - временные диаграммы его работы. Экспоненциальный преобразователь кода содержит суммирующий счетчик 1 и вычитающий счетчик 2, поразрядные выходы которых подключены к соответствующим поразрядным входам сравнивающего устройства 3, а его выход соединен с входом Сброс счетчика 1 и запирающим входом ключа 4, на вход которого подан сигнал высокой частоты , а его выход подключен к входу суммирующего счетчика 1 и через делитель частоты 5 к входу вычитающего счетчика 2, поразрядные входы которого соединена с поразрядными выходами управляемого инвер тора 6, а управляющий вход инвертора 6 подключен к выходу триггера 7 и улравля

юшему. входу управляемого инвертора 8, поразрядные выходы последнего являются выходами младших разрядов преобразователя и подсоединены также к входам младших разрядов сумматора-вычитателя 9, вход старшего разряда которого подключен к выходу триггера 7, а входом преобразователя являются входы сумматора-вычитателя 9, выходы младших разрядов которого соединены с входами управляемого инвертора 6, а выход старшего разряда подключен к информационному входу триггера 7, на стробирующий ,вход которого, соединенный с открывающим входом ключа 4 и установочным входом вычитающего счетчика 2, подан сигнал тактовой частоты fj.

Устройство работает следующим образом.

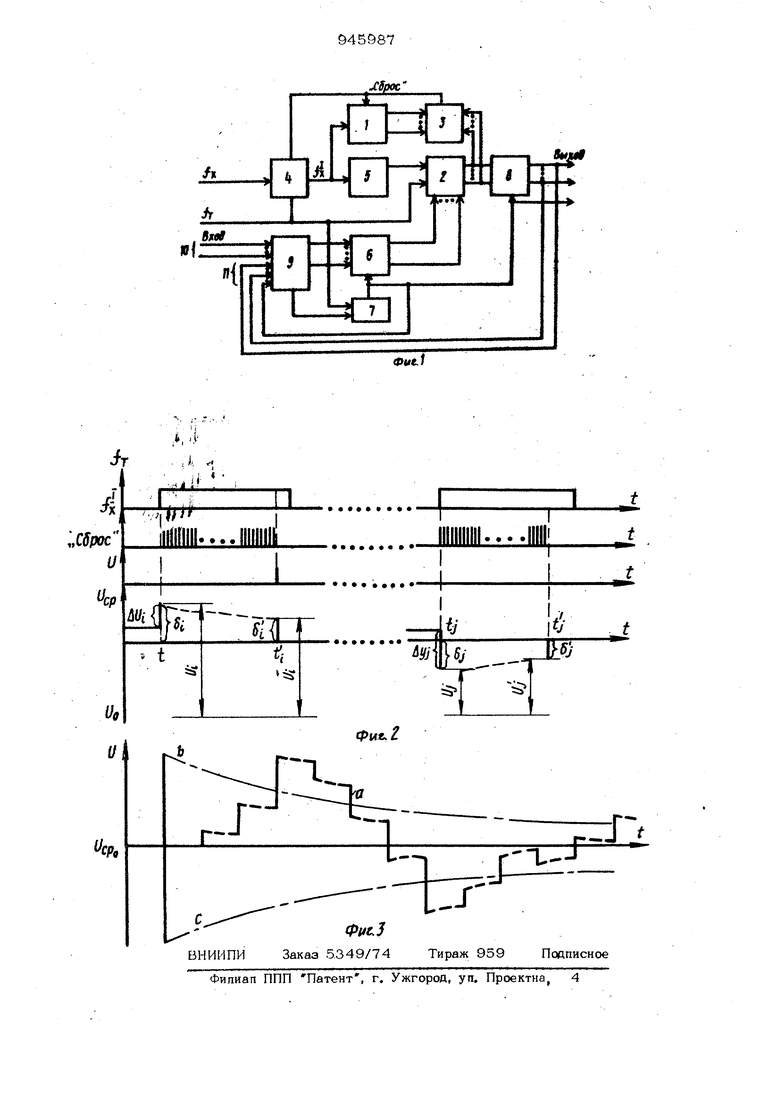

На входы 10 сумматора-вычитателя 9 поступают параллельные кодовые приращения с частотой € . В каждом такте в зависимости от знака кодового приращения, т. е. 1 или О в знаковом разряде, происходит суммирование или вы-, читание его из остатка суммы, подающегося на входы 11 сумматора-вычитателя 9. После суммирования вновь образованна сумма поступает в блок экспоненциальной обработки, состоящий из суммирующего счетчика 1, вычитающего счетчика 2, сравнивающего устройства 3, ключа 4, и делителя частоты 5, после чего на выходе устройства образуется новый остаток суммы, обработанной по экспоненциальному закону, причем экспоненциальный спад стремится к некоторому среднему зна- 4emnoUpp.B момент времени t кодовое приращение д U.- суммируется с ранее образованным остатком накопленных приращений (фиг. 2). Если новая сумма превышает пороговый уровень и,р, то высокий потенциал на выходе старшего разряда сумматора-вычитателя 9 фиксируется триггером 7 и выключает управляемый инвертор 6 и выходы младших разрядов, в прямом коде вписываются в вычитающий счетчик 2. Триггер 7 и управляемый инвертор 6 вписывают в вычитающий счётчик 2 абсолютную величину развости 1сЛ.|)и..и и. - кодовое значение необработанной суммы в момент времени i- ; fo кодовое значение среднего уровня. Затем бткрывается ключ 4 и импульсы высокой частоты fj суммируются счетчиком 1, а также, пройдя делитель часто ты 5, вычитаются из ранее установленно величины/сА (в вычитающем счетчике 2. В момент времени t сравнивающее устройство 3 фиксирует совпадение выходны кодов счетчиков 1 и 2, запирает ключ 4 и устанавливает в исходное состояние суммирующий счетчик 1. В соответствии с управляющим сигналом триггера 7 инвертор 8 пропускает обработанный код младщих разрядов суммы на выход устройства в неинвертированном виде,, а ста ший разряд снимается с выхода триггера 7, т. е. на выходе устройства формируется обработанное кодовое значение суммы Ul. Если в момент времени t; отрицатель ное приращение лО-, поступающее на вход 10 сумматора-вы читателя 9, приведет к тому, что новая сумма Ц/ станет меньше среднего уровня U, то низкий потенциал старщ го разряда сумматора-вычитателя 9 зафиксируется триггером 7 и включит управляемые инверторы 6 и 8. Вследст вие этого в вычитающий счетчик 2 впишется обратный код младших разрядов не обработанной суммы, что соответствует абсолютной величине разности i(fjl-|Uj-Ucp|. Далее через ключ 4 импульсы нысокой частоты f суммируются счетчиком 1 и через делитель 5 вычитаются из кода, соответствующего величине |сЛ:| в счетчике 2. В момент сравнения t. на вычитаю щем счетчике 2, в соответствии с экспоненциальным .законом обработки, будет код |(/j I, который инвертируется инвертором 8 и поступает на вькод устройства а также на вход 11 сумматора-вычита- теля 9 (старший разряд снимается с выхода триггера 8). На выходе экспоненциального преобразователя кода в момент времени ij образуется код обработанной суммы, соответствующий величине (фиг. 2). Таким образом, на выходе устройства в каждом такте происходит обработка накопленной суммы, которая стремится к среднему значению по экспоненциальному закону. На фиг. 3 показаны примеры функционирования устройства. Кривая сЛ отображает пример работы при поступлении на вход устройства последовательности различных положительных и отрицательных кодовых приращений. Кривые Ъ и с показывают экспоненциальный характер изменения амплитуды за несколько тактов 94 7 В случае подачи единовременных положительного или отрицательного приращения соответственно. Таким образом, предлагаемое устройство обеспечивает формирование экспоненциального спада накапливаемой последовательности различных параллельных кодовых приращений, что делает возможным его использование в устройстве стабилизированной адаптивной дельтамодуляции (комплексном устройстве). Формула изобретения Преобразователь кода, содержащий делитель частоты, первый и второй счетчики импульсов, сравнивающее устройство и ключ, при этом соответствующие выходы счетчиков импульсов соединены с соответствующими входами сравнивающего устройства, выход которого соединен с входом Сброс первого счетчика импульсов, выход делителя частоты соединен с соответствующим входом вто. рого счетчика импульсов, вход ключа соединен с входной шиной, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены два управляемых инвертора, трипгер и сумматор -вычитатель, причем входы первого и второго управляемых инверторов соединены с выходами соответствен но сумматора-вы читателя и второго счетчика импульсов, а выходы первого и второго управляемых инверторов соединены с входами соответственно второго.счетчика импульсов и сумматора-Фычитателя, при этсм управляющие входы указанных инверторов подключены к выходу триггера, входы которого подключены соответственно к шине тактовых импульсов, которая соединена с входами ключа иг второго счетчика импульсов, и выходу сумматора-вычитателя, выходы ключа сое динены соответственно с входами Сброс первого счетчика импульсов и входами делителя частоты и первого счетчика импульсов. Источники информации, принятые во внимание прн экспертизе 1.Букреев И. Н, Мансуров Б.М и др. Микроэлектроввые схемы цифровых устройств, М., Советское радио, 1975, с. 339-341. 2.Авторское свидетельство СССР Ма 47ОО73, кл. Н ОЗ К 13/24, О5.05.75 (прототип).

Авторы

Даты

1982-07-23—Публикация

1981-01-05—Подача