1 1

Изобретение относится к вычисли - тельной технике, может быть использовано для моделирования дискретных систем (например, систем передачи и обработки информации, производственных систем и пр.) и позволяет исследовать многофазные системы массового обслуживания с динамическими схемами приоритезации процессов и сложной логикой взаимодействия процессов.

Целью изобретения является расширение функциональных возможностей устройства за счет моделирования требуемых схем динамических приоритетов и логики взаимодействия заявок в многофазных системах массового обслуживания.

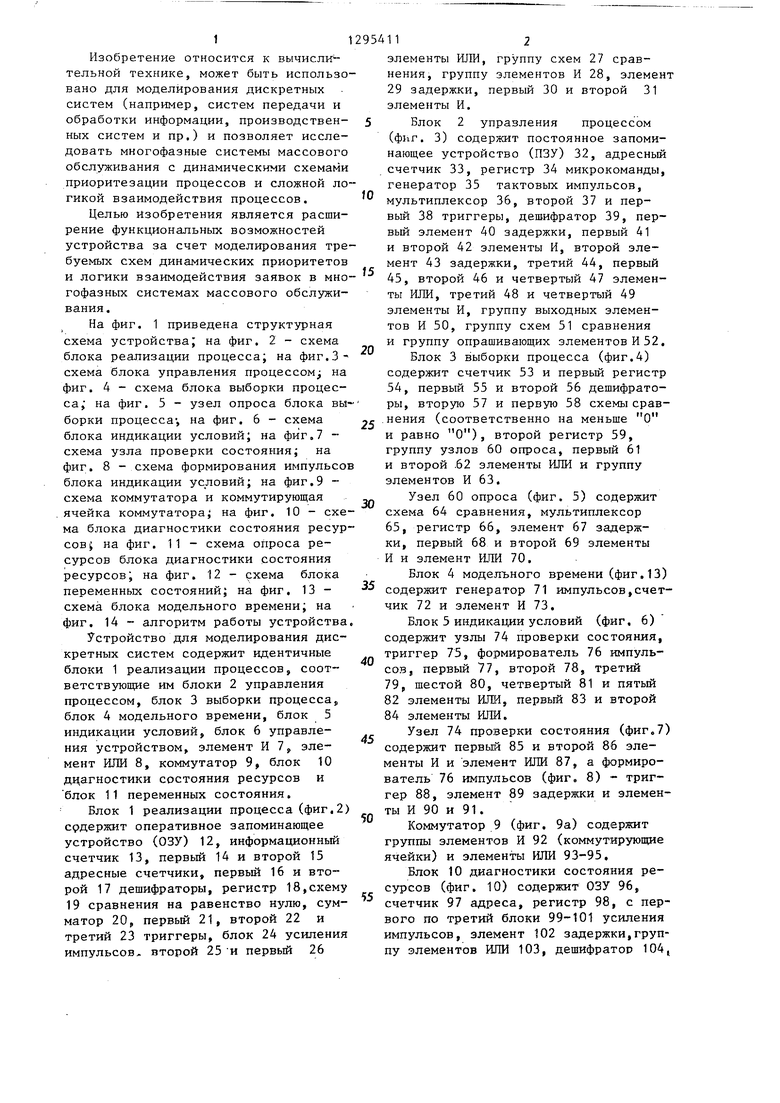

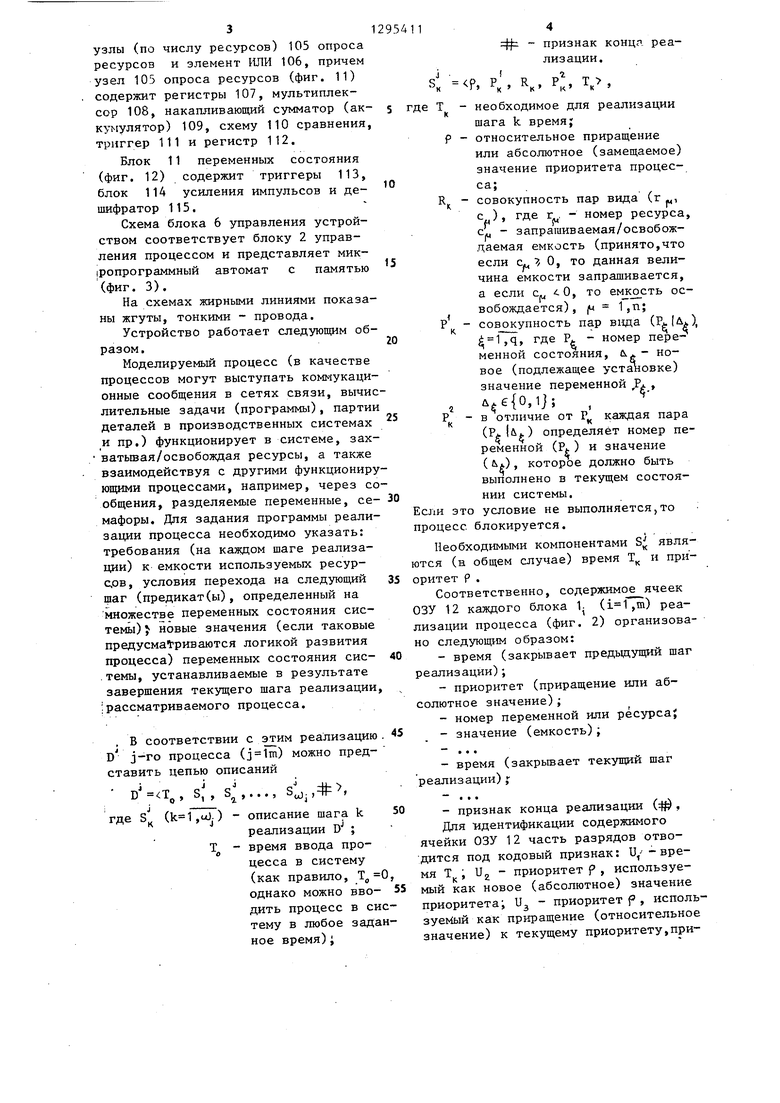

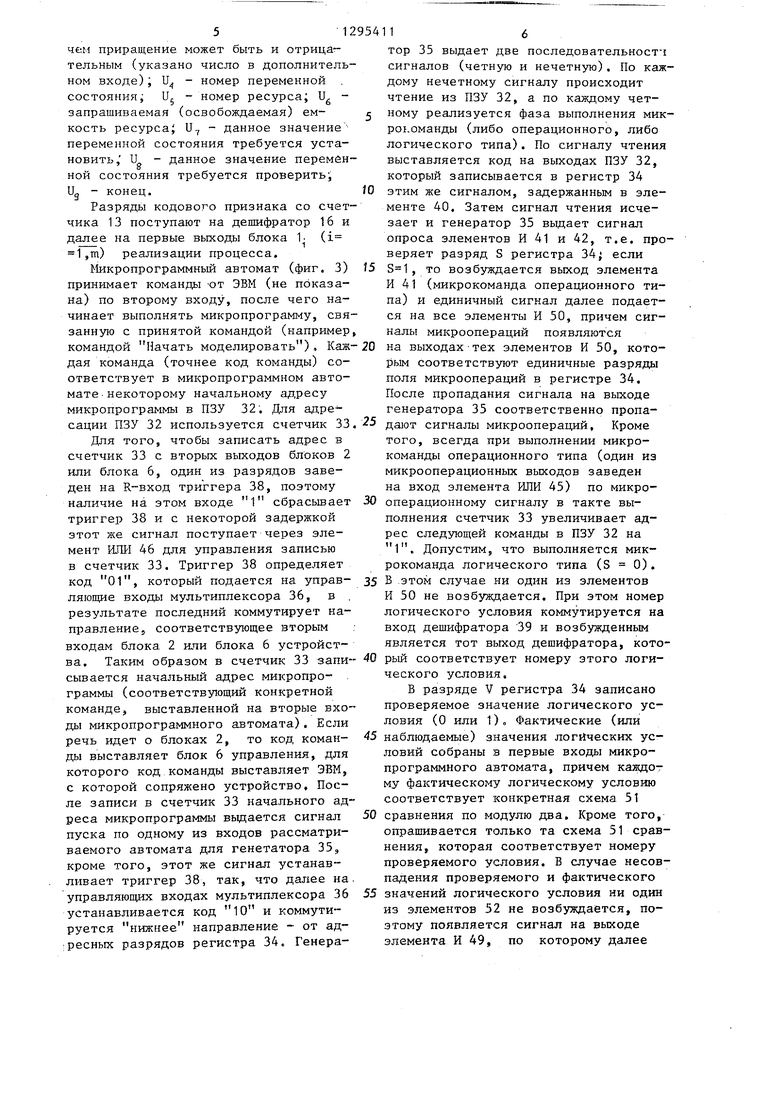

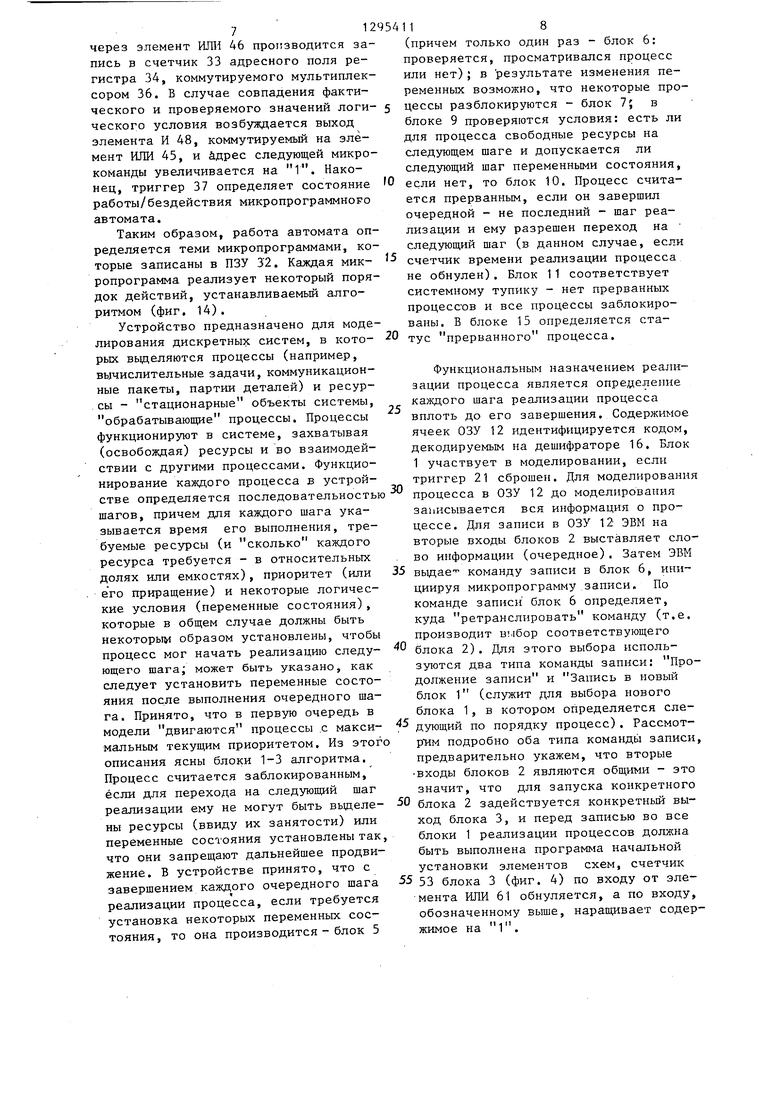

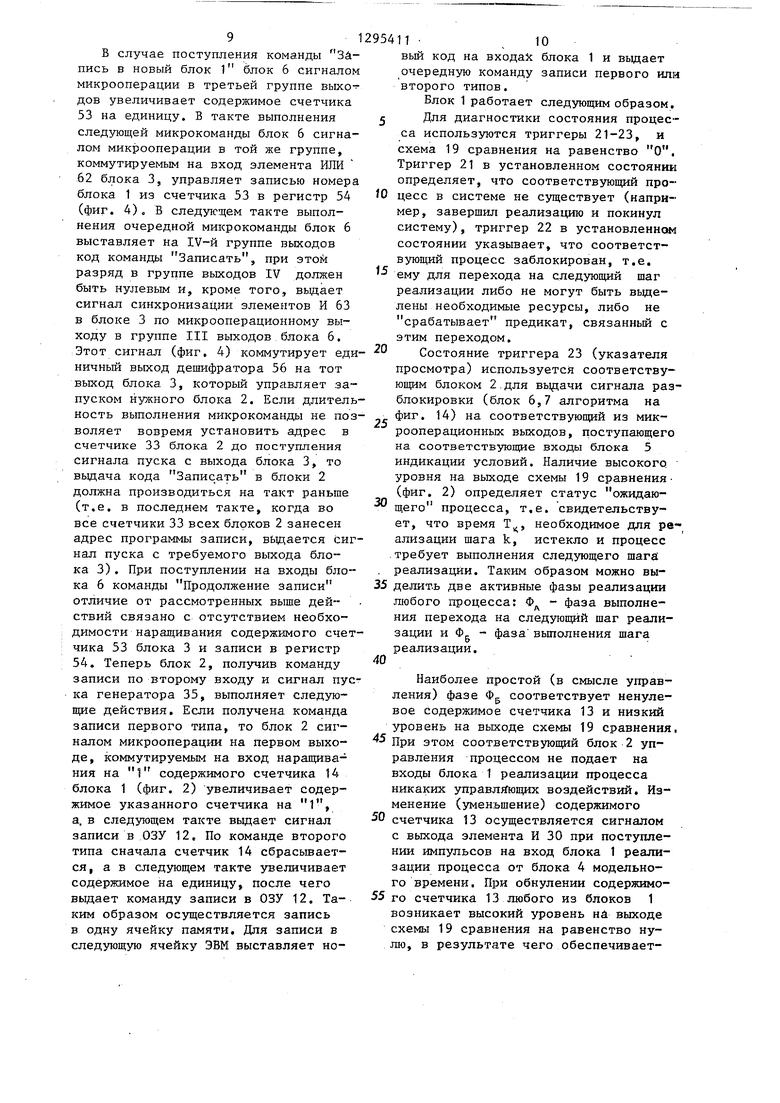

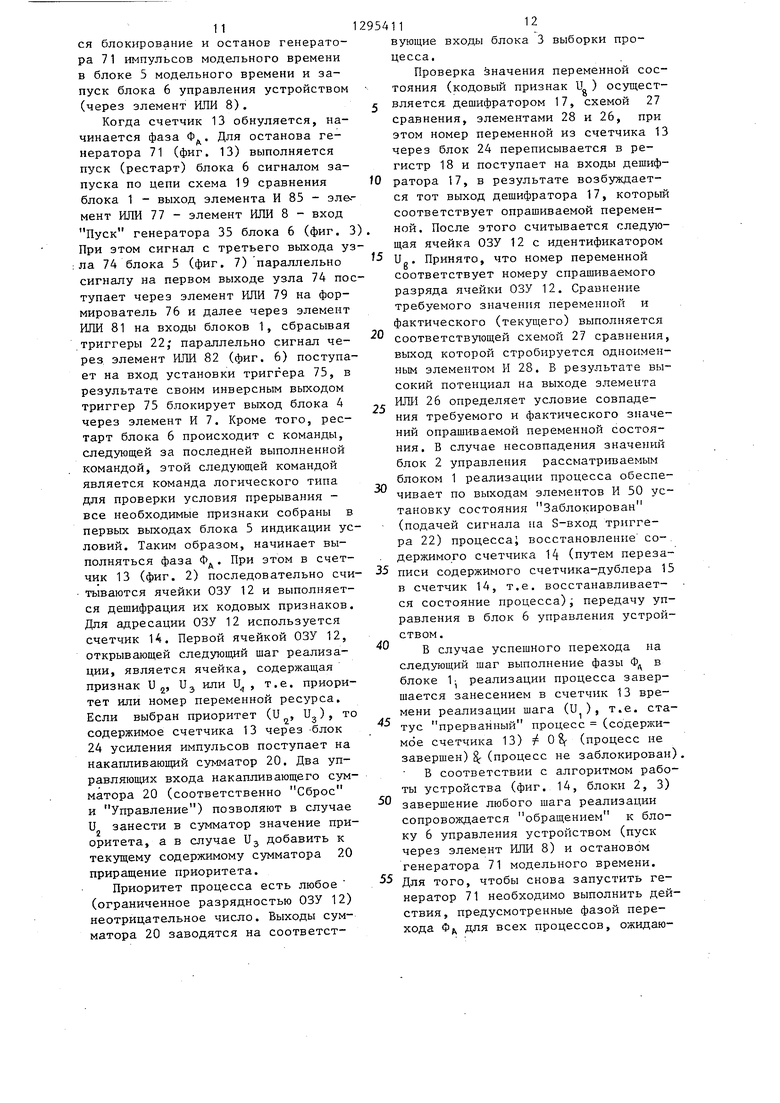

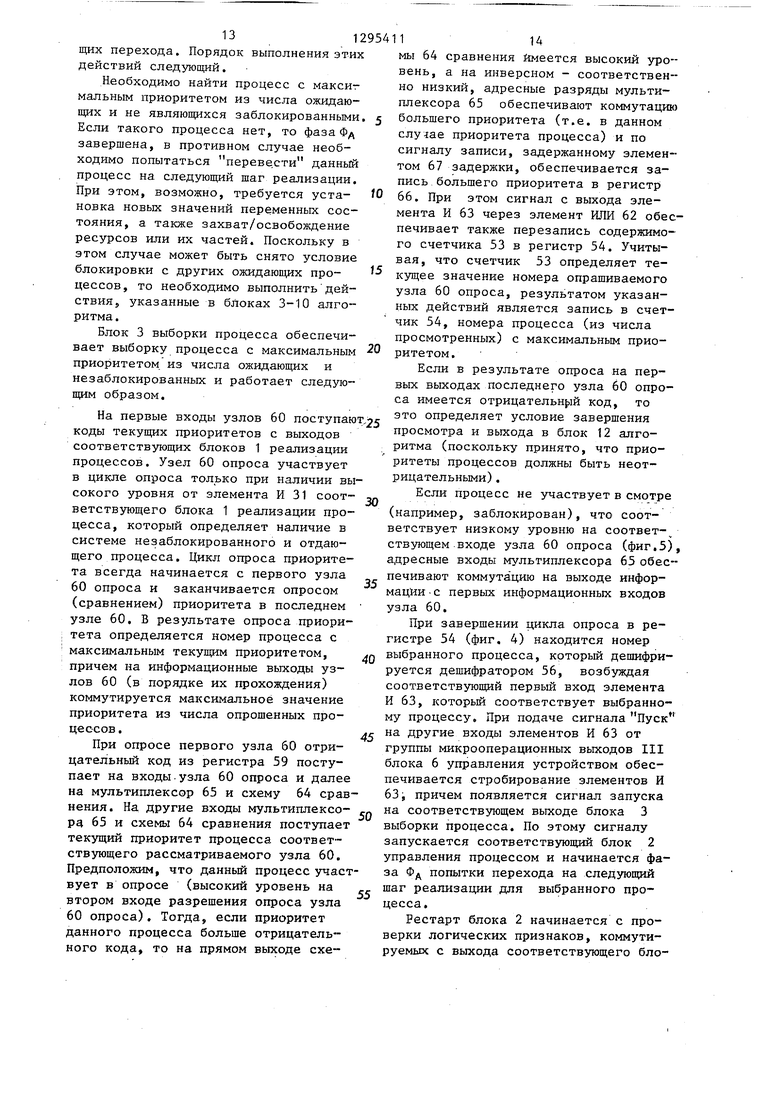

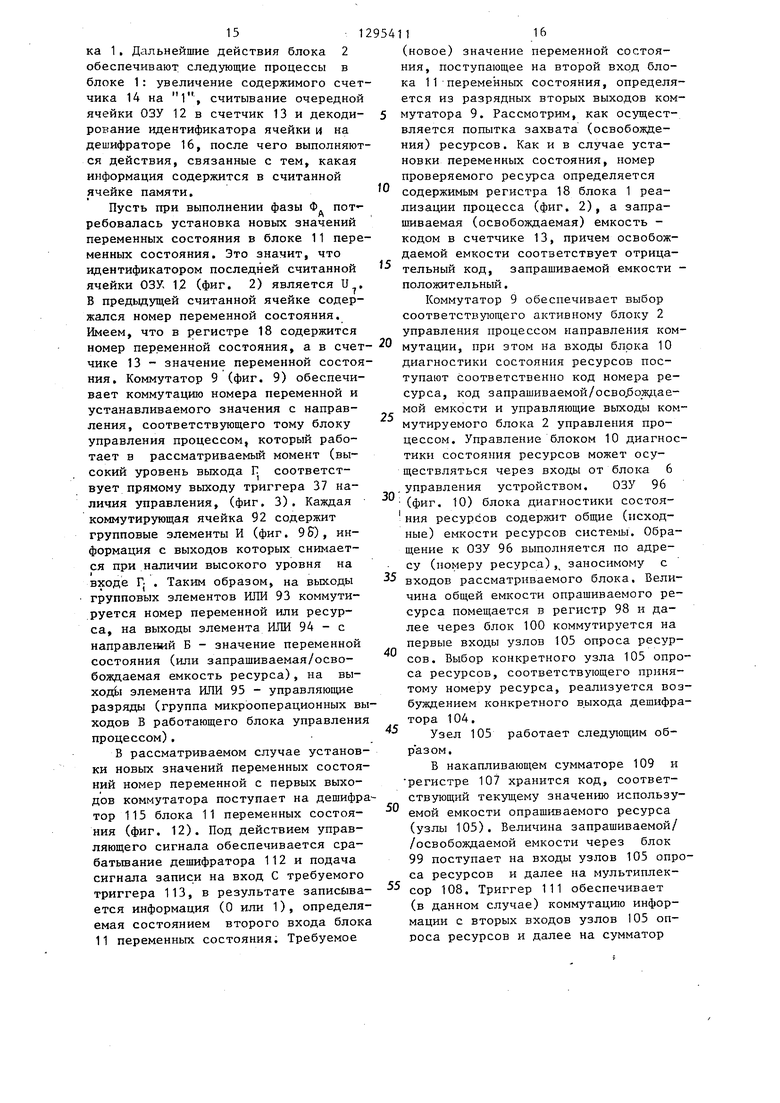

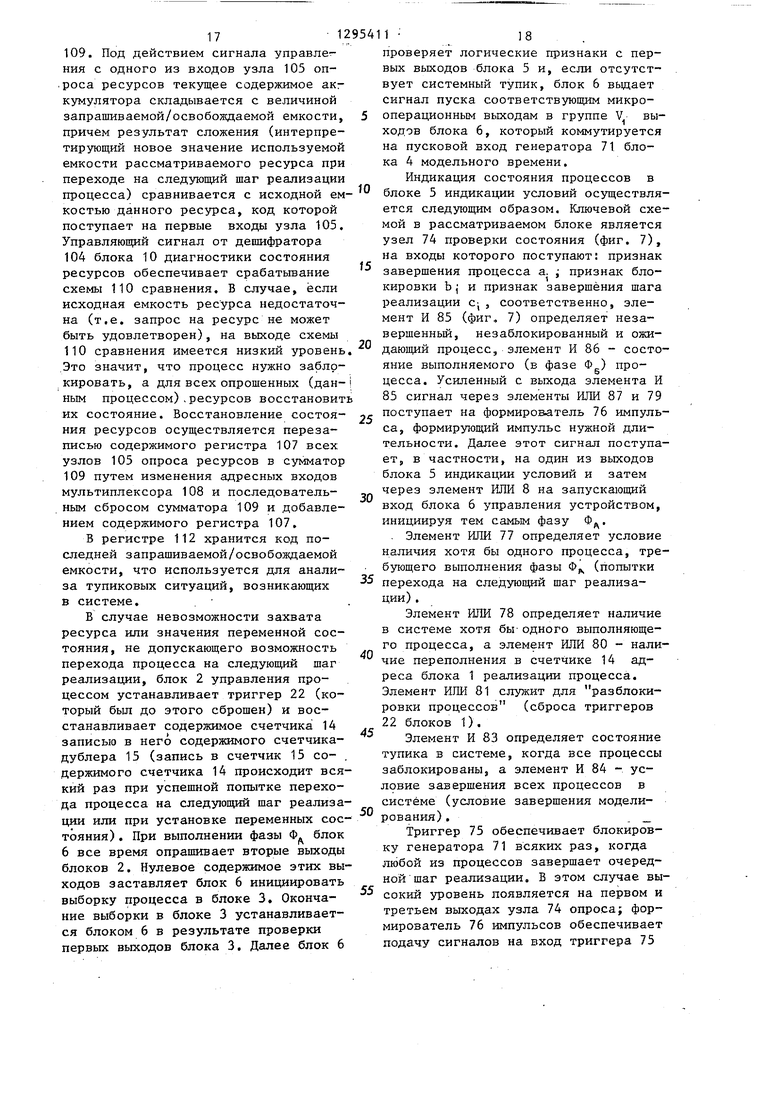

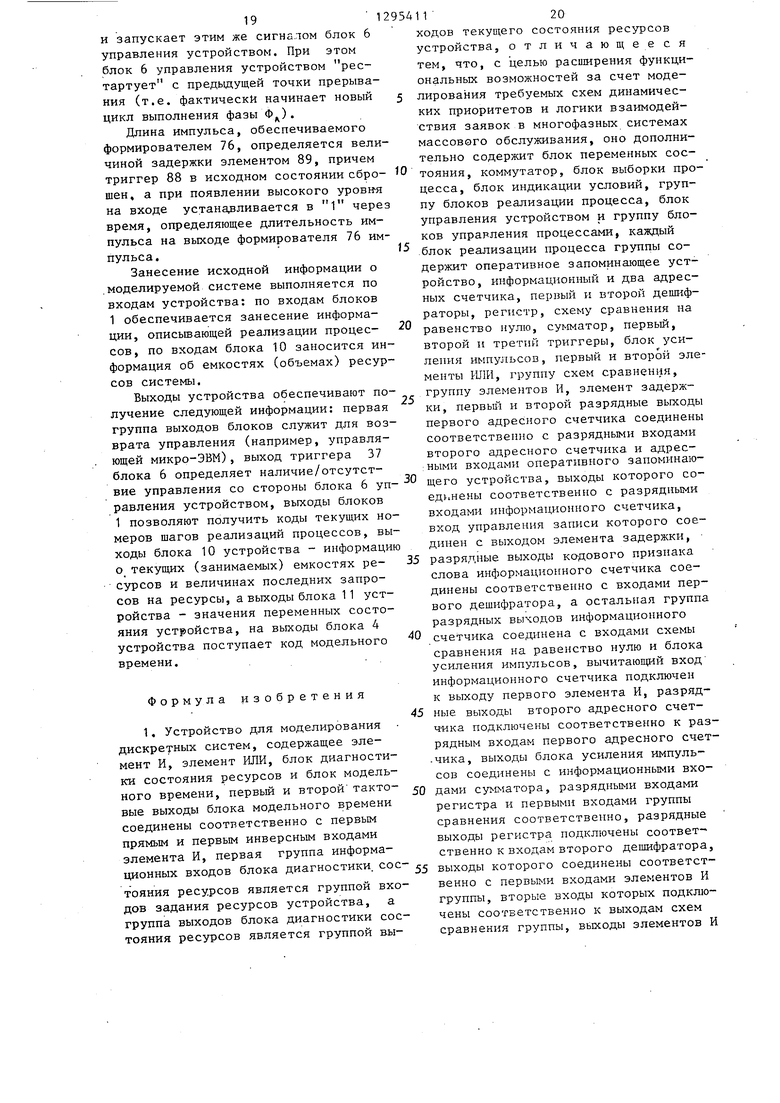

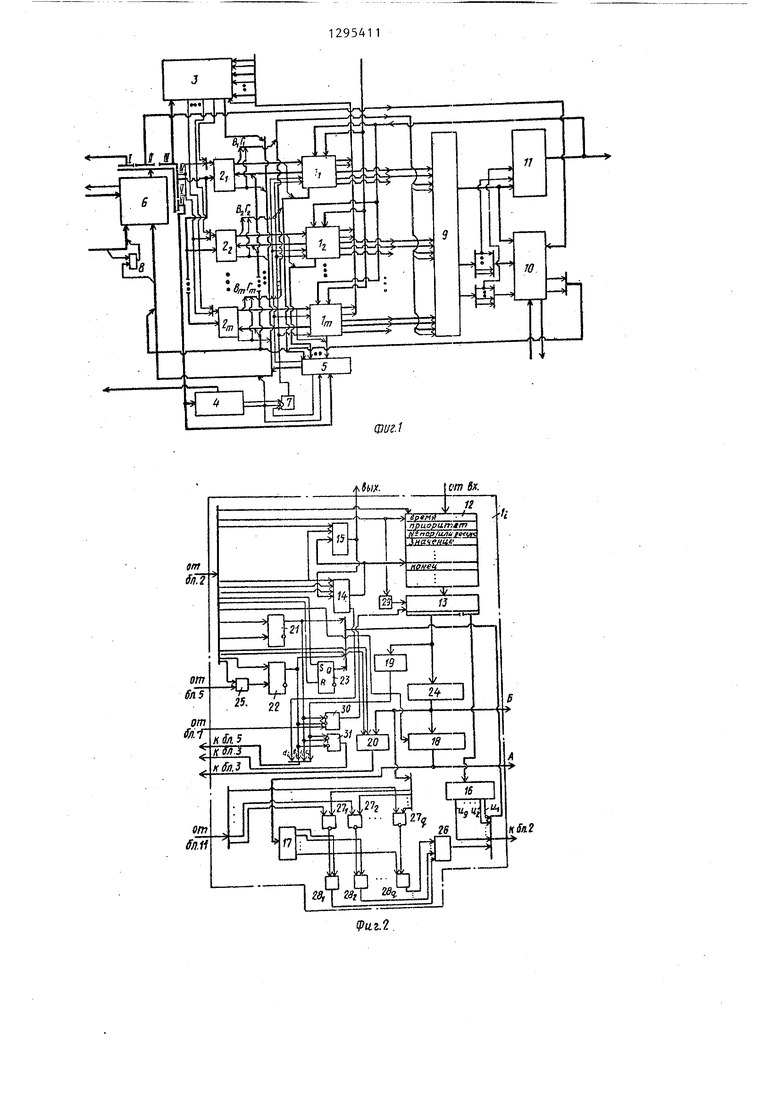

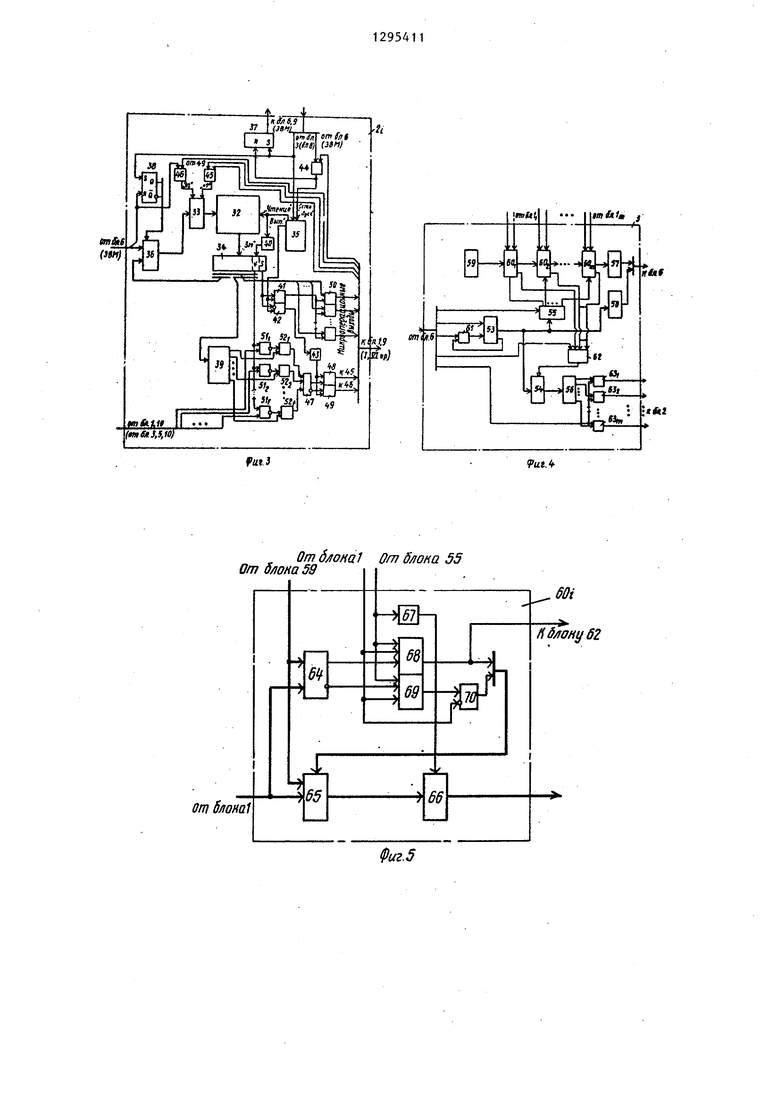

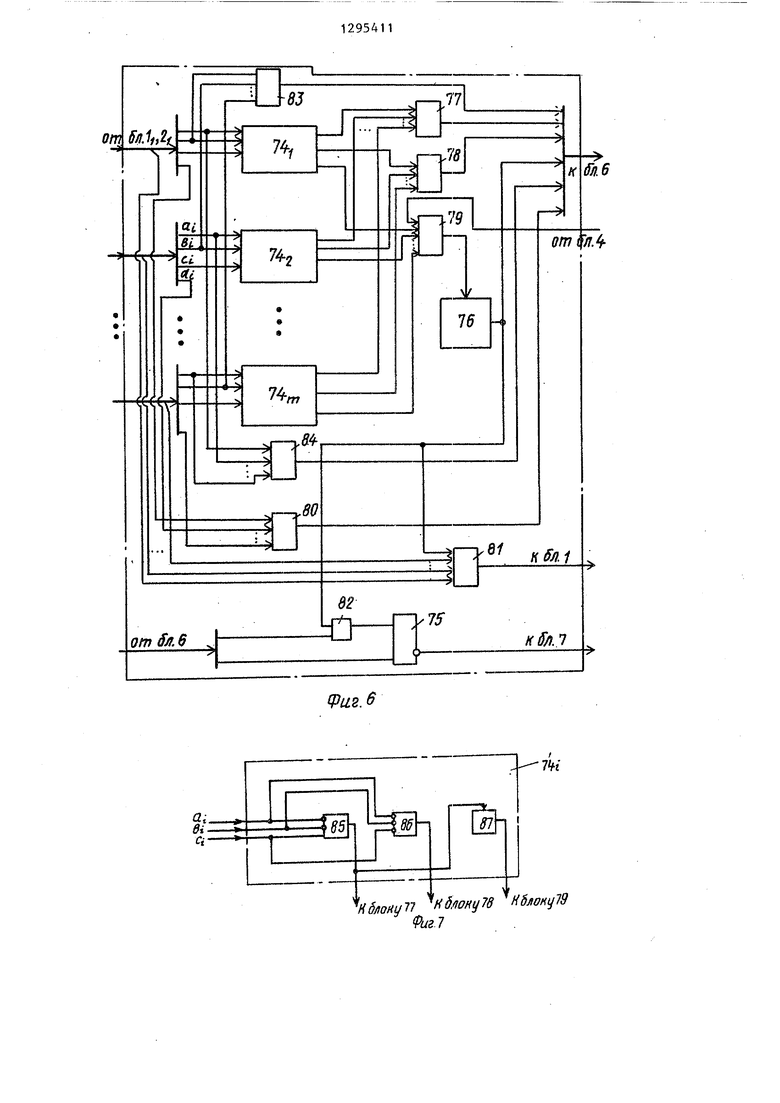

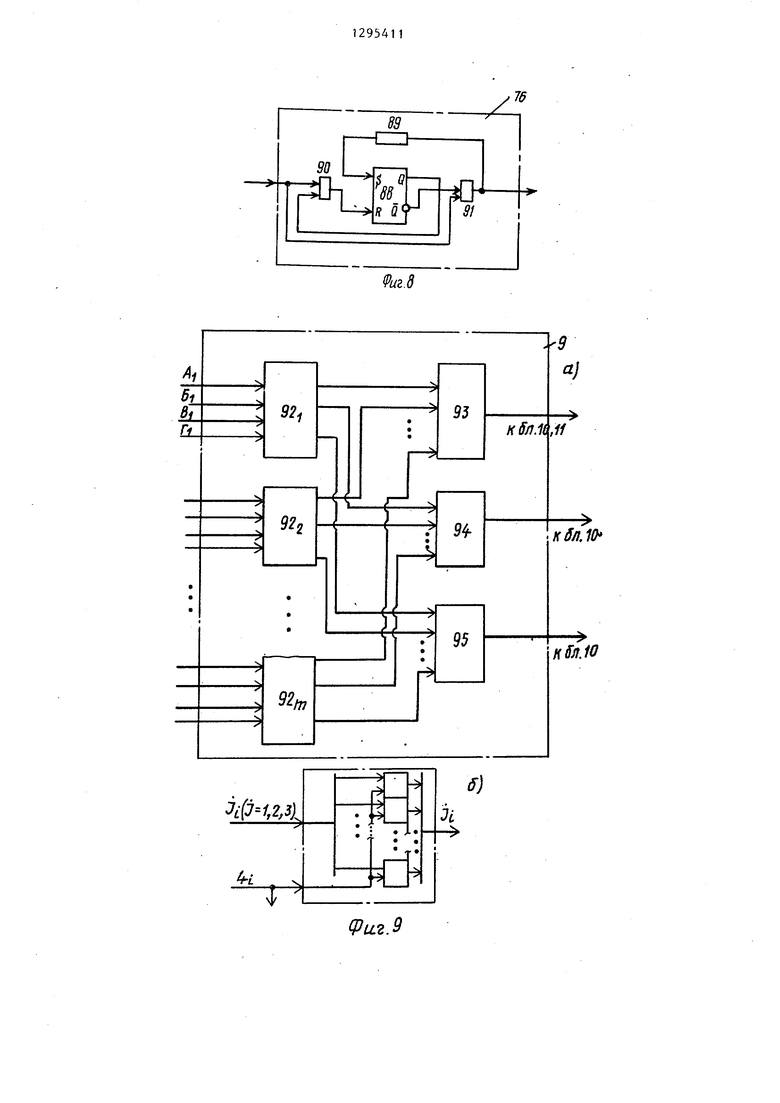

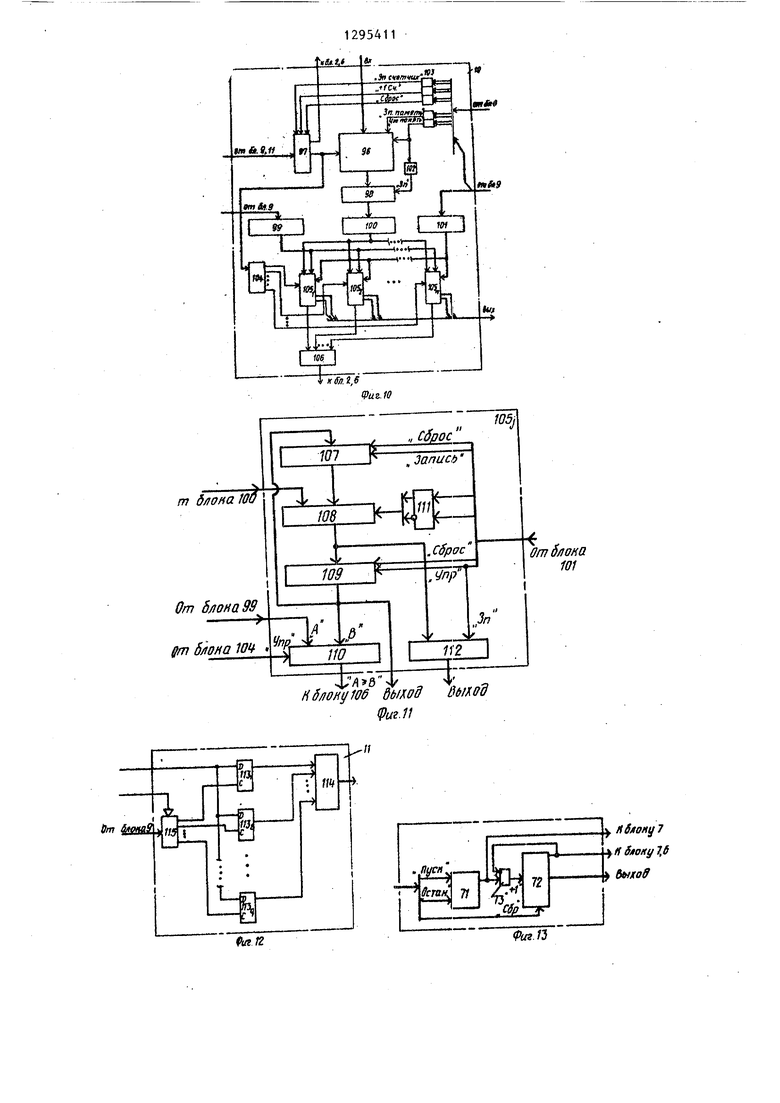

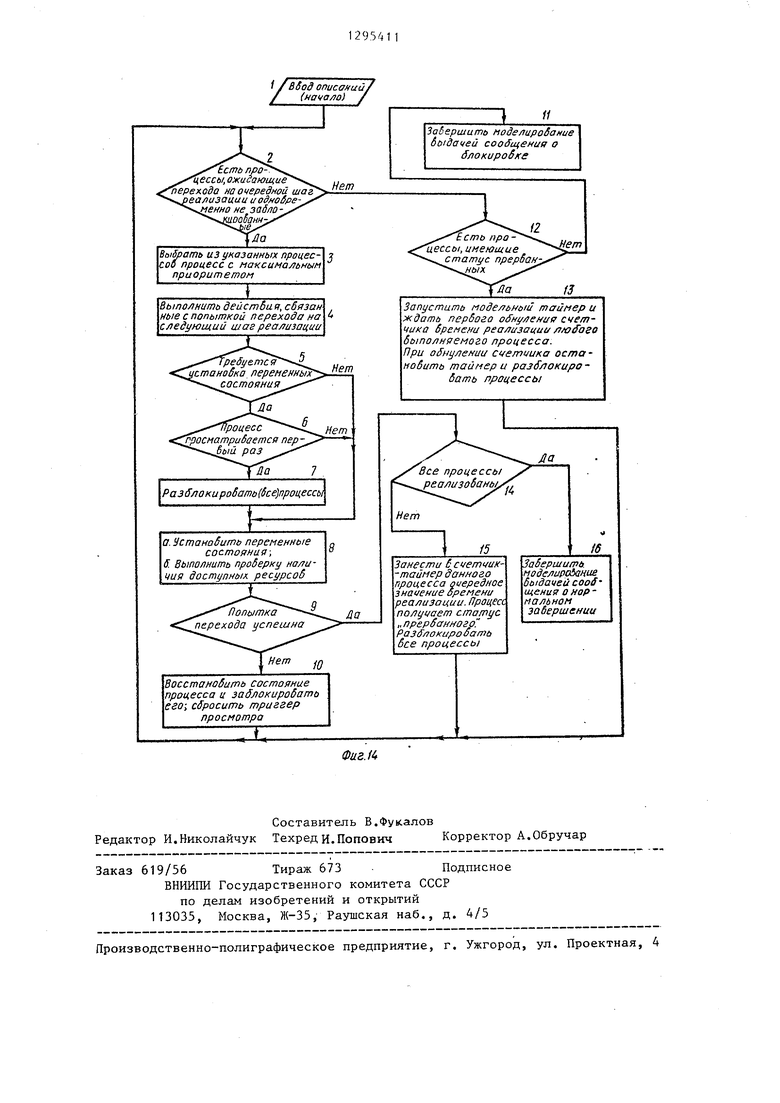

На фиг. 1 приведена структурная схема устройстваJ на фиг. 2 - схема блока реализации процесса; на фиг.З- схема блока управления процессом, на фиг. 4 - схема блока выборки процесса; на фиг. 5 - узел опроса блока выборки процесса-, на фиг. 6 - схема блока индикации условий; на фиг.7 - схема узла проверки состояния; на фиг. 8 - схема формирования импульсов блока индикации условий; на фиг.9 - схема коммутатора и коммутирующая ячейка коммутатора; на фиг. 10 - схема блока диагностики состояния ресурсов; на фиг. 11 - схема опроса ресурсов блока диагностики состояния ресурсов; на фиг. 12 - схема блока переменных состояний; на фиг. 13 - схема блока модельного времени; на фиг. 14 - алгоритм работы устройства.

Устройство для моделирования дискретных систем содержит идентичные блоки 1 реализации процессов, соответствующие им блоки 2 управления процессом, блок 3 выборки процесса блок 4 модельного времени, блок 5 индикации условий, блок 6 управления устройством, элемент И 7,, элемент ИЛИ 8, коммутатор 9, блок 10 диагностики состояния ресурсов и блок 11 переменных состояния,

Блок 1 реализации процесса (фиг.2) срдержит оперативное запоминающее устройство (ОЗУ) 12, информационный счетчик 13, первый 14 и второй 15 адресные счетчики, первый 16 и второй 17 дешифраторы, регистр 18,схему 19 сравнения на равенство нулю, сумматор 20, первый 21, второй 22 и третий 23 триггеры, блок 24 усиления импульсов- второй 25 н первый 26

0

15

0

5

954112

элементы Ш1И, группу схем 27 сравнения, группу элементов И 28, элемент 29 задержки, первый 30 и второй 31 элементы И.

5 Блок 2 управления процессом (фиг. 3) содержит постоянное запоминающее устройство (ПЗУ) 32, адресный счетчик 33, регистр 34 микрокоманды, генератор 35 тактовых импульсов, мультиплексор 36, второй 37 и первый 38 триггеры, дешифратор 39, первый элемент 40 задержки, первый 41 и второй 42 элементы И, второй элемент 43 задержки, третий 44, первый 45, второй 46 и четвертый 47 элементы ИЛИ, третий 48 и четвертый 49 элементы И, группу выходных элементов И 50, группу схем 51 сравнения и группу опрашивающих элементов И 52.

Блок 3 выборки процесса (фиг.4) содержит счетчик 53 и первый регистр 54, первый 55 и второй 56 дешифраторы, вторую 57 и первую 58 схемы сравнения (соответственно на меньше О и равно О), второй регистр 59, группу узлов 60 опроса, первый 61 и второй .62 элементы ИЛИ и группу элементов И 63.

Узел 60 опроса (фиг. 5) содержит схема 64 сравнения, мультиплексор 65, регистр 66, элемент 67 задержки, первый 68 и второй 69 элементы И и элемент ИЛИ 70.

Блок 4 модельного времени (фиг.13) содержит генератор 71 импульсов,счетчик 72 и элемент И 73.

Блок 5 индикации условий (фиг, 6) содержит узлы 74 проверки состояния, триггер 75, формирователь 76 импульсов, первый 77, второй 78, третий 79, шестой 80, четвертый 81 и пятый 82 элементы ИЛИ, первый 83 и второй 84 элементы ИЛИ.

Узел 74 проверки состояния (фиг.7) содержит первый 85 и второй 86 элементы И и элемент ИЛИ 87, а формирователь 76 импульсов (фиг. 8) триггер 88, элемент 89 задержки и элементы И 90 и 91.

Коммутатор 9 (фиг. 9а) содержит группы элементов И 92 (коммутирующие ячейки) и элементы ШШ 93-95,

Блок 10 диагностики состояния ресурсов (фиг. 10) содержит ОЗУ 96, счетчик 97 адреса, регистр 98, с первого по третий блоки 99-101 усиления импульсов, элемент 102 задержки,группу элементов ИЛИ 103, дешифратор 104,

0

0

5

0

3

узлы (по числу ресурсов) 105 опроса ресурсов и элемент ИЛИ 106, причем узел 105 опроса ресурсов (фиг. 11) содержит регистры 107, мультиплексор 108, накапливающий сумматор (ак кумулятор) 109, схему 110 сравнения триггер 111 и регистр 112.

Блок 11 переменных состояния (фиг. 12) содержит триггеры 113, блок 114 усиления импульсов и дешифратор 115.

Схема блока 6 управления устройством соответствует блоку 2 управления процессом и представляет мик- ропрограммный автомат с памятью (фиг. 3).

На схемах жирными линиями показаны жгуты, тонкими - провода.

Устройство работает следующим образом.

Моделируемый процесс (в качестве процессов могут выступать коммукаци онные сообщения в сетях связи, вычилительные задачи (программы), парти деталей в производственных системах и пр.) функционирует в системе, зах ватьшая/освобождая ресурсы, а также взаимодействуя с другими функционирющими процессами, например, через собщения, разделяемые переменные, се мафоры. Для задания программы реализации процесса необходимо указать: требования (на каждом шаге реализации) к емкости используемых ресурсов, условия перехода на следующий щаг (предикат(ы), определенный на множестве переменных состояния системы) } новые значения (если таковые предусма1 риваются логикой развития процесса) переменных состояния сие- .темы, устанавливаемые в результате завершения текущего шага реализации ;рассматриваемого процесса.

, В соответствии с этим реализацию D j-ro процесса () можно представить цепью описаний

,, s,..., s cJi-

(,tO.) - описание шага 1 реализации D ;

где S

- время ввода процесса в систему (как правило, , однако можно вво- 55 дить процесс в систему в любое заданное время);

0

5

0

s где Т

R

0 5 0

J SK Р, Р. .

4j признак конца реализации. ,г

R

5

Т

к к к к

-необходимое для реализации шага k время;

Р - относительное приращение или абсолютное (замещаемое) значение приоритета процесса;

-совокупность пар вида (г „,

с ), где Tjy. - номер ресурса, с,, - запрашиваемая/освобождаемая емкость (принято,что если с,, / О, то данная величина емкости запрашивается, а если с., с О, то емкость освобождается), |И 1,п; совокупность пар вида (P(&), 1,q, где Р - номер переменной состояния, &.Л. новое (подлежащее установке) значение переменной Рл,

.ij; ,

в отличие от Р| каждая пара () определяет номер переменной (PJ. ) и значение

Р. Р.

( &), которое должно быть выполнено в текущем состоянии системы.

Если это условие не выполняется,то процесс блокируется.

Необходимыми компонентами S; являются (в общем случае) время Т и приоритет Р .

Соответственно, содержимое ячеек ОЗУ 12 каждого блока 1. (,т) реализации процесса (фиг. 2) организовано следующим образом:

-время (закрывает предыдущий шаг реализации);

-приоритет (приращение или абсолютное значение);

-номер переменной или ресурса;

-значение (емкость); ...

-время (закрьгоает текущий шаг реализации) ;

-признак конца реализации ( , Для идентификации содержимого

ячейки ОЗУ 12 часть разрядов отводится под кодовый признак: U, - время Т ; и - приоритет Р, используемый как новое (абсолютное) значение приоритетаi U - приоритет р, используемый ка:к приращение (относительное значение) к текущему приоритету,при512954

чем приращение может быть и отрицательным (указано число в дополнительном входе) , и - номер переменной состояния; Uj - номер ресурса; U - запрашиваемая (освобождаемая) ем- кость ресурсаJ U - данное значение переменной состояния требуется установить, и - данное значение переменной состояния требуется проверить ,

Ug - конец.

Разряды кодового признака со счетчика 13 поступают на дешифратор 16 и далее на первые выходы блока } (i- 1,m) реализации процесса.

Микропрограммный автомат (фиг, 3) принимает команды -от ЭВМ (не показана) по второму входу, после чего начинает выполнять микропрограмму, связанную с принятой командой (например командой Начать моделировать), Каж дая команда (точнее код команды) соответствует в микропрограммном автомате- некоторому начальному гщресу микропрограммы в ПЗУ 32. Для адресации ПЗУ 32 используется счетчик 33

Для того, чтобы записать адрес в счетчик 33 с вторых выходов блоков 2 или блока 6, один из разрядов заведен на R-вход триггера 38, поэтому наличие на этом входе 1 сбрасьшает триггер 38 и с некоторой задержкой этот же сигнал поступает через элемент ИЛИ 46 для управления записью в счетчик 33. Триггер 38 определяет код 01, который подается на управляющие входы мультиплексора 36, в , результате последний коммутирует направление , соответствующее вторым входам блока 2 или блока 6 устройства. Таким образом в счетчик 33 запи- сывается начальный адрес микропрограммы (соответствующий конкретной команде, выставленной на вторые входы микропрограммного автомата). Если речь идет о блоках 2, то код команды выставляет блок 6 управления, для которого код команды выставляет ЭВМ, с которой сопряжено устройство. После записи в счетчик 33 начального адреса микропрограммы вьщается сигнал пуска по одному из входов рассматриваемого автомата для генетатора 35, кроме того, этот же сигнал устанавливает триггер 38, так, что далее на управляющих входах мультиплексора 36 устанавливается код 10 и коммутируется нижнее направление - от ад- пресных разрядов регистра 34. Генера

0

5

5

0

0

0 5

5

5

0

116

тор 35 выдает две последовательностч сигналов (четную и нечетную). По каждому нечетному сигналу происходит чтение из ПЗУ 32, а по каждому четному реализуется фаза выполнения микрокоманды (либо операционного, либо логического типа). По сигналу чтения выставляется код на выходах ПЗУ 32, который записывается в регистр 34 этим же сигналом, задержанным в элементе 40. Затем сигнал чтения исчезает и генератор 35 вьщает сигнал опроса элементов И 41 и 42, т.е. проверяет разряд S регистра 34; если , то возбуждается выход элемента И 41 (микрокоманда операционного типа) и единичный сигнал далее подается на все элементы И 50, причем сигналы микроопераций появляются на выходах тех элементов И 50, которым соответствуют единичные разряды поля микроопераций в регистре 34. После пропадания сигнала на выходе генератора 35 соответственно пропа- дшот сигналы микроопераций, Кроме того, всегда при выполнении микрокоманды операционного типа (один из микрооперационных выходов заведен на вход элемента ИЛИ 45) по микро- операдионному сигналу в такте выполнения счетчик 33 увеличивает адрес следующей команды в ПЗУ 32 на 1. Допустим, что выполняется микрокоманда логического типа (). В этом случае ни один из элементов И 50 не возбуж,цается. При этом номер логического условия коммутируется на вход дешифратора 39 и возбужденным является тот выход дешифратора, который соответствует номеру этого логического условия,

В разряде V регистра 34 записано проверяемое значение логического условия (О или 1), Фактические (или наблюдаемые) значения логических условий собраны в первые входы микропрограммного автомата, причем каждот му фактическому логическому условию соответствует конкретная схема 51 сравнения по модулю два. Кроме того, опрашивается только та схема 5 Г сравнения, которая соответствует номеру проверяемого условия. В случае несовпадения проверяемого и фактического значений логического условия ни один из элементов 52 не возбуждается, поэтому появляется сигнал на выходе элемента И 49, по которому далее

712

через элемент HJIli 46 производится запись э счетчик 33 адресного поля регистра 34, коммутируемого мультиплексором 36. В случае совпадения фактического и проверяемого значений логи- ческого условия возбуждается выход элемента И 48, коммутируемый на элемент ИЛИ 45, и адрес следующей микрокоманды увеличивается на 1. Наконец, триггер 37 определяет состояние работы/бездействия микропрограммного автомата.

Таким образом, работа автомата определяется теми микропрограммами, которые записаны в ПЗУ 32. Каждая мик- ропрограмма реализует некоторый порядок действий, устанавливаемьш алгоритмом (фиг. 14).

Устройство предназначено для моде

лирования дискретных систем, в кото- рых выделяются процессы (например, вычислительные задачи, коммуникационные пакеты, партии деталей) и ресурсы - стационарные объекты системы, обрабатывающие процессы. Процессы функционируют в системе, захватывая (освобождая) ресурсы и во взаимодействии с другими процессами. Функционирование каждого процесса в устройстве определяется последовательностью шагов, причем для каждого шага указывается время его выполнения, требуемые ресурсы (и сколько каждого ресурса требуется - в относительных долях или емкостях), приоритет (или его приращение) и некоторые логические условия (переменные состояния), которые в общем случае должны быть некоторым образом установлены, чтобы

процесс мог начать реализацию следу

ющего шага может быть указано, как следует установить переменные состояния после выполнения очередного шага. Принято, что в первую очередь в модели двигаются процессы .с макси- мальным текущим приоритетом. Из этог описания ясны блоки 1-3 алгоритма. Процесс считается заблокированным, если для перехода на следующий шаг реализации ему не могут быть выделе- ны ресурсы (ввиду их занятости) или переменные состояния установлены так что они запрещают дальнейшее продвижение. В устройстве принято, что с завершением каждого очередного шага реализации проце сса, если требуется установка некоторых переменных состояния, то она производится - блок 5

5 О

25

20 ю35

30

40

о -50 , 55

118

(причем только один раз - блок 6: проверяется, просматривался процесс или нет); в результате изменения переменных возможно, что некоторые процессы разблокируются - блок 7; в блоке 9 проверяются условия: есть ли для процесса свободные ресурсы на следующем шаге и допускается ли следующий шаг переменными состояния, если нет, то блок 10. Процесс считается прерванным, если он завершил очередной - не последний - шаг реализации и ему разрешен переход на следующий шаг (в данном случае, если счетчик времени реализации процесса не обнулен). Блок 11 соответствует системному тупику - нет прерванных процессов и все процессы заблокированы, В блоке 15 определяется статус прерванного процесса.

Функциональным назначением реализации процесса является определение каждого шага реализации процесса вплоть до его завершения. Содержимое ячеек ОЗУ 12 идентифицируется кодом, декодируемым на дешифраторе 16. Блок 1 участвует в моделировании, если триггер 21 сброшен. Для моделирования процесса в ОЗУ 12 до моделирования записывается вся информация о процессе. Для записи в ОЗУ 12 ЭВМ на вторые входы блоков 2 выставляет слово информации (очередное). Затем ЭВМ выдае команду записи в блок 6, инициируя микропрограмму записи. По команде записи блок 6 определяет, куда ретранслировать команду (т.е. производит выбор соответствующего блока 2). Для этого выбора используются два типа команды записи: Продолжение записи и Запись в новый блок 1 (служит для выбора нового блока 1, в котором определяется следующий по порядку процесс). Рассмотрим подробно оба типа команды записи, предварительно укажем, что вторые входы блоков 2 являются общими - это значит, что для запуска конкретного блока 2 задействуется конкретный выход блока 3, и перед записью во все блоки 1 реализации процессов должна быть выполнена программа начальной установки элементов схем, счетчик 53 блока 3 (фиг. 4) по входу от элемента ИЛИ 61 обнуляется, а по входу, обозначенному выше, наращивает содержимое на 1.

9

В случае поступления команды Запись в новый блок 1 блок 6 сигналом микрооперации в третьей группе выходов увеличивает содержимое счетчика 53 на единицу. В такте выполнения следующей микрокоманды блок 6 сигналом микрооперации в той же группе, коммутируемым на вход элемента ИЛИ 62 блока 3, управляет записью номера блока 1 из счетчика 53 в регистр 54 (фиг. 4), В следующем такте выполнения очередной микрокоманды блок 6 выставляет на IV-й группе выходов код команды Записать, при разряд в группе выходов IV должен быть нулевым и, кроме того, вьщает сигнал синхронизации элементов И 63 в блоке 3 по микрооперационному выходу в группе III выходов блока 6. Этот сигнал (фиг. 4) коммутирует еди ничный выход дешифратора 56 на тот выход блока 3, который управляет запуском нужного блока 2. Если длительность выполнения микрокоманды не позволяет вовремя установить адрес в счетчике 33 блока 2 до поступления сигнала пуска с выхода блока 3, то выдача кода Записать в блоки 2 должна производиться на такт раньше (т.е. в последнем такте, когда во все счетчики 33 всех блоков 2 занесен адрес программы записи, выдается Сигнал пуска с требуемого выхода блока 3). При поступлении на входы блока 6 команды Продолжение записи отличие от рассмотренных выше действий связано с отсутствием необходимости наращивания содержимого счетчика 53 блока 3 и записи в регистр 54. Теперь блок 2, получив команду записи по второму входу и сигнал пуска генератора 35, выполняет следующие действия. Если получена команда записи первого типа, то блок 2 сигналом микрооперации на первом выхо- де, коммутируемым на вход наращивания на 1 содержимого счетчика 14 блока 1 (фиг. 2) увеличивает содержимое указанного счетчика на 1, а. в следующем такте выдает сигнал записи в ОЗУ 12. По команде второго типа сначала счетчик 14 сбрасывается, а в следующем такте увеличивает содержимое на единицу, после чего вьщает команду записи в ОЗУ 12. Та- КИМ образом осуществляется запись в одну ячейку памяти. Для записи в следующую ячейку ЭВМ выставляет но

5

5

54

5 О 5

0

0

11 10 вый код на входа с блока 1 и вьщает очередную команду записи первого или второго типов.

Блок 1 работает следующим образом.

Для диагностики состояния процесса используются триггеры 21-23, и схема 19 сравнения на равенство О, Триггер 21 в установленном состоянии определяет, что соответствующий процесс в системе не существует (например, завершил реализацию и покинул систему), триггер 22 в установленном состоянии указывает, что соответствующий процесс заблокирован, т.е. ему для перехода на следующий шаг реализации либо не могут быть вьще- лены необходимые ресурсы, либо не срабатывает предикат, связанный с этим переходом.

Состояние триггера 23 (указателя просмотра) используется соответствующим блоком 2,для выдачи сигнала разблокировки (блок 6,7 алгоритма на фиг. 14) на соответствующий из микрооперационных выходов, поступающего на соответствующие входы блока 5 индикации условий. Наличие высокого уровня на выходе схемы 19 сравнения- (фиг. 2) определяет статус ожидающего процесса, т.е. свидетельствует, что время Т, необходимое для реализации шага k, истекло и процесс требует выполнения следующего шага реализации. Таким образом можно выделить две активные фазы реализации любого процесса: Ф - фаза выполнения перехода на следующий шаг реализации и Ф - фаза вьшолнения шага реализации.

Наиболее простой (в смысле управления) фазе Ф соответствует ненулевое содержимое счетчика 13 и низкий уровень на выходе схемы 19 сравнения. При этом соответствуюш 1Й блок 2 управления процессом не подает на входы блока 1 реализации процесса никаких управляющих воздействий. Изменение (уменьшение) содержимого счетчика 13 осуществляется сигналом с выхода элемента И 30 при поступлении импульсов на вход блока 1 реализации процесса от блока 4 модельного времени. При обнулении содержимого счетчика 13 любого из блоков 1 возникает высокий уровень ни выходе схемы 19 сравнения на равенство нулю, в результате чего обеспечивает

11

ся блокирование и останов генератора 71 импульсов модельного времени в блоке 5 модельного времени и запуск блока 6 управления устройством (через элемент ИЛИ 8).

Когда счетчик 13 обнуляется, начинается фаза Ф. Для останова генератора 71 (фиг. 13) выполняется пуск (рестарт) блока 6 сигналом запуска по цепи схема 19 сравнения блока 1 - выход элемента И 85 - эле мент ИЛИ 77 - элемент ИЛИ 8 - вход Пуск генератора 35 блока 6 (фиг. При этом сигнал с третьего выхода ула 74 блока 5 (фиг. 7) параллельно сигналу на первом выходе узла 74 потупает через элемент ИЛИ 79 на формирователь 76 и далее через элемент ИЛИ 81 на входы блоков 1, сбрасывая триггеры 22; параллельно сигнал через элемент ИЛИ 82 (фиг. 6) поступает на вход установки триггера 75, в результате своим инверсным выходом триггер 75 блокирует выход блока 4 через элемент И 7. Кроме того, рестарт блока 6 происходит с команды, следующей за последней выполненной командой, этой следующей командой является команда логического типа для проверки условия прерывания - все необходимые признаки собраны в первых выходах блока 5 индикации условий. Таким образом, начинает выполняться фаза Фд. При этом в счетчик 13 (фиг. 2) последовательно счи тываются ячейки ОЗУ 12 и выполняется дешифрация их кодовых признаков. Для адресации ОЗУ 12 используется счетчик 14. Первой ячейкой ОЗУ 12, открывающей следующий шаг реализации, является ячейка, содержащая признак и 2 U.J или U , т.е. приоритет или номер переменной ресурса. Если выбран приоритет (U , U), то содержимое счетчика 13 через блок 24 усиления импульсов поступает на накапливающий сумматор 20. Два управляющих входа накапливающего сумматора 20 (соответственно Сброс и Управление) позволяют в случае и занести в сумматор значение приоритета, а в случае U добавить к текущему содержимому сумматора 20 приращение приоритета.

Приоритет процесса есть любое (ограниченное разрядностью ОЗУ 12) неотрицательное число. Выходы сумматора 20 заводятся на соответст

0

54

0

0

0

5

вующие входы блока 3 выборки процесса.

Проверка Значения переменной состояния (кодовый признак U ) осуществляется, дешифратором 17, схемой 27 сравнения, элементами 28 и 26, при этом номер переменной из счетчика 13 через блок 24 переписывается в регистр 18 и поступает на входы дешифратора 17, в результате возбуждается тот выход дешифратора 17, который соответствует опрашиваемой переменной. После этого считывается следующая ячейка ОЗУ 12 с идентификатором U-. Принято, что номер переменной

D

соответствует номеру спрашиваемого разряда ячейки ОЗУ 12. Сравнение требуемого значения переменной и фактического (текущего) выполняется соответствующей схемой 27 сравнения, выход которой стробируется одноименным элементом И 28. В результате высокий потенциал на выходе элемецта ИЛИ 26 определяет условие совпадения требуемого и фактического значений опрашиваемой переменной состояния. В случае несовпадения значений блок 2 управления рассматриваемым блоком 1 реализации процесса обеспечивает по выходам элементов И 50 установку состояния Заблокирован (подачей сигнала на S-вход триггера 22) процесса; восстановление содержимого счетчика 14 (путем перезаписи содержимого счетчика-дублера 15 в счетчик 14, т.е. восстанавливается состояние процесса)j передачу управления в блок 6 управления устройством.

В случае успешного перехода на следующий шаг выполнение фазы Ф в блоке 1- реализации процесса завершается занесением в счетчик 13 времени реализации шага (U ), т.е. статус прерванный процесс (содержимое счетчика 13) т 0%( (процесс не завершен)S: (процесс не заблокирован).

В соответствии с алгоритмом работы устройства (фиг. 14, блоки 2, 3) завершение любого шага реализации сопровождается обращением к блоку 6 управления устройством (пуск через элемент ИЛИ 8) и остановом генератора 71 модельного времени. Для того, чтобы снова запустить генератор 71 необходимо выполнить действия, предусмотренные фазой перехода Ф для всех процессов, ожидаю131

щих перехода. Порядок выполнения этих действий следующий.

Необходимо найти процесс с максимальным приоритетом из числа ожидающих и не ЯВЛЯЮ1ЦИХСЯ заблокированными Если такого процесса нет, то фаза Фд завершена, в противном случае необходимо попытаться переве.сти данньй процесс на следующий шаг реализации. При этом, возможно, требуется уста- новка новьк значений переменных состояния, а также захват/освобождение ресурсов или их частей. Поскольку в этом случае может быть снято условие блокировки с других ожидающих про- цессов, то необходимо выполнить действия, указанные в блоках 3-10 алгоритма .

Блок 3 выборки процесса обеспечивает выборку процесса с максимальным приоритетом из числа ожидающих и незаблокированнык и работает следующим образом.

На первые входы узлов 60 поступаю коды текущих приоритетов с выходов соответствующих блоков 1 реализации процессов. Узел 60 опроса участвует в цикле опроса только при наличии высокого уровня от элемента И 31 соот- ветствующего блока 1 реализации процесса, который определяет наличие в системе незаблокированного и отдающего процесса. Цикл опроса приоритета всегда начинается с первого узла 60 опроса и заканчивается опросом (сравнением) приоритета в последнем узле 60. В результате опроса приоритета определяется номер процесса с максимальным текущим приоритетом, причем на информационные выходы узлов 60 (в порядке их прохождения) коммутируется максимальное значение приоритета из числа опрошенных процессов.

При опросе первого узла 60 отри- цательньй код из регистра 59 поступает на входы.узла 60 опроса и далее на мультиплексор 65 и схему 64 сравнения. На другие входы мультиплексо- ра 65 и схемы 64 сравнения поступает текущий приоритет процесса соответствующего рассматриваемого узла 60. Предположим, что данный процесс участвует в опросе (высокий уровень на

втором входе разрещения опроса узла 60 опроса). Тогда, если приоритет данного процесса больше отрицательного кода, то на прямом выходе схе

5 Ю

20

25 у Q

„ 35

5

1114

мы 64 сравнения имеется высокий уровень, а на инверсном - соответственно низкий, адресные разряды мультиплексора 65 обеспечивают коммутацию большего приоритета (т.е. в данном случае приоритета процесса) и по сигналу записи, задержанному элементом 67 задержки, обеспечивается запись большего приоритета в регистр| 66. При этом сигнал с выхода элемента И 63 через элемент ИЛИ 62 обеспечивает также перезапись содержимого счетчика 53 в регистр 54. Учитывая, что счетчик 53 определяет текущее значение номера опрашиваемого узла 60 опроса, результатом указанных действий является запись в счетчик 54, номера процесса (из числа просмотренных) с максимальным приоритетом.

Если в результате опроса на первых выходах последнего узла 60 опроса имеется отрицательн{ ш код, то это определяет условие завершения просмотра и выхода в блок 12 алгоритма (поскольку принято, что приоритеты процессов должны быть неотрицательными) .

Если процесс не участвует в смотре

(например, заблокирован), что соответствует низкому уровню на соответ- ствующем входе узла 60 опроса (фиг.5), адресные входы мультиплексора 65 обеспечивают коммутацию на выходе информации- с первых информационных входов узла 60.

При завершении цикла опроса в регистре 54 (фиг. 4) находится номер выбранного процесса, который дешифрируется дешифратором 56, возбуждая соответствующими первый вход элемента И 63, который соответствует выбранному процессу. При подаче сигнала Пуск на другие входы элементов И 63 от группы микрооперационных выходов III блока 6 управления устройством обеспечивается стробирование элементов И 63; причем появляется сигнал запуска на соответствующем выходе блока 3 выборки процесса. По этому сигналу запускается соответствующий блок 2 управления процессом и начинается фаза Фд попытки перехода на следующий шаг реализации для выбранного процесса.

Рестарт блока 2 начинается с проверки логических признаков, коммутируемых с выхода соответствующего бло

151

ка 1, Дальнейшие действия блока 2 обеспечивают следующие процессы в блоке 1: увеличение содержимого счетчика 14 на 1, считывание очередной ячейки ОЗУ 12 в счетчик 13 и декоди- рование идентификатора ячейки м на дешифраторе 16, после чего выполняются действия, связанные с тем, какая информация содержится в считанной ячейке памяти,

Пусть при выполнении фазы Ф потребовалась установка новых значений переменных состояния в блоке 11 переменных состояния. Это значит, что идентификатором последней считанной ячейки ОЗУ. 12 (фиг. 2) является U . В предыдущей считанной ячейке содержался номер переменной состояния. Имеем, что в регистре 18 содержится номер переменной состояния, а в счет чике 13 - значение переменной состояния. Коммутатор 9 (фиг. 9) обеспечивает коммутацию номера переменной и устанавливаемого значения с направления, соответствующего тому блоку управления процессом, который работает в рассматриваемый момент (высокий уровень выхода Г соответствует прямому выходу триггера 37 наличия управления, (фиг. 3). Каждая коммутирующая ячейка 92 содержит групповые элементы И (фиг. 9 S), информация с выходов которых снимается при наличии высокого уровня на входе Г| . Таким образом, на выходы групповых элементов ИЛИ 93 коммутируется номер переменной или ресурса, на выходы элемента ИЛИ 94 - с направлений Б - значение переменной состояния (или запрашиваемая/освобождаемая емкость ресурса), на вы- ход$1 элемента ИЛИ 95 - управляющие разряды (группа микрооперационных выходов В работающего блока управления процессом).

В рассматриваемом случае установки новых значений переменных состояний номер переменной с первых выходов коммутатора поступает на дешифратор 115 блока 11 переменных состояния (фиг. 12). Под действием управляющего сигнала обеспечивается сра- батьшание дешифратора 112 и подача сигнала записи на вход С требуемого

триггера 113, в результате записыва ется информация (О или 1), определяемая состоянием второго входа блока 11 переменных состояния. Требуемое

25

2954

5 О

0 -5

40

45

50

55

1116

(новое) значение переменной состояния, поступающее на второй вход блока 11 переменных состояния, определяется из разрядных вторых выходов коммутатора 9. Рассмотрим, как осуществляется попытка захвата (освобождения) ресурсов. Как и в случае установки переменных состояния, номер проверяемого ресурса определяется содержимым регистра 18 блока 1 реализации процесса (фиг. 2), а запрашиваемая (освобождаемая) емкость - кодом в счетчике 13, причем освобождаемой емкости соответствует отрицательный код, запрашиваемой емкости - положительный.

Коммутатор 9 обеспечивает выбор соответствующего активному блоку 2 управления процессом направления коммутации, при этом на входы блока 10 диагностики состояния ресурсов поступают соответственно код номера ресурса, код запрашиБаемой/осво.бождае- мой емкости и управляющие выходы коммутируемого блока 2 управления процессом. Управление блоком 10 диагностики состояния ресурсов может осуществляться через входы от блока 6 управления устройством. ОЗУ 96 (фиг. 10) блока диагностики состояния ресурсов содер кит общие (исходные) емкости ресурсов системы. Обращение к ОЗУ 96 выполняется по адресу (номеру ресурса) ,, заносимому с входов рассматриваемого блока. Величина общей емкости опрашиваемого ресурса помещается в регистр 98 и далее через блок 100 коммутируется на первые входы узлов 105 опроса ресурсов. Выбор конкретного узла 105 опроса ресурсов, соответствующего принятому номеру ресурса, реализуется возбуждением конкретного выхода дешифратора 104.

Узел 105 работает следующим образом.

В накапливающем сумматоре 109 и регистре 107 хранится код, соответствующий текущему значению используемой емкости опрашиваемого ресурса (узлы 105). Величина запрашиваемой/ /освобождаемой емкости через блок 99 поступает на входы узлов 105 опроса ресурсов и далее на мультиплексор 108. Триггер 111 обеспечивает (в данном случае) коммутацию информации с вторых входов узлов 105 опроса ресурсов и далее на сумматор

109. Под действием сигнала управлег- ния с одного из входов узла 105 оп- .роса ресурсов текущее содержимое акг кумулятора складывается с величиной запрапгаваемой/освобождаемой емкости, причём результат сложения (интерпретирующий новое значение используемой емкости рассматриваемого ресурса при переходе на следующий шаг реализации процесса) сравнивается с исходной емкостью данного ресурса, код которой поступает на первые входы узла 105. Управляющий сигнал от дешифратора 104 блока 10 диагностики состояния ресурсов обеспечивает срабатывание схемы 110 сравнения. Б случае, если исходная емкость ресурса недостаточна (т.е. запрос на ресурс не может быть удовлетворен), на выходе схемы 110 сравнения имеется низкий уровень. Это значит, что процесс нужно заблр- кировать, а для всех опрошенных (дан-I ным процессом).ресурсов восстановить их состояние. Восстановление состояния ресурсов осуществляется перезаписью содержимого регистра 107 всех узлов 105 опроса ресурсов в сумматор 109 путем изменения адресных входов мультиплексора 108 и последовательным сбросом сумматора 109 и добавлением содержимого регистра 107.

В регистре 112 хранится код последней запрашиваемой/освобождаемой емкости, что используется для анализа тупиковых ситуаций, возникающих в системе. .

В случае невозможности захвата ресурса или значения переменной состояния, не допускающего возможность перехода процесса на следующий шаг реализации, блок 2 управления процессом устанавливает триггер 22 (который бьш до этого сброшен) и восстанавливает содержимое счетчика 14 записью в него содержимого счетчика- дублера 15 (запись в счетчик 15 со- . держимого счетчика 14 происходит всякий раз при успешной попытке перехода процесса на следующий шаг реализа10

15

проверяет логические признаки с первых выходов блока 5 и, есхш отсутствует системный тупик, блок 6 вьщает сигнал пуска соответствующим микрооперационным выходам в группе V выходов блока 6, который коммутируется на пусковой вход генератора 71 блока 4 модельного времени.

Индикация состояния процессов в блоке 5 индика1щи условий осуществляется следующим образом. Ключевой схемой в рассматриваемом блоке является узел 74 проверки состояния (фиг. 7), на входы которого поступают: признак завершения процесса а. признак блокировки b,

20

25

30

35

40

45

1

и признак завершения шага

элереализации с-,, соответственно, мент И 85 (фиг,, 7) определяет неза- вершенньй, незаблокированный и ожидающий процесс,, элемент И 86 - состояние выполняемого (в фазе Ф ) процесса. Усиленный с выхода элемента И 85 сигнал через элементы ИЛИ 87 и 79 поступает на формирователь 76 импульса, формирующий импульс нужной длительности. Далее этот сигнал поступает, в частности, на один из выходов блока 5 индикации условий и затем через элемент ИШ 8 на запускающий вход блока 6 управления устройством, инициируя тем самым фазу Фд.

. Элемент ИЛИ 77 определяет условие наличия хотя бы одного процесса, требующего выполнения фазы Ф (попытки перехода на следующий шаг реализации) .

Элемент ИЛИ 78 определяет наличие в системе хотя бы-одного выполняющего процесса, а элемент ИЛИ 80 - наличие переполнения в счетчике 14 адреса блока 1 реализации процесса. Элемент ИЛИ 81 служит для разблокировки процессов (сброса триггеров 22 блоков 1).

Элемент И 83 определяет состояние тупика в системе, когда все процессы заблокированы, а элемент И 84 - условие завершения всех процессов в системе (условие завершения моделиции или при установке переменных сое- рования). тЬяния). При выполнении фазы Ф блок Триггер 75 обеспечивает блокиров- 6 все время опрашивает вторые выходы ку генератора 71 всяких раз, когда блоков 2. Нулевое содержимое этих вы- любой из процессов завершает очередной шаг реализации. Б этом случае вы- сокий уровень появляется на первом и третьем выходах узла 74 опроса; форходов заставляет блок 6 инициировать выборку процесса в блоке 3. Окончание выборки в блоке 3 устанавливается блоком 6 в результате проверки первых выходов блока 3. Далее блок 6

мирователь 76 liмпyльcoв обеспечивает подачу сигналов на вход триггера 75

5

проверяет логические признаки с первых выходов блока 5 и, есхш отсутствует системный тупик, блок 6 вьщает сигнал пуска соответствующим микрооперационным выходам в группе V выходов блока 6, который коммутируется на пусковой вход генератора 71 блока 4 модельного времени.

Индикация состояния процессов в блоке 5 индика1щи условий осуществляется следующим образом. Ключевой схемой в рассматриваемом блоке является узел 74 проверки состояния (фиг. 7), на входы которого поступают: признак завершения процесса а. признак блокировки b,

0

5

0

5

0

5

1

и признак завершения шага

элереализации с-,, соответственно, мент И 85 (фиг,, 7) определяет неза- вершенньй, незаблокированный и ожидающий процесс,, элемент И 86 - состояние выполняемого (в фазе Ф ) процесса. Усиленный с выхода элемента И 85 сигнал через элементы ИЛИ 87 и 79 поступает на формирователь 76 импульса, формирующий импульс нужной длительности. Далее этот сигнал поступает, в частности, на один из выходов блока 5 индикации условий и затем через элемент ИШ 8 на запускающий вход блока 6 управления устройством, инициируя тем самым фазу Фд.

. Элемент ИЛИ 77 определяет условие наличия хотя бы одного процесса, требующего выполнения фазы Ф (попытки перехода на следующий шаг реализации) .

Элемент ИЛИ 78 определяет наличие в системе хотя бы-одного выполняющего процесса, а элемент ИЛИ 80 - наличие переполнения в счетчике 14 адреса блока 1 реализации процесса. Элемент ИЛИ 81 служит для разблокировки процессов (сброса триггеров 22 блоков 1).

Элемент И 83 определяет состояние тупика в системе, когда все процессы заблокированы, а элемент И 84 - условие завершения всех процессов в системе (условие завершения моделимирователь 76 liмпyльcoв обеспечивает подачу сигналов на вход триггера 75

19 1295

и запускает этим же сигналом блок 6 управления устройством. При этом блок 6 управления устройством рес- тартует с предыдущей точки прерывания (т.е. фактически начинает новый 5 цикл выполнения фазы Ф).

Длина импульса, обеспечиваемого формирователем 76, определяется величиной задержки элементом 89, причем триггер 88 в исходном состоянии сбро- Ю шен, а при появлении высокого уровн-я на входе устанавливается в 1 через время, определяющее длительность импульса на выходе формирователя 76 импульса.

Занесение исходной информации о .моделируемой системе выполняется по входам устройства: по входам блоков 1 обеспечивается занесение информации, описьшающей реализации процес- сов, по входам блока 10 заносится информация об емкостях (объемах) ресурсов системы.

Выходы устройства обеспечивают получение следующей информации: первая группа выходов блоков служит для возврата управления (например, управляющей микро-ЭВМ), выход триггера 37 блока 6 определяет наличие/отсутствие управления со стороны блока 6 уп- равления устройством, выходы блоков 1 позволяют получить коды текущих номеров шагов реализаций процессов, выходы блока 10 устройства - информацию о текущих (занимаемых) емкостях ре- сурсов и величинах последних запросов на ресурсы, а выходы блока 11 устройства - значения переменных состояния устройства, на выходы блока 4 устройства поступает код модельного времени.

Формула изобретения

1. Устройство для моделирования дискре -ных систем, содержащее элемент И, элемент ИЛИ, блок диагностики состояния ресурсов и блок модельного времени, первый и второй такто- вые выходы блока модельного времени соединены соответственно с первым прямым и первым инверсным входами элемента И, первая группа информационных входов блока диагностики, сое-

тояния ресурсов является группой входов задания ресурсов устройства, а группа выходов блока диагностики состояния ресурсов является группой вы

5

15

5

0

35

0

45

Q .5,5

1120

ходов текущего состояния ресурсов устройства, отличающееся тем, что, с целью расишрения функциональных возможностей за счет моделирования требуемых схем динамических приоритетов и логики взаимодействия заявок в многофазных системах массового обслуживания, оно дополнительно содержит блок переменных состояния, коммутатор, блок выборки процесса, блок индикации условий, группу блоков реализации процесса, блок управления устройством и группу блоков управления процессами, каждый блок реализации процесса группы содержит оперативное запоминающее устройство, информационный и два адресных счетчика, первый и второй дешифраторы, регистр, схему сравнения на равенство нулю, сумматор, первый, второй и третий триггеры, блок усиления импульсов, первый и второй элементы Ш1И, группу схем сравнения, группу элементов И, элемент задержки, первьй и второй разрядные выходы первого адресного счетчика соединены соответственно с разрядными входами

второго адресного счетчика и адресными входами оперативного запоминающего устройства, выходы которого со- ед 1нены соответственно с разрядными входами 1П1формационного счетчика, вход управления записи которого соединен с выходом элемента задержки, разрядные выходы кодового признака слова информационного счетчика соединены соответственно с входами первого дешифратора, а остальная группа разрядных выходов информационного счетчика соединена с входами схемы сравнения на равенство нулю и блока усиления импульсов, вычитающий вход информационного счетчика подключен к выходу первого элемента И, разрядные выходы второго адресного счет- ч-ика подключены соответственно к разрядным входам первого адресного счетчика, выходы блока усиления импульсов соединены с информационными входами сумматора, разрядными входами регистра и первыми входами группы сравнения соответственно, разрядные выходы регистра подключены соответ-- ственно к входам второго дешифратора, выходы которого соединены соответственно с первыми входами элементов И группы, вторые входы которых подключены соответственно к выходам схем сравнения группы, выходы элементов И

группы подключены соответственно к входам первого элемента ИЛИ, выход первого триггера соединен с первьп и инверсными входами первого и второго элементов И, вторые инверсные входы которых подключены к выходу второго триггера, первьш вход которого соединен с выходом второго элемента ИЛИ выход схемы сравнения на равенство нулю подключен к первому прямому входу второго элемента И, каждый блок управления процессом, а также блок управления устройством содержат постоянное запоминающее устройство, адресный счетчик, регистр микрокоманды, генератор тактовых импульсов, мультиплексор, первый и второй триггеры, дешифратор, первый и второй элементы задержки, четыре элемента И, первый, второй, третий и четвертый элементы ИЛИ, группы выходных элементов И, группу схем сравнения группу опрашивающих элементов И, выходы постоянного запоминающего устройства подключены к информационным входам регистра микрокоманды, вход записи регистра микрокоманды соединен с выходом первого элемента задержки, вход которого соединен с входом управления чтением постоянного запоминающего устройства и первым выходом генератора тактовых импульсов, адресные входы постоянного запоминающего устройства соединены соответственно с разрядными выходами адресного счетчика, разрядными входами которого являются выходы мультиплексора, суммирующим входом и входом записи адресного счетчика являются соответственно выходы первого и второго элементов ИЛИ, группа адресных разрядных выходов регистра микрокоманды подключена соответственно к первой группе информационных входов мультиплексора, управляющими входами мультиплексора являются выходы первого триггера, группа разрядных выходов номера логического условия регистра микрокоманды соединена соответственно с входами дешифратора, а группа разрядных выходов кода микрооперации регистра микрокоманды соединена соответственно с первыми входами выходных элементов И группы, вторые входы которых подключены к выходу первого элемента И, выход второго элемента И соединен с входом второго элемента задержки,

0

5

0

5

0

5

0

5

0

5

вьпсод которого подключен к первым входам третьего и четвертого элементов И, выходы которых подключены к . первым входам первого и второго элементов ИЛИ соответственно, выход третьего элемента ИЛИ соединен с первым входом второго триггера и входом останова генератора тактовых импульсов, второй выход которого подключен к первым прямьп входам первого и второго элементов И, второй прямой вход первого элемента И и первый инверсный вход второго элемента И соединены с выходом разряда типа микрокоманды регистра микрокоманды, выход разряда значения логического условия которого соединен с первыми входами схем сравнения группы, выходы которых подключены соответственно к первым входам опрашивающих элементов И группы, вторые входы которых подключены соответственно к выходам.дешифратора, а выходы - к входам четвертого элемента ИЛИ, гфямой и инверсный выходы которого соединены с вторыми входами третьего и четвертого элементов И соответственно, вторые входы первого и третьего элементов ИЛИ подк-шочены к выходам соответствующего элемента И группы выходных элементов И, блок выборки процесса содержз1т счетчик, два регистра, первьй и второй дешифраторы, две схемы сравнения, группу узлов опроса, первьш и второй элементы ИЛИ и группу элементов И, группа разрядных выходов счетчика соединена соответственно с информационными входами перЕюго регистра, первого дешифраторе; и парной схемы сравнения, последний разряд счетчика соединен с первым входом первого элемента РШИ, выход которого подключен к входу сброса счетчика, выходы первого дешифратора подключены соответственно к первым входам разрешения опроса узлов опроса группы, информационные выходы k-ro узла опроса (, М-1) соединены соответственно с информационными входами первой группы (k+1)-ro узла опроса, разрядные выходы второго эегистра подключены соответственно к информационным входам первой группы первого узла опроса, а информационные выходы М-го узла опроса подключены соответственно к входам второй схемы сравнения, выходы окончания опроса всех узлов опроса подключены соответственно к группе вхо

23

дов второго элемента ИЛИ, выход которого соединен с входом записи первого регистра, разрядкою выходы которого подключены соответственно к входам второго дешифратора, выходы которого подключены к первым входам элементов И группы соответственно, блок индикации условий содержит группу узлов проверки состояния,триггер, формирователь импульсов, шесть элементов ИЛИ, два элемента И, первый, второй и третий информационные выходы всех узлов проверки состояния группы подключены к входам соответственно первого, второго и третьего элементов ИЛИ, выход третьего элемента ШШ соединен с входом формирователя импульсов, выход которого подключен к первым входам четвертого и пятого элементов ИЛИ, выход пятого элемента ИЛИ соединен с первым входом триггера, блок переменных состояния содержит дешифратор, группу триггеров и блок усилия импульсов, выходы дешифратора подключены соответственно к тактовым входам триггеров , выходы которых соединены соответственно с информационными входами блока усиления импульсов, блок диаг- ностики состояния ресурса содержит элемент задержки, счетчик адреса, оперативное запоминаюш;ее устройство, дешифратор, регистр, группу элементов ШШ, элемент ИЛИ, три блока уси- дения импульсов и группу узлов опро- са ресурсов, первый и второй информационные входы и управляюш;ий вход каждого узла опроса ресурсов группы подключены к выходам соответственно первтэго, второго и третьего блоков усиления импульсов, выходы дешифра- -тора соединены соответственно с вхо- дами разрешения опроса узлов опроса ресурсов, выходы сигнализации о наличии ресурсов которых подключены соответственно к входам элемента ИЛИ выходы первого, второго и третьего элементов ИЛИ группы соединены соответственно с входом записи, суммирующим входом и входом сброса счетчика адреса, разрядные выходы которого подключены соответственно к входам дешифратора и адресным входам оперативного запоминающего устройства, выходы которого подключены соответственно к разрядным входам регистра разрядные выходы которого соединены соответственно с информационными вхо

5

0

54

5

0

5

0

1124

дами второго блока усиления импульсов, выход четвертого элемента ИЛИ г-руппы подключен к входу записи оперативного запоминающего устройства, вход считывания которого и вход элемента задержки соединены с выходом пятого элемента ИЛИ группы, выход элемента задержки подключен к входу записи регистра, в каждом блоке реализации процесса группы входов записи и считывания оперативного запоминающего устройства, вход элемента задержки, входы записи ij сброса второго адресного счетчика, входы записи, сброса и суммирующий вход первого адресного счетчика, первьш и второй входы первого триггера, второй вход второго триггера, первьм и второй входы третьего триггера, вход записи регистра, обнуляющий вход и вход разрешения сложения сумматора и первый вход второго элемента ИЛИ подключены соответственно к выходам выходных элементов И группы соответствующего блока управления процессом, выходы первого, второго и третьего триггеров, первого дешифратора и первого элемента И каждого блока реализации процесса группы подключены соответственно к вторым входам схем сравнения группы соответствующего блока управления процессом,, выходы вторых триггеров всех блоков управления процессами, выходы первой и второй схем сравнения блока выборки процесса, выходы первого, второго и шестого элементов ИЛИ, формирователя импульсов и первого и второго элементов И блока индикации условий, выход элемента ИЛИ и выход переполнения счетчика адреса блока диагностики состояния ресурса подключены соответственно к вторым входам схем сравнения блока управления устройством, вторые входы вторых элементов ИЛИ всех блоков реализации процесса группы подключены к выходу четвертого элемента ШШ блока, индикации условий, выход элемента И устройства соединен с прямым входом первого элемента ИЛИ всех блоков реализации процесса группы, информационные входы оперативных запоминающих устройств которых объединены и являются инфорйаци- онным входом устройства, выходы блока усиления импульсов блока переменных состояния являются выходами состояния переменных устройства и соединены

251

соответственно с вторыми входами схем сравнения всех блоков реализации процесса группы, выходы сумматоров которых подключены к вторым информационным входам соответствующего узла опроса блока выборки процесса, вторые входы разрешения опроса узлов опроса которого подключены к выходам вторых элементов соответствующих блоков выборки процесса, выходы блока усиления импульсов и регистра каждого блока реализации процесса группы соединены с первой группой соответствующих информационных входов коммутатора устройства, вторая группа информационных входов которого соединена с выходами соответствующих выходных элементов И группы всех блоков управления процессом, выходы вторых триггеров которых соединены с управляющими входами коммутатора устройства, первая группа информационных выходов которого соединена соответственно с входами дешифратора блока переменных состояния и раз- рядными входами счетчика адреса блока диагностики состояния ресурса, входы первого блока усиления импульсов которого подключены соответственно к второй группе информационных выходов коммутатора устройства,треть группа информационных выходов которого подключена соответственно к входам третьего блока усиления импульсо и первым входам элементов ИЛИ группы блока диагностики состояния ресурсов информационный выход второй группы коммутатора подключен к ин- формационньм входам триггеров группы блока переменных состояния, вход раз решения работы дешифратора которого соединен с первым выходом третьей группы информационных выходов коммутатора устройства, выход элемента ИЛИ и выход переполнения счетчика адреса блока диагностики состояния ресурса подключены к вторым входам соответствующих схем сравнения всех блоков управления процессами, разрядные выходы первых адресных счетчиков всех блоков реализации процессов образуют 1 руппу выходов состояния процессов устройства, второй тактовый выход блока модельного времени соединен с первым входом элемента ИЛИ устройст- на и первым входом третьего элемента ИЛИ блока индикации условий, выход триггера которого подключен к второ11 .26

му прямому прямому входу элемента И устройства, выход первого триггера каждого блока реализации процесса группы подключен к первому информационному входу соответствующего узла провер1си состояний и соответствующему входу второго элемента И блока индикации условий, выход второго триггера каждого блока реализации процесса группы подключен к второму информационному входу соответствующего узла проверки состояний и соответствующему входу первого элемента И блока индикации условий, выход схемы сравнения на равенство нулю каждого блока реализации процесса группы подключен к третьему информационному входу соответствующего узла проварки состояний, группа входов шестого элемента И1Ш которого соединена соответственно с выходами переполнения первых адресных счетчиков блоков реализации процесса группы, каждый вход группы шестого элемента ИЛИ блока индикации условий подключен к выходу соответствующего выходного элемента И группы блока управления процессом группы, вход запуска генератора тактовых импуль- сов, первый вход второго триггера и второй вход первого триггера блока управления устройством объединены и являются входом запуска устройства, входом останова, которого является второй вход элемента ИЛИ устройства, выход которого подключен к второму входу третьего элемента ИЛИ блока управления устройства, выход второго триггера которого, первая подгруппа выходов выходных элементов И группы, вторая группа информационных входов мультиплексора и объединенные второй Вход первого триггера и второй вход второго элемента ИЛИ блока управления «зтройством являются соответственно выходами-входами обмена информацией с ЭВМ, вторая подгруппа выходов выходных элементов И группы блока управления устройства подключена соответственно к вторым входам элементов И группы блока диагностики состояния ресурса, в блоке выборки процесса вход разрешения дешифрации первого дешифратора, информационный вход счетчика, второй вход первого элемента ШШ, первый вход второго элемента ИЛИ и объединенные вторые входы элементов И группы под25

2712954

ключены соответственно к выходам третьей подгруппы выходных элементов И группы блока управления устройством, выходы четвертой подгруппы выходных элементов И 5 группы которого подключены к вторым входам третьих элементов ИЛИ блоков управления процессом группы соответственно, в каждом из которых вход запуска генератора тактовых им- fO пульсов, первый вход первого тригге-- ра и второй вход второго триггера объединены и подключены к выходу соответствующего элемента И группы блока выборки процесса выходы пя- той подгруппы выходных элементов И группы блока управления устройством соединены соответственно с вторыми входами первого триггера и второго элемента ИЛИ и второй группой ин- 20 формационных входов мультиплексора каждого блока управления процессом, а выходы шестой подгрупкы выходных элементов И группы блока управления устройства соединены соответственно с вторым входом пятого элемента ИЛИ и вторым входом триггера блока индикации условий и входами запуска, останова и сброса блока модельного времени, группа информационных выходов которого является выходами времени работы устройства.

2. Устройство по п. 1, о т л и - ,чающееся тем, что блок модельного времени содержит генератор 35 импульсов, входы запуска и останова которого являются входами запуска и останова блока модельного времени, элемент И и счетчик, группа разрядных выходов которого является группой информационных выходов блока моделирования, входом сброса которого является вход сброса счетчика, выход генератора импульсов является первым тактовым выходом блока и соединен с прямым входом элемента И, выход которого подключен к счетному входу счетчика, выход обнуления которого является вторым тактовым выходом блока и соединен с инверсным входом эле- мента И.

5

54

O 0

5

1128

3. Устройство по п. 1, отличающееся тем, что узел опроса содержит схему сравнения, элемент задержки, элемент ШШ, два элемента И, регистр и мультиплексор, информационные входы первой и второй групп которого объединены с одноименными группами входов схемы сравнения и являются соответственно первым и вторым информационными входами узла опроса, информационными выходами которого являются разрядные выходы регистра, разрядные входы которого соединены соответственно с выходами мультиплексора, первый и второй управляющие входы которого подключены соответственно к выходу первого элемента И и выходу элемента ИЖ, первым входом разрешения опроса узла опроса являются объединенные первые входы первого и второго элементов И и инверсный вход элемента ИЛИ, прямой вход которого подключен к выходу второго элемента И, вторые входы элементов И и вход элемента задержки объединены и являются вторым входом разрешения опроса, выхрд элемента задержки соединен с входом записи регистра, выход первого элемента И является выходом окончания опроса узла опроса, а выходы Больше или равно и Меньше схемы сравнения соединены с третьими входами соот- ветстве;нно первого и второго элемен- тоц И.

4 о Устройство по п. 1, отличающееся тем, что узел проверки состояния содержит, первый и второй элементы И и элемент ИЖ, выходы которых являются соответствен- но первым, вторым и третьим информационными выходами узла проверки состояния, выход первого элемента И подключен к входу элемента ИЛИ, а одноименные входы элементов И объединес

ны и являются-.соответственно первым, вторым итретьим информационными входамиузла проверки состояния.

f J.

ТВ

n

2f

r;

(a

|C Z

JT

«

L

5i7

mi

ТП

a

f

i

/77

H

Л7.

:h

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обменом информацией | 1990 |

|

SU1783525A1 |

| Многоканальное устройство приоритета | 1989 |

|

SU1661765A1 |

| УСТРОЙСТВО ДЛЯ ОПРОСА ИНФОРМАЦИОННЫХ КАНАЛОВ | 2004 |

|

RU2268546C1 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

| Многоканальное устройство приоритета | 1984 |

|

SU1264177A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1550518A1 |

Изобретение относится к вычислительной технике и предназначено для моделирования сложных дискретных систем. Целью изобретения является расширение функциональных возможностей устройства за счет моделирования требуемых схем динамических приоритетов и логики взаимодействия заявок в многофазных системах массового обслуживания. Устройство содержит группу блоков реализации процесса,группу блоков управления процессами, блок выборки процесса, блок модельного . времени, блок индикации условий,блок управления устройства, элемент И,элемент ИЛИ, коммутатор, блок диагностики состояния ресурсов, блок переменных состояний. Устройство обеспечивает реализацию процессов в соответствии с вводимыми описаниями, включающими порядок захвата/освобождения ресурсов и требуемые при этом емкости ресурсов, схемой установки приоритетов по шагам реализации, описанием . логики установки/сброса переменных состояния системы для синхронизации взаимодействующих процессов. 3 з.п. ф-лы, 14 ил. с & (Л с ьс QO СП 4

n

||«лй/« ,

ЯЛ9

tmi t.S

:«А2

ГлгЗ

Vui.

СРи.2.6

0 Ci 85

Лб/1окд 1

Нд.ну78

Н блоку 79

Риг1

(Риг.9

xfл.г,f

«

1 g7РТз с /77 dffOfia Wu

Ш К

W9

От б/гона 99

6/toHQ ЮЧ

Ч

Л

Г W

Зп

иг

t

АУ8 -г о

Ндлояуюб дыкод Выкоо (риг.11

Сброс

105

От 6лока 101

I

Зп

иг

Вы

Лдй

я блоку 7 « блоку 1,6 xoff

Фиг.П

/BSod описаний/ (ноуа/ о) /

Выполнить дейстбия, сбязан ные с попыткой перехода на следующий шаг реализации

TpeSyemcS станобка переменных состояния

Да

Процесс

росматрибается перSt/u pas

Нет

Нет

Да

7

Раэ5локиро5ат1)(6се процессы

а. Устанабить переменные

состояниа;

S. Выполнить пробери у ноли- чия docmynHbif. ресурсоб

Нет

W

L

и

Завершить Hode/iupoSanue 6t)idaveu сообщения о SfiOKUpoSKC

Запустить моде/гднош таймер и ждать пербого о нулениа счетчика бремени реализации /7/odago быполняемого процесса. При обнулении сметчика оста - побить таймер и раз локиро- бать процессы

а

Занести 6 с етчик- -таинер данного процесса очередное значение бремени реализации. Процесс получает статус ,: прербанногр Pa3f/70Kupo о а mil бее процессы

Восстанобить состояние процесса и за6.покиробатй eeo t спросить триггер просмотра

Составитель В.Фуьсалов Редактор И. Николайчук Техред И. Попович Корректор А.Обручар

ив-в -- -и -™-чм1в- ------«-- - - - -р--™

Заказ 619/56 Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для статистического моделирования процессов выполнения системы работ | 1977 |

|

SU708356A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования процесса обслуживания заявок с различными приоритетами | 1983 |

|

SU1091170A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-07—Публикация

1985-07-17—Подача