Изобретение относится к-вычислительной технике и может быть использовано в многоканальных системах отображения информации.

Целью изобретения является расширение области применения устройства за счет обеспечения возможности отображения информации от нерезервированных источников информации.

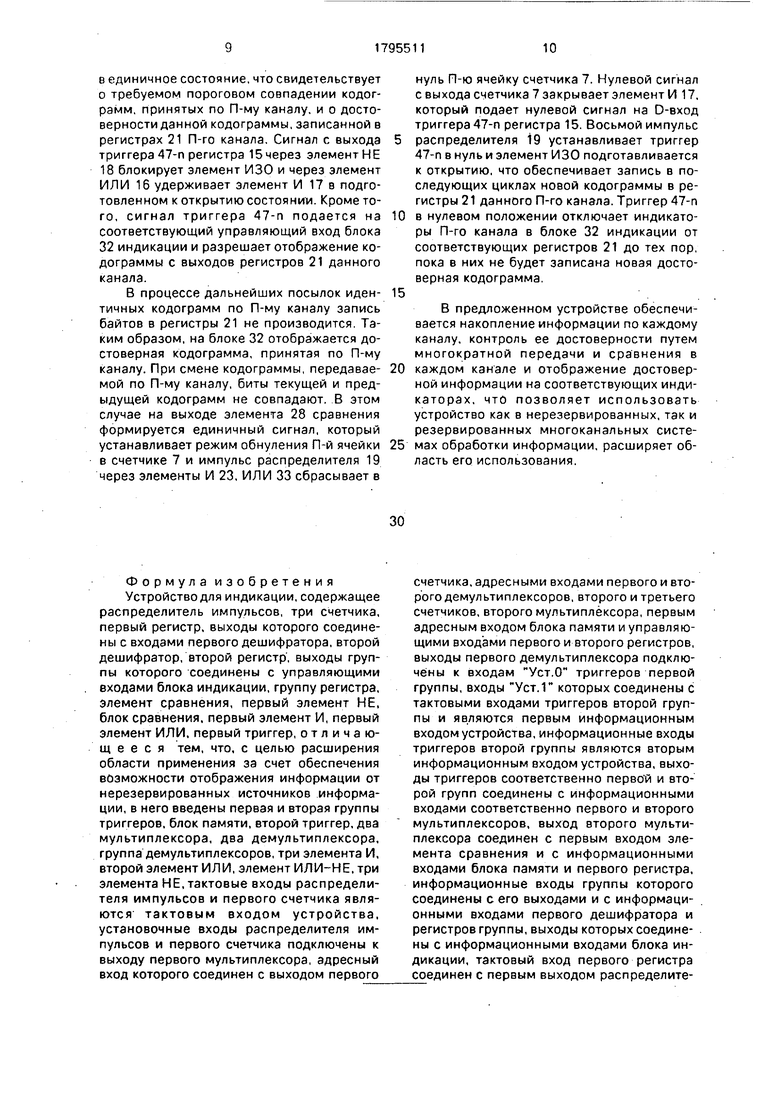

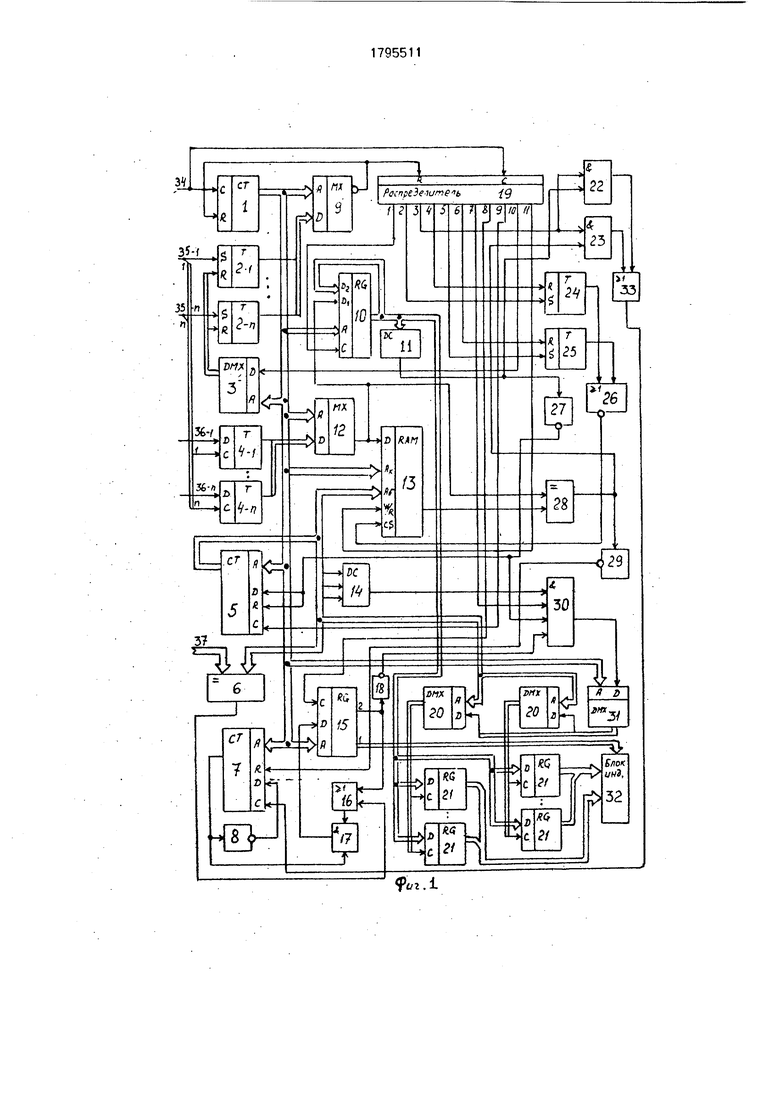

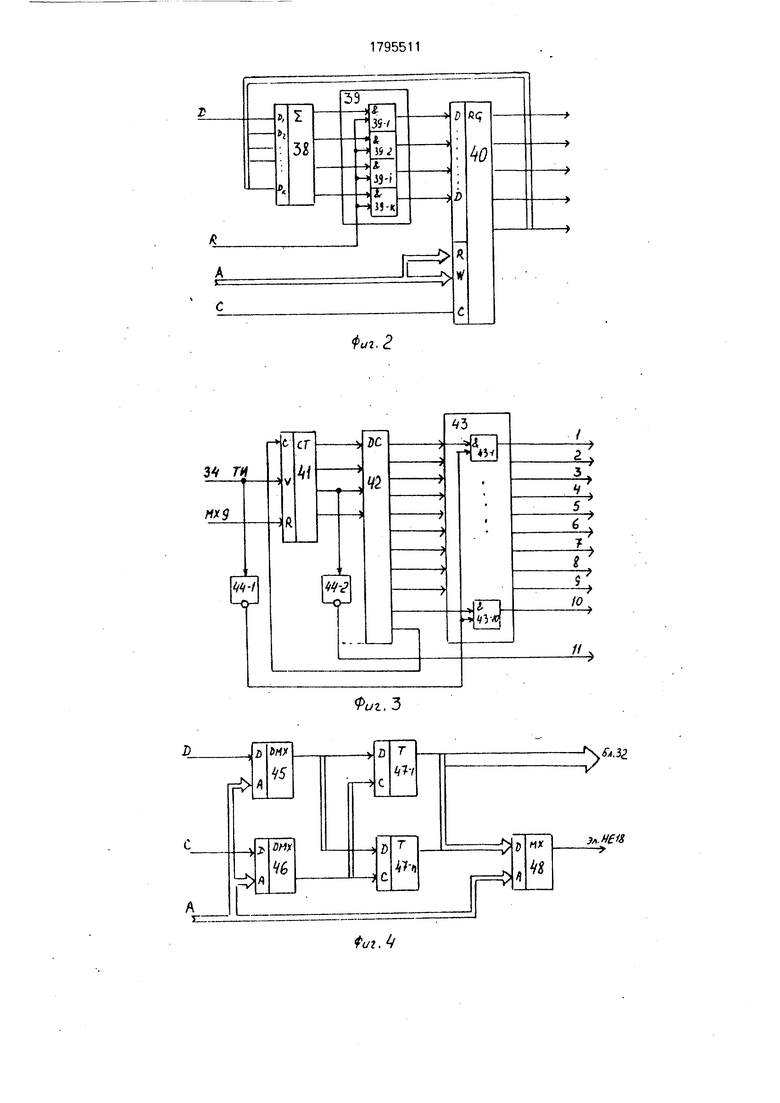

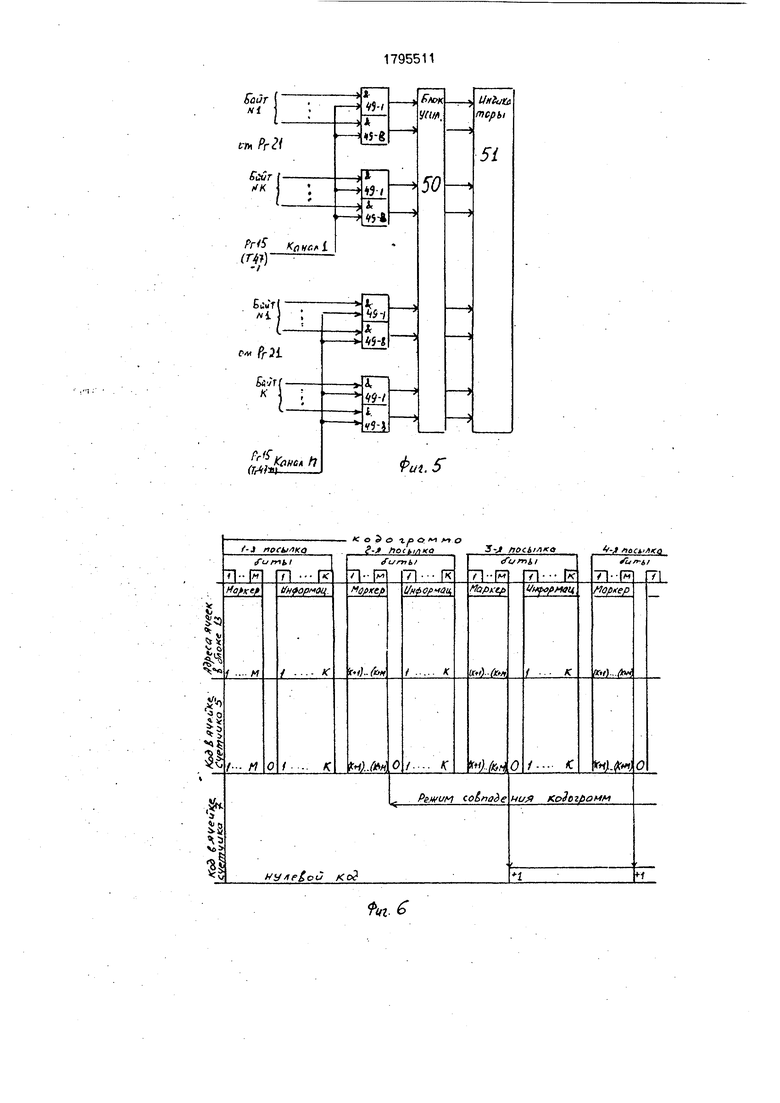

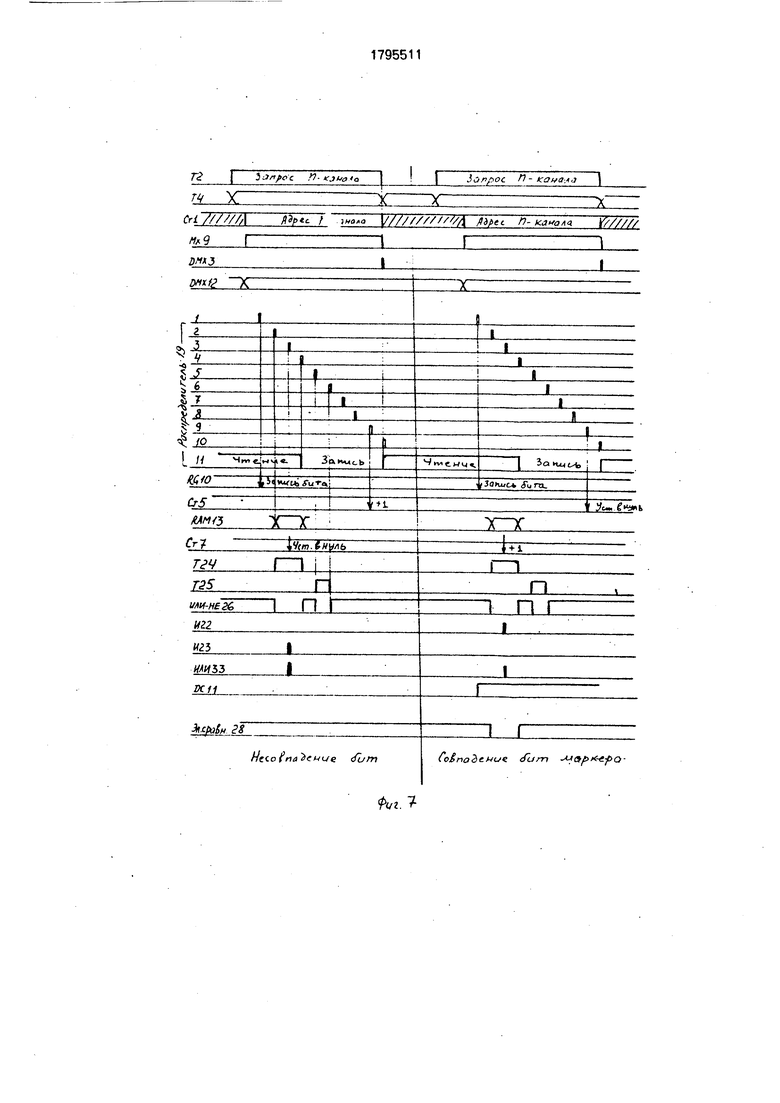

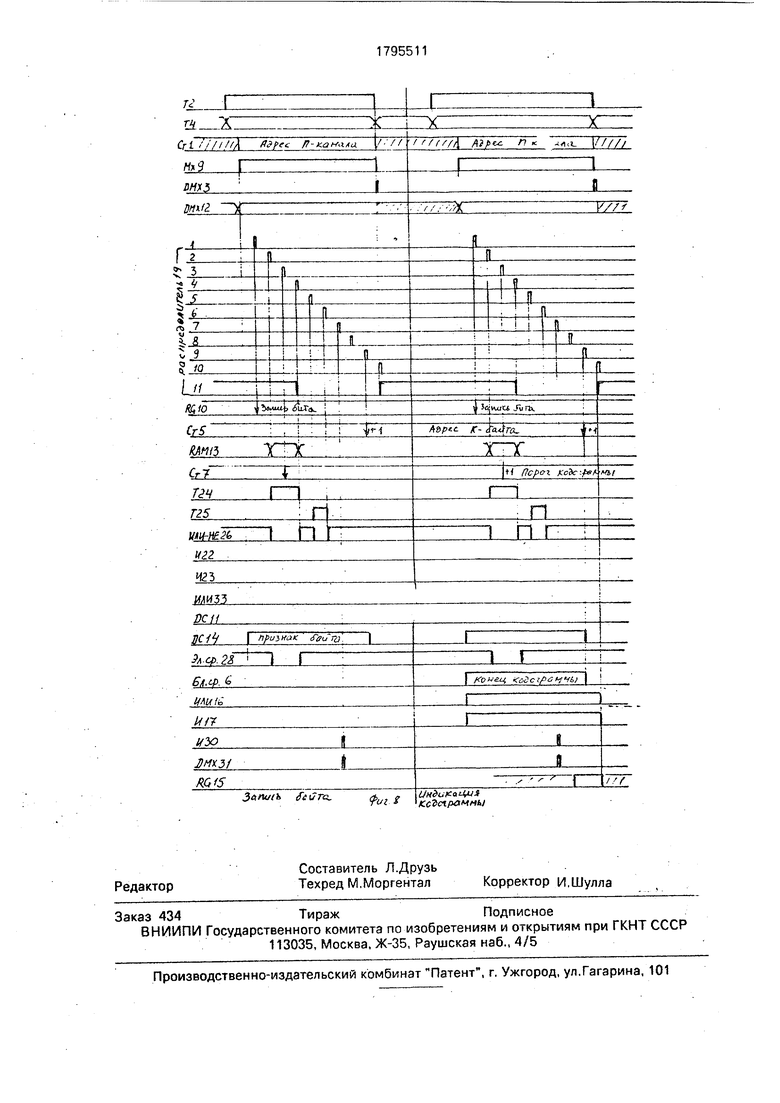

Функциональная схема устройства приведена на фиг.1, схема многоканальных счетчиков- на фиг.2, схема распределителя импульсов - на фиг.З, схема многоканального регистра - на фиг.4, схема блока индикации - на фиг.5, распределение адресов бит при обработке кодограмм - на фиг.б, временная диаграмма работы устройства - на фиг.7. 8.

Устройство содержит счетчик 1 адресов каналов, триггеры 2 запросов каналов, де- мультиплексор 3. триггеры 4 информации каналов, счетчик 5 адресов байт, блок 6 сравнения, счетчик 7 кодограмм, элемент

НЕ 8, мультиплексор 9, регистр 10, дешифратор 11 маркеров, мультиплексор 1.2, блок 1.3 памяти, дешифратор 14 байт, регистр 15, элементы ИЛИ 16, И 17, НЕ 18, распределитель 19 импульсов, группу демультиплексоров 20, группу регистров 21, элементы И 22, И 23, триггеры 24, 25, элемент ИЛИ-НЕ 26, элемент НЕ 27, элемент 28 сравнения, элементы НЕ 29, И 30, демультиплексор 31, блок 32 индикации, элемент ИЛ И 33, вход 34 тактовый, входы 35 запросов каналов, вход 36 информации каналов, входы 37 установочные. Счетчики 5, 7 (фиг.2) являются мно- гоканальными и содержат комбинационный . сумматор 38, коммутатор 39, групповой ре- гистр 40 накопления сумм. Распределитель 19 импульсов (фиг.З) содержит счетчик 41, дешифратор 42, коммутатор 43, элементы НЕ 44-1,44-2. Регистр 15 (фиг.4) содержит демультиплексоры 45,46, триггеры 47, мультиплексор 48. Блок 32 индикации (фиг.5) содержит элементы И 49. усилители 50. индикаторы 51.

ч ю ел ел

Устройство работает следующим образом.

По каналам, обслуживаемым устройством, в последовательных кодах поступают кодограммы стандартного формата, с определенным числом байт в кодограмме. Каждая кодограмма содержит идентичный признак кодограммы - маркер и информационную часть, которая отображается соответствующими индикаторами блока.32. Для достоверного отображения кодограмм передача одной и той же кодограммы по каждому каналу многократно повторяется не менее некоторого порогового числа раз и каждая последующая кодограмма сравнивается с предыдущей. Каждому каналу соответствует определенный триггер запроса из группы триггеров 2 и информационный триггер из группы триггеров 4. Регистр 10 представляет собой групповой регистр накопления байтов. Каждому каналу в этом регистре соответствует ячейка, адресуемая счетчиком 1 по входам запись/чтение этого регистра. За счет обратной связи с выходов регистра 10 на группу его входов, сдвинутых на один разряд, обеспечивается преобразование последовательного кода в параллельный. При этом каждый бит сдвигает предыдущие биты по разрядам ячейки до накопления в ней байта кодограммы для данного канала. Запирь текущего бита в ячейку производится тактовым импульсом с первого выхода распределителя 19, который подается на тактовый вход регистра 10. При подаче адреса со счетчика 1 на входы запись/чтение регистра 10 обеспечивается непрерывное считывание кода из данной ячейки регистра 10.

Регистр 15 предназначен для хранения результата сравнения кодограмм, в этом регистре демультиплексоры 45, 46, адресуемые счетчиком 1, выбирают соответствующий триггер 47 данного канала, который фиксирует результат совпадения кодограмм. Через мультиплексор 48 триггер 47 выбранного канала управляет записью кодограмм в соответствующие регистры 21 через элемент И 30 устройства и непосредственно разрешает индицирова- ние информации в блоке 32 индикации.

Блок 32 индикации отображает на индикаторах 51 байты кодограмм, поступающие с выходов регистров 21 через элементы И 49, управляемые триггерами 47 регистра 15, и усилители 50.

Счетчики 5,7 представляют собой идентичные групповые блоки накопления сумм. Счетчик 5-предназначен для суммирования числа бит, поступающих по каждому каналу, и формирует адреса бит и байт для каждого

канала. Счетчик предназначен для суммирования числа совпавших кодограмм при их побитном сравнении, причем суммирование ведется по числу маркеров совпавших

кодограмм, и формирует сигнал при пороговом значении указанной суммы для каждого канала. В состав каждого из счетчиков 5, 7 входит групповой регистр 40 накопления суммы, в котором каждому каналу соответствует счетная ячейка, адресуемая по входам запись/чтение счетчиком 1. В этой ячейке хранится сумма чисел, накапливаемая счетчиком для данного канала. При подаче адреса П-го канала на вход R регистра

5 40 с его выходов из П-й ячейки считывается код суммы, который подается на группу входов сумматора 38, где суммируется с единицей, подаваемой на D-вход счетчика (сумматора 38). При подаче единичного сиг0 нала на R-вход счетчика открывается коммутатор 39 и код суммы-с выходов сумматора поступает на D-входы ячейки регистра 40, адресуемой по входу W счетчиком 1, Запись суммы в ячейку производится импульсом с

5 соответствующего выхода распределителя 19, который подается на тактовый вход регистра 40. Для установки в нуль счетной ячейки данного канала на вход R счетчика подается сигнал нулевого уровня, при этом

0 коммутатор 39 закрывается и на D-входы регистра 40 в данную ячейку поступает нулевой код, который записывается в нее импульсом, поступающим на тактовый вход регистра 40. Распределитель 19 выполняет

5 функции блока управления, запуск распределителя производится снятием сигнала сброса с R-входа счетчика 41, который считает по срезу тактовых импульсов, поступающих по входу 34 устройства. Состояния

0 счетчика 41 декодируются дешифратором 42, который формирует десять управляющих сигналов, стробируемых тактовыми им- пульсами через элемент НЕ 44-1 и коммутатор 43. Нулевое и единичное значе5 ние третьего разряда счетчика 41 через элемент НЕ 44-2 и одиннадцатый выход распределителя задает в одном цикле его работы последовательно режимы чтения и записи бита кодограммы в блок 13 памяти

0 устройства. Сигнал с 11-го выхода дешифратора 42 воздействует на управляющий вход счетчика 41, запрещает счет, и цикл работы распределителя заканчивается. Триггеры 24, 25 формируют импульсы обращения к

5 блоку 13 памяти соответственно при чтении и записи бита кодограммы. Регистры 21 предназначены для хранения достоверных кодограмм, подлежащих отображению на блоке 32 индикации. Каждому каналу соответствует группа регистров 21, каждый из

которых обеспечивает хранение, например, байта кодограммы. Выбор группы регистров 21 канала обеспечивается демультип- лексором 31, адресуемым счетчиком 1, выбор регистра 21 в группе для записи байта - соответствующим демультиплексором 20, адресуемым счетчиком 5. Дешифратор 11 предназначен для обнаружения кода маркера кодограммы, анализирует коды, накапливаемые в ячейках регистра 10. Дешифратор 14 анализирует три младших разряда суммы бит, накапливаемой в ячейках счетчика 5, и формирует сигнал при накоплении формата байта.

В исходном положении триггеры 2, 4, 24, 25, регистры 21, счетчик 1 установлены в нулевое состояние (цепи начальной установки не показаны). По входам 37 устройства постоянно подан код формата кодограммы (число байт), по входу 34 устройства на счетчик 1 и распределитель 19 поступают тактовые импульсы. Счетчик 1 через мультиплексор 9 циклически и последовательно опрашивает выходы триггеров 2 и через мультиплексор 12 - выходы триггеров 4. При отсутствии сигналов триггеров 2 на инверсном выходе мультиплексора 9 формируется единичный сигнал, разрешающий счет тактовых импульсов в счетчике 1 и удерживающий распределитель 19 в нулевом состоянии. Канал П, передающий бит кодограммы, выставляет импульс запроса по входу 35-п и устанавливает в единичное состояние триггер 2-п. Бит кодограммы П-го канала с опережением подается на вход 36- п. D-вход триггера 4-п и по фронту импульса запроса триггер 4-п фиксирует данный бит кодограммы. При опросе включенного триггера 2-п на инверсном выходе мультиплексора 9 формируется нулевой сигнал, который блокирует счетчик 1 и включает распределитель 19. На выходах счетчика 1 устанавливается адрес (номер) П-го канала. Счетчик 1 адресует в регистрах 10, 15 информационные ячейки, в счетчиках 5, 7 - счетные ячейки П-го канала, через демуль- тйплексор 3 подключает вход сброса триггера 2-п к десятому выходу распределителя 19, через мультиплексор 12 - выход триггера 4-п к информационному входу блока 13 памяти, регистра 10 и входу элемента 28 сравнения. Кроме того, счетчик 1 через де- мультиплексор 31 подключает D-вход соответствующего демультиплексора 20 к выходу элемента И 30, т.е. выбирает группу регистров 21. соответствующих П-му каналу. В n-ячейке регистра 10 накапливается информация, принимаемая по П-му каналу во время предыдущих запросов этого канала. Эта информация анализируется дешифратором 11 для выявления кода маркера кодограммы. Если код в П-ячейке регистра 10 не является кодом маркера, то на выходе дешифратора 11 сигнал не формируется, 5 злемент И 22 закрыт, элемент И 30 через элемент НЕ 27 подготовлен к открытию. Через элемент НЕ 27 на входы D, R счетчика 5 подан единичный сигнал, обеспечивающий режим счета числа бит, принимаемых по П0 му каналу. По сигналу запуска распределитель 19 выполнен цикл обработки бита П-го канала. В начале цикла на одиннадцатом выходе распределителя 19 установлен единичный потенциальный сигнал, который за5 дает режим чтения на входе запись/чтение блока 13 памяти. На адресные входы блока 13 памяти поступают со счетчика 1 - адрес П-го канала, с выходов счетчика 5 - номер байта (бита) кодограммы, Импульс с первого

0 выхода распределителя 19 производит запись принятого бита и сдвиг информации в ячейке регистра 10. Импульс со второго выхода распределителя 19 устанавливает в единичное состояние триггер 24, который

5 через элемент ИЛИ-НЕ 26 подает нулевой сигнал выборки на блок 13 памяти. По указанному адресу из блока 13 памяти считывается бит, принятый для данного канала в предыдущем цикле обработки данной ко0 дограммы и имеющий то же знакоместо в кодограмме, что и текущий бит. Оба бита сравниваются элементом 28 сравнения. При приеме данной кодограммы в первый раз ее биты не совпадают с битами, хранящимися

5 в блоке 13 памяти. При несовпадении бит на входах элемента 28 сравнения последний формирует единичный сигнал, который открывает элемент И 23 и через элемент НЕ 29 устанавливает режим обнуления П-й

0 ячейки счетчика 7. Импульс с третьего выхода распределителя 19 через элементы И 23, ИЛИ 33 записывает нулевой код в П-ю ячейку счетчика 7. Импульс с четвертого выхода распределителя 19 сбрасывает в нуль триг5 rep 24, который обеспечивает требуемую длительность импульса обращения к блоку памяти, При этом на 11-м выходе распределителя 19 устанавливается нулевой сигнал, который задает режим записи информации

0 по входу запись/чтение блока 13 памяти. Импульс с пятого выхода распределителя 19 включает триггер 25. который через элемент ИЛИ-НЕ 26 подает сигнал выборки в блок 13. При этом в блоке 13 на место бита пред5 ыдущей кодограммы записывается бит текущей кодограммы. Импульс с шестого выхода распределителя 19 сбрасывает а нуль триг- . гер 25. Импульс с седьмого выхода распределителя 19 опрашивает элемент ИЗО. Если очередной байт кодограммы в П-ячейке регистра 10 не накоплен и в П-ячейке счетчика 5 не накоплен формат байта, то на выходе дешифратора 14 сигнал отсутствует и элемент ИЗО закрыт. Импульс с восьмого выхода распределителя 19 поступает на тактовый вход регистра 15. При этом триггер 47-п регистра устанавливается в нуль, т.к. на D-вход регистра 15 поступает нулевой сигнал с элемента И 17,закрытого нулевыми сигналами с выхода счетчика 7. Импульс с девятого выхода распределителя 19 увеличивает на единицу содержимое П-й ячейки счетчика 5. Импульс с десятого выхода распределителя 19 через демультиплек- сор 3 устанавливает в нуль триггер 2-п. На этом цикл обработки текущего бита П-го канала заканчивается. После сброса в нуль триггера 2-п снова формируется единичный сигнал на выходе мультиплексора 9, который отключает распределитель 19 и включает в режим счета счетчик 1. Счетчик 1 через мультиплексоры 9, 12 продолжает опрос триггеров 2,4 и при обнаружении сработанных триггеров 2 других или П-ro канала, аналогично, организует обработку запросов этих каналов. После накопления в П-й ячейке регистра 10 байта кодограммы этот байт подается на D-входы регистров 21. В текущем цикле в П-й ячейке счетчика 5 записан адрес-номер текущего байта, который поступает на демультиплексоры 20 и подключает соответствующий выход де- мультиплексора 31, адресуемого счетчиком 1, к тактовому входу соответствующего регистра 21 из группы регистров 21 данного П-го канала. Одновременно на выходе дешифратора 14 байт формируется сигнал, открывающий элемент ИЗО. Если этот байт не является маркером кодограммы, то нулевой сигнал дешифратора 11 через элемент НЕ 27 подготавливает к открытию элемент ИЗО. Кроме того, сигнал с выхода элемента НЕ 18 также подготавливает к открытию элемент ИЗО, т.к. многократная обработка кодограммы П-го канала еще не завершена. Таким образом, седьмой импульс распределителя 19 через элемент ИЗО, демультип- лексор31, соответствующий мультиплексор 20 обеспечивает запись данного байта кодограммы в соответствующий регистр 21. После накопления в П-й ячейке регистра 10 байта маркера кодограммы на выходе дешифратора 11 формируется единичный сигнал, который через элемент НЕ 27 устанавливает режим обнуления П-й ячейки счетчика 5, закрывает элемент ИЗО и подготавливает к открытию элемент И 22, В текущем цикле распределитель 19 устанавливает в нуль счетную П-ю ячейку счетчика 5, после чего в этой ячейке начинается счет бит информационной части кодограммы П-го канала. Если информационная часть кодограммы содержит К бит, то после обработки первой кодограммы по П-му каналу, т.е. после первой ее посылки, в блоке 13 памяти эта информация запишется в ячейках с 1 по К, а в П-й ячейке счетчика 5 зафиксируется адрес К. Во время второй посылки кодограммы ее маркер, содержа0 щий М бит, размещается в блоке 13 памяти в ячейках с (К+1) по (К+М) (фиг.6). После обработки этого маркера адресная П-я ячейка счетчика 5 обнуляется и счетчик 5 адресует в блоке 13 памяти ячейки с 1 по К, в которых

5 записана информационная часть предыдущей кодограммы. В этого момента биты информационных частей текущей и последующей кодограмм при отсутствии ошибок начинают совпадать. Во время сравнения

0 бит этих кодограмм на выходе элемента 28 сравнения формируется нулевой сигнал, который закрывает элемент И 23 и через элемент НЕ 29 задает режим суммирования в счетчике 7 кодограмм. В процессе обрэбот5 ки бит информационной части этой кодограммы, совпадающей с кодограммой предыдущей посылки, элементы И 22, 23 закрыты и третий импульс распределителя 19 не воздействует на счетчик 7. В процессе

0 третьей посылки данной кодограммы по П- му каналу биты ее маркера совпадают с битами маркера кодограммы предыдущей посылки, записанными в ячейках (К+1)...(К+М) блока 13 памяти. После накоп5 ления байта маркера в П-й ячейке регистра 10 сигнал дешифратора 11 открывает элемент И 22. В этом цикле третий импульс распределителя 19 через элементы И 22, ИЛИ 33 увеличивает на единицу содержи0 мое П-й ячейки счетчика 7. При последующих многократных поступлениях идентичных кодограмм по П-му каналу, их сравнении и совпадении, включая маркеры, содержимое П-й ячейки в счетчике 7 дости5 гает пороговой величины и на выходе счетчика 7 формируется сигнал, который через элемент Н Е 8 блокирует дальнейшее приращение суммы совпавших кодограмм в П-й ячейке счетчика 7 и подготавливает к откры0 тию элемент И 17. После приема последнего бита текущей кодограммы адрес в П-й ячейке счетчика 5 совпадает с установочным кодом формата кодограммы, заданным на входе 37 устройства. При этом на выходе

5 блока 6 сравнения формируется сигнал, который через элементы ИЛИ 16, И 17 подаётся на D-вход соответствующего триггера 47-п регистра 15, адресуемого счетчиком 1. В текущем цикле восьмой импульс распределителя 19 устанавливает этот триггер 47-п

в единичное состояние, что свидетельствует о требуемом пороговом совпадении кодограмм, принятых по П-му каналу, и о достоверности данной кодограммы, записанной в регистрах 21 П-ro канала. Сигнал с выхода триггера 47-п регистра 15 через элемент НЕ 18 блокирует элемент ИЗО и через элемент ИЛИ 16 удерживает элемент И 17 в подготовленном к открытию состоянии. Кроме того, сигнал триггера 47-п подается на соответствующий управляющий вход блока 32 индикации и разрешает отображение кодограммы с выходов регистров 21 данного канала.

В процессе дальнейших посылок идентичных кодограмм по П-му каналу запись байтов в регистры 21 не производится. Таким образом, на блоке 32 отображается достоверная кодограмма, принятая по П-му каналу. При смене кодограммы, передаваемой по П-му каналу, биты текущей и предыдущей кодограмм не совпадают. В этом случае на выходе элемента 28 сравнения формируется единичный сигнал, который устанавливает режим обнуления П-й ячейки в счетчике 7 и импульс распределителя 19 через элементы И 23, ИЛИ 33 сбрасывает в

нуль П-ю ячейку счетчика 7. Нулевой сигнал с выхода счетчика 7 закрывает элемент И 17, который подает нулевой сигнал на D-вход триггера 47-п регистра 15. Восьмой импульс

распределителя 19 устанавливает триггер 47-п в нуль и элемент ИЗО подготавливается к открытию, что обеспечивает запись в последующих циклах новой кодограммы в регистры 21 данного П-го канала. Триггер 47-п

в нулевом положении отключает индикаторы П-го канала в блоке 32 индикации от соответствующих регистров 21 до тех пор, пока в них не будет записана новая достоверная кодограмма.

В предложенном устройстве обеспечивается накопление информации по каждому каналу, контроль ее достоверности путем многократной передачи и сравнения в

каждом канале и отображение достоверной информации на соответствующих индикаторах, что позволяет использовать устройство как в нерезервированных, так и резервированных многоканальных системах обработки информации, расширяет область его использования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| Устройство для индикации | 1989 |

|

SU1686474A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Устройство для приема информации | 1988 |

|

SU1562950A1 |

Использование: вычислительная техника, система сбора и отображения с контролем информации от нерезервированных источников. Сущность изобретения: устройство содержит: 3 счетчика, 2 группы триггеров, 2 демультиплексора, 1 блок сравнения, 4 элемента НЕ, 2 мультиплексора, 2 регистра, 1 блок памяти, 2 дешифратора, 1 распределитель импульсов. 4 элемента И, 1 группу демультиплексоров, 1 группу регистров, 1 блок индикации, 2 элемента ИЛИ, 1 элемент ИЛИ-НЕ. 8 ил.

Формула изобретения Устройство для индикации, содержащее распределитель импульсов, три счетчика, первый регистр, выходы которого соединены с входами первого дешифратора, второй дешифратор, второй регистр, выходы группы которого соединены с управляющими входами блока индикации, группу регистра, элемент сравнения, первый элемент НЕ, блок сравнения, первый элемент И, первый элемент ИЛИ, первый триггер, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности отображения информации от нерезервированных источников информации, в него введены первая и вторая группы триггеров, блок памяти, второй триггер, два мультиплексора, два демультиплексора, группа демультиплексоров, три элемента И, второй элемент ИЛИ, элемент ИЛИ-НЕ, три элемента НЕ, тактовые входы распределителя импульсов и первого счетчика являются тактовым входом устройства, установочные входы распределителя импульсов и первого счетчика подключены к выходу первого мультиплексора, адресный вход которого соединен с выходом первого

счетчика, адресными входами первого и второго демультиплексоров, второго и третьего счетчиков, второго мультиплексора, первым адресным входом блока памяти и управляющими входами первого и второго регистров, выходы первого демультиплексора подключены к входам Уст.О триггеров первой группы, входы Уст.1 которых соединены с тактовыми входами триггеров второй группы и являются первым информационным входом устройства, информационные входы триггеров второй группы являются вторым информационным входом устройства, выходы триггеров соответственно перво й и второй групп соединены с информационными входами соответственно первого и второго мультиплексоров, выход второго мультиплексора соединен с первым входом элемента сравнения и с информационными входами блока памяти и первого регистра, информационные входы группы которого соединены с его выходами и с информационными входами первого дешифратора и регистров группы, выходы которых соединены с информационными входами блока индикации, тактовый вход первого регистра соединен с первым выходом распределителя импульсов, второй и третий выходы которого соединены с входами соответственно Уст.О и Уст. Г первого триггера, четвертый и пятый выходы распределителя импульсов соединены соответственно с входами Уст.О и Уст.1 второго триггера, выходы первого и второго триггеров соединены с входами элемента ИЛИ-НЕ, выход которого соединен с входом выборки блока памяти, второй адресный вход которого подключен к выходу второго счетчика, адресным входам демультиплексоров группы информационным входом второго дешифратора и первым информационным входам блока сравнения, второй информационный вход которого является третьим информационным входом устройства, выходы демультиплексоров группы соединены с тактовыми входами регистров группы, а информационные входы подключены к выходам второго демультиплексора, информационный вход подключен к выходу первого элемента И, первый вход которого подключен к выходу второго дешифратора, а второй вход соединен с шестым выходом распределителя импульсов, третий и четвертый входы первого элемента И подключены к выходам соответственно первого и второго элементов НЕ, вход второго элемента НЕ соединен с выходом первого дешифратора и с первым входом второго элемента И, первый вход третьего элемента И подключен к выходу элемента сравнения и входом третьего элемента НЕ, вторые входы второго и третьего элементов И подключены к седьмому выходу распределителя импульсов, а выходы соединены с входами первого элемента ИЛИ, выход которого подключен к тактовому входу третьего счетчика, установочный вход которого подключен к восьмому выходу распределителя импульсов, девятый выход которого подключен к тактовому входу второго счетчика, информационный вход которого подключен к выходу второго элемента НЕ, информационный вход третьего счетчика подключен к выходу четвертого элемента НЕ, вход которого соединен с выходом третьего счетчика и с первым входом четвертого элемента И, выход которого подключен к информационному входу второго регистра, тактовый вход которого подключен к десятому выходу распределителя импульсов, одиннадцатый выход которого соединен с информационным входом первого демультиплексора, выход второго регистра соединен с входом первого элемента НЕ и с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу блока сравнения, а выход - к второму входу четвертого элемента И.

«г.2

Фиг.Ъ

Л/г. 4

Ъг.6

| Устройство для индикации | 1985 |

|

SU1511763A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

| Устройство для индикации | 1989 |

|

SU1686474A1 |

| кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1993-02-15—Публикация

1990-12-25—Подача