Изобретение относится к вычислительной технике и может быть использовано в многоканальных вычислительных комплексах с магистралями последовательного и параллельного интерфейса.

Известно буферное запоминающее устройство, содержащее блок памяти, реверсивный счетчик, дешифратор, счетчик, триггер, регистр, формирователь импульсов, сумматор и элементы И.

Однако это устройство обеспечивает запись-считывание информации только от одного канала в параллельных кодах, что ограничивает его функциональные возможности и область использования.

Наиболее близким к предлагаемому по технической сущности является буферное запоминающее устройство, содержащее блоки памяти, входные и выходные регистры, блок синхронизации, распределитель, дешифратор, счетчики и коммутаторы.

В известном устройстве последовательно выполняются два этапа: этап ввода и этап вывода информации всем участвующим в обмене абонентам, причем этап вывода выполняется после окончания этапа ввода. Такая последовательность работы не позволяет одним абонентам считывать информацию в процессе записи (ввода) информации другими абонентами, что увеличивает время обмена информацией и снижает быстродействие устройства. Кроме того, в известном устройстве абоненты вводят информацию только в параллельных кодах, что ограничивает область использования известного устройства системами с параллельным интерфейсом.

Целью изобретения является расширение области применения устройства за счет

чередования циклов записи и считывания информации между передающими и принимающими каналами.

В буферное запоминающее устройство, содержащее блок памяти, выходы которого соединены с информационными входами выходных регистров, первый дешифратор, распределитель импульсов, коммутатор и счетчик, введены первая, вторая и третья

группы триггеров, первый, второй и третий мультиплексоры, первый, второй, третий и четвертый демультиплексоры, второй дешифратор, пербый и второй блоки регистров, суммирующий блок, блок сравнения,

триггер, элементы И, ИЛИ, НЕ, генератор импульсов, согласующие элементы, причем входы запросов передающих каналов устройства соединены с единичными входами триггеров первой группы и тактовыми входами триггеров третьей группы соответственно, входы запросов принимающих каналов устройства соединены с единичными входами триггеров второй группы, информационные входы устройства

соединены с информационными входами триггеров третьей группы. Выходы триггеров первой и второй групп соединены с ин- формационными входами первого мультиплексора, выход которого соединен с

входом элемента НЕ, выход которого соединен с управляющим входом распределителя и счетчика, тактовые входы которых соединены с выходом генератора импульсов, выходы счетчика соединены с адресными

входами первого, второго и третьего мультиплексоров, первого, второго, третьего и четвертого демультиплексоров, с адресными входами первого и второго блоков регистров, с адресными входами первой группы

блока памяти. Выходы триггеров третьей группы соединены с информационными входами второго мультиплексора, выход которого соединен с первым информационным входом первого блока регистров, выходы которого соединены с вторыми информационными входами первого блока регистров, информационными входами блока памяти и входами первого дешифратора, инверсный выход которого соединен с информационными входами первой группы третьего мультиплексора, группа вторых информационных входов второй группы которого соединена с инверсным выходом блока сравнения, выход третьего мультиплексора соединен с управляющим входом коммутатора и первым входом суммирующего блока, выходы которого соединены с информационными входами коммутатора, выходы которого подключены к информационным входам второго блока регистров, выходы которого соединены с вторыми входами суммирующего блока, третьи входы которого объединены с шиной питания, выходы старших разрядов второго блока регистров соединены с первыми входами блока сравнения, вторые входы которого являются четвертыми входами устройства, и группой вторых.адресных входов блока памяти. Выходы младших разрядов второго блока регистров соединены с входами второго дешифратора, инверсный выход которого соединен с первым входом элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с информационным входом первого демуль- типлексора, выходы которого соединены с нулевыми входами триггеров первой и второй групп. Первый выход распределителя импульсов соединен с информационным входом второго демультиплексора, группа выходов которого объединена с согласующим элементом и тактовым входом первого блока регистра, второй выход распределителя импульсов соединен с тактовым входом второго блока регистров, третий выход распределителя импульсов соединен с вторым входом элемента И, четвертый и шестой выходы распределителя импульсов соединены соответственно с единичным и нулевым входами триггера, выход которого соединен с входом выборки блока памяти, вход установки режима которого соединен с группой выходов третьего демультиплексора и согласующим элементом, информационный вход третьего демультиплексора соединен с нулевой шиной, пятый выход распределителя импульсов соединен с информационным входом четвертого демультиплексора, выходы которого соединены с

0 тактовыми входами выходных регистров,

седьмой выход распределителя импульсов

соединен с вторым входом элемента ИЛИ.

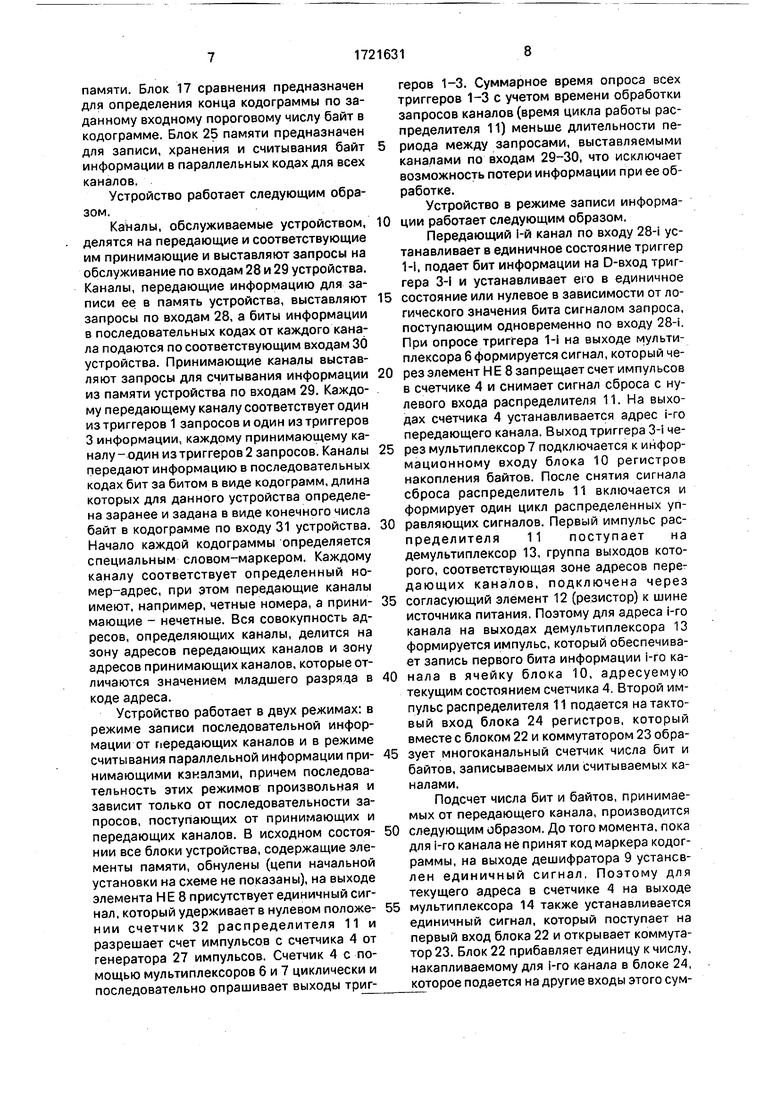

На фиг. 1 приведена функциональная

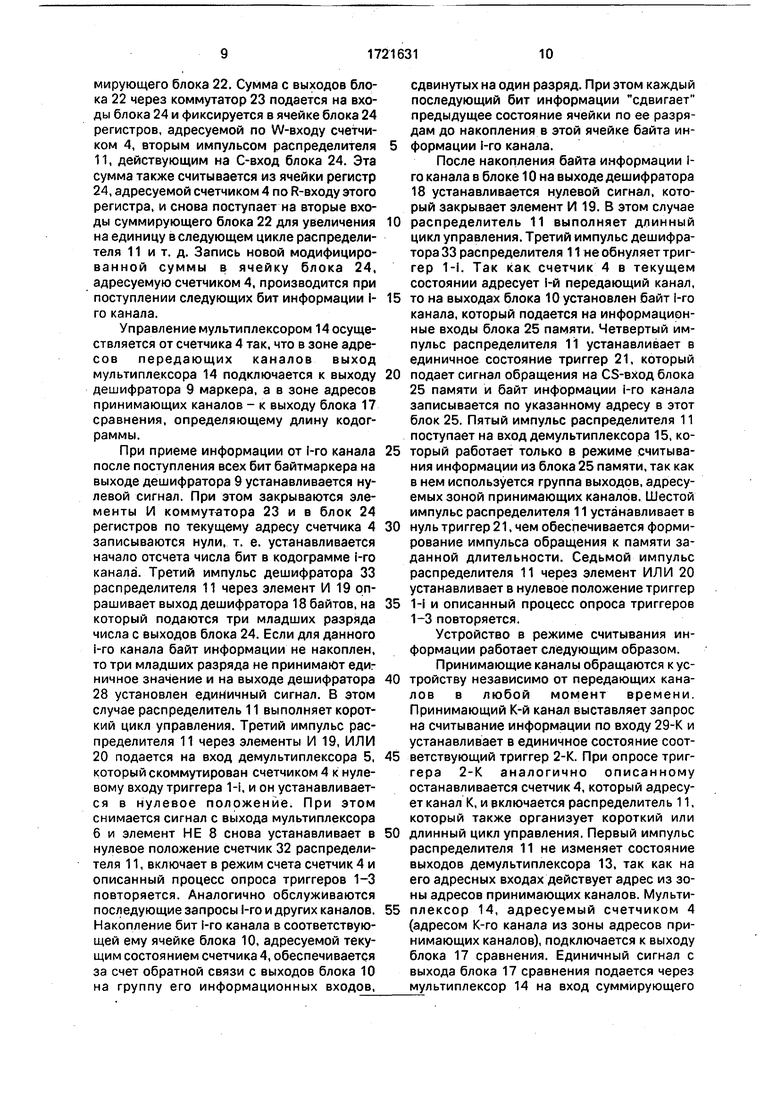

схема устройства; на фиг. 2 - временная

5 диаграмма его работы.

Устройство содержит первую группу 1 триггеров запросов от передающих каналов, вторую группу 2 триггеров запросов от принимающих каналов, третью группу 3

0 триггеров бит информации, счетчик 4, первый демультиплексор 5, первый 6 и второй 7 мультиплексоры, элемент НЕ 8, первый дешифратор 9 маркера, первый блок 10 регистров (накопления бит информации), рас5 пределитель 11 импульсов, согласующие элементы 12, второй демультиплексор 13, третий мультиплексор 14, четвертый 15 и третий 16 демультиплексоры, блок 17 сравнения, второй дешифратор 18, элемент И 19, элемент ИЛИ 20, триггер 21, суммирующий блок 22, коммутатор 23, второй блок 24 регистров, блок 25 памяти, выходные регистры 26, генератор 27 тактовых импульсов, входы 28 запросов передающих каналов.

входы 29 запросов принимающих каналов, информационные входы 30 (от передающих каналов), входы 31 числа передаваемых байт. Распределитель 11 импульсов выполнен на счетчике 32 и дешифраторе 33.

0 Блок 10 регистров накопления байтов предназначен для накопления бит по каждому из передающих каналов и формирования байтов информации в параллельных кодах, ячейки для хранения информации по

5 каналам адресуются по входам W записи и

R считывания, управление записью бит в

регистр производится сигналом по входу С.

Суммирующий блок 22 с коммутатором

23и блоком 24 регистров предназначены 0 для подсчета числа бит и байтов для каждого

передающего и принимающего канала. Регистры 26 предназначены для хранения считываемой из блока 25 памяти информации каждого канала. Демультиплексор 5 пред5 назначен для установки в нуль триггеров 1 и 2 запросов каналов после обработки их информации. Демультиплексор 13 предназначен для формирования импульса записи бит информации в блок 10 регистров. Де0 мультиплексор 14 предназначен для прибавления в 1 в блок 22 и обнуления блока

24регистров после поступления маркера кодограммы при записи информации или после считывания всей кодограммы для дан5 ного канала. Демультиплексор 15 предназначен для выборки одного из регистров 26, соответствующего запросу данного канала. Демультиплексор 16 предназначен для установки режима запись / чтение в блоке 25

памяти. Блок 17 сравнения предназначен для определения конца кодограммы по заданному входному пороговому числу байт в кодограмме. Блок 25 памяти предназначен для записи, хранения и считывания байт информации в параллельных кодах для всех каналов.

Устройство работает следующим образом.

Каналы, обслуживаемые устройством, делятся на передающие и соответствующие им принимающие и выставляют запросы на обслуживание по входам 28 и 29 устройства. Каналы, передающие информацию для записи ее в память устройства, выставляют запросы по входам 28, а биты информации в последовательных кодах от каждого канала подаются по соответствующим входам 30 устройства. Принимающие каналы выставляют запросы для считывания информации из памяти устройства по входам 29. Каждому передающему каналу соответствует один из триггеров 1 запросов и один из триггеров 3 информации, каждому принимающему каналу-один из триггеров 2 запросов. Каналы передают информацию в последовательных кодах бит за битом в виде кодограмм, длина которых для данного устройства определена заранее и задана в виде конечного числа байт в кодограмме по входу 31 устройства. Начало каждой кодограммы определяется специальным словом-маркером. Каждому каналу соответствует определенный номер-адрес, при этом передающие каналы имеют, например, четные номера, а принимающие - нечетные. Вся совокупность адресов, определяющих каналы, делится на зону адресов передающих каналов и зону адресов принимающих каналов, которые отличаются значением младшего разряда в коде адреса.

Устройство работает в двух режимах: в режиме записи последовательной информации от передающих каналов и в режиме считывания параллельной информации принимающими каналами, причем последовательность этих режимов произвольная и зависит только от последовательности запросов, поступающих от принимающих и передающих каналов. В исходном состоянии все блоки устройства, содержащие элементы памяти, обнулены (цепи начальной установки на схеме не показаны), на выходе элемента НЕ 8 присутствует единичный сигнал, который удерживает в нулевом положе- нии счетчик 32 распределителя 11 и разрешает счет импульсов с счетчика 4 от генератора 27 импульсов. Счетчик 4 с помощью мультиплексоров 6 и 7 циклически и последовательно опрашивает выходы триггеров 1-3. Суммарное время опроса всех триггеров 1-3 с учетом времени обработки запросов каналов (время цикла работы распределителя 11) меньше длительности пе- 5 риода между запросами, выставляемыми каналами по входам 29-30, что исключает возможность потери информации при ее обработке.

Устройство в режиме записи информа0 ции работает следующим образом.

Передающий 1-й канал по входу 28-i устанавливает в единичное состояние триггер 1-1, подает бит информации на D-вход триггера 3-1 и устанавливает его в единичное

5 состояние или нулевое в зависимости от логического значения бита сигналом запроса, поступающим одновременно по входу 28-i. При опросе триггера 1-i на выходе мультиплексора 6 формируется сигнал, который че0 рез элемент Н Е 8 запрещает счет импульсов в счетчике 4 и снимает сигнал сброса с нулевого входа распределителя 11. На выходах счетчика 4 устанавливается адрес i-ro передающего канала. Выход триггера З-i че5 рез мультиплексор 7 подключается к информационному входу блока 10 регистров накопления байтов. После снятия сигнала сброса распределитель 11 включается и формирует один цикл распределенных уп0 равляющих сигналов. Первый импульс распределителя 11 поступает на демультиплексор 13, группа выходов которого, соответствующая зоне адресов передающих каналов, подключена через

5 согласующий элемент 12 (резистор) к шине источника питания. Поэтому для адреса i-ro канала на выходах демультиплексора 13 формируется импульс, который обеспечивает запись первого бита информации i-ro ка0 нала в ячейку блока 10, адресуемую текущим состоянием счетчика 4, Второй импульс распределителя 11 подается на тактовый вход блока 24 регистров, который вместе с блоком 22 и коммутатором 23 обра5 зует многоканальный счетчик числа бит и байтов, записываемых или считываемых каналами.

Подсчет числа бит и байтов, принимаемых от передающего канала, производится

0 следующим образом. До того момента, пока для i-ro канала не принят код маркера кодограммы, на выходе дешифратора 9 установлен единичный сигнал. Поэтому для текущего адреса в счетчике 4 на выходе

5 мультиплексора 14 также устанавливается единичный сигнал, который поступает на первый вход блока 22 и открывает коммутатор 23. Блок 22 прибавляет единицу к числу, накапливаемому для i-ro канала в блоке 24,

которое подается на другие входы этого суммирующего блока 22. Сумма с выходов блока 22 через коммутатор 23 подается на входы блока 24 и фиксируется в ячейке блока 24 регистров, адресуемой по W-входу счетчиком 4, вторым импульсом распределителя 11, действующим на С-вход блока 24. Эта сумма также считывается из ячейки регистр 24, адресуемой счетчиком 4 по R-входу этого регистра, и снова поступает на вторые входы суммирующего блока 22 для увеличения на единицу в следующем цикле распределителя 11 и т. д. Запись новой модифициро- ванной суммы в ячейку блока 24, адресуемую счетчиком 4, производится при поступлении следующих бит информации I- го канала.

Управление мультиплексором 14 осуществляется от счетчика 4 так, что в зоне адре- сов передающих каналов выход мультиплексора 14 подключается к выходу дешифратора 9 маркера, а в зоне адресов принимающих каналов - к выходу блока 17 сравнения, определяющему длину кодограммы.

При приеме информации от 1-го канала после поступления всех бит байтмаркера на выходе дешифратора 9 устанавливается нулевой сигнал. При этом закрываются элементы И коммутатора 23 и в блок 24 регистров по текущему адресу счетчика 4 записываются нули, т. е. устанавливается начало отсчета числа бит в кодограмме 1-го канала. Третий импульс дешифратора 33 распределителя 11 через элемент И 19 опрашивает выход дешифратора 18 байтов, на который подаются три младших разряда числа с выходов блока 24. Если для данного i-ro канала байт информации не накоплен, то три младших разряда не принимают единичное значение и на выходе дешифратора 28 установлен единичный сигнал. В этом случае распределитель 11 выполняет короткий цикл управления. Третий импульс распределителя 11 через элементы И 19, ИЛИ 20 подается на вход демультиплексора 5, который скоммутирован счетчиком 4 к нулевому входу триггера 1-i, и он устанавливает- ся в нулевое положение. При этом снимается сигнал с выхода мультиплексора 6 и элемент НЕ 8 снова устанавливает в нулевое положение счетчик 32 распределителя 11, включает в режим счета счетчик 4 и описанный процесс опроса триггеров 1-3 повторяется. Аналогично обслуживаются последующие запросы i-ro и других каналов. Накопление бит i-ro канала в соответствующей ему ячейке блока 10, адресуемой текущим состоянием счетчика 4, обеспечивается за счет обратной связи с выходов блока 10 на группу его информационных входов,

сдвинутых на один разряд. При этом каждый последующий бит информации сдвигает предыдущее состояние ячейки по ее разрядам до накопления в этой ячейке байта информации 1-го канала.

После накопления байта информации I- го канала в блоке 10 на выходе дешифратора 18 устанавливается нулевой сигнал, который закрывает элемент И 19. В этом случае распределитель 11 выполняет длинный цикл управления. Третий импульс дешифратора 33 распределителя 11 не обнуляет триггер 1-1. Так как. счетчик 4 в текущем состоянии адресует 1-й передающий канал, то на выходах блока 10 установлен байт i-ro канала, который подается на информационные входы блока 25 памяти. Четвертый импульс распределителя 11 устанавливает в единичное состояние триггер 21, который подает сигнал обращения на CS-вход блока 25 памяти и байт информации i-ro канала записывается по указанному адресу в этот блок 25. Пятый импульс распределителя 11 поступает на вход демультиплексора 15, который работает только в режиме считывания информации из блока 25 памяти, так как в нем используется группа выходов, адресуемых зоной принимающих каналов. Шестой импульс распределителя 11 устанавливает в нуль триггер 21, чем обеспечивается формирование импульса обращения к памяти заданной длительности. Седьмой импульс распределителя 11 через элемент ИЛИ 20 устанавливает в нулевое положение триггер 1-i и описанный процесс опроса триггеров 1-3 повторяется.

Устройство в режиме считывания информации работает следующим образом.

Принимающие каналы обращаются кус- тройству независимо от передающих каналов в любой момент времени. Принимающий К-й канал выставляет запрос на считывание информации по входу 29-К и устанавливает в единичное состояние соответствующий триггер 2-К. При опросе триггера 2-К аналогично описанному останавливается счетчик 4, который адресует канал К, и включается распределитель 11, который также организует короткий или длинный цикл управления. Первый импульс распределителя 11 не изменяет состояние выходов демультиплексора 13, так как на его адресных входах действует адрес из зоны адресов принимающих каналов. Мультиплексор 14, адресуемый счетчиком 4 (адресом К-го канала из зоны адресов принимающих каналов), подключается к выходу блока 17 сравнения. Единичный сигнал с выхода блока 17 сравнения подается через мультиплексор 14 на вход суммирующего

блока 22, и второй импульс распределителя 11 увеличивает на единицу содержимое К-й ячейки в блоке 24 регистров, адресуемой текущим адресом счетчика 4. С выходов блока 24 число считанных бит подается на де- шифратор 18, блок 17 сравнения, суммирующий блок 22 и адресные входы блока 25 памяти. Третий импульс распределителя 11 опрашивает выход дешифратора 18 и в случае, если адрес блока 24 регистров 24 (младшие разряды) не соответствуют числу бит в байте, то распределитель 11 выполняет короткий цикл управления: третий импульс через элементы И 19, ИЛИ 20 устанавливает в нуль через демультиплексор 5 триггер 2-К и описанный процесс повторяется до следующего запроса канала К или другого канала.

После считывания числа бит, при котором младшие разряды на выходе блока 24 устанавливаются в единичное состояние, дешифратор 18 закрывает элемент И 19 и выполняется длинный цикл управления. При подаче на адресные входы демультип- лексора 16 адреса из зоны адресов прини- мающих каналов на его выходе формируется управляющий сигнал чтения, который подается на вход W/R блока 25 памяти. Четвертый и шестой импульсы распределителя 11 управляюттриггером21, ко- торый формирует импульс обращения к блоку 25 памяти. Из блока 25 считывается байт информации для К-го канала, адресуемый старшими разрядами счетчика 4 и старшими разрядами блока 24. Считанная информация записывается в выходной регистр 26-К. Выборка регистра 26 производится демультиплексором 15, адресуемым К-ым адресом счетчика 4. Пятый импульс распределителя 11 через демультиплексор 15 записывает считанный байт из блока 25 памяти в регистр 26-К, воздействуя на его тактовый вход. Седьмой импульс распределителя 11 устанавливает в нуль триггер 2-К и описанный процесс повторяется.

По количеству запросов, выданных принимающим каналом, последний определяет номер считанного байта и его положение в кодограмме. После считывания К-ым каналом всех байтов кодограммы на выходе бло- ка 24, адресуемого счетчиком 4 по адресу К-го канала, устанавливается число, совпадающее с пороговым числом, заданным по входам 31. С выхода блока сравнения при этом выдается нулевой сигнал, который ана- логично описанному в очередном цикле обработки запроса К-го канала устанавливает в нулевое положение ячейку блока 24, адресуемую К-ым каналом. После этого К-й канал начинает повторное считывание кодограммы. Многократное считывание кодограммы и совпадение соответствующих байтов в них свидетельствует для данного канала о достоверном считывании информации.

Формула изобретения Многоканальное буферное запоминающее устройство, содержащее блок памяти, выходы которого соединены с информационными входами выходных регистров, первый дешифратор, распределитель импульсов, коммутатор, счетчик, отличающееся тем, что, с целью расширения области применения устройства за счет чередования циклов записи и считывания информации между передающими и принимающими каналами, в него введены первая - третья группы триггеров, с первого по третий мультиплексоры, с первого по четвертый демультиплексоры, второй дешифратор, первый и второй блоки регистров, суммирующий блок, блок сравнения, триггер, элементы И, ИЛИ, НЕ, генератор импульсов, согласующие элементы, причем входы запросов передающих каналов устройства соединены с единичными входами триггеров первой группы и тактовыми входами триггеров третьей группы, входы запросов принимающих каналов устройства соединены с единичными входами триггеров второй группы, информационные входы устройства - с информационными входами триггеров третьей группы, выходы триггеров первых и вторых групп - с информационными входами первого мультиплексора, выход которого соединен с входом элемента НЕ, выход которого соединен с управляющим входом распределителя импульсов и счетчика, тактовые входы которых соединены с выходом генератора импульсов, выходы счетчика - с адресными входами первого - третьего мультиплексоров, первого - четвертого демультиплексоров, первого и второго блоков регистров, с адресными входами первой группы блока памяти, выходы триггеров третьей группы соединены с информационными входами второго мультиплексора, выход которого соединен с первым информационным входом первого блока регистров, выходы которого соединены с вторыми информационными входами первого блока регистров, информационными входами блока памяти и входами первого дешифратора, инверсный выход которого соединен с информационными входами первой группы третьего мультиплексора, информационные входы второй группы которого соединены с инверсным входом блока сравнения, выход третьего мультиплексора - с управляющим входом

коммутатора и первым входом суммирующего блока, выходы которого соединены с информационными входами коммутатора, выходы которого подключены к информационным входам второго блока регистров, выходы которого соединены с вторыми входами суммирующего блока, третьи входы которого подключены к шине питания, входы старших разрядов второго блока регистров соединены с первыми входами блока сравнения, вторые входы которого являются входами числа передаваемых байтов устройства и с адресными входами второй группы блока памяти, выходы младших разрядов второго блока регистров соединены с входами второго дешифратора, инверсный выход которого соединен с первым входом элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с информационным входом первого демультиплексора, выходы которого соединены с нулевыми входами триггеров первой и второй групп, первый

0

5

0

выход распределителя импульсов соединен с информационным входом второго демультиплексора, выходы группы которого соединены с первым согласующим элементом и тактовым входом первого блока регистров, второй выход распределителя импульсов соединен с тактовым входом второго блока регистров, третий выход - с вторым входом элемента И, четвертый и шестой выходы соответственно с единичным и нулевым входами триггера, выход которого соединен с входом обращения блока памяти, вход установки режима которого соединен с вторым согласующим элементом и выходами группы третьего демультиплексора, информационный вход которого соединен с шиной питания, пятый выход распределителя импульсов - с информационным входом четвертого демультиплексора, выходы которого соединены с тактовыми входами соответствующих выходных регистров, седьмой выход распределителя импульсов соединен с вторым входом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1499358A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

Изобретение относится к вычислительной технике и может быть использовано в многоканальных вычислительных комплексах с магистралями последовательного и параллельного интерфейса. Цель изобретения - расширение области применения устройства за счет чередования циклов записи и считывания информации между передающими и принимающими каналами. Триггеры 1 фиксируют запросы передающих каналов, триггеры 2 - запросы приемных

| Буферное запоминающее устройство | 1986 |

|

SU1455363A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1481852A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-03-23—Публикация

1990-05-15—Подача