выполнен на дешифраторе, элементах ИЛИ, элементах задержки, первый, второй , третий и четвертый входы дешифратора являются первым, вторым, третьим и четвертым входами блока анализ а, нуле вой выход дешифратора является первым выходом блока анализа, с первого по четвертый, с шестого по дейятый, одиннадцатый и двенадцатый выходы дешифратора соединены с первого по десятый входами первого элемента ИЛИ, одиннадцатый и двенадцатый входы элемента ИЛИ являются пятым и седьмым входами блока анализа, выход первого элемента ИЛИ объединен с входом первого элемента задержки и является вторым выходом блока анализа выход первого элемента задержки соединен с первым входом второго элемета ИЛИ и является третьим выходом блока анализа, второй вход второго элемента ИЛИ является шестым входом блока анализа, другие входы второго элемента ИЛИ соединены с пятым, десятым, тринадцатым, четырнадцатым и пятнадцатым выходами дешифратора, выход второго элемента ИЛИ соединен с входом второго элемента задержки, выход которого является четвертым выходом блока анализа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сокращения избыточности информации | 1982 |

|

SU1075289A1 |

| Устройство для сокращения избыточности информации | 1980 |

|

SU959129A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1084837A1 |

| УСТРОЙСТВО МОНИТОРИНГА ПАРАМЕТРОВ ЗАДЫМЛЕННОСТИ И ИХ ДОСТОВЕРНОСТИ | 2011 |

|

RU2457541C1 |

| Устройство для считывания графической информации | 1985 |

|

SU1292019A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| Устройство для распознавания на линейность булевых функций | 1990 |

|

SU1756879A1 |

| Устройство для формирования отрезка прямой линии на экране электронно-лучевой трубки | 1979 |

|

SU919163A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Устройство для генерации векторов на индикаторе с черезстрочной разверткой | 1980 |

|

SU922718A1 |

1. УСТРОЙСТВО ДЛЯ СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ, содержащее первый элемент И, первый вход которо го соединен с информационной шиной, регистры, первые входы первого.и второго регистров объединены и соединены с выходом первого элемента И, первый вход третьего регистра соедииен с первым входом первого элемента и, ключ, выход которого соединен с выходной шиной устройства,второй элемент И, выход которого соединен с первым входом ключа, регистр сдвига, выход которого соединен с первым входом ключа, триггер, нулевой выход которого соединен с объединенными вторыми входами первого элемента И и регистра сдвига, два блока вычитания, первне входы которых объединены с вторым входом ключа и соединены с выходом первого регистра, второй вход первого блока-вычитания объединен с вторым входом первого регистра и Joeдинен с выходом второго регистра, а второй вход второго блока вычитания Объединен с вторым входом второго регистра и соединен с выходом третьего регистра, третий элемент И, арифметические блоки, первые управляющие входы которых объединены и соединены с выходом третьего элемента И, вход первого арифметического блока соединен с первым выходом первого блока вычитания, а вход второго арифметического блока соединен с первым выходом второго блока вычитания, блок сравнения , входы которого соединены соответственно с выxoдa lи первого и второго арифметических блоков, блок анализа,первый и второй входы которого соединены с первым и вторым входами первого блока вычитания, третий и четвертый - с первым и вторым входами второго блока вычитания, пятый и шестой - с первым и вторым выходами блока сравнения, седьмой - с входной ШИНОЙ устройства, первый .выхЬд блока анализа соединен с вторым входом третьего, элемента И, второй - с вторым входом второго элемента И, третий и четвертый - с соответствующими третьими входами первого и вто1ел рого регистров, блок синхронизации, входами которого являются две ин.форF - мационные шины, одна яз которых объе динена с R -входом триггера первый выход блока синхронизации соединен с объединенным синхронизирующим S-входом триггера и с входами блоков вычитания, второй выход соединен с первым входом третьего элемента. И, третий выход соединен с входом блока сравнения, отличающееся , тем, что, с целью повышения точности ел и упрощения устройства, в него введены второй и третий блоки сравнения 4ik и четвертый элемент И, входы которого подключены к выходам второго итретьего блоков сравнения, выход соединен с объединенными вторыми управляющими входами первого и второго арифметических блоков, первые входы второго и третьего блоков сравнения соединены с соответствующими первыми выходами первого и второго блоков вычитания, управляющие входы второго и третьего блоков сравнения объединены и соединены с четвертым выходом блока синхронизации. 2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок анализа

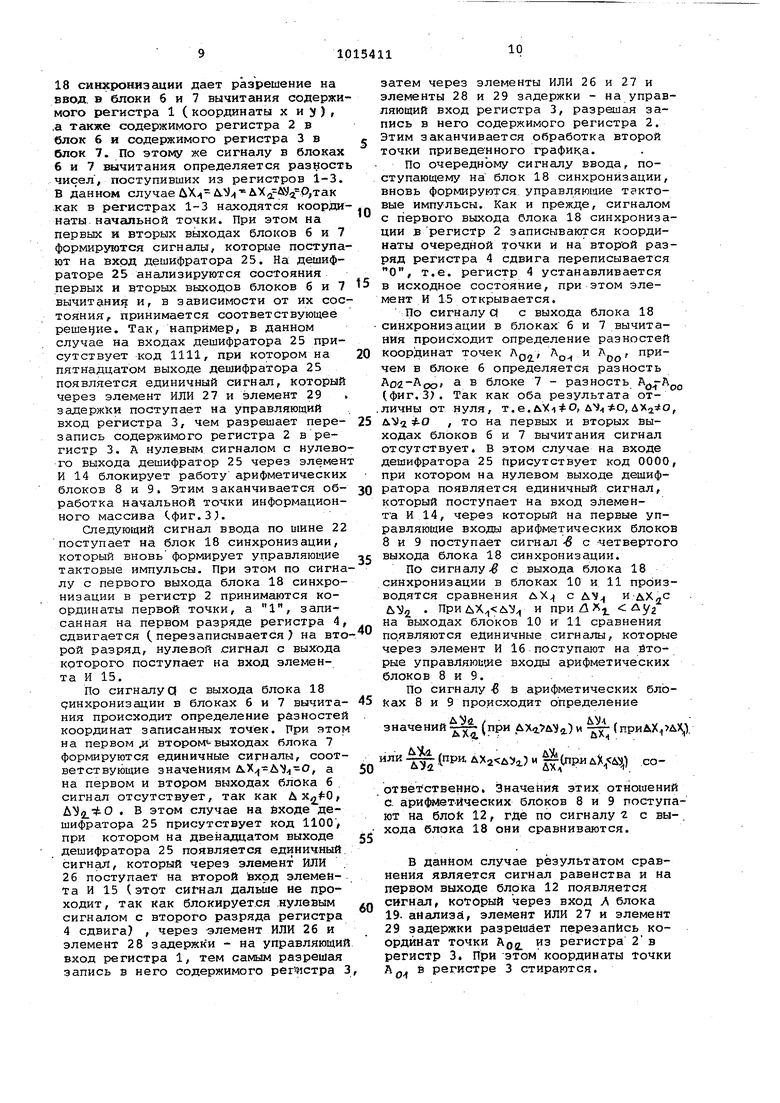

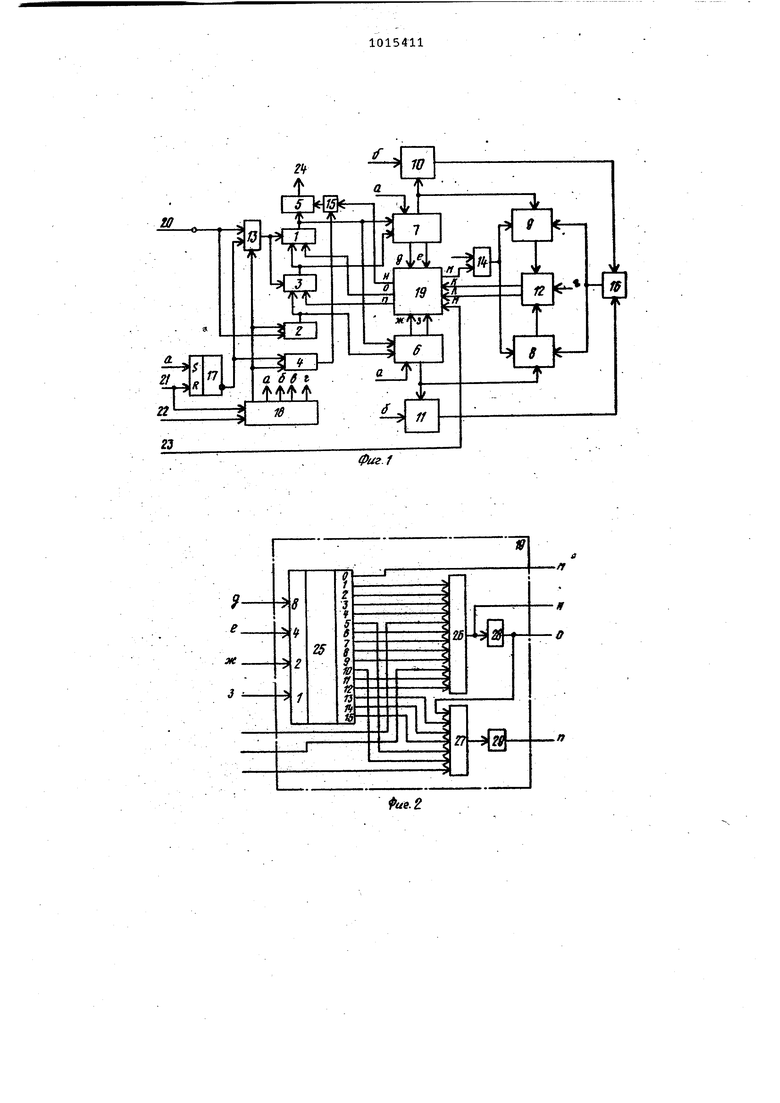

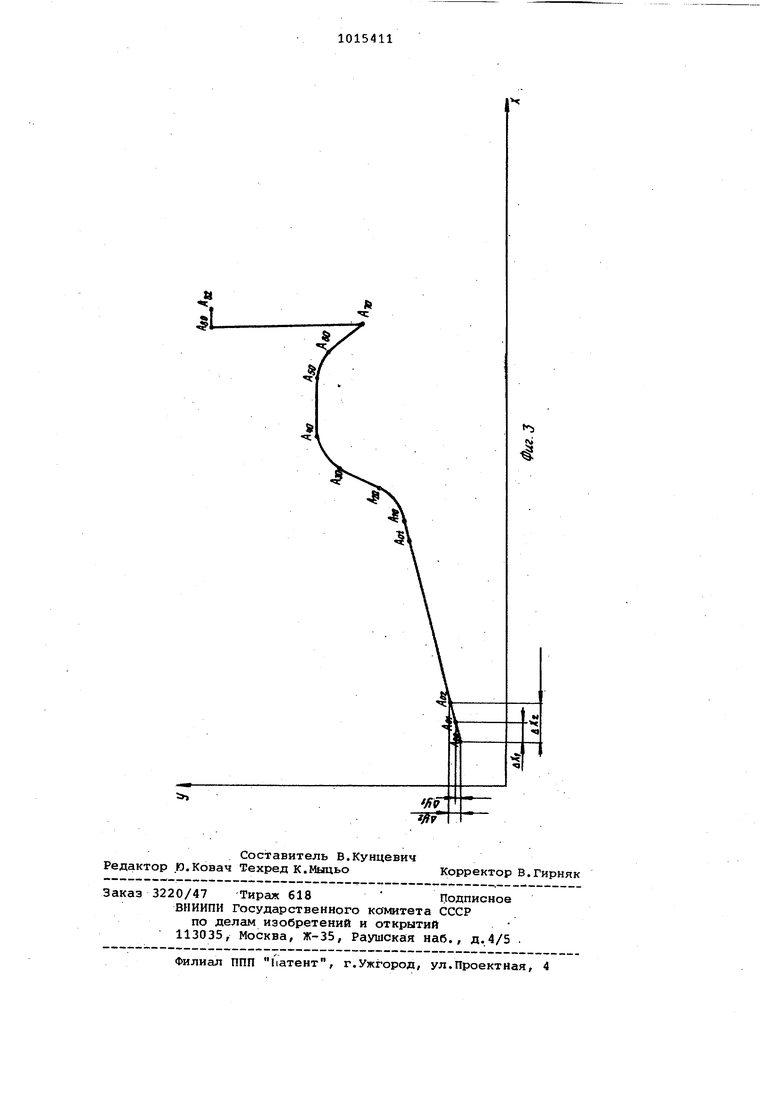

Изобретение относится к приему, передаче и обработке информации и может быть использовано в различных отраслях промышленности, где требуется обрабатывать большие информационные массивы.. Известно устройство для сокрашени избыточности информации, содержащее регистр текущей выборки, выход которого соединен с входом ре1истра памя ти выборок, первым входом блока вычитания и через второй арифметически блок с первым арифметическим блоком, выход регистра памяти соединен с вторым входом блока вычитания и первым входом электронного ключа, выход блока вычитания соединен через дешифратор и первый арифметический бло с вторым арифметическим блоком и выходным арифметическим блоком, выход которого подключен к второму входу электронного ключа, второму арифмети ческрму блоку, и к второму входу счет чика, первый вход которого соединен с входом устройства, а выход подключен к второму входу дешифратора ll. Недостатками данного устройства являются сложность его аппаратурной реализации и низкое быстродействие. Наиболее близким к предлагаемому потехнической сущности является устройство для сокращения избыточнос ти информации,-содержащее первый элемент И, первый вход которого соединен с информационной шиной, регист ры, первые входы первого.и второго регистров,первые входы первого и второго регистров Объединены и соеди нены с выходом первого элемента И, первый вход третьего регистра соединен с первым входом первого элемента И, ключ, выход которого соединен с выходной шиной устройства, второй элемент И, выход которого соединен с первым входом ключа, регистр сдвига. выход которого соединен с первым входом ключа, триггер, нулевой выход которого соединен с объединенными вторыми входами первого элемента И и регистра-сдвига, два блока вычитания, первые объединенные входы которых объединены с вторым входом ключа и соединены с выходом первого регистра, второй вход первого блока вычитания объединен, с вторым входом первого регистра и соединен с выходом второго регистра, а второй вход второго блока вычитания объединен с вторым входом второго регистра и соединен с выходом третьего регистра, третий, элемент И, арифметические блоки, первые управляющие входы которых объединена, и соединены с выходом третьего элемента Н, вход первого арифметического блока соединен с первым выходом первого блока вычитания, а вход второго арифметического блока соединён с первым выходом второго блока вычитания, блок сравнения, входы которого соединены соответственно с выходами первого и второго арифметических блоков, блоканализа, первый и второй входы которого соединены с первым и вторым входами первого блока вычитания , третий и четвертый - с первым и вторим входами второго блока вычитания, пятый и шестой - с первым и вторым выходами блока сравнения,седь-. мой - с входной шиной устройства,первый выход блока анализа соединен с вторым входом TpieTbero элемента И, Второй -г с вторым входом второго элемента И, третий и четвертый - с срответствующими тpeтьи a входами первого и второго регистров, блок синхронизации, входами .которого являются две информационные шины, одна из которых объединена С R -входом триггера, первый выход блока синхронизации соединен с объединенным синхрониэируртгпим ,S-входом триггера и с вхо дами блоков вычитания-, второй выход соединен с первым входом третьего элемента И, третий выход соединен с входом блока сравнения, причем блок анализа содержит ИЛИ, И, ИЛИ-НЕ, элементы задержки 2. Недостатками известного устройств являются сложность аппаратурной реализации и недостаточная точность. Повышение точности обеспечивается меньшими требованиями к длине разряд ной сетки в устройстве, что достигается сравнением либо тангенсов накло на передаваемой функции от О до 45, либо котангенсов от 45 до 90. Это позволяет исключить необходимость оперирования с большими числами. Цель изобретения - повышение точности и упрощение устройства. Указанная цель достигается там, что в устройство для сокращения избы точности информации, содержащее первый элемент И, первый вход которого соединен с информационной шиной, регистры, первые входы первого и второ го регистров объединены и соединены выходом первого элемента И, первый вход третьего регистра соединен с первым входом первого элемента И, ключ, выход которого соединен с выходной шиной устройства, второй элемент И, выход которого соединен с первым входом ключа, регистр сдвига, выход которого соединен с первым вхо дом ключа, триггер, нулевой выход которого соединен с объединенными вторыми входами первого элементаИ и регистра сдвига, два блока вычитания .первые входы которых объединены с .вторым входом ключа и соединены с выходом первого регистра, второй вхо первого -блока вычитания объединен с вторым входом первого регистра и сое динен с выходом второго регистра, а второй вход второго блока вычитания объединен с вторым входом второго регистра и соединен с выходом третье го регистра, третий элемент И, арифметические блоки, первые управляющие входы которых объединены и соединены с выходом третьего элемента И, вход первого арифметического блока соединен с первым выходом первого блока вычитания, а вход второго арифметического, блока соединен с первым выхо дом второго блока вычитания, блок сравнения, входы которого соединены соответственно с выходами первого и второго арифметических блоков, блок анализа, первый и второй входы которого соединены с первым и вторым вхо дами первогогблока вычитания, третий и четвертый - с первым и вторым входами второго блока вычитания, пятый и шестой - с первым и вторым выхода ми блока сравнения, седьмой - с вход ной шиной устройства, первый выход блока анализа соединен с вторым входом третьего элемента И, второй - с вторым входом второго элемента И,третий и четвертый - с соответствующими . третьими входами первого и.второго ре ги ст ро в J бло к си нхро ни з ации, входами которого являются две информационные шины,-одна из которых объединена с R -виодом триггера, первый выход блока синхронизации соединен с объединенным синхронизирующим S -входом триггера и-с входами блоков вычитания, второй выход соедин ен с первым входом третьего элемента И, третий выход соединен с входом блока сравнения, дополнительно введены второй и третий блоки сравнения и четвертый элемент И, входы которого подключены к выходам второго и третьего блоков сравнения, выход соединен с объединенными вторыми управляющими входами первого и второго арифметических блоков, первые входы второго и третьего блоков сравнения соединены с соответствукедими первыми выходами первого и второго блоков вычитания, управляющие входы второго и третьего блоков сравнения объединены и соединены с четвертым выходом блока синхронизации.. Причем блок анализа выполнен на дешифраторе, элементах ИЛИ, элементах задержки, первый, второй, третий и четвертый входы дешифратора являются первым, вторым, третьим и четвертым входами блока анализа, нулевой выход дешифратора является первым выходом блока анализа, с первого по четвер тый, с шестого по девятый, одиннадцатый и двенадцатый выходы дешифратора, соединены с первого по десятый входами первого элемента ИЛИ, одиннадцатый и двенадцатый входы элемента ИЛИ являются пятым и седьмым входами блока анализа, выход первого элемента ИЛИ объединен с входом первого элемента задержки и является вторымвыходом блока анализа, выход первого элемента задержки соединен с первым входом второго элемента ИЛИ и является, третьим выходом блока анализа, второй вход второго элемента ИЛИ является шестым входом блока анализа, другие входы второго элемента ИЛИ соединены с пятым, десятым, тринадцатым,четырнадцатым и пятнадцатым выходами дешифратора, выход второго элемента ИЛИ соединен с входом второго элемента задержки, выход которого является четвертым выходом блока анализа. На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 - схема блока анализа на фиг.З - кривая для пояснения принципа сокращения избыточности. Устройство Сфиг.1) содержит регистры 1-3, регистр 4 сдвига, ключ 5, блоки 6 и 7 вычитания, арифметические блоки 8 и 9, блоки 10-12 сравнения, элементы И 13-16, триггер 17, блок 18синхронизации, блок 19 анализа, входные шины 20-23 и выходную шину 24 Блок 19 анализа (фиг.2 ) состоит из дешифратора 25, элементов ИЛИ 26 и. 27 и элегиентов 28 и 29 задержки. Выходы регистров-1 и 2 соединены первым и вторым входами блока б вычи тания, выходом соединенного с первым арифметическим блоком 8. Первый вход регистра 3 соединен с первым входом регистра 1 и через элемент И 13 с ин формационным входом 20 и входом регистра 2, второй вход регистра 3 сое динен с выходом регистра 2, а выход с вторым входом регистра 1 и с первы входом блока 7 вычитания, к второму входу которого подключен выход перво го регистра 1, одновременно через ключ 5 соединенный с выходной ши- . ной 24.., . Входы д , е f 1С и : блока 19 анали за, соединены с первым и вторым выходами блоков б к 7 вычитания, третьи выходы которых подключены к входам блоков 8 и 11 и блоков 9 и 10 соответственно. Первые управляющие входи арифметических блоков 8 и 9 через элемент И 14 подключены к выходу Лл блока 19 анализа, а выходы - к входам блока.12 сравнения, выходы которого соединены с входами к и л блока 19.анализа. Нулевой выход триггера 17 соединен с вторым входом элемента И 13 и с информационным входом регистра 4 сдвига, выход которого со единен с первым входом элеманта И 15 подключенного к ключу 5. Выходы ц , 0и н блока 19 анализа соединены с управляющими входами регистров 3 и 1и с вторым входом элемента И 15 со ответственно. Вход М блока 19 анализа и R -вход триггера 17 соединены соответственно с входными шинами 23 21. Входы блока 18 синхронизации сое динены с входными шинами 21 и 22.Пер вый выход блока 18 соединен с управляющими входами регистров 4 и 2 и с Третьим входом элемента И 13, второй выход ( выход а ) - с управлякяцими . входами блоков б и 7 вычитания и с 5-входом триггера 17,«третий выход (выход б) с управлякядими входами блоков 10 и 11 сравнения, выходы которых через элемент И 16 подключены вторым управляющим входам арифметических блоков 8 и 9, четвертый выход .(выход ) - с вторым входом элемента И 14, пятый выход (выход г.} - с управляющим входом блока 12 сравнени В блоке 19 анализа первый выход дешифратора 25 подключен к первому . входу элемента И 14, выходы дешифратора 25 с второго по пятый,с седьмого по десятый, двенадцатый и тринадцатый через первый логический эле мент ИЛИ 26 подключены к второму вхо ду элемента И 15 и к входу элемента 28 задержки, выход которого подключен к первому входу второго элемента ИЛИ 27 и к управляющему входу регистра 1, а шестой, одиннадцатый, четырнадцатый; пятнадцатый и шестнадцатый выходы дешифратора 25 через элемент ИЛИ 27 и элемент 29 задержки подключены к управляющему входу регистра 3. Первый, второй, четвертый и восьмой адресные входы дешифратора 25 подключены соответственно к первым и вторым входам 6JioKOB 6 и 7 вычитания, .. Метод обработки информации, заложенный в предлагаемом устройстве,заключается в определении отношения для каждой точки двухмерного информационного массива, сравнении этого отношения с соответствующим отношением для предЕЛДущей точки с заданной точностью, т.е.. для i -и трчки определяется отношение сравнивается с отношением .;;.,|/йУ.,-. , полученным для (.1-)-й точки, где . .i.,--,-Vo, U,-KI-,-XO,X;;. 3 Хо, VQ, Xi-, - координаты начальной f или информативной), Ci-f -и и -f -и точки соответственно. Иными словами в устройстве реализуется с заданной точностью критерий выборки в соответствии с выражением Д. Min ДХГ При этом точность с или погрешность сравнения задается оператором длиной разрядной сетки сравниваемых отношений - M-L. . , Х. Для уменьшения длинй разрядной сетки в устройстве сравнивают при AV S:&Xi,-AV.,-.f - лх,-. при Л .ДХ.;;Д:9 17 Х. AV4-1 Физический смысл указанного вь1ше состоит в том, что гфи сравнении тангенсов от О до 45(л:#/л) и котангенсов от 45 до 90(дх/л) операцию проводят нал числами от 0,00 до 1,00 включительно. Это. позволяет исключить необходимость оперировать с большими числамии повысить точность устройства. Устранение избыточности вводимой двухмерной информации осуществляют в. реальном масштабе времени в процессе анализа текущих координат. При этом выявляют прямолинейные участки кривой. Точки перехода из криволинейного участка в прямолинейный и наоборот считаются характерными (или информативными7 точками данной кривой. В процессе такой обработки координа- ты характерных точек поступают на вы ход устройства для ввода в ЭВМ, а координаты точек, имеющих на прямоли нейных участках вводимой кривой, на выход устройства не поступают ив ЭВМ не вводятся. ,. . , Ддя анализа формы вводимой кривой в устройстве определяют элементарные приращения К9ррдинат ДХ и л каждой последующей точки относительно предыдущейхарактерной точки, .дпя чего-координаты первой точки записывают в регистр. 1, второй - в регистр 3, третий - в ре.гистр 2. При этом на блок 6 вычитания поступают данные с регистров 1 и 2, а на блок 7 вычитания - с регист эов 1.И 3. В блоках б и 7 определяются разности АХ , , и Дх 2; соответственно/ Значение дХ и ДV поступают в арифметический блок 8 и на блок 11 сравнения, а значения дХ/2.и поступают-в аркфмётичёский блок 9 и, на блок 10 срав.ненйя. Причем в зависимости от результатов сравнения в бло ках 10 и 11 на выходе арифметических блоков 8 и,9 получают t . - д-;;. при ,л)27ДV2: , при AN-, -7 , .7ЛХ2 Полученные частные являются танreHca-NM (котангенсами) углов наклона элементарных отрезков прямых или производными вводимой кривой. ., Сравнивая между Собой значения . , ДХ-« лХ/g Ж, Жа д5Т «. ллгг но определить лежат точки на одной прямой или нет. Сравнение производится :В блоке 12. При неравенстве указанных значений дается .разрешение на передачу координат точки в ЭВМ;. Одновременно в регистр 1 перезаписываются координаты первой точки, а в регистр 3 - координаты второй точки. При ра. венстве дается разрешение только на перезаписькоординат второй точки в регистр 3, при этом координаты первой точки стирают с я.-В обоих случаях когординаты последующей точки записыва-. ются в регистр 2.. При обнаружении прямолинейного участка координаты Кс1Ждой последуюи ей точки на этой прямой сопоставляются с координатами начальной точки отрезка, чем достигается высокая точность анализа и исключается смыибочное представление криволинейных, участков с брлыдим радиусом кривизны прямолиней ными.. При обнаружении криволинейного участка координаты каждой последующей точки на этой кривой сопоставляются с координатами каждой предыдущей точки и при выполнении условия нера-. венетва координаты- предыдущей точки передаются в ЭВМ. При этом количество передавае№1Х точек на единицу длины участка кривой зависит от кривизны участка и-величины принятой погрешности,. При обнаружении у.частка прямой, параллельной оси координат , т.е. кoг да ДХ или ЛЯ равны нулю работа . арифметических блоков 8 и 9 аапрещается и в блоке 19 ан&лиза формируется сигнал, аналогичный сигналу равенства блока 12 сравнения, который также разрешает только перезаписькоординат из регистра 2 в регистр 3, при этом координаты .в регистре 3 стирают ся, т.е. устроист во работ ает ан алогично рассмотренному ранее при анализе прямолинейного участка, однако . без использования арифметических блоков 8 и 9 и блока 12 сравнения. Устройство (фиг.1 работает следующим образом. Перед началом ввода по входной шине 21 на R-вход тригге1ра 17 ,и fla один из входов блока 18 синхронизации поступает сигнал установки. Триггер 17 фиксируется в нулевом состояний,причем сигнал с нулевого выхода триггера 17 поступает на элемент. И 13 и на информационный вход регистра 4 сдвига. Поступление координат каждой точки сопровождается сигналом ввода, который по входной ЛИне 22 поступает на второй вход блока 18 синхронизации. При этом на выходах блока 18 . синхронизации поо1ередно формируются управляющие тактовые импульсы, которые обеспечивают синхронную работу устройства. Одновременно с сигналом ввода по входной шине 20 .на входы элемента И 1.3 и регистра 2 из устройства съема данных (не показано) по- сту.пают координаты X и V начальной точки А в цифровом Параллельном йодеСигнал с выхода блока 18 синхронизации разрааает запись координат х и у в регистры 1 и 3 (через элементИ Гф и в регистр 2. Этим же сигналом производится запись в первый разряд регистра 4 сдвига 1. Регистры 1-3 построены таким образом, что при записи новой информации предыдущая стирается Qнапример, на -триггерах. Далее, при поступлении с выхода блока 18 синхронизации, сиг- налай наS -вход триггера 17 последний устанавливается в единичное состояние и блокирует поступление координат X и в регистры 1 и 3 через элемент И 13, а также прекращает поступление единичного сигнала на информационный вход регистра 4 сдвига. Одновременно сигнал с выхода блока

18 синхронизации дает разрешение на ввод, в блоки б и 7 вычитания содержимого регистра 1 ( координаты х и ( ) , .а также содержимого регистра 2 в блок 6 и содержимого регистра 3 в блок 7. По этому же сигналу в блоках 6 и 7 вычитания определяется разность чисел , поступивших из регистров 1-3. В данном случае .,,так как в регистрах 1-3 находятся коордиваты.начальной точки. При этом на первых и вторых выходах блоков 6 и 7 формируются сигналы, которые поступают на вход дешифратора 25. На дешифраторе 25 анализируются состояния первых и вторых выходов блоков б и 7 вычитания и, в зависимости от их состояния, принимается соответствующее решецие. Так, например, в данном случае на входах дешифратора 25 присутствует код 1111, при котором на пятнадцатом выходе дешифратора 25 появляется единичный сигнал, который через элемент ИЛИ 27 и элемент 29 . задержки поступает на управляющий вход регистра 3, чем разрешает перезапись содержимого регистра 2 в регистр 3. А нулевым сигналом с нулевого выхода дешифратор 25 через элемент И 14 блокирует работу арифметических блоков 8 и 9. Этим заканчивается обработка начальной точки информационного массива Сфиг.З).

Следующий сигнал ввода по шине 22 поступает на блок 18 синхронизации, который вновь формирует управляющие тактовые импульсы. При этом по сигналу с первого выхода блока 18 синхронизации в регистр 2 принимаются координаты первой точки, а 1, записанная на первом разряде регистра 4, сдвигается (перезаписывается на втoрой разряд, нулевой .сигнал с выхода которого поступает на вход элемента И 15.

По сигналу а с выхода блока 18 динхронизадии в блоках б и 7 вычитания происходит определение разностей координат записанных точек. При этом на первом втором -выходах блока 7 формируются единичные сигналы, соответствук)щие значениям , а на первом и втором выходах блока б сигнал отсутствует, так как , . В этом случае на йходе дешифратора 25 присутствует код 1100 при котором на двенадцатом выходе дешифратора 25 появляется единичный, сигнал, который через элемент ИЛИ 26 поступает на второй вход элемента И 15 С этот сигнал дальние не проходит, так как блокирует.ся .нулевым сигналом с второго разряда регистра 4 сдвига) , через элемент ИЛИ 26 и элемент 28 задержки - на управляющий вход регистра 1, тем самым разрешая запись в него содержимого рег мстра 3

затем через элементы ИЛИ 26 и 27 и элементы 28 и 29 задержки - на управляющий вход регистра 3, разрешая запись в него содержимого регистра 2. Этим заканчивается обработка второй точки приведенного графика. По очередному сигналу ввода, поступающему на блок 18 синхронизации, вновь формируются управляющие тактовые импульсы. Как и прежде, сигналом с первого выхода блока 18 синхронизации в регистр 2 записываются координаты очередной точки и на второй разряд регистра 4 сдвига переписывается О, т.е. регистр 4 устанавливается в исходное состояние, при этом элемент И 15 открывается.

По сигналу с| с выхода блока 18 синхронизации в блоках 6 и 7 вычитания происходит определение разностей координат точек Лд, Л и л, причем в блоке б определяется разность э в блоке 7 - разность Ajj-Ap (фиг.З). Так как оба результата отличны от нуля, т.е.лУчФО , , u.V 4-0 , то на первых и вторых выходах блоков б и 7 вычитания сигнал отсутствует, в этом случае на входе ешифратора 25 Присутствует код 0000, при котором на нулевом выходе дешифратора появляется единичный сигнал, который поступает на вход элемента И 14, через который на первые управляющие входы арифметических блоков 8 и 9 поступает сигнал -5 с четвертого выхода блока 18 синхронизации.

По сигналу с выхода блока 18 синхронизации в блоках 10 и 11 производятся сравнения дх с AV H/AXjC ПрилХ ЛУ и приЛХ лу2 на выходах блоков 10 и 11 сравнения появляются единичные сигналы, которые через элемент И 16 поступают на йторые управляюиле входы арифметических блоков 8 и 9. .

По сигналу -6 S арифметических блоках В и 9 происходит определение

3 н аче НИИ - { при а) и (приЛХ лХ,у

)и||и1ридХ,/а)) соответственно. Значения этих отношений с. .йческих блоков 8 и 9 поступают на блок 12, где по сигналу г с вы-, хода блока 18 они сравниваются.

В данном случае результатом сравнения является сигнал равенства и на первом выходе блока 12 появляется сигнал, который через вход А блока 19. анализа, элемент ИЛИ 27 и элемент 29 задержки разрешйет перезапись коордйиат точки АО; из регистра 2 в регистр 3. При этом координаты точки Ад. в регистре 3 стираются.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сокращения избыточности информации | 1975 |

|

SU523438A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 2966739/18-24, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1983-04-30—Публикация

1980-12-11—Подача