блоков симметричных и несимметричных преобладаний подключены к четвертому и пятому входам анализатора величины преобладаний, первый выход которого через блок управления зоной селекции подключен к третьему входу блока селекции, а второй выход анализатора величины преобладаний подключен к второму входу элемента ИЛИ, выход f OToporo подключен второму входу блока управления зоной селекции, а четвертый вход блока коммутации объединен с вторым входом блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации регенератора | 1985 |

|

SU1283992A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU919130A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU938420A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU882012A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU803112A1 |

| Устройство фазирования регенераторов цифрового сигнала для радиоканалов | 1979 |

|

SU873434A2 |

| Устройство тактовой синхронизации | 1991 |

|

SU1807578A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1985 |

|

SU1840278A1 |

| УСТРОЙСТВО ПОИСКА СИСТЕМЫ СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1980 |

|

SU1840267A1 |

УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ РЕГЕНЕРАТОРА, содержащее последовательно оединенные опорный генератор, блок компенсации расхождения частот, блок фазовой автоподстройки частоты (ФАПЧ) с дискретным управлением, анализатор зашумленного сигнала, блок памяти, ключ, интегратор и формирователь сигнала потери синхронизма, а также блок коммутации, блок селекции, блок выделения Фронтов и асинхронный интегральный приемник, которого подключен к . второму входу ключа и первому входу блока коммутации, к второму входу которого подключен первый выход блока ФАПЧ с дискретным управлением, второй выход которого подключен к второму входу блока компенсации расхождения частот, а выход блока коммутации через блок селекции подключен к второму входу блока ФАПЧ с дискретным управлением,при этом выход опорного генератора через блок вьщелення фронтов подключен к вторым объединенным входам анализатора зашумленного сигнала н блока памяти и иепосредствечно к первому входу асинхронного интегрального приемника, второй вход которого объединен с входом блока выделения Фронтов и является входом устройства, отличающее с я тем/ что, с целью повьаиения точности синхронизации путем раздельного управления зоной и скоростью фази ования при постоянных и переменных преобладаниях, в него введены блок управления скоростью фазирования, блок управления зоной селекции, элемент ИЛИ, блок вьщеления сигнсша расфазировки, анализатор величины преобладаний, блок обнаружения симметричных пре обладаний, блок обнаружения несимметричных преобладаний и формирователь зон анализа, к входу которого подключен третий выход блока ФАПЧ с дискретным управлением, четвертый | выход которого подключен к второму W входу блока селекции и первому входу анализатора величины преобладаний, с к второму входу которого, объединен) ному с первыми входа1ми блока вщделе ния сигнала расфазировки и блоков обнаружения симметричных и несимметричных преобладаний подключён выхсд ключа, к третьему входу которого, объединенному с вторым входом интегратора и третьими входами блока комел сл мутации, и блока ФАПЧ с дискретным управлением, подключен вьаюд блока , управления скоростью фазирования, О к первому входукоторого, а также к третьему входу анализатора величию ны преобладаний подйлючен выход интегратора, а к второму входу блока управления скоростью фазирования и первому входу элемента ИЛИ подключен выход формирователя сигнала пог тери синхронизма, к второму входу которого подключен выход блока выделения сигнала расфазировки, при этом выход формирователя зон анализа подключен к вторьш входам блока вьаделения сигнала расфазировки, блока обнаружения симметричных преобладаний и блока обнаружения несимметричньк преобладаний, причем выходы

1

Изобретение относится к радиотехнике и предназначено для использования в аппаратуре телеграфной связи и передачи данных, в частности -в регенераторах.

Известно устройство тактовой синхронизации, содержащее блок фазовой автоподстройки частоты (ФАПЧ) с дискретным управлением, блок селекции, формирователь сигнала потери синхронизма, формирователь сигнала синхронизма, блок управления l

Известно устройство тактовой синхронизации регенератора, содержащее последовательно соединенные опорный генератор, блок компенсации расхож дения частот,блок фазовой автоподстройки частоты (ФАПЧ) с дискретным управлением, -анализатор згииумлениого сигнала, блок памяти, ключ, интегратор и формирователь сигнала потери синхронизма, а также блок коммутаций блок селекции, блок выделения фронтов и асинхронный интегральный приемник , выход которого подключен к второму входу ключа и первому входу блока коммутации, к второму входу которого подключен первый выход блока ФАПЧ с дискретным управлением, второй выход которого подключен к второму входу блока компенсации расхождения частот, а выход блока коммутации через блок селекции подключен к второму входу блока ФАПЧ с. дискретным управлением, при этом выход опорного генератора через блок выделения фронтов подключен к вторым объединенным входам анализатора зашумленного сигнала и блока памяти и непосредственно к первому входу асинхронного интегрального приемника, второй вход которого объединен С вторым входом блока выделения фронтов, а также блок выделения одного фронта за такт, решающий блок и формирователь временных зон 23.

Однако известные устройства обладают низкой точностью синхронизации.

Цель изобретения - повышение точности синхронизации путем раздельного управления зоной и скоростью фазирования при постоянных и перемен ных преобладаниях.

Поставленная цель достигается тем, что устройство тактовой синхронизации регенератора, содержащее последовательно соединенные опорный генератор, блок компенсации расхождения частот, блок фазовой автоподстройки частоты (ФАПЧ) с дискретным управлением, анализатор зашумленного сигнала, блок памяти, ключ, интегратор и формирователь сигнала потери синхронизма, а также блок коммутации блок селекции, блок выделения фронтов и асинхронный интегральный приемник, выход которого подключен к второму входу ключа и пepвo .y входу блока коммутации, к второму входу которого подключен первый выход блока ФАПЧ с дискретным управлением, второй выход которого подключен к второму входу блока компенсации расхождения частот, а выход блока коммутации через блок селекции подключен к второму входу блока ФАПЧ с дискретным управлением, при этом выход опорного генер1атора через блок выделения фронтов подключен к вторым объединенным входам анализаторов зашумленного сигнала и блока памяти и непосредственно - к первому входу асинхронного интегрального приемника, второй вход которого объединен с Ёторым входом блока выделений фронтов и является входом устройства, введены блок управления скорость фазирования, блок управления зоной селекции, элемент ИЛИ, блок вьвделения сигнала расфазировки, анализатор величины преобладаний, блок обнаружения симметричных преобладаний, блок обнаружения несимметричных преобладаний и формирователь зон анализа, к входу которого подключен третий выход блока ФАПЧ с дискретным управлением, четвертый выход которого подключен к второму входу блока селекции и первому входу анализатора величины преоблсоданий, к второму входу которого, объединенному с первыми входами блока выделения сигнала расфазировки и блоков обнаружения симметричных и несимметричных преобладаний подключен выход ключа, к третьему входу которого,объединенном

с вторым входом интегратора и третьими входами блока коммутации и блока Фдач с дискретным управлением подключен выход блока.управления скоростью фазирования, к первому входу которого,:а также к третьему входу анализатора величины преобладаний подключен выход интегратора, а к второму входу блока управления скоростью фазирования и первому входу элемента ИЛИ подключен выход формирователя .сигнала потери синхронизма, к второму входу которого подключен выход блока выделения сигнала расфазировки, при этом выход формирователя зон анализа подключен к вторым входам блока выделения сигнала расфазировки, блока обнаружения симметричных преобладаний и блока обнаружения несимметричных Преобладаний, причем выходы блоков симметричных .и несимметричных преобладаний подключены к четвертому и пятому входам анализатора величины преобладаний, первый выход которого через блок управления зоной селекции подключен к третьему входу блока селекции, а второй выхОд анализатора величины преоблгщаний подключен к второму входу элемента ИЛИ, выход которого подключен к второму входу блока управления зоной селекции, а четвертый вход блока коммутации объединен с вторым в-ходом блока памяти.

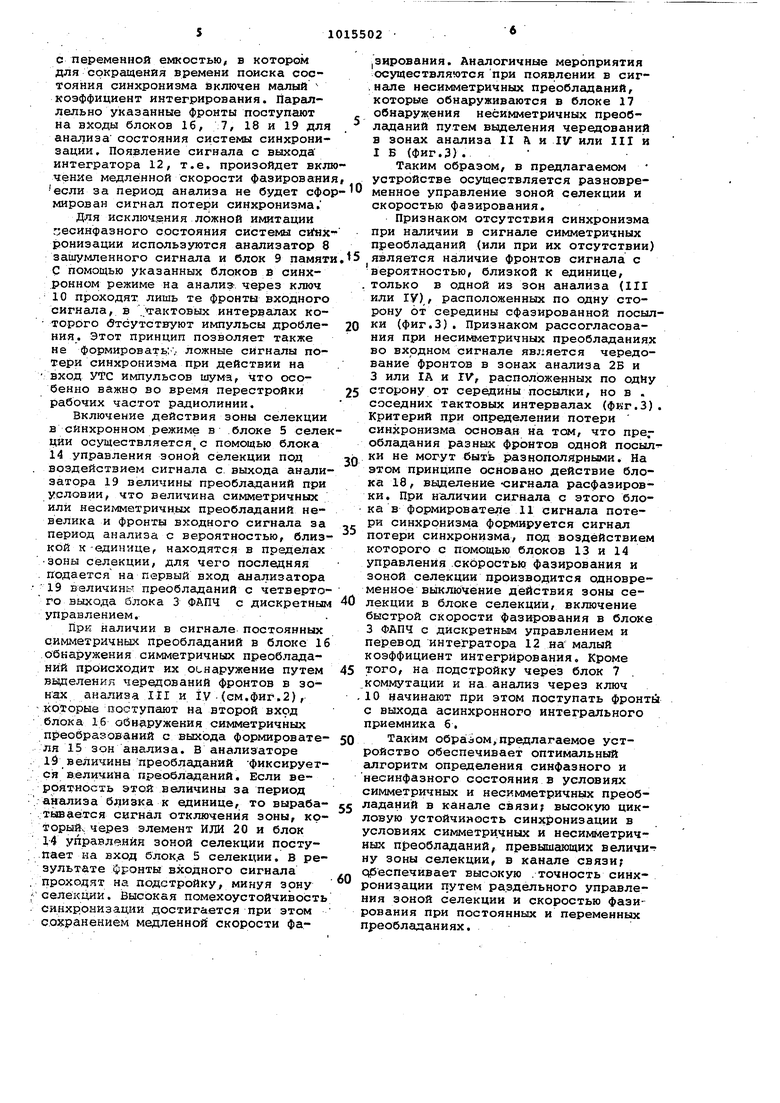

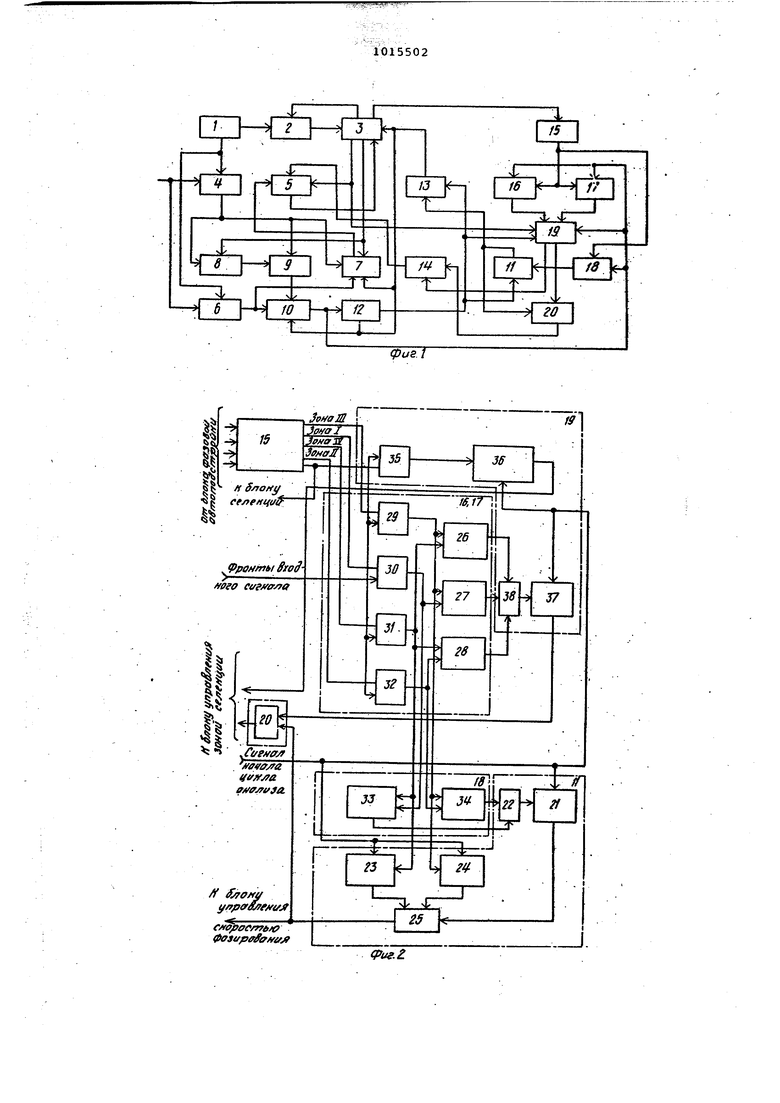

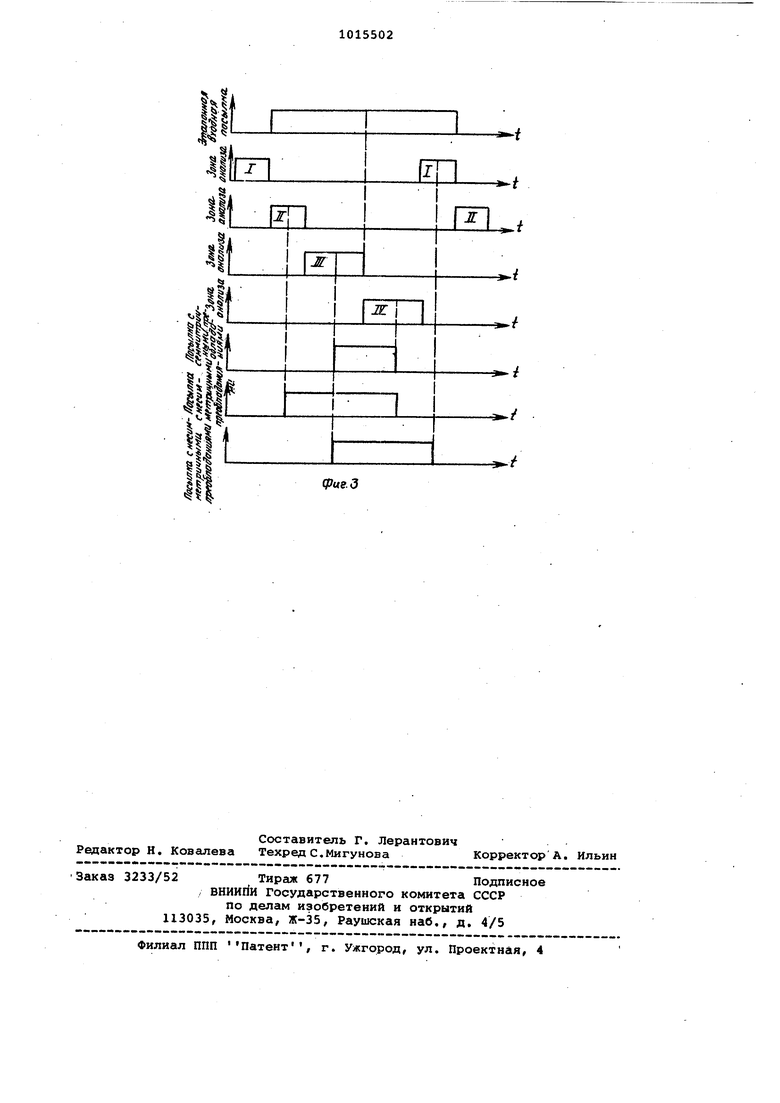

На фигЛ изображена структурная электрическая схема предлагаемого устройства; на фиг.2 - реализация анализатора величины преобладаний, блоков обнаружения си1 1метричных и несимметричных преобладаний, формирователя сигнала потери синхронизма и блока вьщеления сигнала расфазиров ки; на фиг.З - временные диаграммы, поясняющие работу устройства.

Устройство содержит опорный генератор 1, блок 2 компенсации расхождения частот, блок 3 фазовой автоподст ройки частоты (ФАПЧ) с дискретным управлением, блок 4 вьщеления фронтов, блок 5 селекции, асинхронный .интегральный.приемник 6, блок 7 коммутации, анализатор 8 зашумленного сигнала, блок 9 памяти, ключ 10,формирователь 11 сигнала потери синхронизма, интегратор 12, блок 13 управления скоростью фазирования, блок 14 управления зоной селекции, формирователь 15 зон анализа, блок 16 обнат ружения симметричных преобладаний, блок 17 обнаружения несимметричных преобладаний, блок 18 вьаделения сигнала расфазировки, анализатор 19 величины преобладаний,элемент ИЛИ 20, кроме того, формирователь 11 сигнала потери синхронизма содержит интегратор 21 чередований, первый элемент ИЛИ 22, интеграторы 23 и 24, второй элемент ИЛИ 25, блоки 16 и 17 обнаружения симметричных и неспгпметричных преоблсщаний содержат выделители 26 - 28 чередований, элементы И 29 - 32, блок 18 выделения сигнала расфазировки содержит два вьаделителя 33 и 34 чередований, анализатор 19 величины преобладаний содержит элемент И 35, интегратор 36 фронтов в зоне селекции, интегратор 37 чередований, элемент ИЛИ 38

Устройство тактовой синхронизации работает следующим образом.

В блоке 4 выделения фронтов осуществляется дискретизация временного положения фронтов входного сигнаша, для чего на один из его входов подается сигнал с выхода опорного генератора 1. Выделенные фронты в синхронном режиме через блок 7 коммутации поступают на вход блока 5 селекции. В указанном, режиме блок 5 селекции осуществляет селекцию фронтов входного сигнала по величине краевых искажений, т.е. «а подстройку поступают лишь фронты, попавшие в зону селекции, которая подается на вход блока 5 селекции с выхода блока 3 фазовой автоподстройки частоты (ФАПЧ) с дискретным управлением.

В синхронном режиме в блоке 3 ФАПЧ с дискретным управлением с помощью блока 13 управления, скоростью фазирования под воздействием сигнала с выхода интегратора 12 с пере- . менной емкостью включается большой козффициент интегрирования импульсов подстройки и осуществляется медленное фазирование.

В режиме поиска синфазного состояния фронты сигнала поступают на по; стройку и анализ состояния системы синхронизации с выхода асинхронного интегрального приемника 6,скоторый выполняет функцию преобразования дроблений сигнала в краевые-искажения. На выходе асинхронного интегрального приемника 6 осуществляется дискретизация временного положения фронтов преобразованного сигнала, для.чего на первый его вход подается сигнал с выхода опорного генератора 1. Выделенные фронты через блок 7 коммутации поступают на подстройку, Для исключения ложной синхронизации при использовании- cи Ф1eтpичнoгo фазового дискриминатора в блоке 3 ФАПЧ с дискретным управлением в блоке 7 коммутации осуществляется, вьщеление одного фронта эа такт, т.е. переход к однополярной синхронизации. . С этой целью на один из входов блока 7 коммутации поступает тактовый сигнал с первого выхода блока 3 ФАПЧ с дискретным управлением.

В режиме поиска сийхронизма фронты с выхода асинхронного и-нтегрального приемника б через ключ 10 поступают на первый вход интегратора 12

с переменной емкостью, в котором для сокращения времени поиска состояния синхронизма включен малый коэффициент интегрирования. Параллельно указанные фронты поступают на входы блоков 16, 7, 18 и 19 для анализа состояния системы синхронизации , Появление сигнала с выхода интегратора 12, т.е. произойдет вклю чение медленной скорости фазирования

110 если за период анализа не будет сфер мирован сигнал потери синхронизма.

Для исключйния ложной имитации г;есинфазного состояния системы синхронизации используются анализатор 8 зашумленного сигнала и блок 9 памяти С помощью указанных блоков в синхронном режиме на анализ-, через ключ 10 проходят лишь те Фронты входного сигнала, в .чгактовых интервалах которого Отсутствуют импульсы дробления. Этот принцип позволяет также не формировать;,, ложные сигналы потери синхронизма при действии на

вход УТС импульсов шума, что особенно важно во время перестройки рабочих частот радиолинии.

Включение действия зоны селекции в синхронном режиме в .блоке 5 селек ции осуществляется, с помощью блока

14управления зоной селекции под воздействием сигнала с. выхода анализатора 19 величины преобладаний при условии, что величина симметричных или несимметричных преобладаний невелика и фронты входного сигнала за период анализа с вероятностью, близкой к-единице, находятся в пределах

зоны селекции, для чего последняя подается на первый вход анализатора 19 величины преобладаний с четверто40го выхода блока 3 ФАПЧ с дискретным управлением.

lipK наличии в сигнале постоянных симметричных преобладаний в блоке 16 обнаружения симметричных преобладаний происходит их обнаружение путем выделения чередований фронтов в зонах анализа III и iV - (см.фиг.2), оторые поступают на второй вход блока 16 обнаружения симметричных ПЕ еобразований с выхода формироватея 15 зон анализа. В анализаторе

15величины преобладаний фиксируетя В:еличииа преобладаний. Если веоятность этой величины за период :налиэа близка к единице, то выраба55ывается сигнал отключения зоны, крорыйччерез элемент ИЛИ 20 и блок

14 управления зоной селекции прстуает на вход блок.а 5 селекции, В результате фронты входного сигнала

60 роходят на подстройку, минуя зрну елекх ии. Высокая помехоустойчивость инхронизации достигается при этом охранением медленной скорости Фа|3ирования. Аналогичные мероприятия осуществляются при появлении в сиг. нале несимметричных преобладаний, которые обнаруживаются в блоке 17 обнаружения несимметричных преобладаний путем выделения чередований в зонах анализа II V и IV или III и I Б (фиг.З). Таким образом, в предлагаемом устройстве осуществляется разновременное управление зоной селекции и скоростью фазирования.

Признаком отсутствия синхронизма при наличии в сигнале симметричных преобладаний (или при их отсутствии) является наличие фронтов сигнала с вероятностью, близкой к единице, , только в одной из зон анализа (III или ГУ), расположенных по одну сторону от середины сфазированной посылки (фиг.З). Признаком рассогласования при несимметричных преобладаниях во входном сигнале является чередование фронтов в зонах анализа 2В и 3 или IA и IVf расположенных по одИу сторону от середины посылки, но в . соседних тактовых интервалах (фкг.З) Критерий при определении потери синхронизма основан на том, что прег обладания разнызс фронтов одной посылки не могут быть разнополйрными. На этом принципе основано действие блока 18, вьщеление -сигнала расфазировки. При наличии сигнала с этого блока в формирователе 11 сигнала потери синхронизгла формируется сигнал потери синхронизма, под воздействием которого с помощью блоков 13 и 14 управления .скбростью фазирования и зоной селекции производится одновременное выключение действия зоны селекции в блоке селекции, включение быстрой скорости фазирования в блоке 3 ФАПЧ с дискретным управлением и перевод интегратора 12 на малый коэффициент интегрирования. Кроме того, на подстройку через блок 7 ,коммутации и на анализ через ключ 10 начинают при этом поступать фронт с выхода асинхронного интегрального приемника б.

Таким образом,предлагаемое устройство обеспечивает оптимальный ёшгоритм определения синфазного и несинфазного состояния в условиях cиlvIмeтpичныx и несимметричных преобладаний в канале связи; высокую цикловую устойчивость синхронизации в условиях симметричных и несимметричныз{ преобладаний, превышающих величи ну зоны селекции, в канале связи; Обеспечивает высокую .точность синхронизации путем раздельного управления зоной селекции и скоростью фазирования при постоянных и переменных преобладаниях.

и

сриг.2.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1976 |

|

SU640440A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-04-30—Публикация

1981-11-30—Подача