Изобретение относится к технике передачи дискретньк сообщений и может быть использовано для обеспечения тактовой синхронизации приемной части аппаратуры систем передачи информации.

Известно устройство тактовой синхронизации, содержащее последовательно соединенные преобразователь сигналов и формирователь фрон-. тов сигнала и последовательно соединенные генератор импульсов, блок управления, к другим входам которого подключены выходы блока усреднения, и делитель частоты, выход которого подключен к одному из входов фазового дискриминатора, а выходы разрядов делителя частоты - через дешифратор к одному из входов блока защиты,причем вход и выход преобразователя сигналов являются соответственно входом и выходом устройства 111 .

Однако такое устройство не обеспечивает достаточного быстродействия и точности синхронизации из-за искажений типа преобладаний принимаемых элементов сообщения.

Цель изобретения - повышение точности тактовой синхронизации.

Поставленная цель достигается тем, что устройство тактовой синхронизации, содержащее последовательно соединенные преобразователь сигналгов и формирователь фронтов сигнала и последовательно соединенные генератор импульсов, блок управления, к другим входам которого подключены выходы блока усреднения, и делитель

10 частоты, выход которого годключен к одному из входов фазового дискриминатора, а выходы разрядов делителя частоты - через дешифратор к одному из входов блока защиты, причем вход

15 и выход преобразователя сигналов являются соответственно входом и выходом устройства, введены два анализатора преобладаний, элемент ИЛИ, блок задержки и реверсивный счетчик,

20 при этом выход формирователя фронтов сигнала через блок защиты подключен к другому входу фазового.дискриминатора, выходы которого подключены к первому и второму входам блока усред25нения, дополнительные выходы формирователя фронтов сигнала подключены соответственно к первым и вторым объединенным входам первого и вторюго анализаторов преобладаний, к третьим

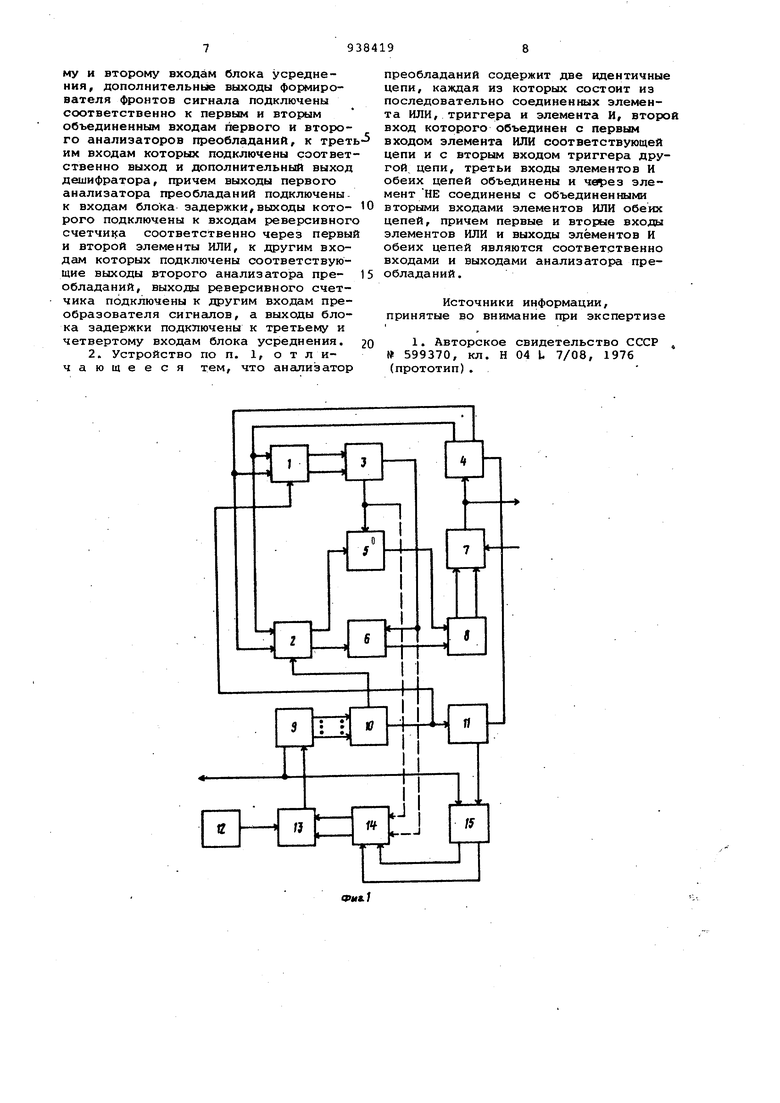

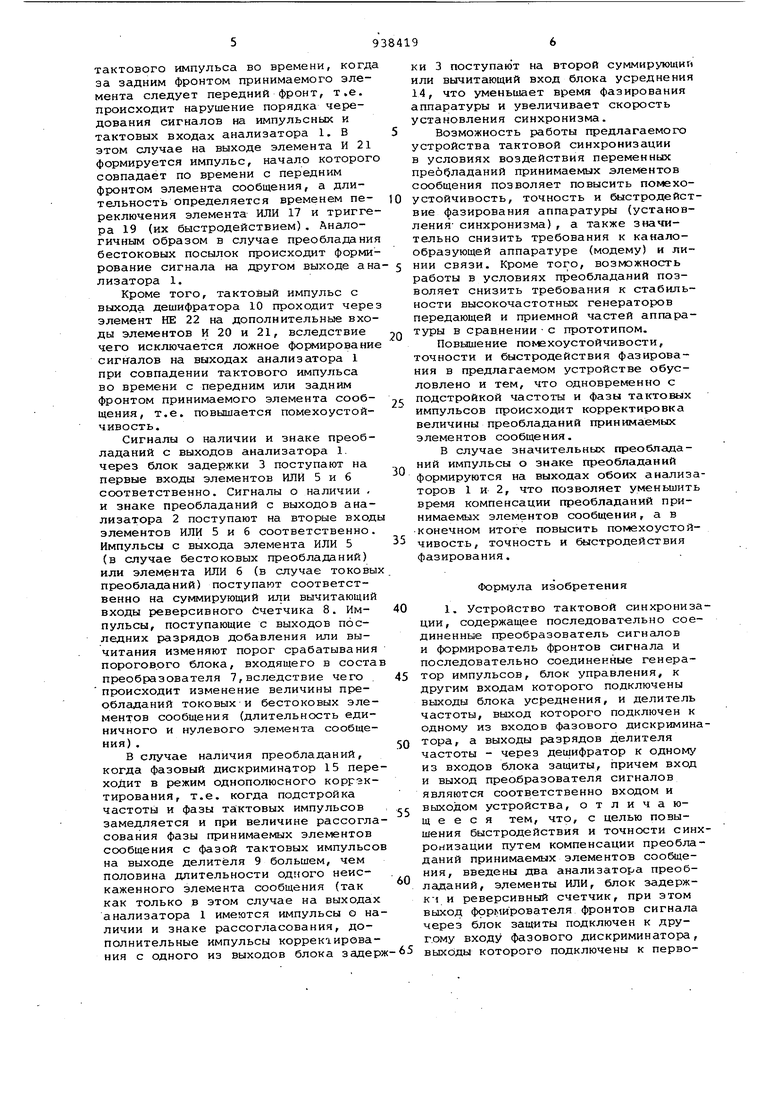

30 входам которых подключены соответст.веино выход и дополнительный выход дешифратора, причем выходы первого анализатора преобладаний подключены к входам блока задержки, выходы кото рого подключены к входам реверсивног счетчика соответственно через первый и второй элементы ИЛИ, к другим входам которых подключены соответствующие выходы второго анализатора преобладаний, выходы реверсивного счетчика подключены к другим входам преобразователя сигналов, а выходы блока задержки подключены к третьем и четвертому входам блока усреднения Причем анализатор преобладаний содержит две идентичные цепи, кажда из которых состоит из последовательно соединенных элемента ИЛИ, триггера и элемента И, второй вход которого объединен с- первым входом элемента ИЛИ соответствующей цепи и с :вторым входом триггера другой цепи, третьи входы элементов И обоих цепей объединены и через элемент НЕсоединены с объединенными,вторыми входа ми элементов ИЛИ обеих цепей, причем первые и вторые входы элементов ИЛИ и выходы элементов И обеих цепей являются соответственно входами и выхо дами анализатора преобладаний. На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг.2 - структурная электриуоская схема анализатора преобладаний. Устройство тактовой синхронизаци содержит анализаторы 1 и 2- преоблаДании, блок задержки 3, формировате 4 -фронтов сигнала, элементы ИЛИ 5 и 6, преобразователь 7 сигналов, реверсивный счетчик 8, делитель 9 частоты, дешифратор 10, блок 11 защиты, генератор 12 импульсов, блок 13 управления, блок 14 усреднения, фазовый дискриминатор 15, а в соста анализатора преобладаний входят элементы ИЛИ 16 и 17, триггеры 18 и 19, элементы И 20 и 21 и элемент НЕ 22. Устройство тактовой синхронизации работает следующим образом. Генератор 12 формирует импульсы высокой частоты, вследствие чего на потенциальном выходе делителя 9 формируется.импульсная последовательность (меандр) с частотой,близкой к скорости телеграфирования принимаемых элементов сообщения. При этом на выходах дешифратора 10 формируются две тактовые последовательности, следующие с той же частотой и сдвинутые один относительно другого на полупериод их следования. Одновременно с этим на выходе преобразователя 7 формируется последовательность принимаемых из канала связи элементов сообщения а передний и задний фронты принзгмае мых элементов поступают на информационный вход блока 11 защиты, на выходе которого формируются либо оба фронта принимаемого элемента (в случае отсутствия преобладаний), либо один из фронтов принимаемого элемента сообщения, фазовый дискриминатор 15 осуществляет сравнение фаз принимаемых элементов сообщения с фазой тактового меандра и в случае их несовпадения формируются корректирующие импульсы добавления или вычитания (режим однополюсного или- двухполюсного корректирования фазы), которые поступают на суммирующий или вычитающий вход блока 14 усреднения, осуществляющего дополнительную защиту устройства . тактовой синхронизации от ложной подстройки частоты при случайных искажениях в канале связи принимаемых элементов сообщения. Усредненные корректирующие -импульсы поступают на суммирующий или исключающий входы блока 13 управления, вследствие чего производится подстройка фазы и частоты следования тактовых импульсов на выходах делителя 9 и дешифратора 10. Кроме того передние и задние фронты и выходов формирователя 4 поступают на входы анализаторов 1 и 2, которые производят определение наличия и знака преобладаний в принимаемых элементах сообщения. Установка триггера 18 в единичное состояние производится передним фронтом принимаемого элемента, а его сброс (перевод в нулевое состояние) производится посредством элемента ИЛИ 16 задним фронтом принимаемого элемента или тактовым импульсом, поступающим с выхода дешифратора 10. Установка триггера 19 в единичное состояние производится задним фронтом принимаемого элемента, а его,сброс осуществляется посредством элемента ИЛИ 17 передним фронтом принимаемого элемента или тактовым импульсом. Вследствие этого при расположении во времени тактового импульса между передним и задним фронтами или между задним и передним фронтами принимаемого элемента, что может иметь место только при отсутствии преобладаний, элементы И 20 и 21 соответственно оказываются закрытыми для прохождения сигналов с выходов формирователя 4 по вторым входам нулевыми уровнями напряжения с выходов триггеров 18 и 19 соответственно. Поэтому сигналы на выходах анализатора 1 не формируются. В случае преобладания токовых посылок (длительность единичного элемента принимаемого сообщения больше длительности нулевого элемента) возможно такое расположение тактового импульса во времени, когд за задним фронтом принимаемого элемента следует передний фронт, т.е. происходит нарушение порядка чередования сигналов на импульсных и тактовых входах анализатора 1. В этом случае на выходе элемента И 21 формируется импульс, начало которог совпадает по времени с передним фронтом элемента сообщения, а длительность определяется временем переключения элемента ИЛИ 17 и тригге ра 19 (их быстродействием), Аналогичным образом в случае преобладани бестоковых посылок происходит форми рование сигнала на другом выходе а н лизатора 1. Кроме того, тактовый импульс с выхода дешифратора 10 проходит чере элемент НЕ 22 на дополнительные вхо ды элементов И 20 и 21, вследствие чего исключается ложное формировани сигналов на выходах анализатора 1 при совпадении тактового импульса во времени с передним или задним фронтом принимаемого элемента сообщения, т.е. повышается помехоустойчивость. Сигналы о наличии и знаке преобладаний с выходов анализатора 1. через блок задержки 3 поступают на первые входы элементов ИЛИ 5 и 6 соответственно. Сигналы о наличии . и знаке преобладаний с выходов анализатора 2 поступают на вторые вход элементов ИЛИ 5 и б соответственно. Импульсы с выхода элемента ИЛИ 5 (в случае бестоковых преобладаний) или элемента ИЛИ б (в случае токовы преобладаний) поступают соответственно на суммирующий или вычитающий входы реверсивного Счетчика 8. Импульсы, поступающие с выходов последних разрядов добавления или вычитания изменяют порог срабатывания порогового блока, входящего в соста преобразователя 7,вследствие чего происходит изменение величины преобладаний токовых и бестоковых элементов сообщения (длительность единичного и нулевого элемента сообщения) . В случае наличия преобладаний, когда фазовый дискриминатор 15 пере хоДит в режим однополюсного коррзктирования, т.е. когда подстройка частоты и фазы тактовых импульсов замедляется и при величине рассогла сования фазы принимаемых элементов сообщения с фазой тактовых импульсо на выходе делителя 9 большем, чем половина длительности одного неискаженного элемента сообщения (так как только в этом случае на выходах анализатора 1 имеются импульсы о на личии и знаке рассогласования, дополнительные импульсы корректирования с одного из выходов блока задер к и 3 поступают на второй суммирующие или вычитающий вход блока усреднения 14, что уменьшает время фазирования аппаратуры и увеличивает скорость установления синхронизма. Возможность работы предлагаемого устройства тактовой синхронизации в условиях воздействия переменных преобладаний принимаемых элементов сообщения позволяет повысить помехоустойчивость, точность и быстродействие фазирования аппаратуры (установления- синхронизма), а также значительно снизить требования к каналообразующей аппаратуре (модему) и линии связи. Кроме того, возможность работы в условиях преобладаний позволяет снизить требования к стабильности высокочастотных генераторов передающей и приемной частей аппаратуры в срав.нении с прототипом. Повышение помехоустойчивости, точности и быстродействия фазирования в предлагаемом устройстве обусловлено и тем, что одновременно с подстройкой частоты и фазы тактовых импульсов происходит корректировка величины преобладаний принимаемых элементов сообщения. В случае значительных преобладаний импульсы о знаке преобладаний формируются на выходах обоих анализаторов 1 и 2, что позволяет уменьшить время компенсации преобладаний принимаемых элементов сообщения, а в конечном итоге повысить помехоустойчивость, точность и быстродействия фазирования. Формула изобретения 1. Устройство тактовой синхронизации, содержащее последовательно соединенные преобразователь сигналов и формирователь фронтов сигнала и последовательно соединенные генератор импульсов, блок управления, к другим входам которого подключены выходы блока усреднения, и делитель частоты, выход которого подключен к одному из входов фазового дискриминатора, а выходы разрядов делителя частоты - через дешифратор к одному из входов блока защиты, причем вход и выход преобразователя сигналов являются соответственно входом и вьоходом устройства, отличающееся тем, чтр, с целью повышения быстродействия и точности синхронизации путем компенсации преобладаний принимаемых элементов сообщения, введены два анализатора преобЛс1даний, элементы ИЛИ, блок задержкч и реверсивный счетчик, при этом выход форг дарователя фронтов сигнала через блок защиты подключен к другому входу фазового дискриминатора, выходы которого подключены к первому и второму входам блока усреднения, дополнительные выходы формирователя фронтов сигнала подключены соответственно к первым и вторым объединенным входам первого и второго анализаторов преобладаний, к треть им входам которых подключены соответственно выход и дополнительный выход дешифратора, причем выходы первого анализатора преобладаний подключенык входам блока задержки,выходы которого подключены к входам реверсивного счетчи| а соответственно через первый и второй элементы ИЛИ, к другим входам которых подключены соответствующие выходы второго анализатора преОбладаний, выходы реверсивного счетчика подключены к другим входам преобразователя сигналов, а выходы блока задержки подключены к третьему и четвертому входам блока усреднения,

2. Устройство по п. 1, о т л ичающееся тем, что анализатор

преобладаний содержит две идентичные цепи, каждая из которых состоит из последовательно соединенных элемента ИЛИ, триггера и элемента И, второ вход которого объединен с первым входом элемента ИЛИ соответствующей цепи и с вторым входом триггера другой цепи, третьи входы элементов и Обеих цепей объединены и через элемент НЕ соединены с объединенными вторыми входами элементов ИЛИ обеих цепей, причем первые и вторые входы элементов ИЛИ и выходы элементов И обеих цепей являются соответственно входами и выходами анализатора преобладаний.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 599370, кл. Н 04 I, 7/08, 1976 (прототип) .

J 21 ,

L-l-j

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство для компенсации искажений типа "преобладание | 1987 |

|

SU1506581A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство для компенсации искажений типа "преобладание | 1983 |

|

SU1113899A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU965005A2 |

Авторы

Даты

1982-06-23—Публикация

1980-06-23—Подача