2. Устройство по п, 1, о т личающееся тем, что блок управления содержит распределитель сигналов, преобразоватоль кодов, пятый дешифратор, второй коммутатор, второй и третий регистры и узел усилителей, линии двунаправ ленной шины которого являются второй группой двунаправленных входов-выходов блока, входы второго и выходы третьего регистров являются первой группой двунаправленных входов-выходов блока,, первый, второй и третий выходы распределителя сигналов первый выход преобразователя кодов,первый выход узла усилителей, четвертый выход распределителя сигналов, первый и второй выходы второго регистра и пятый выход распределителя сигналов являются выходами с первого По четвертый и с. шестого по десятый блока управ- ; ления соответственно, третий выход второго регистра подсоединен к первому входу распределителя си1- налов, второй и третий входы которого, первый вход преобразователя кодов, вход третьего регистра, первый и второй входы второго коммутатора являются входами с второго по седьмой блока управления соответственно, первый вход преобразователя кодов является пятым выходом блока, шестой выход распределителя сигналов через пятый дешифратор соединен с первым входом узла усилителей, второй вход которого соединен с седьмым выходом распределителя сигналов, восьмой выход которого подключен к третьему входу второго коммутатора, второй выход преобразователя кодов соединен с вторым

входом узла усилителей,третий вход которого подключен к выходу второго коммутатора, третий вход преобразователя кодов является первым входом блока управления, четвертый вход преобразователя кодов соединен с вторым выходом узла усилителей, третий выход которого подключен к четвертому входу распределителя сигналов.

.3. Устройство по п. 1, о т л ичающееся тем, что распределитель сигналов содержит, кварцевый генератор, формирователь импульсов,

пятый счет чик,шестой и седьмой дешифра торы,триггеры,первый и второй блоки

элементов И,элементы И,элементы ИЛИ, причем входы шестого дешифратора, первый вход первого элемента ИЛИ и входы второго элемента ИЛИ являются входами с первого по третий распределителя сигналов соответственно, первый вход первого элемента И, первый вход установки в О пятого счетчика и первые входы установки в О с первого по четвертый триггеров являются четвертым входом распределителя сигналов, выходы первого и второго блоков элементов И и выход первого триггера являются первым выходом распределителя сигналов, выход второго триггера, выход второго блока элементов И, выход первого элемента ИЛИ, выход второго элемента И и выходы шестого дешифратора являются с второго по. шестой в.ыходами распределителя сигналов соответственно, выходы первого и второго блоков элементов И, выход третьего элемента И и первый выход формирователя импульсов .: являются седьмым выходом распределителя сигналов, выходы второго и третьего триггеров, второй и третий выходы формирователя импульсов и фыход первого элемента И являются восьмым выходом распределителя сигналов, выходы пятого дешифратора соединены с соответствующими входами третьего элемента ИЛИ, выход которого подключен к второму входу первого элемента И, третий вход которого соединен с третьим выходом формирователя импульсов и с первым входом четвертого элемента И, второй вход которого подключен к выходу четвертого элемента ИЛИ, а выход - к счетному входу пятого счетчика, выход которого через седьмой дешифратор соединен с первыми входами первого и второго блоков элементов И, выходы которых подключены к первым входам второго и третьего Э),ёментов И соответственно, выход второго триггеа соединен с вторым входом второго лока элементов И и с первым входом четвертого элемента ИЛИ,выход третъего триггера соединен с вторым входом первого блока элементов И с вторым входом четвертого элемента ИЛИ, выход четвертого триггера под- ключен к вторым входам второго и третьего элементов И, выход второго

элемента ИЛИ соединен с вторым входом установки в П пятого счетчиKdj первый и второй входы первого элемента ИЛИ подключены к входам установки в 1 и в О четвертого триггера соответственноj первый вход второго элемента ИЛИ соединен с входом установки в 1 первого триггера, с вторым входом установки в О второго триггера и с третьим входом первого элемента ИЛИ, второй

вход второго элемента ИЛИ подключен к второму входу установки в О первого триггера и к входу установки в 1 третьего триггер , а третий входк входу установки в 1 второго триггера и к второму входу установки в

третьего триггера, выход кварцевого генератора подключен к входу

формирователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления накопителями на магнитных дисках | 1982 |

|

SU1053143A1 |

| Устройство для сжатия информации | 1982 |

|

SU1043711A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1084837A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Устройство для управления считыванием графической информации | 1990 |

|

SU1725241A1 |

| Устройство для дискретизации и передачи сейсмических сигналов | 1980 |

|

SU1096680A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ПОСЛЕДОВАТЕЛЬНОСТИ СИГНАЛОВ | 2005 |

|

RU2299474C2 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ НАПРЯЖЕНИЯ ПРОБОЯ ЖИДКИХ ДИЭЛЕКТРИКОВ | 1997 |

|

RU2192650C2 |

| Устройство для управления считыванием графической информации | 1985 |

|

SU1357985A1 |

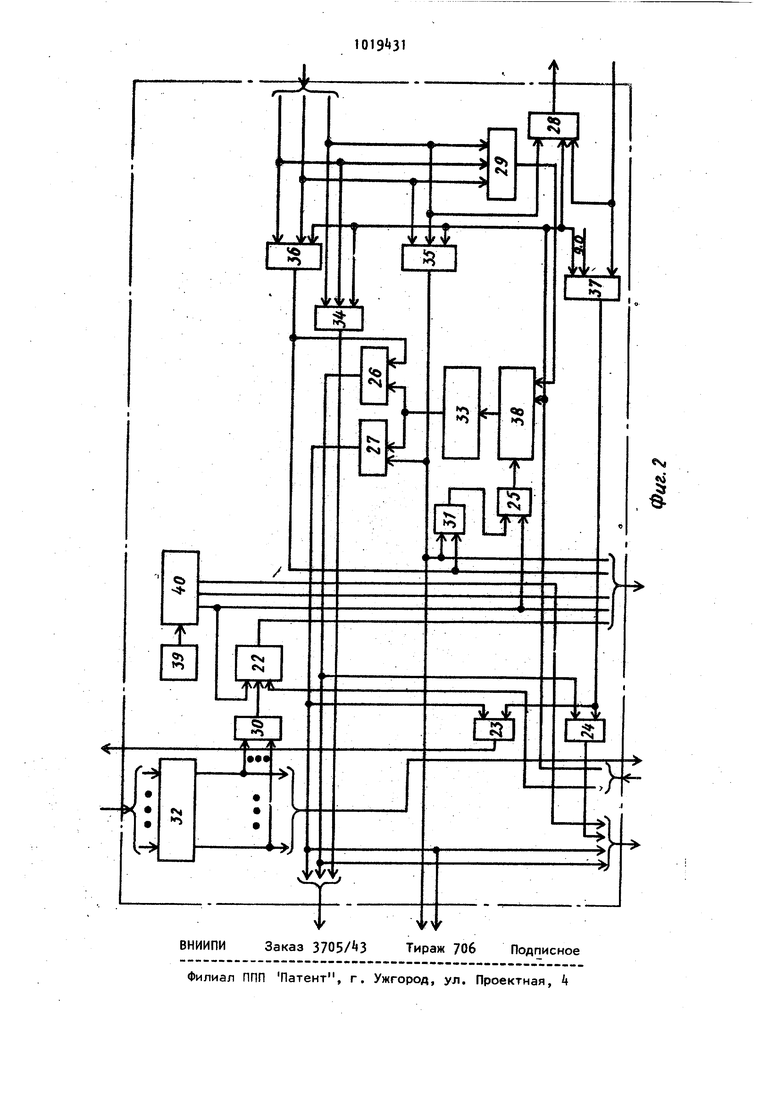

Изобретение относится к вычислительной технике и может быть исполь зовано при построе иии внешней памят вычислительных систем. Известно устройство для управления накопителями на магнитных дисках, содержащее регистр, блок управ ления, npeoбpaзoвateль кодов, комму татор, дешифратор, узел усилителей Недостатком известного устройства являются ограниченные функционал ные возможности из-за необходимости занимать центральный процессор под вспомогательнь1е процедуры разметки магнитных дисков . Наиболее близким по технической сущности к изобретению является устройство для ввода-вывода.информации из накопителей на магнит- ных дисках, содержащее блок управлен1(1Я,первая и вторая шина которого являются шинами канала и накопителя соответственно, блок памяти, вход которого соединен с первым вых дом блока, управления, второй и трет выходы которого соединены с, первыми входами блоков сравнения и контроля разметки, четвертый и пятый выходы - с вторым и третьим входами блока сравнения , четвертый вход которого подключен к выходу блока памяти и к первому входу блока управления , выход блока сравнения соединен с вторым входом блока контроля разметки, выход которого подключен к второму входу блока управления, шестой и седьмой выходы кот эрого соединены с соответствующими входамипервого счетчика, выход которого через первый дешиф-. ратор подключен к третьему входу блока управления, четвертый вход ко торого соединен с выходом первого регистра 2 }. Однако это устройство имеет ограниченные функциональные возможности, так как может производить разметку пакета только с. помощью последовательности .команд разметки дорожки, генерируемых центральным процессором. Целью изобретения является расширение функциональных возможностей устройства путем выполнения им функций центрального процессора по разметке магнитных дисков Указанная цель достигается тем, что в устройство для ввода-вывода информации из накопителей она магнитных дисках, содержащее блок управления, первая и вторая группы двунаправленных входов-выходов которого являются первой и второй двунаправленными шинами устройства соответственно, блок памяти, вход которого соединен с первым выходом блока управления, второй и третмй выходы которого соединены с первыми входами блоков сравнения и контроля разметки магнитных дисков соответственно, четвертый и пятый выходысоответственно с вторым и треТьиМ входами блока сравнения, четвертый вход которого подключен к выходу блока памяти и к первому входу блока управления, выход блока сравнения соединен с вторым входом блока контроля разметки магнитных дисков, выход которого подключен к второму входу блока управления, шее той и седьмой выходы которого соединены с соответствующими входами первого счетчика , выход которого через первый дешифратор подключен к третьему входу блока управления,чет вертый вход которого соединен с выходом первого регистра, введены с в рого по червертый счетчики и дешифраторы и первый Коммутатор, выход блока контроля разметки магнитных дисрков подключен к счетному входу второго счетчика, выход которого через второй дешифратор соединен с первым входом первого коммутатора, выход которого подключен к пятому входу блока управления, регистровые входы третьего и четвептого счетчик соединены с восьмым и девятым выходами блока управления соответственн выход третьего счетчика соединен с вторым входом первого коммутатора, с первым входом первого регистра, с шестым входом блока управления и через третий«дешифратор с тре им входом первого коммутатора и с счетным входом четвертого счетчика, выход которого соединен с четвертым входом первого коммутатора, с вторым входом первого регистра, с седьмым входом блока управлен и через четвертый дешифратор с пятым входом первого коммутатора, счетный вход третьего счетчика подключен к выходу первого дешифратора, десятый выходу блока управления соединен с шестым входом коммутатора. Блок управления содержит распределитель сигналов, преобразователь кодов,.пятый дешифратор, второй ком мутатор, второй и третий регистры и узел усилителей, линии двунаправленной шины которого являются второй группой двунаправленных в йэдоввыходов блока, входы второго и выходы третьего регистров являются первой группой двунаправленных вход выходов блока, первый, второй и тре тий выходы распределителя сигналов, первый выход преобразователя кодов, первый .выход узла усилителей, четве тый выход распределителя сигналов, первый и второй выходы второго регистра и пятый выход распределителя сигналов являются выходами с перво го по четвертый и с шестого по десятый блока управления соответствен но, третий выход второго регистра подсоединен с первому входу распределителя сигналов, второй и третий входы которого , первый вход преобразователя Korj,oB, вход третьего регистра, первый и второй входы вто рого коммутатора являются входами .с второго по седьмой блока управления соответственно, первый вход преобразователя кодов является пятым выходом блока, шестой рыход распределителя сигналов через пятый дешифратор соединен с первым входом узла усилителей, второй вход которого соединен с седьмым выходом распределителя сигналов, восьмой выход которого подключен к третьему входу второго коммутатора, второй выход преобразователя кодов соединен с вторым входом узла усилителей, третий вход преобразователя кодов является входом блока управления, четвертый вход преобразователя кодов соединен с вторым выходом узла усилителей, третий выход которого подключен к четвертому входу распределителя сигналов. Распределитель сигналов содержит кварцевый генератор, формирователь импульсов, пятый счетчик, шестой и седьмой дешифраторы, триггеры , первый и второй блоки элементов И, элементы И, элементы ИЛИ, причем входы шестого дешифратора, первый вход первого элемента ИЛИ и входы второго элемента ИЛИ являются входами -с первого по третий распределителя сигналов соответственно, первый вход первого элемента И, первый вход устанобки в О пятого счетчика и первые входы установки в О пятого счетчика и первые входы установки в О с первого по четвертый триггеров являются четвертым входом распределителя сигналов, выходы первого и второго блоков элементов И и выход первого триггера являются первым выходом раопредели-еля сигналов, выход второго.триггера, выход второго блока элементов И, выход первого элемента ИЛИ, выход второго элемента И и выходы шестого дешифратора являются с второго по шестой выходами распределителя сигналов соответственно, выходы первого и второго блоков элементов И, выход третьего элемента И и первый выход формирователя импульсов Являются седьмым выходом распределителя сигналов, выходы второго и третьего триггеров, второй и третий выходы формирователя импульсов и выход первого элемента И являются восьмым выходом распределителя сигналов, выходы пятого дешифратора соединены с соответствующими входами третьего элемента И, третиГ- вход .которого соединен с третьим выходом формирователя импульсов и с первым входом четвертого элемента И, второй вход которого подключен к выходу четвертого элемента ИЛИ, а выход - к сметному входу пятого счетчика, выход которого через седь дешифратор соединен с первыми входами первого и второго блоков элементов И, выходы которых подключены первым входам второго и третьего эл ментов И соответственно, выход второго триггера соединен с вторым вхо дом второго блока элементов И и с первым входом четвертого элемента ИЛИ,выход третьего триггера соединен с вторым входом первого блока элементов И с вторым входом четвертого элемента ИЛИ, выход четвертого триггера подключен к вторым входам второго и третьего элементов И, выход второго элемента ИЛИ соединен с вторым входом установки в О ПЯТОГО счетчика, первый и второй входы первого элемента ИЛИ подключены к входам установки в 1 и в О, четвертого триггера соответственно, первый вход второго эяе мента ИЛИ соединен с входом установки в 1 первого триггера, с вторым входом установки в О второго триггера и третьим входом первого элемента ИЛИ, второй вход второго элемента ИЛИ подключен к второму входу установки в О перво гс триггера и к входу установки в третьего триггера, а третий входк входу установки в 1 второго тpигfepa и к второму входу установки в Q третьего триггера, выход кварцевого генератора подключен к входу формирователя импульсов. На фиг. 1 показана функциональная схема устройства; на фиг.2- фун кциональная схема распределителя сигналов. Устройство содержит блок 1 управ ления, блок 2 памяти, блок 3 сравнения, блок 4 .контроля разметки маг нитных дисков , первый регистр 5, счетчики с первого по четвертый 6-9 дешифраторы с первого по четвертый. 1(Р-13,. первый коммутатор 1А, распределитель 15 сигналов, преобразова тель 16 кодов, пятый дешифратор 17, второй коммутатор 18, второй и третий регистры 19 и 20, узел 21 усили телей, элементы И с первого по четвертый 22-23, первый и второй блоки 26 и 27элементов И,элементы HJffI с, первого по четвертыГ , шесто{ и седьмой дешифраторы 32 и 33, с первого по четвертый триггеры 3|-37, пятый счетчик 38, кварцевый генератор 39, формирователь ЦО импульсов. Устройство работает следующим образом. По шине связи с каналом в блок 1 управления на регистр 19 поступает командное слово разметка дорожки. В командном слове содержатся номер цилиндра и номер доро)«ки, которую необходимо разметить. Код номера накопителя поступает из регистра 19 в распреде.питель 15 сигналов,где,, дешифрируется на дешифраторе 32 И через дешифратор 17, а также через узел усилителей 21 поступает в нужный накопитель.Кроме toro, при наличии сигнала на любой выходной шине дешифратора 32 (через элемент ИЛИ 30) и при наличии ответного сигнала готовности накопителя к работе из узла 21 тактовые импульсы из формирователя 0 импульсов (работающего от кварцевого генератора 39) проходят на вход элемента И 22 и поступают в коммутатор 18, в который также выдаются номера дорожки и ц||линдра соответственно с счетчиков 8 и 9, в которые они поступили из регистра 19. Ком(татор 18 коммутирует си|-, налы, поступающие через узел 21 и выбранный наког 1ТЙ1ь для установки блока головок на заданный цилиндр и включения нужной головки. После получения из накопителя сигнала Внимание в распределителе 15 сигналов происходит установка триггеров 35-37 и счетчика 38 в исходное состояние. Кроме того, на выходе элемента ИЛИ 28 вырабатыва ется сигнал, по которому устанавливается в О счетчик 6. На счетный вход счетчика 6 через узел 21 поступает сигнал Индекс из накопителя. Дальнейшая работа устройства определяется состоянием счетчика 6, передаваемым в распределитель IS на счетный счетчика 8 через jne. шифратор 10. По сигналу 1 индекс с дешифратора 10 в распределителе 15 триггер 36 устанавливается в 1( одновременно через элементы ИЛИ 29 тверждается нулевое состояние счетчика 38 ), Триггер 36 через коммутатор 18 переводит накопитель в состо яние записи, а также разрешает прох дение тактовых импульсов через элементы ИЛИ 31 и И 25 на вход счетчика 38. Положения счетчика 38 выделяются дешифратором 33 и через блок 27 элементов И поступают а блок 2 памяти и преобразователь 1б кодов. Таким образом, счетчик З8 обеспечивает заданную последовательность прохождения определенных кодов, сое тавляющих пробелы, и дгугую служебную информацию (из блока 2 памяти). номера цилиндра и дорожки ( из регист ра 5) и первого контрольного кода, который выбирается из блока 2 памяти при нулевом состоянии триггера З. Данные записи из преобразователя ко дов 1б через узел 2 поступают в на копитель для записи на дорожку. По сигналу 2 индекс в распреде лителе 15 триггер 36 устанавливает ся в О, а триггер 35 в состояние 1, Одновременно счетчик 38 устанавливается в нулевое состояние.Триг гер 35 через коммутатор 18 переводит накопитель в -состояние чтения, а также разрешает прохождение такто вых импульсов через элементы ИЛИ 3V и И 25 на вход счетчика 38. Продешифрированные положения счетчика 38 через блок элементов И 26 поступают в блоки контро/(я разметки памяти 2, преобразователь l6 кодов. После перевода накопителя в состояние чтения на вход преобразователя 16 кодов через узел 21 начинают поступать данные считывания. Считанные с дорожки собственный адрес и контрольный код передаются на один из входов блока 3 сравнения на другой вход которого поступает собственный адрес из регистра.5 а затем первый контрольный код из блока 2 памяти под действием управляющих сигналов с выходов блока И 27 элементов распределителя. В блоке 3 производится сравнение поступающей на его входы информации . При отсутствии ошибок разметки по сигналу 3 индекс в распределителе 15 через элемент ИЛИ 29 уст навливается в О счетчик 38, снимается сигнал чтения, и устанавливается в 1 триггер а также через элемент ИЛи 28 устанавливается в О счетчик 6. Далее по сигналу 1 индекс распределитель 15 переводит накопитель в состояние записи, и операция разметки повторяется аналогично описанной с той лишь разницей, что с выхода блока 2 памяти в блок 3 сравнения и преобразователь 16 кодов поступает второй контрольный код (по сигналу с выхода триггера 3). При отсутствии ошибок после чтения второго контрольного кода операция разметки дорожек заканчивается. При обнаружений ошибок разметки во время любого чтения в блоке 3 сравнения формируется сигнал несрав нения, который поступает в блок Л контроля разметки и проходит на выход блока Ц под действием управляющих сигналов с выходов блока 27 элементов И. На выходе блока 4 появляется сиг1нал ошибки, который, поступая в аспределитель 15, устанавливает в 1 триггер 37 и через элемент ИЛИ 28 устанавливает в О счетчик 6. Триггер 37 разрешает прохождение через элемент И 2k управляющего сигнала, обеспечивающего через преобразователь 16 кодов, запись собственного адреса с признаком дефектной дорожки. При этом запись контрольного кода не производится. После этого производится чтение вновь записанного собственного адреса. Если в блоке 3 сравнения вновь формируется ошибка, то с выхода элемента И 23 через коммутатор 14 и регистр 20 выдается, в блок сопряжения с каналом признак дефектного пакета. Если ошибок не обнаружено, огарация разметкй дорожки заканчивается выдачей в блок сопряжений с каналом признака ефектной дорожки.При выполнении команды Разметка цилиндра в командном сЛове информация о дорожках не указывается, а номер дорожки формируется в счетчике 8, содержимое которого увеличивается на единицу после каждой операции разметки дорожки. Дешифратор 12 выдает сигнал, соответствующий последней дорожке на цилиндре. Сигнал с выхода дешифратора 12 через коммутатор 1 после разметки последней дорожки на цилиндре (с поступлением разрешающего сигнала из распределителя 15) проходит в регистр 20, после чего операция размет Ю1 цилиндра заканчивается. При обнаружении одной или нескольких дефектных дорожек счетчик 7 произ водит их повсчет. Сигналы с выхода дешифратора 11 управляют прохождением через коммутатор Н в регистр :20 номера заданного цилиндра и номеров дефектных дорожек по мере их обнару.жения . Для выполнения команды Разметка пакета в командном слове указывается номер цилиндра, с которого надо начинать разметку пакета.Впроцеёсе выполнения этой команды операция разметки цилиндра выполняется столько раз, сколько цилиндров насчитывается от заданного до последнего, а следующий номер цилиндра формируется в счетчике 9, содержимое которого увеличивается на единицу после кайщой операции разметки цилинд ра. Дешифратор 13 выдает сигнал при состоянии счетчика 9, соответствующе номеру последнего цилиндра в пакете. Сигнал с выхода дешифратора 13 после

К

. t разметки последнего цилиндра прохо дит в регистр 20, после чего операция разметки пакета заканчивается. Содержимое слова состояния в регистре 20 при выполнении этой команды форми-. руется аналогично .предыдущей с той лишь разницей, что номера цилиндров, на которых обнаружены дефектные дорожки, могут быть разными и записываются в слово состояния через коммутатор Н из счетьмка 9. По сравнению с известным решением изобретение позволяет расширить функциональные возможности устройства. : путем повышения производительности вычислительной системы по отношени.в к пользовательским программам путем практически полного освобождения центрального процессора от операции инициа лизации пакета-дисков. Кроме того. при этом количество .обменов между каналами ввода-вывода и устройствами управления сокращается не менее чем на 10000 ед.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| м,, 1986 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| 0 |

|

SU77765A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-05-23—Публикация

1982-02-11—Подача