ды устройства соединены с пятым входом коммутатора и с четвертым входом блока усилителей соответственно, четвертый выход блока усилителей является первым выходом устройства, шестой выход первого регистра соединен с пятым входом блока формирования и поиска сигналов записи, отличающееся тем, что, с целью повышения пропускной способности подсистемы внешней памяти, в него введены девятый и десятый элементы И, пятый дешифратор, вторая сборка элементов И, второй элемент ИЛИ, инвертор, второй регистр, третий счетчик, выход которого соединен с входом пятого дешифратора, первый выход которого соединен с первым входом установки в «1 первого триггера, а второй выход - с первыми входами девятого и десятого элементов И, с вторым входом установки в «1 первого триггера и через инвертор с первым входом второй сборки элементов И, выход которой является вторым выходом устройства, а второй вход соединен с шестым выходом блока формирования и поиска сигналов записи, седьмой выход последнего подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, а выход - с вторым входом восьмого элемента И, третий вход которого подключен к выходу первого элемента ИЛИ, второй вход девятого элемента И соединен с четвертым выходом блока формирования и поиска сигналов записи, а выход - с первым входом второго регистра, второй вход которого соединен с выходом десятого элемента И, а выход является третьим выходом устройства, счетный вход и вход установки в «О третьего счетчика соединены с пятым и вторым выходами блока усилителей, соответственно, второй вход десятого элемента И и третьи входы девятого элемента И и второй сборки элементов И подключены к соответствующим выходам второго дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода информации из накопителей на магнитных дисках | 1982 |

|

SU1019431A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для сопряжения | 1983 |

|

SU1104498A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Информационный видеонакопитель | 1984 |

|

SU1180827A1 |

УСТРОЙСТВО УПРАВЛЕНИЯ НАКОПИТЕЛЯМИ НА МАГНИТНЫХ ДИСКАХ, содержащее первый регистр, вход которого является входом устройства, а первый выход через первый дешифратор соединен с первым входом первого элемента И, выход которого подключен к первому входу . блока управления накопителями, соединенного выходом с первым входом блока усилителей, первый выход последнего подключен к первому входу блока формирования и поиска сигналов записи, соединенного первым выходом с вторым входом блока усилителей, второй выход которого подключен к первым входам установки в «О первого счетчика, первого и второго триггеров, выход первого триггера соединен с одним входом первого элемента ИЛИ и с вторым входом блока управления накопителями, а также с вторым входом блока формирования и поиска сигналов записи, выход второго триггера соединен с третьим входом блока управления накопителями и с другим входом первого элемента ИЛИ, выход которого соединен с первыми входами с второго по пятый элементов И и первой сборки элементов И, выход которой подключен к первому входу коммутатора, выход которого соединен с третьим входом блока формирования и поиска сигналов записи, второй и третий выходы которого соединены с первым и вторьш входами шестого элемента И соответственно; а четвертый выход - с вторьш вхо- , дом установки в «О первого счетчика, выходом соединенного с входом второго дешифратора, а счетным входом - с выходом седьмого элемента И, первый вход последнего соединен с выходом третьего триггера, первый вход установки в «1 которого подключен к выходу второго элемента И, а второй вход установки в «1 - к выходу пятого элемента И, выход четвертого элемента И соединен с входом установки в «О третьего триггера, второй выход первого регистра через третий дешифратор соединен с третьим входом блока усилителей, третий выход которого соединен с вторым входом первого элемента И, третий выход первого регистра соединен с вторым входом коммутатора и с регистровым входомвторого счетчика, выход которого через четвертый дешифратор соединен с вторым входом второго элемента И, четвертый выход $S первого регистра соединен с третьим дом коммутатора и с четвертым входом блока управления накопителями, пятый выход первого регистра соединен с четвертым входом коммутатора и с пятым входом блока управления накопителями, выход восьмого элемента И соединен со счетным входом формирователя контрольной суммы, выход которого соединен с вторым входом первой сборки элементов И, управляюш.ий вход коммутатора, четвертый вход блока формирования и поиска сигналов записи, вторые ел входы третьего, четвертого и пятого элеменсо тов И, третий вход первой сборки элементов И, первый вход восьмого элемента И, вторые входы установки в «О первого и второго триггеров, вход установки в «1 второго со триггера, вход установки «О формирователя контрольной суммы, третий вход установки в «О первого счетчика соединены с соответствуюш,ими выходами второго дешифратора, третьи входы первого, второго, третьего, четвертого и пятого элементов И, второй вход седьмого элемента И, шестой вход блока управления накопителями соединены с пятым выходом .блока формирования и поиска сигналов записи, второй и третий вхо

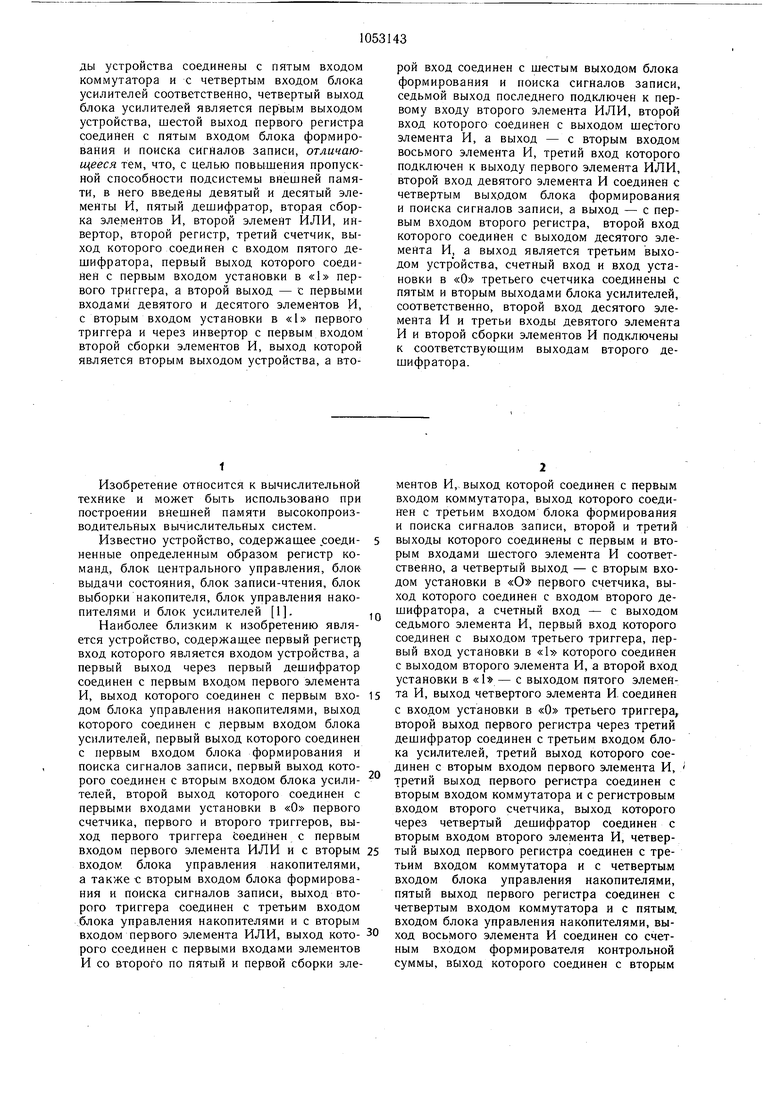

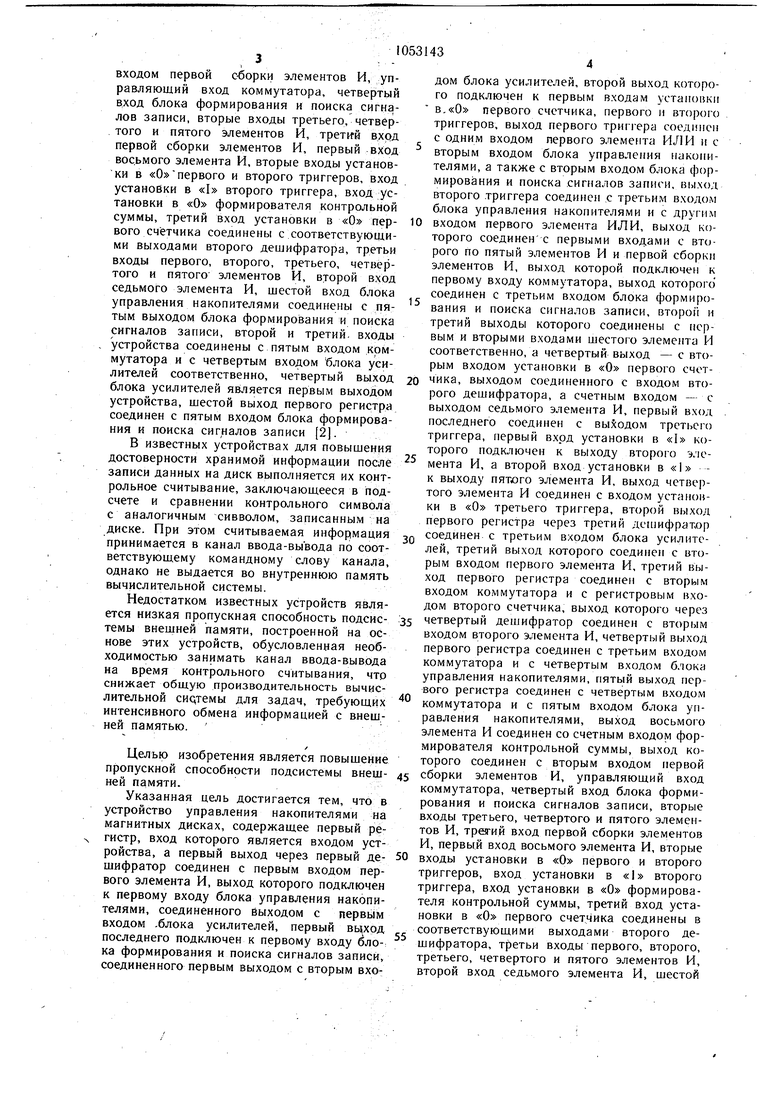

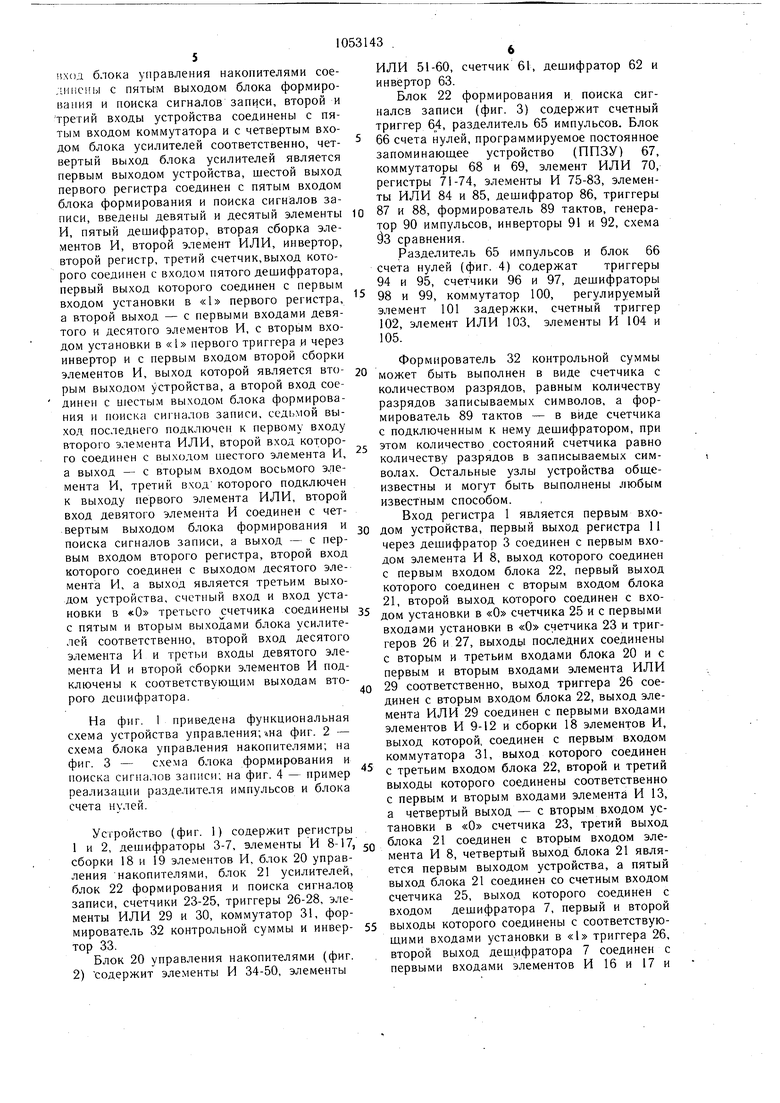

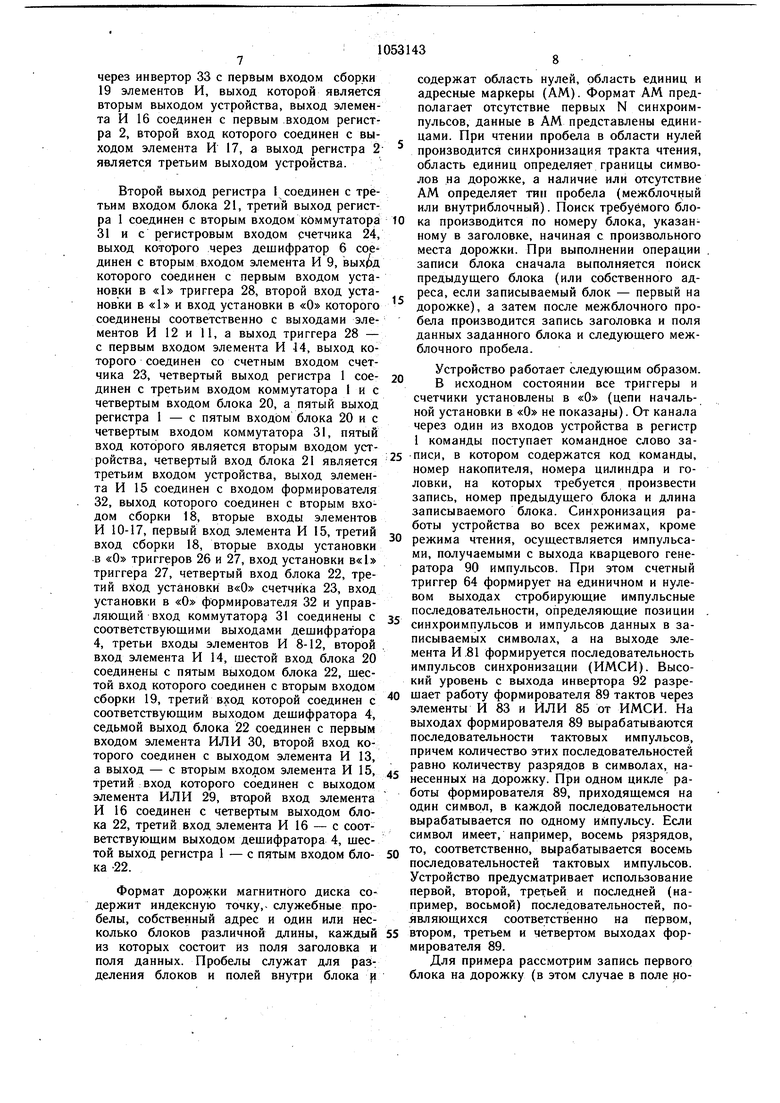

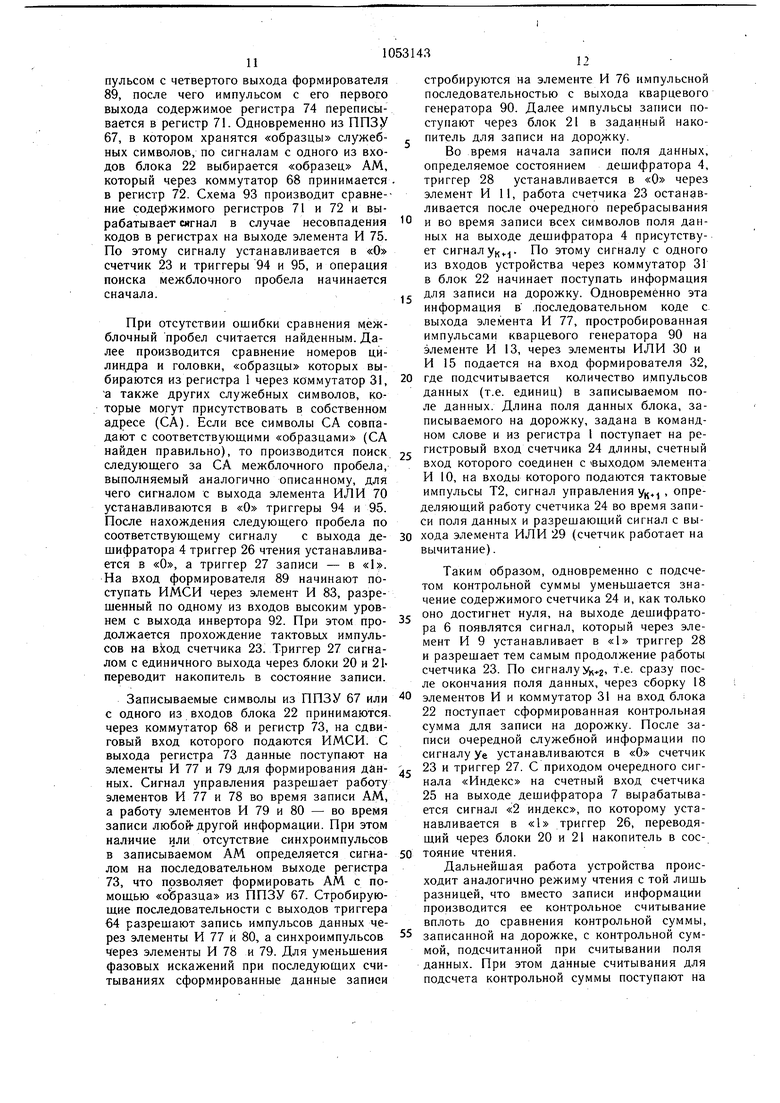

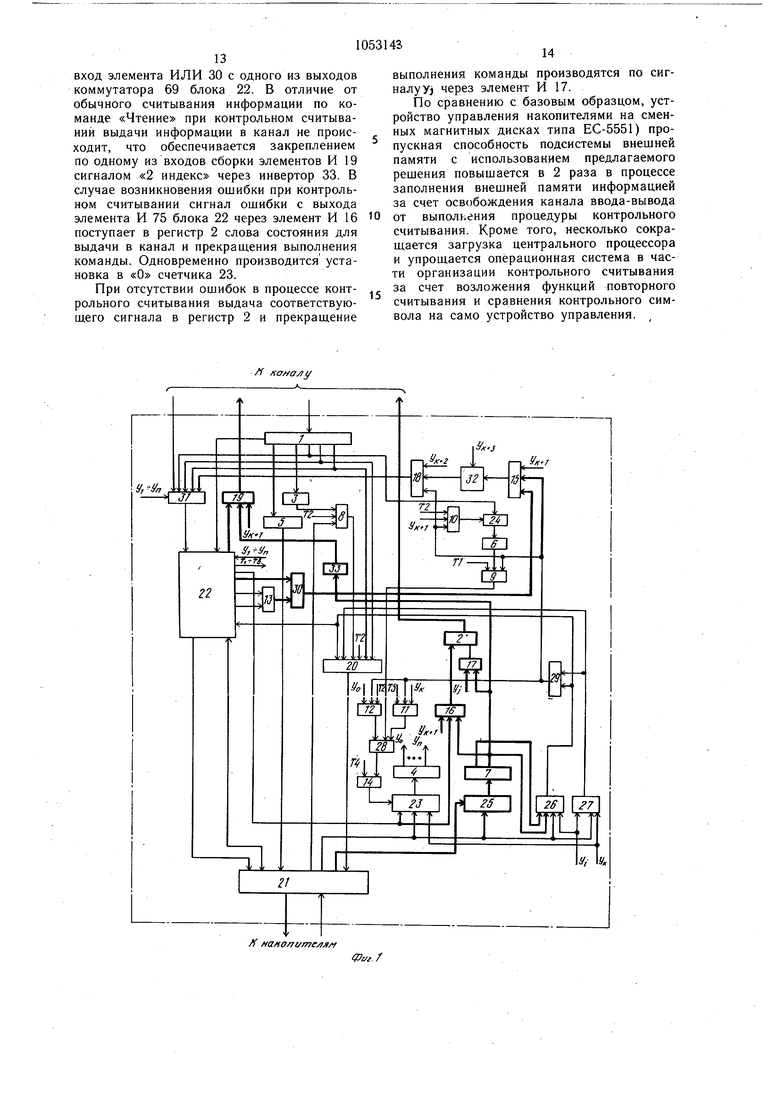

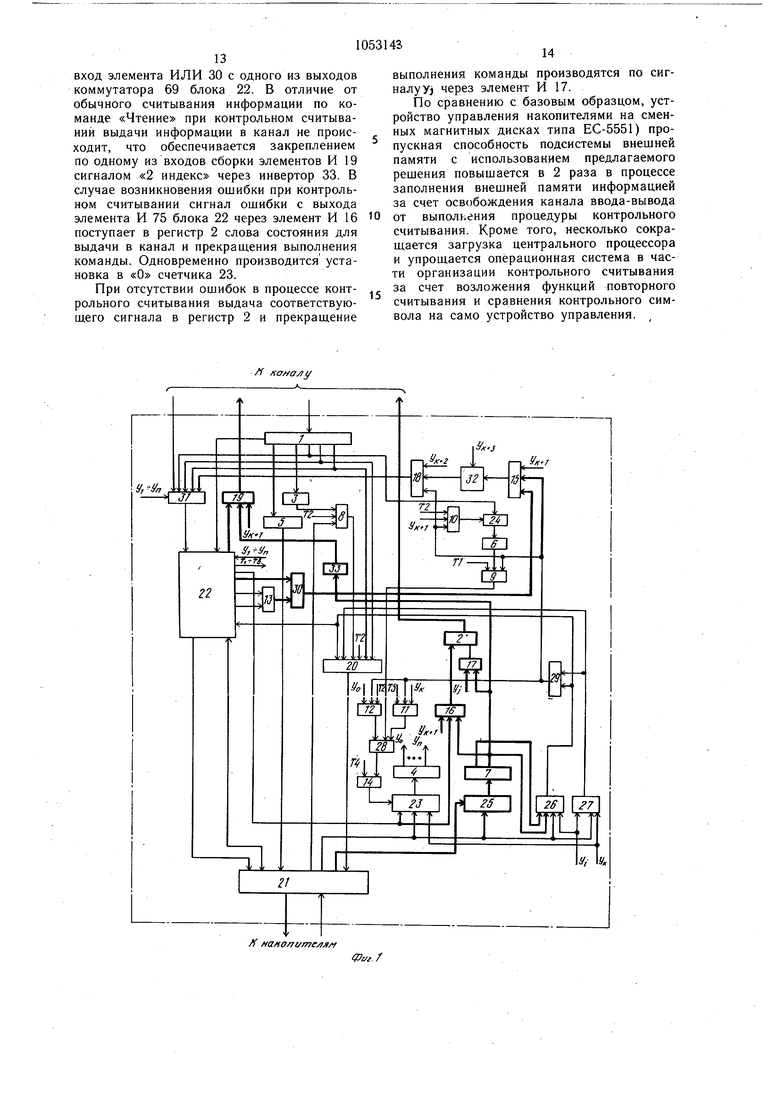

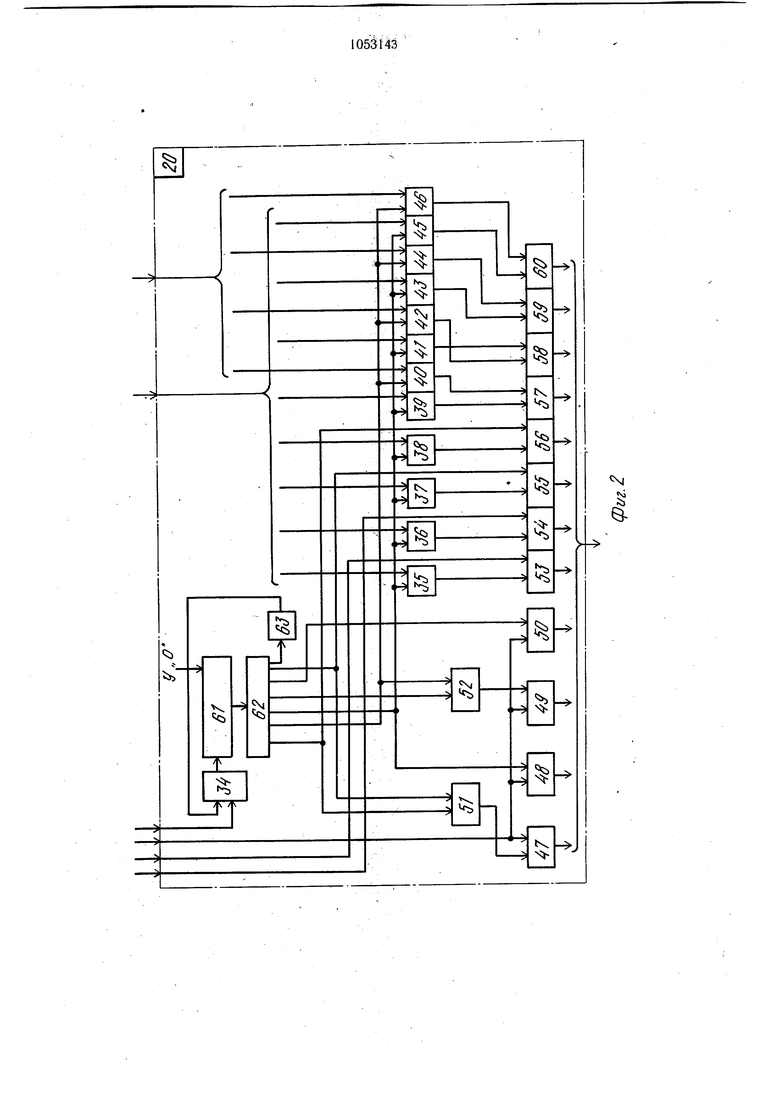

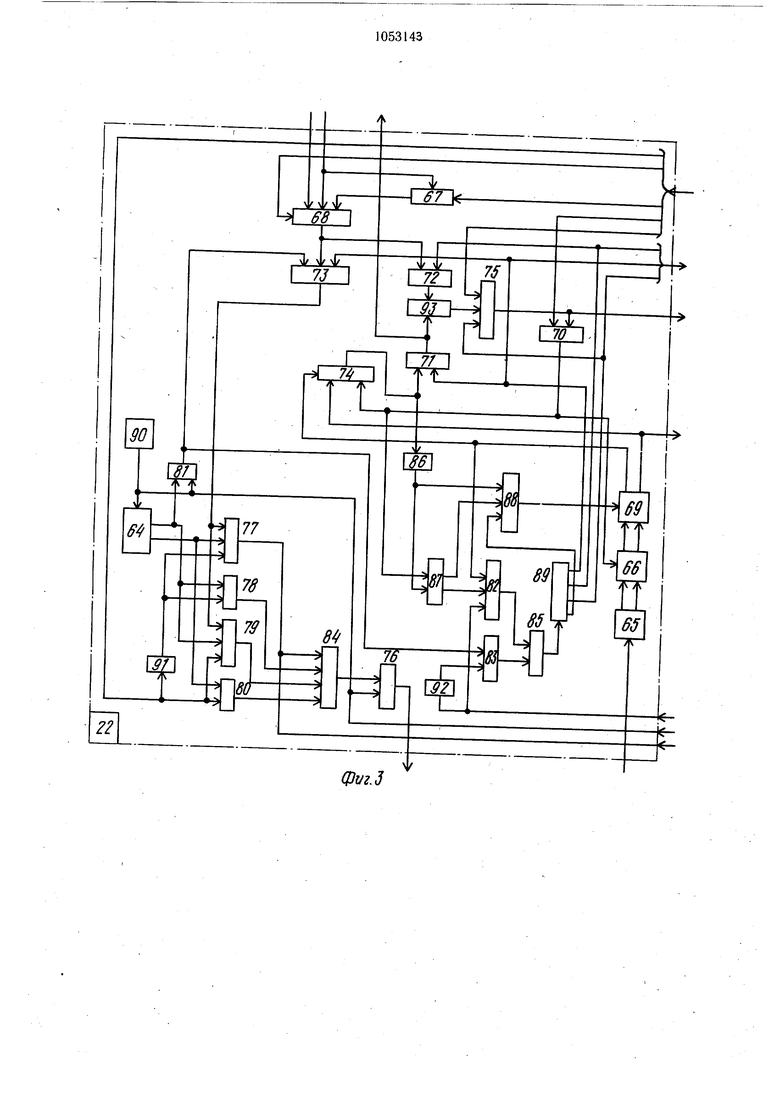

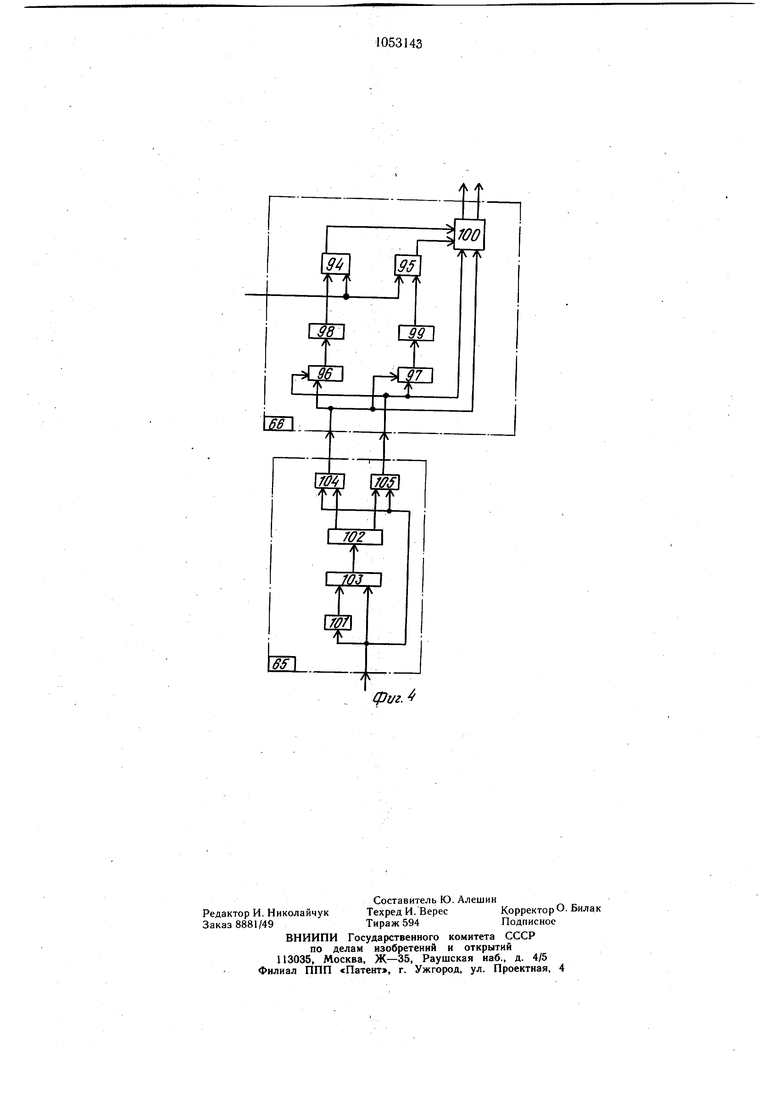

Изобретение относится к вычислительной технике и может быть использовано при построении внешней памяти высокопроизводительных вычислительных систем. Известно устройство, содержашее соединенные определенным образом регистр команд, блок центрального управления, блок выдачи состояния, блок записи-чтения, блок выборки накопителя, блок управления накопителями и блок усилителей 1. Наиболее близким к изобретению является устройство, содержащее первый регистру вход которого является входом устройства, а первый выход через первый дешифратор соединен с первым входом первого элемента И, выход которого соединен с первым входом блока управления накопителями, выход которого соединен с первым входом блока усилителей, первый выход которого соединен с первым входом блока формирования и поиска сигналов записи, первый выход которого соединен с вторым входом блока усилителей, второй выход которого соединен с первыми входами установки в «О первого счетчика, первого и второго триггеров, выход первого триггера Соединен с первым входом первого элемента ИЛИ и с вторым входом блока управления накопителями, а также ; вторым входом блока формирования и поиска сигналов записи, выход второго триггера соединен с третьим входом блока управления накопителями и с вторым входом первого элемента ИЛИ, выход которого соединен с первыми входами элементов И со второго по пятый и первой сборки элементов И, выход которой соединен с первым входом коммутатора, выход которого соединен с третьим входом блока формирования и поиска сигналов записи, второй и третий выходы которого соединены с первым и вторым входами шестого элемента И соответственно, а четвертый выход - с вторым входом установки в «О первого счетчика, выход которого соединен с входом второго дешифратора, а счетный вход - с выходом седьмого элемента И, первый вход которого соединен с выходом третьего триггера, первый вход установки в «1 которого соединен с выходом второго элемента И, а второй вход установки в «1 - с выходом пятого элемента И, выход четвертого элемента И. соединен с входом установки в «О третьего триггера, второй выход первого регистра через третий дешифратор соединен с третьим входом блока усилителей, третий выход которого соединен с вторым входом первого элемента И, третий выход первого регистра соединен с вторым входом коммутатора и с регистровым входом второго счетчика, выход которого через четвертый дешифратор соединен с вторым входом второго элемента И, четвертый выход первого регистра соединен с третьим входом коммутатора и с четвертым входом блока управления накопителями, пятый выход первого регистра соединен с четвертым входом коммутатора и с пятым, входом блока управления накопителями, выход восьмого элемента И соединен со счетным входом формирователя контрольной суммы, выход которого соединен с вторым входом первой сборки элементов И, управляющий вход коммутатора, четвер тый в.ход блока формирования и поиска сигналов записи, вторые входы третьего, четвёртого и пятого элементов И, rpeTifS вход первой сборки элементов И, первый вход восьмого элемента И, вторые входы установки в «О первого и второго триггеров, вход установки в «I второго триггера, вход установки в «О формирователя контрольной суммы, третий вход установки в «О первого счетчика соединены с соответствующими выходами второго дешифратора, третьи входы первого, второго, третьего, четвертого и пятого элементов И, второй вход седьмого элемента И, шестой вход блока управления накопителями соединены с пятым выходом блока формирования и поиска сигналов записи, второй и третий, входы устройства соединены с пятым входом коммутатора и с четвертым входом блока усилителей соответственно, четвертый выход блока усилителей является первым выходом устройства, шестой выход первого регистра соединен с пятым входом блока формирования и поиска сигналов записи 2. В известных устройствах для повышения достоверности хранимой информации после записи данных на диск выполняется их контрольное считывание, заключаюшееся в подсчете и сравнении контрольного символа с аналогичным сивволом, записанным на диске. При этом считываемая инфор|мация принимается в канал ввода-вывода по соответствующему командному слову канала, однако не выдается во внутреннюю память вычислительной системы. Недостатком известных устройств является низкая пропускная способность подсистемы внешней памяти, построенной на основе этих устройств, обусловленная необходимостью занимать канал ввода-вывода на время контрольного считывания, что снижает общую производительность вычислительной системы для задач, требующих интенсивного обмена информацией с внешней памятью. , Целью изобретения является повышение пропускной способности подсистемы внешней памяти. Указанная цель достигается тем, что в устройство управления накопителями на магнитных дисках, содержащее первый регистр, вход которого является входом устройства, а первый выход через первый дешифратор соединен с первым входом первого элемента И, выход которого подключен к первому входу блока управления накопителями, соединенного выходом с первь1м входом -блока усилителей, первый выход последнего подключен к первому входу лока формирования и поиска сигналов записи, соединенного первым выходом с вторым входом блока усилителей, второй выход которого подключен к первым входам установки в,«О первого счетчика, первого и второго триггеров, выход первого триггера соединен с одним входом первого элемента ИЛИ н с вторым входом блока управления накопителями, а также с вторым входом блока формирования и поиска сигналов записи, ви.ход второго триггера соединен с третьим входом блока управления накопителями и с другим входом первого элемента ИЛИ, выход которого соединен с первыми входами с второго по пятый элементов И и первой сборки элементов И, выход которой подключен к первому входу коммутатора, выход которого соединен с третьим входом блока формирования и поиска сигналов записи, второй и третий выходы которого соединены с нсрвым и вторыми входами шестого элемента И соответственно, а четвертый выход - с вторым входом установки в «О первого счотчика, выходом соединенного с входом второго дешифратора, а счетным входом - с выходом седьмого элемента И, первый вход последнего соединен с выводом третьего триггера, первый вход установки в «I которого подключен к выходу второго элемента И, а второй вход установки в «I к выходу пятюго элемента И, выход четвертого элемента И соединен с входом установки в «О третьего триггера, второй выход первого регистра через третий дсчиифратлр соединен с третьим входом блока усилителей, третий выход которого соединен с вторым входом первого элемента И, третий выход первого регистра соединен с вторым входом коммутатора и с регистровым входом второго счетчика, выход которого через четвертый дешифратор соединен с вторым входом второго элемента И, четвертый выход первого регистра соединен с третьим входом коммутатора и с четвертым входом блока управления накопителями, пятый выход первого регистра соединен с четвертым входом коммутатора и с пятым входом блока управления накопителями, выход восьмого элемента И соединен со счетным входом формирователя контрольной суммы, выход которого соединен с вторым входом первой сборки элементов И, управляющий вход коммутатора, четвертый вход блока формирования и поиска сигналов записи, вторые входы третьего, четвертого и пятого элементов И, третий вход первой сборки элементов И, первый вход восьмого элемента И, вторые входы установки в «О первого и второго триггеров, вход установки в «1 второго триггера, вход установки в «О формирователя контрольной суммы, третий вход установки в «О первого счетчика соединены в соответствующими выходами второго дещифратора, третьи входы первого, второго, третьего, четвертого и пятого элементов И, второй вход седьмого элемента И, шестой иход блока управления накопителями соединены с пятыМ выходом блока формирования и поиска сигналов записи, второй и третий входы устройства соединены с пятым входом коммутатора и с четвертым входом блока усилителей соответственно, четвертый выход блока усилителей является первым выходом устройства, шестой выход первого регистра соединен с пятым входом блока формирования и поиска сигналов записи, введены девятый и десятый элементы И, пятый дешифратор, вторая сборка элементов И, второй элемент ИЛИ, инвертор, второй регистр, третий счетчик,выход которого соединен с входом пятого дешифратора, первый выход которого соединен с первым входом установки в «1 первого регистра, а второй выход - с первыми входами девятого и десятого элементов И, с вторым входом установки в «1 первого триггера и через инвертор и с первым входом второй сборки элементов И, выход которой является вторым выходом устройства, а второй вход соединен с шестым выходом блока формирования и поиска сигналов записи, седьмой выход последнего подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом шестого элемента Л, а выход - с вторым входом восьмого элемента И, третий вход которого подключен к выходу первого элемента ИЛИ, второй вход девятого элемента И соединен с чет,,, вертым выходом блока формирования и ования V - с пер поиска сигналов записи, а выход - с первым входом второго регистра, второй вход которого соединен с выходом десятого элемента И, а выход является третьим выходом устройства, счетный вход и вход установки в .0 третьего счетчика соединены с пятым и вторым выходами блока усилите „ леи соответственно, второй вход десятого элем.ента И и третьи входы девятогоэлемента И и второй сборки элементов Иподключены к соответствуюшим выходамвторого дешифратора. На фиг. 1 приведена функциональная схема устройства управления;-sHa фиг. 2 - схема блока управления накопителями; на фиг. 3 - схема блока формирования и поиска сигналов записи; на фиг. 4 - пример реализации разделителя импульсов и блока счета нулей. Устройство (фиг. 1) содержит регистры 1 и 2, дешифраторы 3-7, элементы И 8-17, сборки 18 и 19 элементов И, блок 20 управления накопителями, блок 21 усилителей, блок 22 формирования и поиска сигнало1 записи, счетчики 23-25, триггеры 26-28, элементы ИЛИ 29 и 30, коммутатор 31, формирователь 32 контрольной суммы и инвертор 33. Блок 20 управления накопителями (фиг. 2) содержит элементы И 34-50, элементы ИЛИ 51-60, счетчик 61, дешифратор 62 и инвертор 63. Блок 22 формирования и поиска сигналсв записи (фиг. 3) содержит счетный триггер 64, разделитель 65 импульсов. Блок 66 счета нулей, программируемое постоянное запоминающее устройство (ППЗУ) 67, коммутаторы 68 и 69, элемент ИЛИ 70, регистры 71-74, элементы И 75-83, элементы ИЛИ 84 и 85, дешифратор 86, триггеры 87 и 88, формирователь 89 тактов, генератор 90 импульсов, инверторы 91 и 92, схема 93 сравнения. Разделитель 65 импульсов и блок счета нулей (фиг. 4) содержат триггеры 94 и 95, счетчики 96 и 97, дешифраторы 98 и 99, коммутатор 100, регулируемый элемент 101 задержки, счетный триггер 102, элемент ИЛИ 103, элементы И 104 и 105. Формирователь 32 контрольной суммы может быть выполнен в виде счетчика с количеством разрядов, равным количеству разрядов записываемых символов, а формирователь 89 тактов - в виде счетчика с подключенным к нему дешифратором, при „ количество состояний счетчика равно количеству разрядов в записываемых символах. Остальные узлы устройства обш,еизвестны и могут быть выполнены любым известным способом. Вход регистра 1 является первым входом устройства, первый выход регистра И ..р дешифратор 3 соединен с первым входом элемента И 8, выход которого соединен с первым входом блока 22, первый выход которого соединен с вторым входом блока 21, второй выход которого соединен с ;; а :;овкТ;То;Ге ;чика 2Ти Гп вьГм и j оо входами установки в «О счетчика 23 и тригп п-г геров 26 и 27, выходы последних соединены с вторым и третьим входами блока 20 и с первым и вторым входами элемента ИЛИ 29 соответственно, выход триггера 26 соединен с вторым входом блока 22, выход элемента ИЛИ 29 соединен с первыми входами элементов И 9-12 и сборки 18 элементов И, выход которой, соединен с первым входом коммутатора 31, выход которого соединен с третьим входом блока 22, второй и третий выходы которого соединены соответственно с первым и вторым входами элемента И 13, а четвертый выход - с вторым входом установки в «О счетчика 23, третий выход 21 соединен с вторым входом элемента И 8, четвертый выход блока 21 является первым выходом устройства, а пятый выход блока 21 соединен со счетным входом счетчика 25, выход которого соединен с входом дешифратора 7, первый и второй выходы которого соединены с соответствующими входами установки в «1 триггера 26, второй выход дешифратора 7 соединен с первыми входами элементов И 16 и 17 и через инвертор 33 с первым входом сборки 19 элементов И, выход которой является вторым выходом устройства, выход элемента И 16 соединен с первым .входом регистра 2, второй вход которого соединен с выходом элемента И 17, а выход регистра 2 является третьим выходом устройства. Второй выход регистра 1 соединен с третьим входом блока 21, третий выход регистра 1 соединен с вторым входом коммутатора 31 и с регистровым входом счетчика 24, выход которого через дешифратор 6 соединен с вторым входом элемента И 9, которого соединен с первым входом установки в «1 триггера 28, второй вход установки в «1 и вход установки в «О которого соединены соответственно с выходами элементов И 12 и 11, а выход триггера 28 - с первым входом элемента И 14, выход которого соединен со счетным входом счетчика 23, четвертый выход регистра 1 соединен с третьим входом коммутатора 1 и с четвертым входом блока 20, а пятый выход регистра 1 - с пятым входом блока 20 и с четвертым входом коммутатора 31, пятый вход которого является вторым входом устройства, четвертый вход блока 21 является третьим входом устройства, выход элемента И 15 соединен с входом формирователя 32, выход которого соединен с вторым входом сборки 18, вторые входы элементов И 10-17, первый вход элемента И 15, третий вход сборки 18, вторые входы установки в «О триггеров 26 и 27, вход установки в«1 триггера 27, четвертый вход блока 22, третий вход установки в«0 счетчика 23, вход установки в «О формирователя 32 и управляющий вход коммутатора 31 соединены с соответствующими выходами дещнфратора 4, третьи входы элементов И 8-12, второй вход элемента И 14, щестой вход блока 20 соединены с пятым выходом блока 22, шестой вход которого соединен с вторым входом сборки 19, третий вход которойсоединен с соответствующим выходом дешифратора 4, седьмой выход блока 22 соединен с первым входом элемента ИЛИ 30, второй вход которого соединен с выходом элемента И 13, а выход - с вторым входом элемента И 15, третий вход которого соединен с выходом элемента ИЛИ 29, второй вход элемента И 16 соединен с четвертым выходом блока 22, третий вход элемента И 16 - с соответствующим выходом дешифратора 4, шестой выход регистра 1 - с пятым входом блока -22. Формат дорожки магнитного диска содержит индексную точку,- служебные пробелы, собственный адрес и один или несколько блоков различной длины, каждый из которых состоит из поля заголовка и поля данных. Пробелы служат для раЗ: деления блоков и полей внутри блока р содержат область нулей, область единиц и адресные маркеры (AM). Формат AM предполагает отсутствие первых N синхроимпульсов, данные в AM представлены единицами. При чтении пробела в области нулей производится синхронизация тракта чтения, область единиц определяет границы символов на дорожке, а наличие или отсутствие AM определяет тип пробела (межблочь1ый или внутриблочный). Поиск требуемого блока производится по номеру блока, указанному в заголовке, начиная с произвольного места дорожки. При выполнении операции , записи блока сначала выполняется поиск предыдущего блока (или собственного адреса, если записываемый блок - первый на дорожке), а затем после межблочного пробела производится запись заголовка и поля данных заданного блока и следующего межблочного пробела. Устройство работает следующим образом. В исходном состоянии все триггеры и счетчики установлены в «О (цепи начальной установки в «О не показаны). От канала через один из входов устройства в регистр 1 команды поступает командное слово записи, в котором содержатся код команды, номер накопителя, номера цилиндра и головки, на которых требуется произвести запись, номер предыдущего блока и длина записываемого блока. Синхронизация работы устройства во всех режимах, кроме режима чтения, осуществляется импульсами, получаемыми с выхода кварцевого генератора 90 импульсов. При этом счетный триггер 64 формирует на единичном и нулевом выходах стробирующие импульсные последовательности, определяющие позиции . синхроимпульсов и импульсов данных в записываемых символах, а на выходе элемента И,81 формируется последовательность импульсов синхронизации (ИМСИ). Высокий уровень с выхода инвертора 92 разрещает работу формирователя 89 тактов через элементы И 83 и ИЛИ 85 от ИМСИ. На выходах формирователя 89 вырабатываются последовательности тактовых импульсов, причем количество этих последовательностей равно количеству разрядов в символах, нанесенных на дорожку. При одном цикле работы формирователя 89, приходящемся на один символ, в каждой последовательности вырабатывается по одному импульсу. Если символ имеет, например, восемь рязрядов, то, соответственно, вырабатывается восемь последовательностей тактовых импульсов. Устройство предусматривает использование первой, второй, третьей и последней (например, восьмой) последовательностей, появляющихся соответственно на первом. втором, третьем и четвертом выходах формирователя 89. Для примера рассмотрим запись первого блока на дорожку (в этом случае в поле номера предыдущего блока в командном слове додержатся нули). Код номера накопителя из регистра 1 поступает через дешифратор 5 в блок 21 усилителей в требуемый накопитель. Кроме того, выделенный код команды с выхода дешифратора 3 при наличии ответного сигнала готовности накопителя к работе из блока 21 пропускает на выход элемента И 8 тактовые импульсы из формирователя 89, которые поступают в блок 20 управления накопителями на вход элемента 10 И 34 (фиг. 2). При отсутствии сигнала на последнем выходе дешифратора 63 на элемент И 34 поступает через инвертор 63 сигнал, разрешающий прохождение тактовых импульсов на вход счетчика 61 позиционирования Продешифрированные положения счетчика 61 с выхода дешифратора 62 разрешают прохождение тактовых импульсов через элементы И 35-50 и ИЛИ 51-60 в соответствии с интерфейсом «Устройство управления - накопитель на сменных маг- 20 нитных дисках (на фиг. 2 показана схемная реализация интерфейса ОСТ4 аШО.304. 005 редакция 1-74 для работы с накопителями на сменных магнитных дисках типа ЕС-5056М). В блок 20 также выдаются номера цилиндра и дорожки из регистра 1 и он вырабатывает сигналы, поступающие через блок 21 в выбранный накопитель для установки блока головок на заданный цилиндр и включения нужной головки. После получения от 30 накопителя (через блок 21) сигнала «Внимание происходит установка в «О триггеров 26, 27 и счетчиков 23,25. На счетный вход счетчика 25 индексов через блок 21 поступает из накопителя сигнал «Индекс, сообшающий о начале дорожки. По сигналу 35 «1 индеко с выхода дешифратора 7 триггер 26 чтения устанавливается в «Ь и сигналом с выхода через блок 20 переводит накопитель в состояние чтения, а также через элемент ИЛИ 29 разрешает прохождение 40 тактового импульса через элемент И 12, устанавливающего в «1 триггер 28. Выход триггера 28 разрешает прохождение тактовых импульсов через элемент И 14 на счетный вход счетчика 23 управления, положения которого выделяются дешифра- 45 тором 4 и управляют общей последовательностью работы устройства. Как только счетчик 23 выйдет из нулевого состояния, прохожде.ние тактовых импульсов через элемент И 12 запрещается вплоть до следую- СА - - - щего нулевого состояния. Одновременно на вход разделителя 65 импульсов блока 22 (фиг. 3 и 4) поступают данные, считываемые с дорожки. В блоке 65 производится предварительное разделение считанных синхроимпульсов (СИ) и импульсов данных55 на основании априорно известных вреРегулируемыйсоотношений. менных формирует на 101 задержки элемент 5 25 выходе импульсную последовательность, задержанную относительно входной на полрвину периода синхросерии. Задержанные импульсы, проходя через элемент ИЛИ 103, объединяются с входными импульсами и образуют последовательность, в которой присутствуют все импульсы без пропусков, хотя во входной и задержанной последовательностях такие пропуски имеются. Счетный триггер 102, перебрасываясь по заднему фронту импульсов с выхода элемента ИЛИ 103, обеспечивает прохождение одних импульсов (например, СИ) через элемент И 104, а других (импульсов данных) - через элемент И 105, Однако при этом неизвестно, на каком из выходов блока 65 выделяются СИ, а на каком - данные. Для их идентификации в блоке 66 служат счетчики 96 и 97, каждый из которых считает импульсы, идущие с одного из выходов бло « устанавливается в «О импульсами с другого его выхода. Таким образом, счетчики 96 и 97 выполняют подсчет количества нулей (отсутствия импульсов) в каждой из последовательностей. Если в одной из них насчитано нулей больше, чем N, что определяется дешифраторами 98 и 99, настроенными на состояния N+1 счетчиков, и фиксируется триггерами 94 или 95, то эта последовательность идентифицируется как СИ, а другая - как данные. При этом триггера 94 и 95 разрешают прохождение идентифицированных последовательностей через коммутатор 100 на соответствующие выходы блока 66. Проходя через коммутатор 69, данные поступают на последовательный вход рерастра 74, а СИ --на сдвиговый вход этого регистра, обеспечивая последовательное его заполнение. В момент заполнения регистра 74 единицами, определяющий границу считываемого символа на выходе дешифратора 86 появляется сигнал, который устанавливает в «1 триггер 87 пуска формирователя 89 и триггер 88 чтения AM. При этом сигнал с единичного выхода триггера 87 разрешает работу формирователя 89 от СИ, считываемых с дорожки, а низкий уровень с нулеg p выхода триггера 87 запрещает повторное срабатывание триггера 88. Сигнал с единичного выхода триггера 88, поступая на управляющий вход коммутатора 69, изменяет его работу во, время предполагаемого считывания AM таким образом, что последовательности СИ и данных на выхо,Т ж дах коммутатора 69 меняются местами. При этом в регистре 74 формируется код, в разрядах которого единицы и нули соответствуют наличию или отсутствию СИ в соответствующих позициях считываемого символа и который служит для последующей идентификации AM. В последнем считывании AM триггер 88 устанавливается в «О импульсом с четвертого выхода формирователя 89, после чего импульсом с его первого выхода содержимое регистра 74 переписывается в регистр 71. Одновременно из ППЗУ 67, в котором хранятся «образцы служебных символов, по сигналам с одного из входов блока 22 выбирается «образец AM, который через коммутатор 68 принимается в регистр 72. Схема 93 производит сравнение содержимого регистров 71 н 72 и вырабатывает сигнал в случае несовпадения кодов в регистрах на выходе элемента И 75. По этому сигналу устанавливается в «О счетчик 23 и триггеры 94 и 95, и операция поиска межблочного пробела начинается сначала. При отсутствии ошибки сравнения межблочный пробел считается найденным. Далее производится сравнение номеров цилиндра и головки, «образцы которых выбираются из регистра 1 через коммутатор 31, а также других служебных символов, которые могут присутствовать в собственном адресе (СА). Если все символы СА совпадают с соответствующими «образцами (СА найден правильно), то производится поиск следующего за СА межблочного пробела, выполняемый аналогично описанному, для чего сигналом с выхода элемента ИЛИ 70 устанавливаются в «О триггеры 94 и 95. После нахождения следующего пробела по соответствующему сигналу с выхода дешифратора 4 триггер 26 чтения устанавливается в «О, а триггер 27 записи - в «1. На вход формирователя 89 начинают поступать имей через элемент И 83, разрешенный по одному из входов высоким уровнем с выхода инвертора 92. При этом продолжается прохождение тактовых импульсов на вход счетчика 23. Триггер 27 сигналом с единичного выхода через блоки 20 и 21переводит накопитель в состояние записи. Записываемые символы из ППЗУ 67 или с одного из входов блока 22 принимаются через коммутатор 68 и регистр 73, на сдвиговый вход которого подаются ИМСИ. С выхода регистра 73 данные поступают на элементы И 77 и 79 для формирования динных. Сигнал управления разрешает работу элементов И 77 и 78 во время записи AM, а работу элементов И 79 и 80 - во время записи любой-другой информации. При этом наличие или отсутствие синхроимпульсов в записываемом AM определяется сигналом на последовательном выходе регистра 73, что позволяет формировать AM с помощью «о бразца из ППЗУ 67. Стробирующие последовательности с выходов триггера 64 разрешают запись импульсов данных через элементы И 77 и 80, а синхроимпульсов через элементы И 78 и 79. Для уменьшения фазовых искажений при последующих считываниях сформированные данные записи стробируются на элементе И 76 импульсной последовательностью с выхода кварцевого генератора 90. Далее импульсы записи поступают через блок 21 в заданный накопитель для записи на дорожку. Во время начала записи поля данных, определяемое состоянием дешифратора 4, триггер 28 устанавливается в «О через элемент И 11, работа счетчика 23 останавливается после очередного перебрасывания и во время записи всех символов поля данных на выходе дешифратора 4 присутствует сигнал У|. По этому сигналу с одного из входов устройства через коммутатор 31 в блок 22 начинает поступать информация для записи на дорожку. Одновременно эта информация в .последовательном коде с выхода элемента И 77, простробированная импульсами кварцевого генератора 90 на элементе И 13, через элементы ИЛИ 30 и И 15 подается на вход формирователя 32, где подсчитывается количество импульсов данных (т.е. единиц) в записываемом поле данных. Длина поля данных блока, записываемого на дорожку, задана в командном слове и из регистра 1 поступает на регистровый вход счетчика 24 длины, счетный вход которого соединен свыходом элемента И 10, на входы которого подаются тактовые импульсы Т2, сигнал управления у, , определяющий работу счетчика 24 во время записи поля данных и разрешающий сигнал с выхода элемента ИЛИ 29 (счетчик работает на вычитание). Таким образом, одновременно с подсчетом контрольной суммы уменьшается значение содержимого счетчика 24 и, как только оно достигнет нуля, на выходе дешифратора 6 появлятся сигнал, который через элемент И 9 устанавливает в «1 триггер 28 и разрешает тем самым продолжение работы счетчика 23. По сигналуУк.е2 сразу после окончания поля данных, через сборку 18 элементов И и коммутатор 31 на вход блока 22 поступает сформированная контрольная сумма для записи на дорожку. После записи очередной служебной информации по сигналу Уе устанавливаются в «О счетчик 23 и триггер 27. С приходом очередного сигнала «Индекс на счетный вход счетчика 25 на выходе дешифратора 7 вырабатывается сигнал «2 индекс, по которому устанавливается в «Ь триггер 26, переводящий через блоки 20 и 21 накопитель в состояние чтения. Дальнейщая работа устройства происходит аналогично режиму чтения с той лишь разницей, что вместо записи информации производится ее контрольное считывание вплоть до сравнения контрольной суммы, записанной на дорожке, с контрольной суммой, подсчитанной при считывании поля данных. При этом данные считывания для подсчета контрольной суммы поступают на вход элемента ИЛИ 30 с одного из выходов коммутатора 69 блока 22. В отличие от обычного считывания информации по команде «Чтение при контрольном считываний выдачи информации в канал не происходит, что обеспечивается закреплением по одному из входов сборки элементов И 19 сигналом «2 индекс через инвертор 33. В случае возникновения ошибки при контрольном считывании сигнал ошибки с выхода ном считывании t;ni пл,л ишпилп . оетлида элемента И 75 блока 22 через элемент И 16 поступает в регистр 2 слова состояния для выдачи в канал и прекращения выполнения команды. Одновременно производится установка в «О счетчика 23. При отсутствии ошибок в процессе контрольного считывания выдача соответствующего сигнала в регистр 2 и прекращение

А к он а/ у

/у HaMO/7i/mf/ Aff

I-. Ул./

и выполнения команды производятся по сигналу Yj через элемент И 17. По сравнению с базовым образцом, устройство управления накопителями на сменных магнитных дисках типа ЕС-5551) пропускная способность подсистемы внешней памяти с использованием предлагаемого решения повышается в 2 раза в процессе заполнения внешней памяти информацией за счет освобождения канала ввода-вывода - от выполнения процедуры контрольного считывания. Кроме того, несколько сокра щается загрузка центрального процессора и упрощается операционная система в части организации контрольного считывания за счет возложения функций повторного считывания и сравнения контрольного символа на само устройство управления. ,

1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Локомотив, работающий под давлением продуктов горения и паром | 1925 |

|

SU5551A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для записи информации в накопителях на магнитных дисках | 1978 |

|

SU734801A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-11-07—Публикация

1982-11-04—Подача