Изобретение относится к технике . связи и может исполь зоваться для передачи дискретной информации по каналам связи.

Известен цифровой формирователь манипулированных сигналов, содержа- 5 щий два делителя 4acTOTisi, накапли ванадий сумматор, блок памяти, дешифратор, сумматор и |ияьтр нижних частот flj

Однако известный 1 ифррвс й (. 0 рователь имеет нйзкую точность п иформировании сигналов с мрогоподиционной амплитудой, ча.стотной и. фазоэой манипуляцией. . .

Цель изобретения - пов;ышение 15 точности при )Овании сигналов с многопозиционной амплитудной , частотной и фазовой манипулядией. Поставленная цель дрстигается тем, что в цифровой формиров.атель . тО манипулированных .сигналов, содержаЩИ.Й два делителя частоты, нак:апли- вающий сумматоЕ, блок памяти, дешифратор, ; сумматор и фильтр :нижш:х . частотf ввелены распределитель, циф- 25 роаналоговый прербразователь, триггер, элемент ;И и ко;де;р, выходу котррохчэ подключены к. информационньц входам накапливающего ;Сумматора, управлячодий вход которого соединен с входом триггера, с первьом входом элемента И и с выходом первого делителя час- .тоты, вх:ОД которого соединен с входом кодера и с выхрдом второго делителя, частоты, вход которого соединен с первш входом раясцредёлителя, вы- 35 ходы которого подключены к одним входам блока памяти, другие йходы и выходы которого соединен соответственно с выходами дешифратора и со йходами сумматора, выходы которого 40 через цифроамалоговый преоб.раэрватель подключены ко входам фильтра нижних частот, при этом выход триггера соединен со вторым входом элементами, выход которого подклю- 45 чен ко второму ВХОДУ распр(вдёлителя, и с первым входом Дешифратора, к второму входу.которого подклю-аен ВТОРОЙ выход триггера, а .выходы накапливающего сумматора сое динены с со- ел йтвётствующими входами. дешкФ)атора. .При этом дешифратор содержит два регистра и распр еделитель,. выходы которого подключены к одним входам , :регйстров, :выходы которых являются .выходами дешифратора, .выходами которого являются входы распределителя .и другие входы регистров.

Причем кодер содеян т три триггера г два сумматора по модулю два и два элемента И, при этом первый вы- 60 ход первого триггера подключен, к первому входу второго триггера, вторбй вяод которого соединен с вторым входом первого триггера, второй выход которого подключен к первому 65

входу первого сумматора по модулю два, вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом второго сумматора по модулю два первый вход которого соединен с выходом второго триггера и с первым входом третьего триггера, второй вход и выход которого соединены сооветственно с вторым входом второго триггера и с первьил в.ходом второго элемента и, второй вход и выход-которого соединены соответственно со вторым входом -первого элемента И и с вторым входом второго с;дау1атора по модулю два, причем выходы .сумматоров пс модулю два и вадхрд третьег триггера являются выхойадлй кодера, «входами которого являются.первые . ходы триггеЕрв и вторые рходы элементов И. г

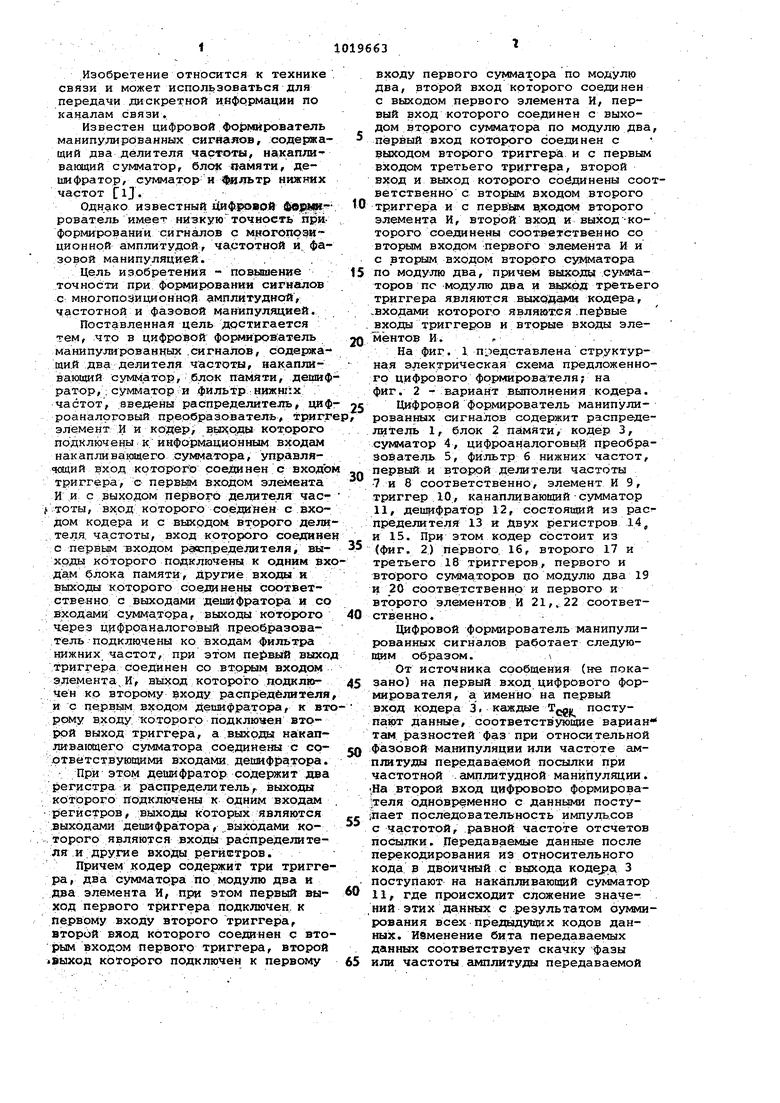

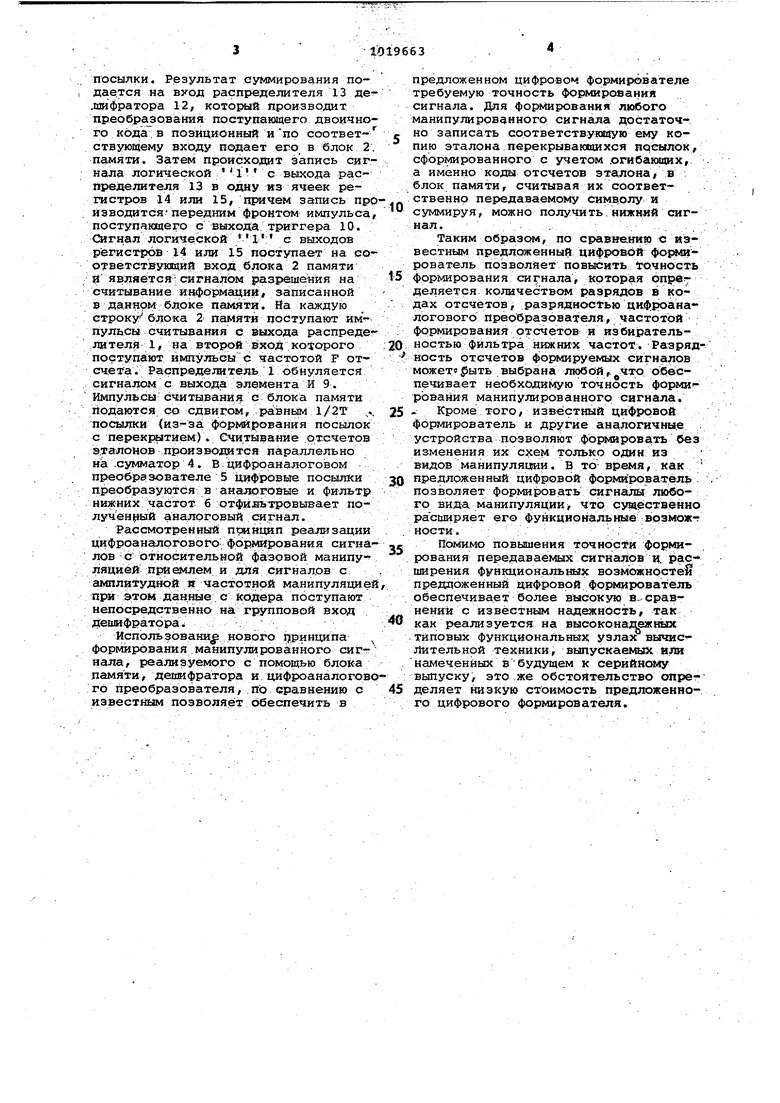

На фиг. 1 п едставлена структурная электрическая схема предложенного цифрового формирювателя; на фиг. 2 - вариант выполнения кодера.

Цифровой формирователь манипулированных сигналов содержит распределитель 1, блок 2 памяти, кодер 3, сумматор 4, цйфроаналоговый преобразователь 5, фильтр б нижних частот, первый и второй делители частоты 7 и 8 соответственно, элемент И 9, триггер . 10, канапливающийсумматор 11, дешифратор 12, состоящий из распределителя 13 и Двух регистров 14, и 15. При этом кодер состоит из (фиг. 2) первого 16, второго 17 и третьего 18 триггеров, первого и второго сумматоров по модулю два 19 и 20 соответственно и первого и второго элементов И 21,.22 соответственно.

Цифровой формирователь манипулнрованных сигналов работает следуюnwM о&раэом. ,

От источника сообщения (не показано) на первый вход цифрового формирователя, а именно на первый вход кодера 3. каждые TQgu поступают данные, соответствующие вариан там разностей Фаз при относительной ;фазовой манипуляции или частоте амплитуды передаваемой посылки при частотной .амплитудной манипуляции. vHa второй вход цифровосо формирова1теля одновременно с данными поступает последовательность импудь.сов с частотой, равной частоте отсчетов посылки. .Передаваемые данные после перекодирования из относительного кода в двоичный с выхода кодера 3 поступают на накапливающий сумматор 11, где происходит сложение значе,ний этих данных с .результатом оумлирования всех предыдутцих кодов данных, изменение бита передаваемых данных соответствует скачку фазы или частоты амплитуды передаваемой посылки. Результат cy миpoвaния подается на вход распределителя 13 дв .шифратора 12, который производит. пр.еобра зования поступающего двоично го кода. в позиционный и по соответствующему входу подает его в блок 2 памяти. Затем происходит запись сиг нала логической 1 с выхода распределителя 13 в одну из ячеек регистров 14 или 15, причем запись пр изводится- передним фронтом импульса поступающего с выхода, триггера 10. Сигнал логической с выходов регистров 14 или 15 поступает на ео ответстйуквдий вход б-пока 2 памяти 0 является-сигналом разрешения на считывание информации записанной в данном блоке памяти, йа каждую строку блока 2 памяти поступают импульсы считывания с выхода распреде лител 1, ia второй увходкоэ;орого поступают импульсыс частотой F от счета. Распределитель 1 обнуляется сигналом:с выхода-элемента И 9. Импульсысчитывания с блока памяти подакисся со сдвигом, .равным 1/2Т ,, ПОСЫЛКИ ( фьрми:рования посылок с перекрытием). Считызвание .отсчетов э.талонов п)ооизвозштса параллельно нЬ .сумматор 4. В цифЕ)оаналого вом преобразователе 5 1шфровые посылки преобразуются в аналоговые и фильтр нижних.частот 6 отфильтровывает получен ый аналоговый сигнал. Рассмотренный принцип реализации цифpoaн tлQГoвofOv Фррк рования сигна лов-С-относительной фазовой манипу ляцией -приемлем, и для сигналов с ампл|1тудной и частотной манипуляци е при атом д;ан.ные. с кодера поступают непосредственно на групповой вход дешифратора ; . Использование нового т ринципа формирования.манипулировйнного сигнала, реализуемого с помощью блока памяти, декифратора и цифроаналогов го преобразователя, по сравнению с известшам позволяет обеспечить в предложенном цифровом формирователе требуемую точность Формирования сигнала. Для формирования любого манипулированного сигнала достаточно записать соответствующую ему копию эталона перекрывающихся посылок, сформированного с учетом .огибакяцих,. а именно коды отсчетов зталона в . блок памяти, считывая их соответственно передаваемому символу и суммируя, можно получи ть.нижний сиг.нал. ..-... -. .. . . . Та:ким образом, по сравнению 5 известным предложенный цифрр вой формирователь позволяет повысить to.4HOCTb формирования сигнала, которая бпрвг деляется количестве разрядов в кодах отсчётов, разрядностью .на логового Преобразователя, частотой формирования отсчетов и из би|рательностью фильтра нижних частот. Разрядность отсчетов формируемых сигналов может5 ыть выбрана любой,, Что обе спечивает необходимую точность формирования манипулированного сигнала, . Кроме того, известный цифровой формирователь и другие ана:логичны.е . устройства позволяют фоЕФ1Ирова;ть без изменения их схем только один из видов манипуляиии. В то- , как предложенный цифровой формирователь позволяет фор1 мровать сигналы любого вида манипуляции что существенно рас1даряет его функциональные врзмож-г ности. ;. : . .;. Помимо повышения точности формирования передаваемых сигналов к. рас вшрения Фьгнкциойа-| ьных возможностей предложенными цифровой формирователь обеспечива.ет более высокую в.-сравнении с известным надикнОсть, так как реализуется на высоконадюжн ах Типовых функциональных узлах вычисйительной техники, выпускаеьеапс или намеченных вбудущем к серийному выпуску, это же обстоятельство опрег деляет низкую стоимость предложенного цифрового формирователя.

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи информации по электрическим сетям | 1984 |

|

SU1279076A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛАМ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1994 |

|

RU2079855C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1992 |

|

RU2047908C1 |

| ДИСКРЕТНЫЙ ФАЗОРАЗНОСТНЫЙ МАНИПУЛЯТОР | 2017 |

|

RU2666228C1 |

| ЦИФРОВАЯ СИСТЕМА РАДИОВЕЩАНИЯ | 1992 |

|

RU2048704C1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| СИСТЕМА ЦИФРОВОГО СТЕРЕОФОНИЧЕСКОГО РАДИОВЕЩАНИЯ | 1991 |

|

RU2019041C1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ РЕЧЕВЫХ СООБЩЕНИЙ | 1994 |

|

RU2085044C1 |

1. ЦИФРОВОЙ ФОРМИРОВАТЕЛЬ МАНИПУЛИРОВАНИКХ СИГНАЛОВ, содержащий два делителя частоты, накапливающий сумматор, блок памяти, дешифратор, сумматор и фильтр нижних частот, от л и ч а ю щ и йен тем, что с целью повышения точности при формировании сигналов с многопозиционной амплитудной, частотной и фазовой манипуляцией, введены распределитель, цифроаналоговый преобразователь, триггер, элемент Ии кодер, выходы которого подключены к информационным входам накапджвающего сумматора, управлякяций вход которого соединен с входом триггера, с первым входом элемента И и с вы.ходом первого делителя частоты, вход которого соединен с входом кодера и с выходом второго делителя частоты, вход которого соединен с первым входом распределителя, выходы которого подключены к одним входам . блока памяти, другие входы и выходы которого соединены соответственно с выходами дешифратора и со входами сумматора, выходы которого через цифроаналоговый преобразователь подключены ко входам фильтра нижних частот, при этом первый выход триггера соединен с вторым входом элемента И, выход которого подключен ко второму входу распределителя, и с первым входом деимфратора, к рому входу которого подключен второй выход триггера, а вьлходы накапливакнцего сумматора соединены с соответствуюазими входами деиифратора. 2.Устройство по П.1 ,о т л и 1 а ю щ е ее я тем, что деоифратср содержит два регистра н распределитель, выходы которого подключены к одним входам регистров , выходы которых являются выходами деаифратора, входами которого являются входф распределителя и другие входы регистров. 3.Устройство по п. 1, о т л и чающееся TeM,w что кодер б содержит три триггера, два сумматора по модулю два и два элемента И, при этом первый выход первого ригге ра подключен к первому входу второго триггера, второй вход которого соединен с вторым входом первого триггера, второй выход которого под ключен к первому входу первого сумматора по модулю два, второй вход которого -соединен с выходом первого элемента И, первый вход которого О соединен с выходом второго сумматора по модулю два, первый вход которого соединен с выходом второго о триггера и с первш 4 входом третьего :триггера, второй вход и выход которо го соединены соответственно с втоо: рым входом второго триггера и с перС вым входом второго элемента И, второй вход и выход которого соединены соответственно с вторым входом перя вого элемента И и с BTopt t входом второго cyi« 4aтора по моду;ш два, при чем выходы сумматоров по модулю два и выход третьего триггера являются выходами кодера, входами которого являются первые входы триггеров я вторые входы элементов И.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для цифро-аналогового формирования однополостных сигналов с амплитудно-фазовой модуляцией | 1976 |

|

SU653764A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1983-05-23—Публикация

1982-01-04—Подача