соединен с входом третьего счетчика, разрядные выходы реверсивного счетчика соединены с входами блока индикации и. с входами управляемого генератора импульсов соответственно, первые входы третьего и четвертого элементов И подключены к выходу элемента ИЛИ блока поиска свободных терминалов, выход 2k-ro элемента И первой группы которого соединен с нулевым входом k-ro триггера группы блока поиска свободных терминалов и с управляющим входом k-ro элемента И группы блока моделирования очереди, выходы вычитающих счетчиков которого подключены соответственно к единичным входам триггеров группы блока поиска свободных терминалов, единичные нулевые выходы триггеров группы которого соединены соответственно с инфомационными входами регистра сдвига, управлякиций вход которого подключен к выходу третьего элемента И, а группа разрядных выходов регистра сдвига соединена соответственно с входами элемента И блока моделирования очереди, управляющий вход элемента И которого соединен с выходом четвертого элемента И, группа выходов генератора произвольно распреЛеленных случайных чисел подключена соответственно к входам элементов И группы блка моделирования очереди, выход элемента ИЛИ которого соединен с входом третьего счётчйка и вторам входом третьего элемента ИЛИ бЯока управления, выход генератора импульсов которого соединен с вторым входом четвертого элемента И, третий вход которого подключен к нулевому выходу второго триггера блока управления, выход третьего элемента ИЛИ которого соединен с вторым входом третьего элемента ИЛИ, отличающеес я тем, что, с целью расширения функциональных возможностей путем моделирования мультипрограммных вычислительных процессов с шаговой адаптацией, оно дополнительно содержит приоритетный блок, блок сравнения и блок измерения времени ответа, приоритетный блок включает суммирующий счетчик интервалов, два элемента ИЛИ, четыре группы элементов И, п триггеров, единичный вход k-ro триггера соединен с выходом соответсвующего элемента И первой группы, первые входы зуэторых соединены с единичным входом первого триггера, а второй вход 1-го элемента И первой (1-1, п) группы соединен с единичным выходом 1-го триггера, нулевой

вход 1-го триггера соединен с выходом соответствующего элемента И второй группы, первые входы которых соединены с нулевым входом ir-ro триггера, а второй вход 1-го элемента И второй группы соединен с нулевым выходом (1+1)-го триггера, выходы триггеров соединены соответственно с первыми входами элементов И третьей группы, выходы которых подключены соответственно к входам первого элемента ИЛИ, единичные выходы триггеров соответственно соединены с первыми входами элементов И четвертой группы,.выходы которых соединены соответственно с входами второго элемента ИЛИ, выход которого подключен к входу суммирующего счетчика интервалов, блок измерения времени ответа включает первый и-ВТОРОЙ накапливающие сумматоры/ Генератор фиксированного числа импульсов, элемент И, элемент задержки и суммирующий счетчик, вход которого соединен с первьш входом элемента И и выходом элемента задержки, вход которого соединен с входом генератора фиксированного числа импульсов, выход которого соединен с входом сдвига первого сумматора, выход которого подключен к второму входу элемента И, выход которого соединен с суммирующим входом второго сумматора и с певым информационным входом блока сравнения соответст)аеннО, второй информационный вход которого является входом устройства, а управляющий вход подключен к выходу элемента задержки блока измерения времени ответа, вход элемента задержки блока измерения времени ответа соединен с выходом переполнения третьего счетчика,первый и второй выходы блока сравнения подключешл соответственно к единичному,входу первого триггера и нулевому входу п-го триггера приоритетного блока, вторые входы k-x элементов И третьей и четвертой группы которого подключены соответственно к. единичным выходам k-x триггеров группы блока поиска свободных терминалов и выходом . 2k-го элемента И первой группы блока пшска свободных терминалов,вторые входы элементов И второй группы которого соединены соответственно с нулевыми выходами триггеров приоритетного блока, выход первого элемента ИЛИ которого подключен к второму входу второго элемента И, выход п-го элемента И второй группы блока поиска свободных терминалов является дополнительным выходом устройства.

Изобретение относится к вычислительнЬй технике и может быть использовано для статистического моделирования широкого класса вычислительных систем, в частности для моделирования мультипрограммных ЭВМ, работающих в режиме разделения времени с шаговым алгоритмом адаптации.

Известны специализированные устройства для моделирования систем массового обслуживания и, в частности, для моделирования вычислительных систем fl .

Однако подобные устройства позволяют моделировать простейшие вычислительные системы,, работающие в одно программном режиме. Наиболее близким к предлагаемому является устройство для моделирования систем массового обслуживания, содержащее блок поиска свободных терминаловj блок моделирования очереди, блок синхронизации, управляемы регистр сдвига, блок индикации, суммирующие и реверсивный счетчики, генератор произвольно распределенных случайных чисел, элементы И, ИЛИ, геHeipaTop случайного noToka импульсов, выход которого соединен со счетным входом первого счетчика и с первым входом первого элемента И, второй вход которого соединен с первым выхо дом блока поиска свободных терминало вход которого объединен с выходом первого элемента И и подключен к первому входу второго элемента И, а его выход подключен к первому входу генератора произвольно распределенных случайных чисел, к входу второго счетчика и к сумйирующему входу реверсивного счетчика, вычитаквдий вход которого соединен .с входом третьего счетчика, разрядные выходы .сивйого счетчика соединены с зхояамк блока индикации и с входами управляемого генератора импульсов соответственно, первые входы третьег и. четвертого элементов И подключены к второму выходу блока поиска свобод ных терминалов, первая rpytina выходов которого соединена с первой группой входов блока моделирования .очереди соответственно, группа выходов которого соединена с группой входов блока поиска свободных терминалов соответственно, вторая группа выходов которого соединена с группой входов управляемого регистра сдвига соответственно, группа выходов которого соединена с второй группой входов блока моделирования очереди соответственно, третья группа входов

которого соединена с выходом генератора произвольно распределенных случайных чисел соответственно, первый и втррой выходы блока синхронизации соединены .соответственно с вторыми

входами третьего и четвертого элементов И, выходы которых соединены соответственно с входами управляемого регистра сдвига и блока моделирования очереди, выход которого соединен с вычитающим входом ревереив-. ного счетчика и с входом блока синхронизации, третий выход которого соединен с третьим входом четвертого элемента И f 2 J.

Известное устройство позволяет моделировать мультипрограммные вычислительные системы, работающие в пакетном режиме и в режиме разделения времени .Однако моделирование

ключатель, элемент задержки, три элемента ИЛИ, два триггера п пересчет ную схему, состоящую из двух счетчиков и элемента И, выход которого соединен с входом первого счетчи слительных систем, использующих шаговый алгоритм адаптации, невозможно с помощью известных устройств для моделирования . цель изобретения - расширение функциональных возможностей устройства путем моделирования мультипрограммных вычислительных процессов с шаговой адаптацией. Поставленная цель достигается тем, что в устройство, содержащее регистр сдвига, блок индикации, три счетчика, реверсивный счетчик, генератор произвольно распределенных случайных чисел, четыре элемента И, генератор случайного потока импульсов, блок поиска свободных терминалов, включающий группу из п триггеров, элемент ИЛИ, элемент И-НЕ, первую группу из 2п элементов И, вторую группу из 2п элементов И, нулевсй вход k-ro триггера группы (, п) подключен к первому входу (2k-l)-ro элемента И первой группы, единичный выход k-ro триггера группы соединен с первым входом 2k-го элемента И первой группы, вторые вхрды 2|-го и {2i-l)-ro элемента И первой группы (, п) объединены: и подключены к выходу (i-l)-ro элемента И второй группы, первый вход k-rp элемента И второй группы соединен с выходом {2k-1)-го элемента И. первой Группы, нулевые выходы триггеров подключе ны к вхсяам элемента И-НЕ и элемента ИЛИ соответственно, блок моделирования очереди, включающий элемент И, элемент ИЛИ,-группу вшчитакицих счетчиков и группу элементов И,. выхода которых подключены соответственно к разрядным входам вычитающих C4eTtmKOB группы, инфс«)мационные входы которых соединены соответстванно с выходами элемента И, выходы вычитающих счетчиков .группы подключены соответственно к входам элемента ИЛИ, блок управления, включакнций генератор импульсов, перека, выход генератора импульсов блок управления соединен через переключатель с первым входом элемента И и входом второго счетчика .пересчетной схемы, выход которого подключен к первому входу первого элемента ИЛИ блока управления и нулевому входу первого триггера, нулевой выход которого соединен с вторым входом элемента И пёресчетной схемы, выход первого счетчика пересчетной схемы подключен к первому входу второго элемента ИЛИ блока управления, единичному входу первого триггера, а через переключатель к первому входу третьего элемента ИЛИ, второй вход которого соединен с вторым входом .второго элемента ИЛИ, а через элемент задержки - с входом первого элемента ИЛИ, выход которог подключен к нулевому входу второго триггера, едй:ничный вход которого соединен с .выходом второго элемента ИЛИ, выход генератора случайного потока импульсов соединен с входом первого счетчика и с первым входом первого э.лемента И, второй вход котрого Соединен с в.ыходом элемента И-НЕ блока поиска свободных терминалов, выход первого элемента И подключен к первым входам первого и второго элементов И первой группы блока поиска свободных терминалов и к первому входу второго элемента И, выход которого подключен к входу генератора произвольно распределенных случайных чисел, к входу второго счетчика и к суммирующему входу реверсивного счетчика, вычитающий вход которого соединен с входом третьего счетчика, разрядные выходы реверсивного счетчика соединены с входа1 4и блока индикации и с входами управляемого генератора импульсов соответственно, первые входы третьего и четвертого элементов И подключены к выходу элемента ИЛИ блока поиска свободных терминалов, выход 2k-ro элемента И первой группы которого соединен с нулевым входом k-ro триггера группы блока поиска свободных терминалов и с управляккким входом k-ro элемента И группы, блока моделирования очереди, выходы вычитающих счетчиков которого подключены соответственно к единичным входам триггеров группы блока поиска сводных терминалов, единичные нулевые выходи триггеров групы которого соединены соответственн с информационными щходаык регистра сдвига, управляющий вход которого подключен к выходу третьего элемента И, а группа разрядных выходов регистра сдвига соединена соответственно с входа ми элемента И блока моделирования Очереди, управлянхоий вход элемента И которого соединен с входом четвертого элемента И, групп

выходов генератора произвольно распределенных случайных чисел подключена соответственно к входам элемен. тов И группы блока моделирования очереди, выход элемента ИЛИ которого

соединен с входом третьего счетчика и вторым входом третьего элемента ИЛИ блока управления, выход генератора импульсов которого соединен с вторым входом четвертого эле1«кнта И, третий

-J вход которого подключен к нулевому выходу второго триггера блока управления, выход третьего элемента ИЛИ которого соединен с вторым входом третьего элемента ИЛИ, дополнительно введены приоритетный блок, блок сравнения и блок измерения времени ответа, приоритетный блок включает суммирующий счетчик интервалов, два элемента ИЛИ, четыре группы элементов И, п триггеров, единичный вход

k-ro триггера соединен с выходом соответствующего элемента И первой группы, первые входы которых соединены с единичным входом первого триггера, а второй вход 1-го элемента И первой группы (, ) соединен с единичным выходом 1-го триггера, нулевой вход 1-го триггера соединен с выходом соответствующего элемента И второй группы, первые

0 входы которых соединены с нулевым входом п-го триггера, а второй вход 1-го элемента И второй группы соединен с нулевым выходом- (1+1)-го триггера, нулевые выходы триггеров

г соединены соответственно с первыми входами элементов И третьей группы, выходы которых подключены соответственно к входам первого элемента ИЛИ, единичные выходы триггеров соответственно соеяиненн с первыми входами элементов И четвертой группы, выходсл которых соединены соответственно с входами.второго элемента ИЛИ, выход которого подключен к входу суммирующего счетчика интервалов, блок иэме5 реЬия времени ответа включает первый и второй накапливающие сумматоры, генератор фиксированного числа импульсов, элемент И, элемент задержки и суммирующий счетчик, вход которого соединен с первым входом элемента и

и выходом элемента задержки, вход которого соединен с входом генератора фиксированного числа импульсов, выход которого соединен с входом сдвига первого сумматора, выход которого

подключен к второму входу элемента И, выход которого соединен с суммирующим входом второго сумматора и с первым информационным входом блока сравнения соответственно, второй- информационный вход которого является входом устройства, а управляющий вход подключен к выходу элемента задержки блока измерения времени ответа, вход элемента задержки блока измерения

времени ответа соединен с выходом

переполнения третьего счетчика, первый и второй выходы блока сравнения подключены соответственно к единичному входу первого триггера и нулевму входу п-го триггера приоритетного блока, вторые входы: k-x элементо И третьей и четвертой группы которого подключены соответственно .к единичным выходам k-x триггеров группы блока поиска свободных терминалов и выходом 2k-го элемента И первой группы блока поиска свободных терминалов, .вторые входы элементов И второй группы которого соединены соответственно с нулевыми выходами триггеров приоритетного блока, выход первого элемента ИЛИ которого подключён к второму входу второго элемента И, выход п-го элемента И второй группы блока доиска свобод.ных терминалов является дополнительным выходом устройства.

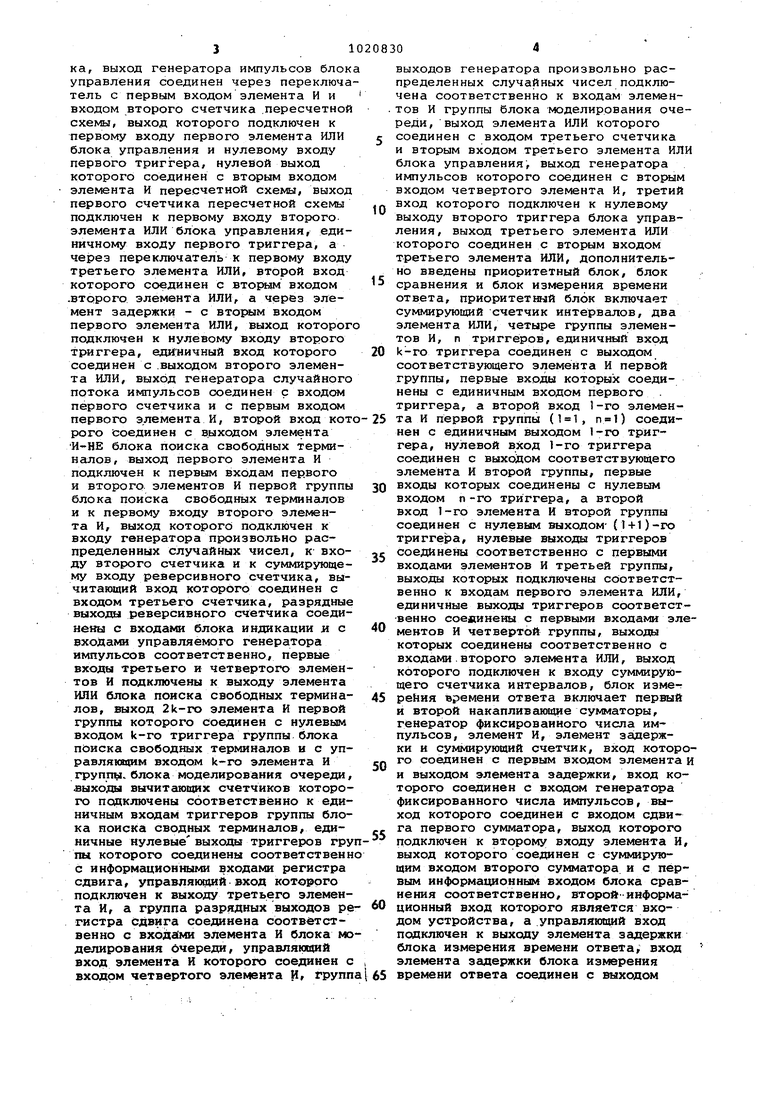

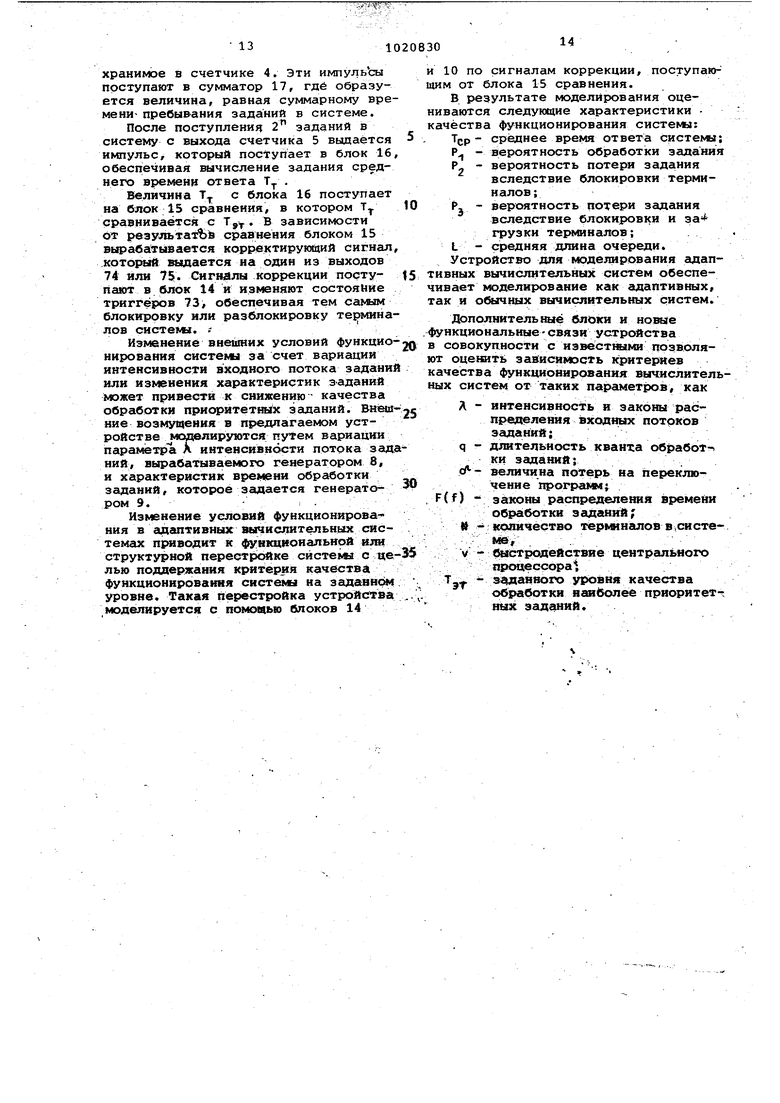

. На фиг. 1 приведена блок-схема устройства; на фиг. 2-6 - функциональные схемые блока поиска свободных терминалов, управляемого регист ра сдвига, блок;а моделирования очереди, блока управления приоритетного блока соответственно; на фиг. 7 - схема-пересчетноД схемы с изменяетФам коэффициентом пересчета блока управления.

Устройство содержит (фиг. 1) блок 1 статистической обработки, включающий в себя первый и второй счетчики 2 и 3, реверсивный счетчик 4, третий счетчик 5, блок 6 индикации длины очереди и управляемый генератор 7 импульсов, генератор 8 случайного потока импульсов, генераФор 9 произвольно распределенных случайных .чисел/ блок 10 поиска свободных терминалов, регистр 11 сдвига, блок 12 .моделирования очереди, блок 13 управления, приоритет-. ный блок 14, блок 15 сравнения, блок 16 измерения времени ответа, включающий первый и второй накапливйидие сумматоры 17 и 18, суммирующий счетчик 19, -генератор 20 фиксированного числа импульсов, элемент И 21 и элемент 22 задержки, первый, второй третий и четвертый элементы И 23-2б, вход 27 устройства.

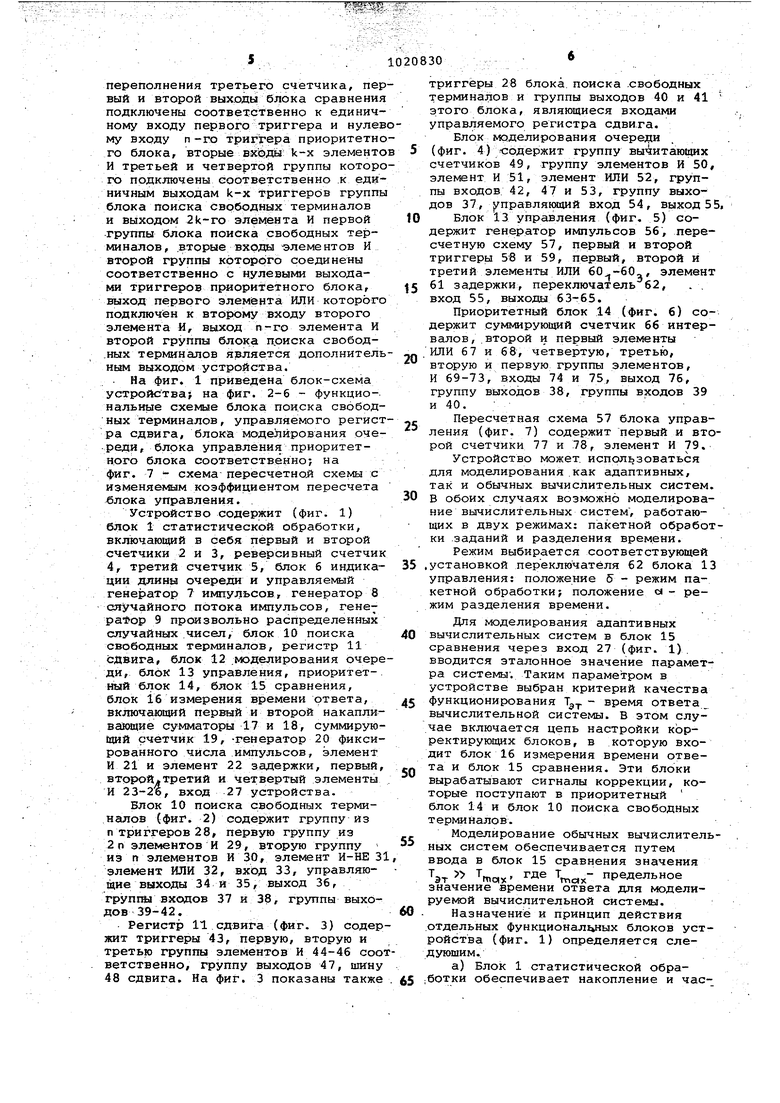

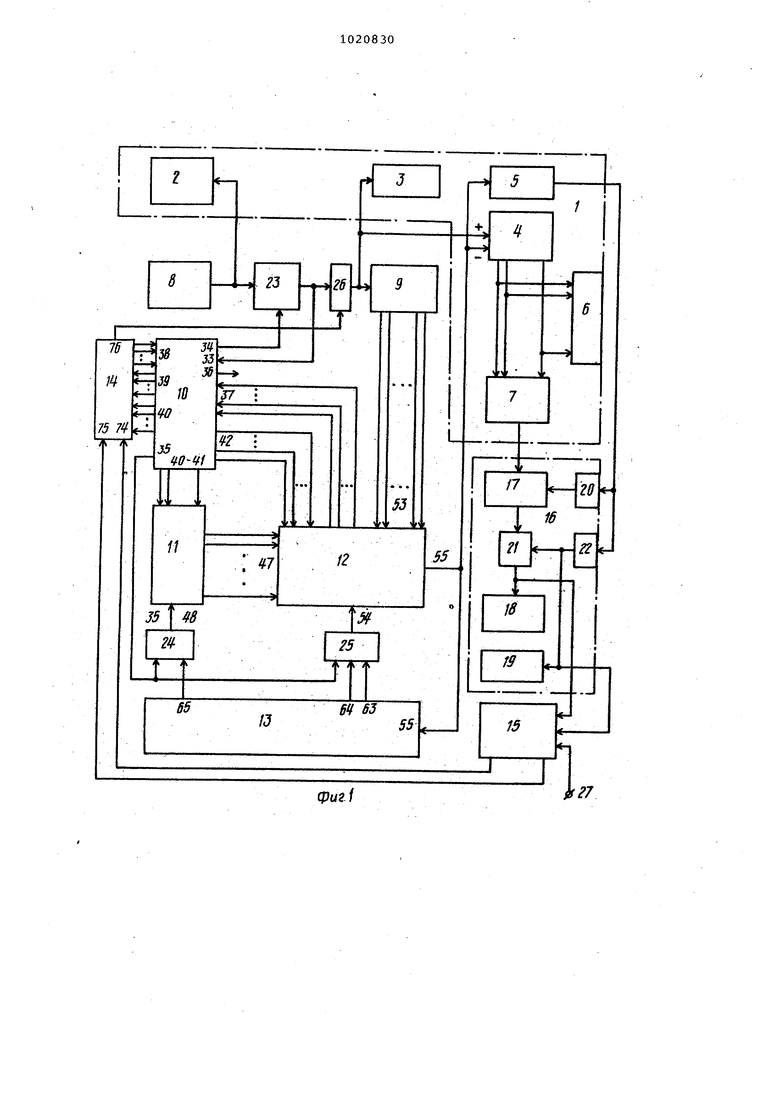

Блок 10 поиска свободных терминалов (фиг. 2) содержит группу из птриггеров 28, первую группу из 2 о элементов И 29, вторую группу из п элементов И 30, элемент И-НЕ 31 элемент ИЛИ 32, вход 33, управляющие выходы 34 и 35, выход 36, группы входов 37 и 38, группы выходов 39-42.

Регистр 11 сдвига (фиг. 3) содержит триггеры 43, первую, вторую и третью группы элементов И 44-46 соответственно, группу выходов 47, шину 48 сдвига. На фиг. 3 показаны также

триггеры 28 блока, поиска .свободных терминалов и группы выходов 40 и 41 этого блока, являющиеся входами управляемого регистра сдви.га.

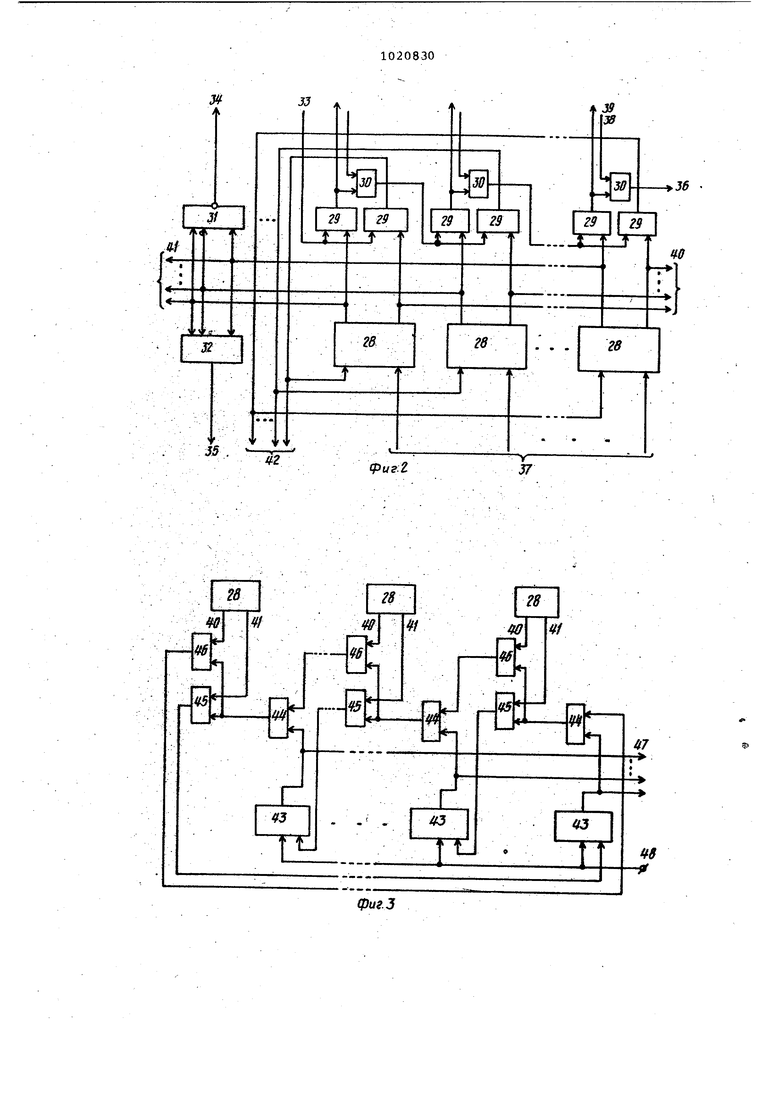

Блок моделирования oчepeJctи (фиг. 4) /содержит группу вычитающих счетчиков 49, группу элементов И 50, элемент И 51, элемент ИЛИ 52, группы входов 42, 47 и 53, группу выходов 37, управляющий вход 54, выход 5

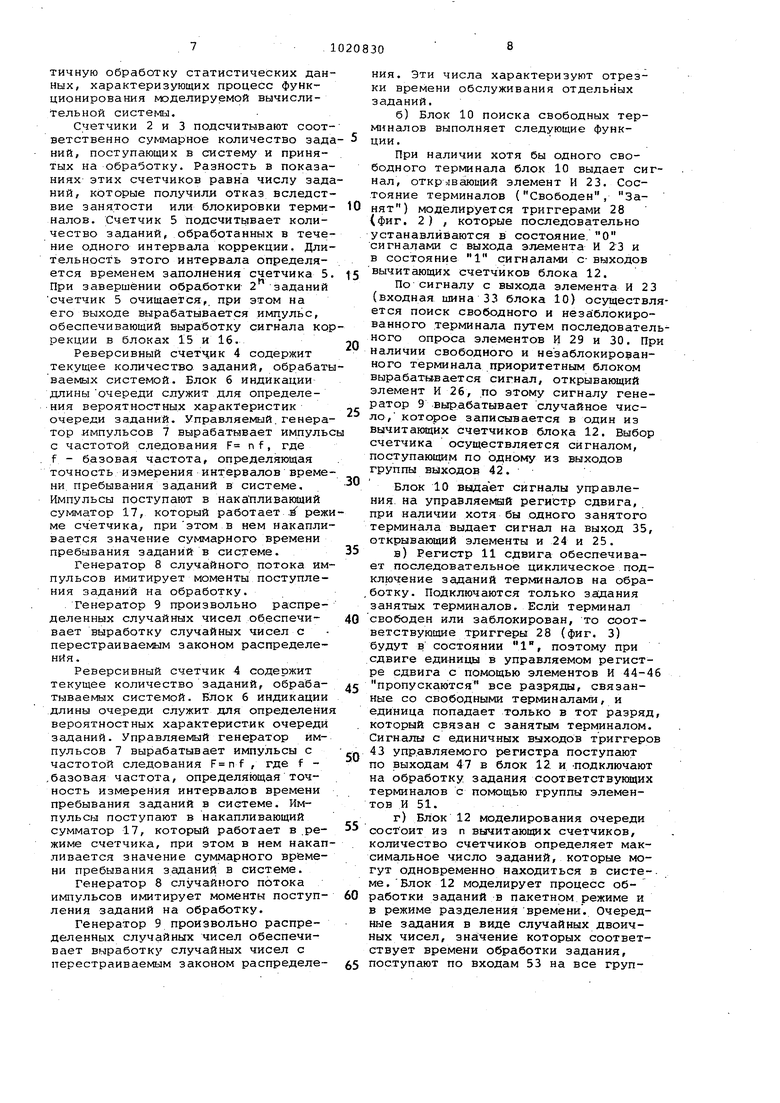

Блок 13 управления (фиг. 5) содержит генератор импульсов 56, пересчетную схему 57, первый и второй триггеры 58 и 59, первый, второй и третий элементы ИЛИ , элемент 61 задержки, переключатель 62, вход 55, выходы 63-65.

Приоритетный блок 14 (фиг. 6) содержит суммирующий счетчик 66 интервалов ,. второй и первый элементы .ИЛИ 67 и 68, четвертую, третью, вторую и первую группы элементов, И 69-73, входы 74 и 75, выход 76, группу выходов 38, группы входов 39 и 40.

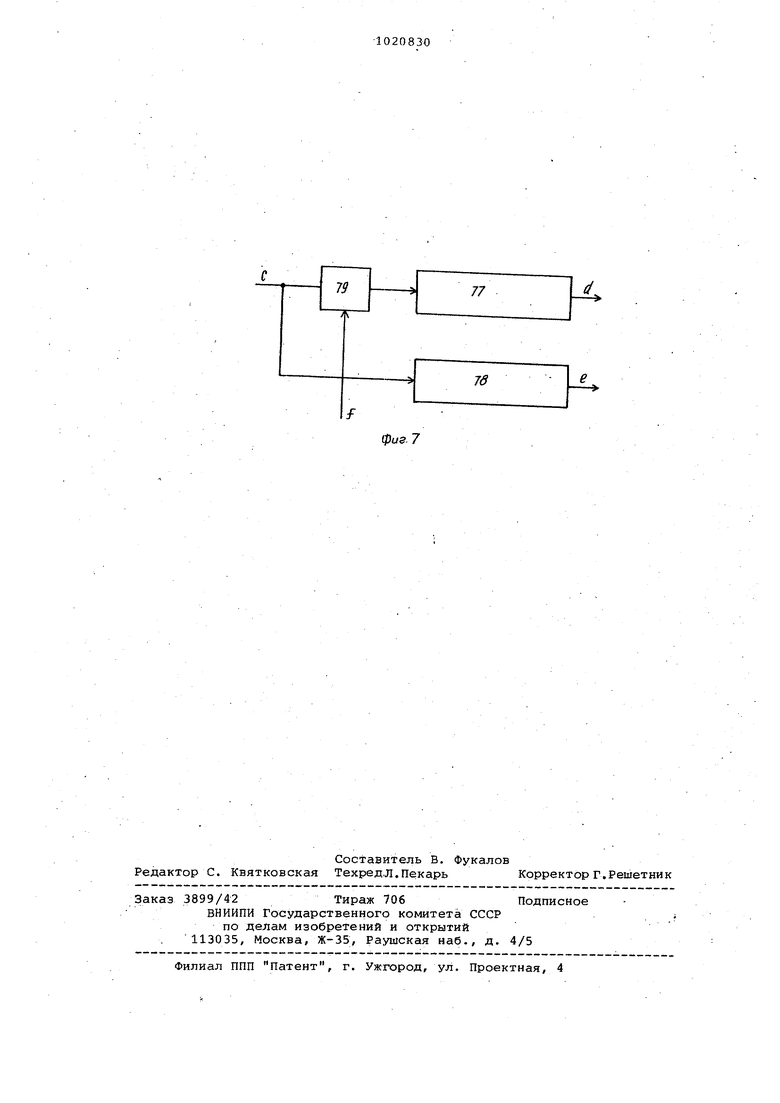

Пересчетная схема 57 блока управления (фиг. 7) содержит первый и второй счетчики 77 и 78, элемент И 79.

Устройство может, использоваться для моделирования.как адаптивных, так и обычных вычислительных систем. В обоих случаях возможно моделирование вычислительных систем , работающих в двух режимах: пакетной обработки .заданий и разделения времени.

Режим выбирается соответствующей .установкой переключателя 62 блока 1 управления: положение 5 - режим пакетной обработки; положение ci - режим разделения времени.

Для моделирования адаптивных вычислительных систем в блок 15 сравнения через вход 27 (фиг. 1). вводится эталонное значение параметра системы; Таким параметром в устройстве выбран критерий качества функционирования Т - время ответа вычислительной системы. В этом случае включается цепь настройки корректирующих блоков, в которую входит блок 16 измерения времени ответа и блок 15 сравнения. Эти блоки вырабатывают сигналы коррекции, которые поступают в приоритетный блок 14 и блок 10 поиска свободных терминалов.

Моделирование обычных вычислительных систем обеспечивается путем ввода в блок 15 сравнения значения

эт тах- Д предельное значение времени ответа для моделируемой вычислительной системы.

Назначение и принцип действия .отдельных функционал1 ных блоков устройства (фиг. 1) определяется слеД5ЮШИМ.

а) Блок 1 статистической обра;ботки обеспечивает накопление и частичную обработку статистических данных, характеризующих процесс функционирования моделируемой вычислительной системы.

Счетчики 2 и 3 подсчитывают соответственно суммарное количество зада НИИ, поступающих в систему и принятых на обработку. Разность в показаниях этих счетчиков равна числу заданий, которые получили отказ вследствие занятости или блокировки терминалов. Счетчик 5 подсчитывает количество заданий, обработанных в течение одного интервала коррекции, Длительность этого интервала определяется временем заполнения счетчика 5 При завершении обработки 2 заданий счетчик 5 очищается, при этом на его выходе вырабатывается , обеспечивающий выработку сигнала коррекции в блоках 15 и 16.

Реверсивный счетч.ик 4 содержит текущее количество заданий, обрабатываемых системой. Блок б индикации длиныочереди служит для определения вероятностных характеристик очереди заданий. Управляемый, генератор импульсов 7 вырабатывает импульс с частотой следования F пf, где f - базовая частота, определяющая точность измерения интервалов времени, пребывания заданий в системе. Импульсы поступают в накапливающий сумматор 17, который работает .и режиме счетчика/ приэтом в нем накапливается значение суммарного времени пребывания заданий в системе.

Генератор 8 случайного потока импульсов имитирует моменты поступления заданий на обработку.

Генератор 9 произвольно распределенных случайных чисел обеспечивает выработку случайных чисел с перестраиваемым законом распределения.

Реверсивный счетчик 4 содержит текущее количество заданий, обрабатываемых системой. Блок 6 индикации длины очереди служит для определения вероятностных характеристик очереди заданий. Управляемый генератор импульсов 7 вырабатывает импульсы с частотой следования , где f .базовая частота, определяющая точность измерения интервалов времени пребывания заданий в системе. Импульсы поступают в накапливающий сумматор 17, который работает в .режиме счетчика, при этом в нем накапливается значение суммарного времени пребывания заданий в системе.

Генератор 8 случайного потока импульсов имитирует моменты поступления заданий на обработку.

Генератор 9 произвольно распределенных случайных чисел обеспечивает выработку случайных чисел с перестраиваемым законом распределения. Эти числа характеризуют отрезки времени обслуживания отдельных заданий.

б)Блок 10 поиска свободных терминалов выполняет следующие функции.

При наличии хотя бы одного свободного терминала блок 10 выдает сигнал, откр,ваютий элемент И 23. Состояние терминалов (Свободен, Занят) моделируется триггерами 28 (фиг. 2 ) , которые последовательно

устанавливаются в состояние, О сигналами с выхода элемента И 23 и в состояние 1 сигналами с- выходов вычитающих счетчиков блока 12.

По сигналу с выхода элемента И 23 (входная шина 33 блока 10) осуществлется поиск свободного и незаблокированнрго .терминала путем последователного опроса элементов И 29 и 30. Пр наличии свободного и незаблокированного терминала приоритетным блоком вырабатывается сигнал, открывающий элемент И 26, по этому сигналу генератор 9 вырабатывает случайное число, которое записывается в один из вычитающих счетчиков блока 12. Выбор счетчика осуществляется сигналом, поступающим по одному из выходов группы выходов 42.

Блок 10 вьйает сигналы управления, на управляемый регистр сдвига, при наличии хотя бы одного занятого терминала выдает сигнал на выход 35, открывающий элементы и 24 и 25.

в)Регистр 11 сдвига обеспечивает последовательное циклическое подключение заданий терминалов на обра,ботку. Подключаются только задания занятых терминалов. Если терминал свободен или заблокирован, то соответствующие триггеры 28 (фиг. 3) будут в состоянии 1, поэтому при сдвиге единицы в управляемом регистре сдвига с помощью элементов И 44-4 пропускаются все разряды, связанные со свободными терминалами, и единица попадает Только в тот разряд который связан с занятым тер1 шналом. Сигналы с единичных выходов триггеро 43 управляемого регистра поступают по выходам 47 в блок 12 и -подключают на обработку задания соответствукяцих терминалов с помощью группы элементов И 51.

г)Блок 12 моделирования очереди состоит из п вычитающих счетчиков, количество счетчиков определяет максимальное число заданий, которые могут одновременно находиться в системе.Блок 12 моделирует процесс обработки заданий в пакетном режиме и

в режиме разделения времени. Очередные задания в виде случайных двоичных чисел, зна:чение которых соответствует времени обработки задания, поступают по входам 53 на все группы элементов И 50 (фиг. 4) . Одна из групп элементов И. 50 открывается сигналом, поступающим из блока 10 по одному из входов 42, и число записывается в соответствующий счетчик. Вычитающие входы счетчиков через элементИ 51, управляемый сигналами, поступающими по входам 47 из блока 11 (фиг. 1), соединены с входом 54. На этот вход из блока 13через элемент И 25 поступают пачки импульсов, имитирующих кванты обслуживания.

Счетчики 49 содержат текущее значение оставшегося времени обработки задания. Когда обработка одного из заданий завершается, то соответствующий- счетчик 49 переходит в нулевое состояние, при этом на его выходе появляется импульс. Этот импульс выполняет следующее: по одному из выходов 37. поступает в блок 10 (фиг. 1) и устанавливает соответст|вующий триггер 28 (фиг. 2) в нулевое состояние; через элемент ИЛИ 52 постпает на выход 55 и далее на вычитающий вход реверсивного счетчика 4 и нвход счетчика 5j с 55 импульс поступает в блок 13 управления, прекращая поступление импульсов обслуживания в блок. 12. .

д) Блок управления 13 (фиг. 1} выдает на блок 12 моделирования очереди пачки импульсов: количество импульсов в пачках соответствует величине квантов обслуживания, последовательно выделяеьФлх для обработки зада НИИ в режиме разделения времени. Интервалы между пачками моделируют временные потери на переключение программ. При работе в пакетном режиме блок вьщает непрерывную последовательность импульсов на выход 64 и далее на один из входов элемента И 25.

Выбор режимов (разделение времени пакетный) осуществляется переключателем 62. Длительность кванта q и в{5еменные потери на переключение программ сЛ задаются с помощью пересчетной схемы 57.

Пересчетная схема 57 (фиг. 5) содержит счетчики 77 и 78, элемент И 79. Коэффициент пересчета К сЧетчика 77 задает величину q, а коэффициент пересчета К счетчика 78 определяет величину . Триггер 59 блока управления вырабатывает сигнал разрешающий выдачу импульсов обслуживания через элемент И 25 в блок 12. Триггер 59 устанавливается в состояние О, запрещая вьщачу импульсов .в течение интервалов сЛ при работе в режиме разделения времени и на время переходных процессов при смене заданий. Это время определяется задержкой импульса, поступающего на вход 55 в элементе 61 задержки.

е) Приоритетный блок 14 совместно с блоком поиска свободных терминалов выполняет функции корректирующего блока при моделировании адаптивных вычислительных систем.

В процессе адаптивной настройки систе1 ш на -заданное значение качества обслуживания приоритетнызс заданий корректируется структура моделируемой вычислительной системы. Сущность корректировки заключается в том, что число терминалов, имеющих доступ к системе,изменяется в зависимости от. текущегсэ значения критерия качества обслуживания приоритетных.заданий Уровень приоритета определяется номером терминала, наивысшим приоритетом обладают задания, поступающие в систему с терминала с наибольшим .номером. .

Если текущее значение качества обработки заявок Т, замеренное в очередном интервале коррекции, больше заданного Т 7эт ° блока 15 сравнения в при орите т ныйблок 14 (фиг. 1) поступает одиночный импульс по входу 74 на регистр 73 (фиг. 6). При этом ойин из триггеров регистра с наименьшим номером будет установлен в состояние 1 и соответствующий терминал будет заблокирован, т.е. менее приоритетные- заявки с этого терминала в систему посjTynaTb на будут. В очередном йнтервале коррекции вновь пюжет быть ., поэтому с блока 14 опять будет выдан импульс и.следующий старший триггер приоритетного регистра будет установлен в состояние 1 и связанный с ним терминал окажется заблокированным. Этот процесс пошаговой блокировки терминалов с низшими приоритетами будет продолжаться до тех пор, пока .. При условии блока 14 сравнения вырабатывает импульс, поступающий на вход 75 при этом будет разблокирован наиболее приоритетный из заблокированных терминалов.

Количество терминалов, имеющих доступ к системе, будет автоматически поддерживаться таким образом, чтобы обеспечить качество обслуживания заданий, поступающих с теримналов с более высоким приоритетам, на уровне . На входы 39 приоритетного блока поступают импульсы неудовлетворенных запросов на терминалы вследствие их блокировки. Эти импульсы по.ступают через соответствующий элемент И 69 и ИЛИ 67 и подсчитываются суммирующим счетчиком 66, в котором накапливается суммарное число заданий, необслуженных вследствие блокировки.

Элементы И 70 и ИЛИ 68, на которые поступают сигналы с единичных выходов триггеров блоков 10 и 14, обеспечивают выработку сигнала Есть свобод ные и незаблокированные терминалы Этот сигнал поступает на выход 76, обеспечивая доступ заданий в систем путем открытия элемента И 26. Блок измерения времени ответа служит для оценки текущих значений критерия качества Т. Оценка осуществляется в течение интервала коррекции, длительность которого определяется временем заполнения счетчика 5 (фиг. 1) . Б нем подсчитывается количество обслуженных заявок Если счетчик 5 содержит п разрядов то после поступления 2 заявок он устанавливается в состояние О,а на его выходе появляется импульс, который подается на генератор 20 фиксированного числа импульсов и на элемент 22 задержки. Генератор 20 вырабатывает п сдвигающих импульсов, которые посту пают в накапливающий сумматор 17 и обеспечивают сдвиг содержимого сумматора на п разрядов вправо. Так как в. сумматоре 17 в течение интервала коррекции накапливается суммарное время ответа 2 заданий в системе, то после сдвига на п разрядов вправо содержимое сумматора 1 делится на 2, в результате после сдвига сумматора 17 будет содержать среднее значение времени ответа Т Полученное значение Т j. импульсом с выхода элемента 22 задержки через элемент И 21 перепишется в накаплив ющий сумматор 18, где. накапливается сумма величин Jf i 1, 2 .. .К, К число интервалов коррекции за время моделирования, а также в блок 15 ср нения. В блоке 15 сравнения значени Т сравнивается с эталонным Т 37 пр этом вырабатывается импульс коррекции, который поступает на один из выходов 74 и 75.. Если Т Тз-г то корректирующий импульс выдается на выход 74, при условии импульс поступает на выход 75. При моделировании вычислительных систем без адаптации в блок 15 вводится (T,- предельное значение времени ответа для моделируемой системы), поэтому в каждом интервале коррекции блоком 15 будет выдаваться импульс на выход 7 поэтому все триггеры блока 14 будут в состоянии О, терминалы в этом случае не блокируются. При моделировании адаптивных вычислительных систем устройство рабо тает следующим образом. В блок 15 сравнения (фиг. 1) вводится эталонное значение критерия TjY Импульсы с выхода генерато ра. 8 подсчитываются счетчиком 2 и поступают на элемент И 23. Если в системе имеется хотя бы один свобод ный терминал, то на управляющий вход И 23 с выхода 34 блока 10 будет подан разрешающий сигнал и импульс опроса с выхода И 23 поступает по входу 33 в блок 10. Этот импульс опрашивает цепочку элементов И 29 и И 30 и при наличии свободного и незаблокированного терминала подается на один из выходов 42, разрешая запись случайного числа с генератора 9 в один из счетчиков 49. Генератор 9 вырабатывает случайное число только при наличии свободного и незаблокированного терминала, эти условия контролируются элементами И 70 и ИЛИ 68, на выходе которых при соблюдении указанных условий будет разрешанвдий сигнал, открывающий элемент И 26. Счетчик 3 подсчитывает число заданий, поступивших в систему, в счётчике 4 хранится текущее число заданий в системе. Задания, по мере их поступления, заполняют счетчики 49. Обработка заданий моделируется путем выработки импульсов обслуживания, поступающих с блока 13 управления в блок 12 моделирования очереди. Порядок поступления этих импульсов регулируется элементом И 25. в зависимости от положения переключателя 62 в блоке 13 обработка задани.й производится квантами или непрерывно до завершения обработки. В первом случае моделируется режим разделения времени, во втором - пакетная обработка. Элемент И 25 управляется разрешающими сигналами, поступающими с блока 10 по выходу 35 и с блока 13 по выходу 63. Переход от обработки одного задания к обработке очередного осуществляется по сигналу, выдаваемому на выход 65 блока 13. По этому сигналу сдвигается 1 в регистре 11, при этом открывается очередной элемент И 51 и новая пачка импульсов выдается через открытый элемент И 51на следующий счетчик 49. При завершении обработки задания соответствующий счетчик 49 устанавливается в состояние О, на его выходе появляется импульс, которыйпо выходу 55 поступает в блок 13, прерывая, на время переходных процессов (это время определяется задержкой в элементе 61 блока 13) поступление импульсов в блок 12. Импульс завершения обработки задания поступает также на счетчики 4 и 5. Текущее значение длины очереди заданий, находящихся в системе со счетчика 4, подается в блокиндикации очереди и в управляемый генератор 7, который вырабатывает импульсы с частотой следования F п f , где f - базовая частота генератора; п - число xpaHMh4oe в счетчике 4. Эти импульЪы поступают в сумматор 17, где образуется величина, равная суммарному вре мени- пребывания заданий в системе. После поступления 2 заданий в систему с выхода счетчика 5 выдаётся импульс, который поступает в блок 16 обеспечивая вычисление задания среднего вреАюни ответа Т . Величина Т с блока 16 поступает на блок 15 сравнения, в котором Т сравнивается с . В зависимости (эт результат } сравнения блоком 15 выраба тывается корректирующий сигнал который выдается на ояин из выходов 74 или 75. Сигналы коррекции поступают в блок 14 и изменяют состояние триггеров 73, обеспечивая тем самым блокировку или разблокировку теркотна лов системы. ; Изменение внешних условий функцио нирования системы за счет вариации интенсивности входного потока задани или изменения характеристик з аданий южeт привести к снижению качества обработки приоритетны х заданий. ние возмущения в предлагаемом устройстве моделируются путем вариации параметра X интенсивн х;ти потока зад ний, вырабатываемого генератором 8, и характеристик времени обработки заданий, которое задается генератором 9. I . Изменение условий функционирова-ния в адаптивных вычислительных системах приводит к фувкцноиальирй или структурной перестр)Ойке системы с цв лью поддержания качества функционироваиия системы на заданном уровне. Такая перестройка устройства моделируется с помощью блоков 14 0 по сигналам коррекции, поступаюот блока 15 сравнения. В результате моделирования оцеаются следующие характеристики ества функционирования система: TCP- среднее время ответа систе1«1; Р - вероятность обработки задания Р - вероятность потери задания вследствие блокировки терминалов;Р, - вероятность потери задания вследствие блокировки и за грузки терминалов; L - средняя длина очер(5ди. Устройство для моделирования адапных вычислительных систем обеспеает моделирование как адаптивных, и обычных вычислительных систем. Дополнительшде бльки и новые кциональные-связи устройства овокупности с изве:стшми позволяоценить зависимость критериев ества функционирования вычислительсистем от таких параметров, как А - интенсивность и законы распределения входных потоков заданий; q - длительность кваита обработки заданий; сЛ - величина потерь на переключение программ; f) 3 аконы распределе ния времени обработки задгший; W - кояичество терминалов в,систе JuJUBt- - - --,. РЮ f - , ,. V - С стропействие центрального процессора ; зад1анного уровня качества обработки наиболее приоритет ных задгший.

#1

т

.4

ifl

41

т

US

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования адаптивных вычислительных систем | 1987 |

|

SU1441416A2 |

| Устройство для моделирования вычислительной системы | 1990 |

|

SU1786492A1 |

| Устройство для моделирования систем массового обслуживания | 1980 |

|

SU922756A1 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1783539A1 |

| Устройство для моделирования систем массового обслуживания | 1982 |

|

SU1067508A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1532943A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1545226A1 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1612311A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1319043A1 |

| Устройство для моделирования систем передачи и обработки информации | 1986 |

|

SU1392573A1 |

УСТРОЙСТВО ДЛЯ ЬЮДЕЛЙРОВА«ЙЯ АДАПТИВНЫХВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ,: содержащее регистр сдвига, блок индикации , три счетчика, реверсивный счетчик, генератор произвольно расПЕхеделенгшх случайных чисел, четы рё элемента И, генератор случайного notOKa импульсЬВг блок поиска свобод Них TepNMHatnoB, включающий группу из п-триггеров, элемент ИЛИ, элемент И-НЕ;, iIepiвyю группу из,: 2п элементов И, вторую згруппу. из, 2п элементов И, ну левой В1ыход k-го триггера группы , - подключен к первому йходу Ч )-го элемента И гтервой группы, единичный выход k-го триггера группы соединен с пе |вымвх зд6м 2k-го элеMesHta И первой группы, вторые входы 21-го и С ii -1)-гр элемвнта И первой группы {.-2, п) объединены и подключены к выходу ( r-V)-ro элемента И второй группы, первый 1вход k-ro элемента И второй группы соединен с вькодом ( )-rp элемента И первой группы, нулевые выходы триггеров подключеад к входам элемента И-НЕ и элемента: ИЛИ соответственно, блок моделирования оч1ереди, включакидай элемент И, элемент ИЗ|Иг группу вычиташцих счетчиков и группу элемен- . тов И, йыхсды которых подключены соответственно к разрядным входам Вычитающих счетчиков группы, информационные входы которых соединены соот ветственно с выходами элемента И, выходы вычитшощих счетчиков группы подключены с ответственнр к входам элемента ИЛИ, блок управления, включанндий генератор импульсов, переключатель, элемент задержки, три элемента ИЛИJ, два триггера и пересчетйую схему, состоящую из счетчиков и элемента И, выход которого соединен с входом первого счетчика, выход генератора импульсов блока управления соединен через переключатель с первым входом элемента И -и входом второго счетчика пересчетной : схемы, выход которого подключен к первому входу первого элемента РШИ блока управления и нулевс |у входу первого триггера, нулевой выход которого соедияен с вторым входом элемента И пересчетной схекял, выход пер во го счетчика пересчетнрй схеш подключен к первому вкопу вторрго элемента :ИЛИ блока управления, единичному входу первого триггера, a через пе:реключатель к перовому входу-третьего элемента ИЛИ, второй вход которого соединен с вторим входом второго элемента ИЛИ,a через элемент задержки - с вторым входом первого элемента ИЛИ, выход которого подключен к нулевому входу второго триггера, единичный вход которого соединен с выходом BTOJXDго элеме|1Тa ИЛИ, выход генератора случайногр потока импульсов срединен с входом первого счетчика и с первым входом первого элемента И, второй ВхОД которого coej QiHeH с выходом элемента Й-НЕ блока поиска свободных терминалов, выход первого элемента И подключен к первым входам первого и второго элементов И первой группы блока поиска свободных терминалов и к первому входу второго элемента И, выход которого подключен к Bxoft генератора произвольно распределенных случайных чисел, к входу второго счетчика и к суммирующему входу реверсивного счетчика, вычитающий вход которого

42

53

473I-1

57

фагМ

SS W S2

55

77

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Авторское свидетельство СССР по заявке 2905351/24, кл | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1983-05-30—Публикация

1981-12-22—Подача