Изобретение относится к устройствам имитационного моделирования и может найти применение для анализа и синтеза эргатических систем. Целью изобретения является расширение функциональных возможностей устройства за счет моделирования обслуживания наиболее срочных сообщений, а также обнаружения и исправления ошибок, допущенных при выполнении алгоритмов деятельности.

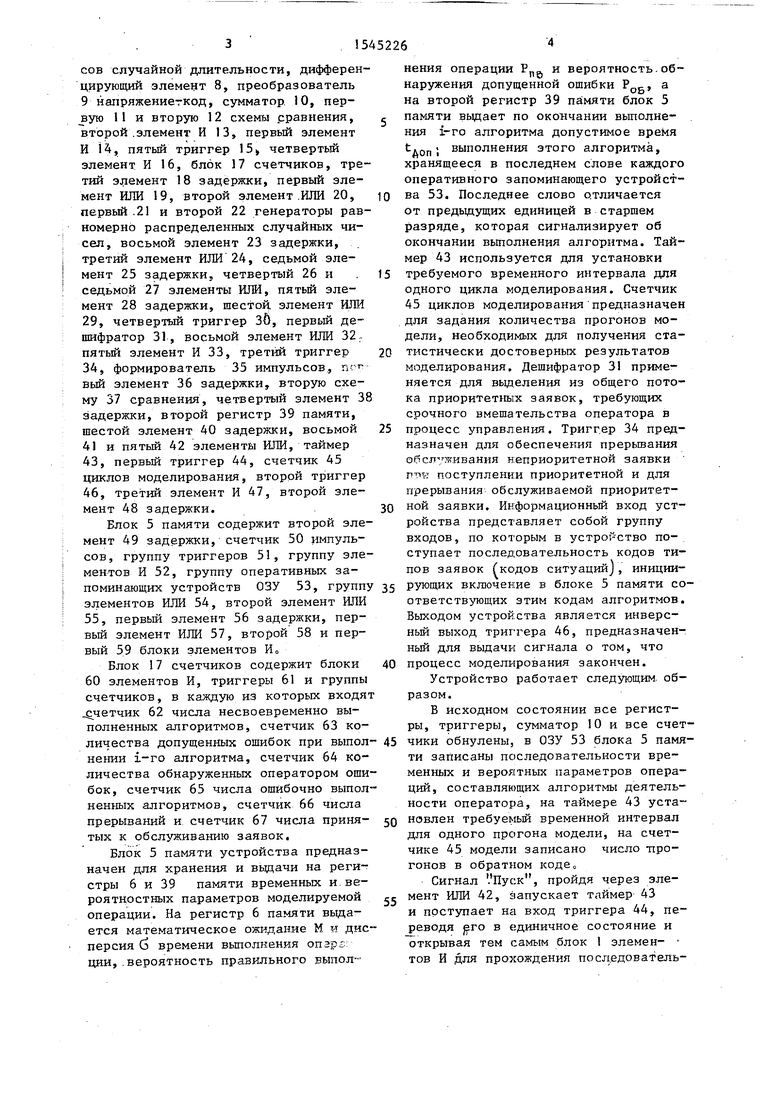

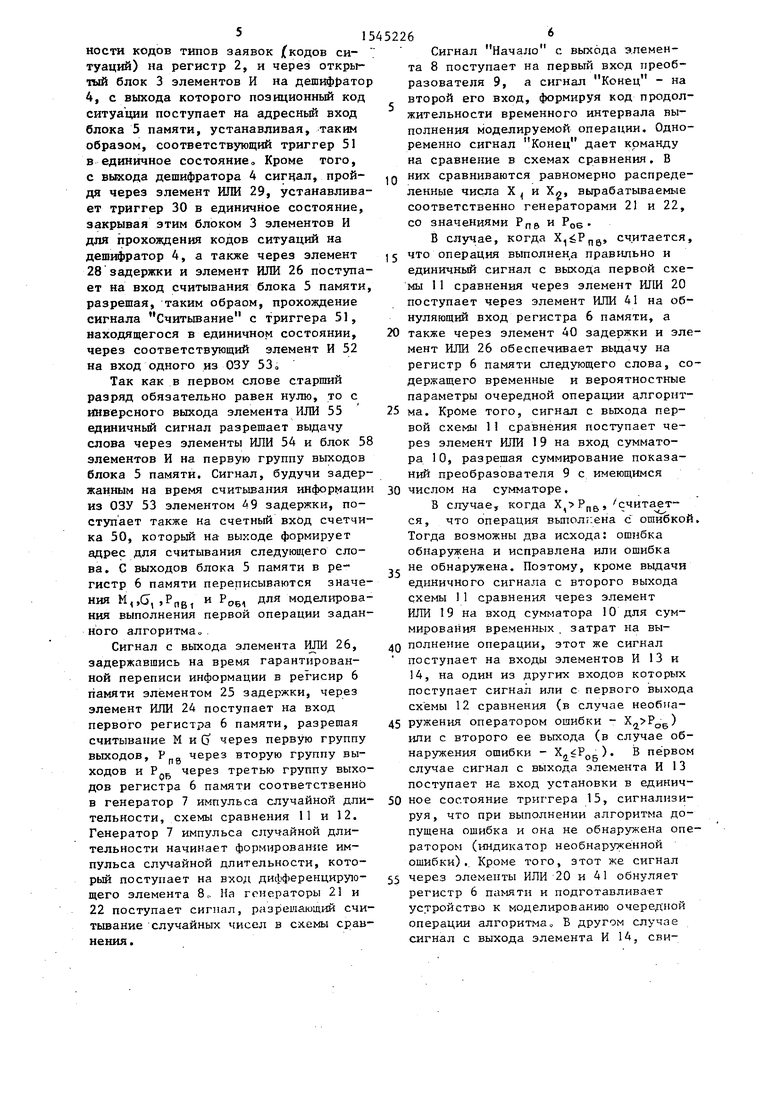

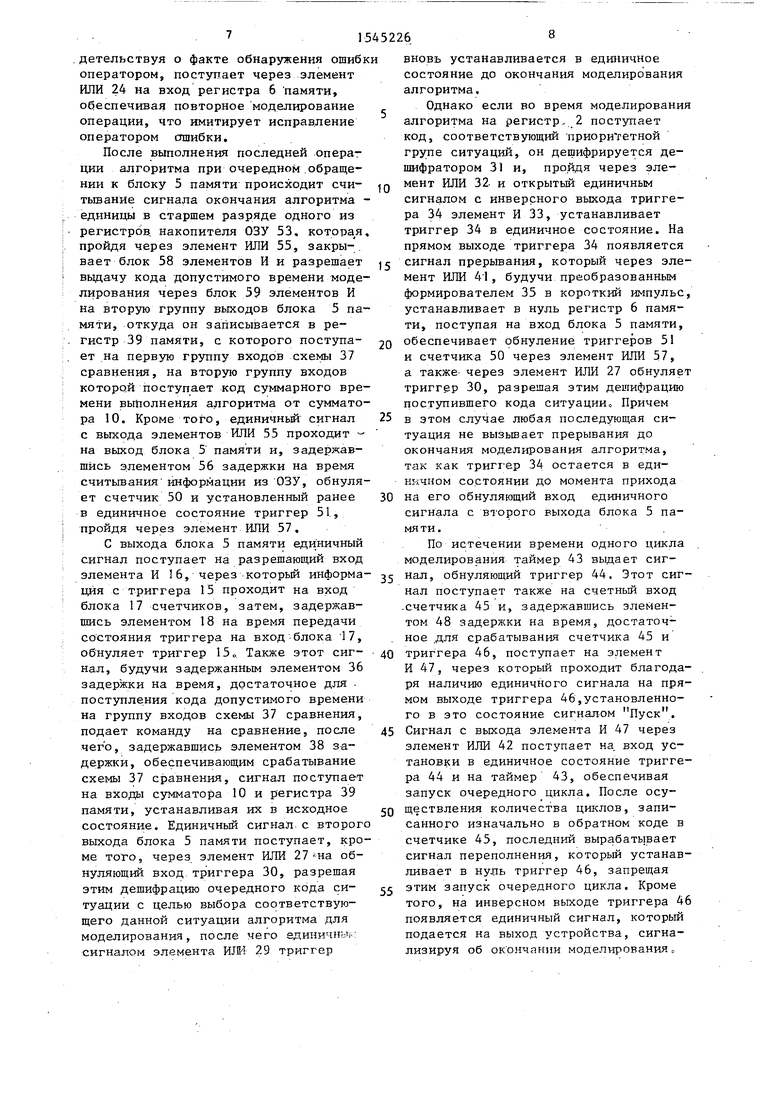

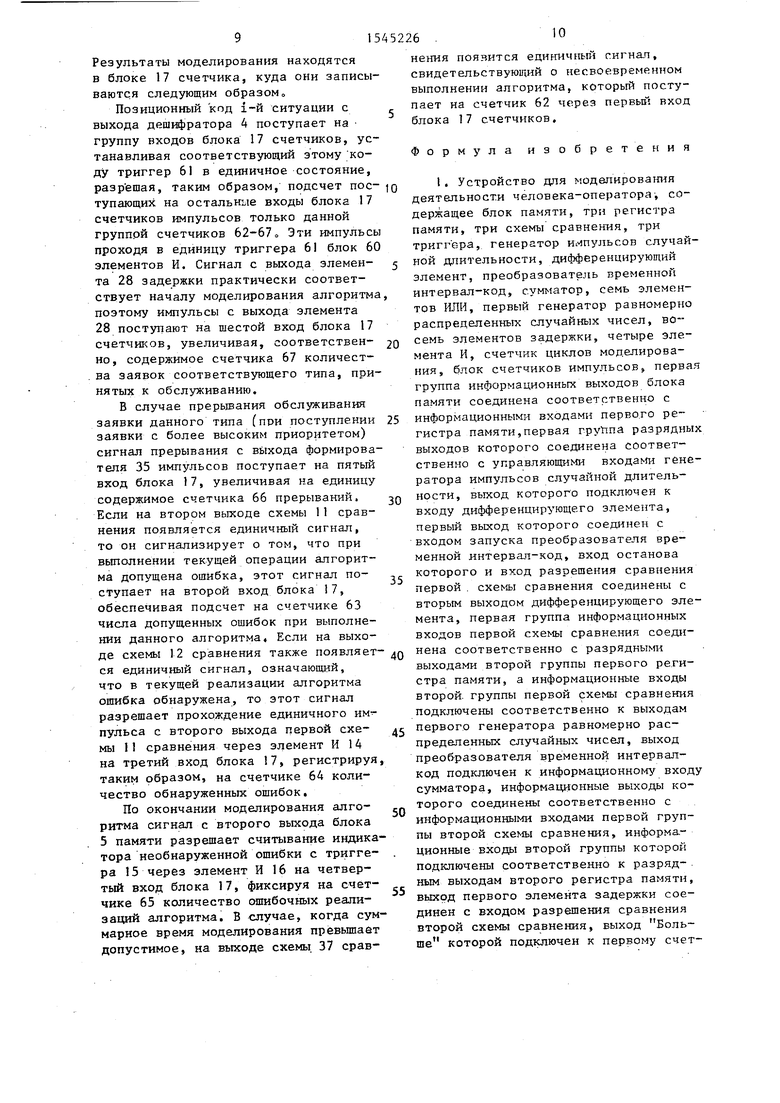

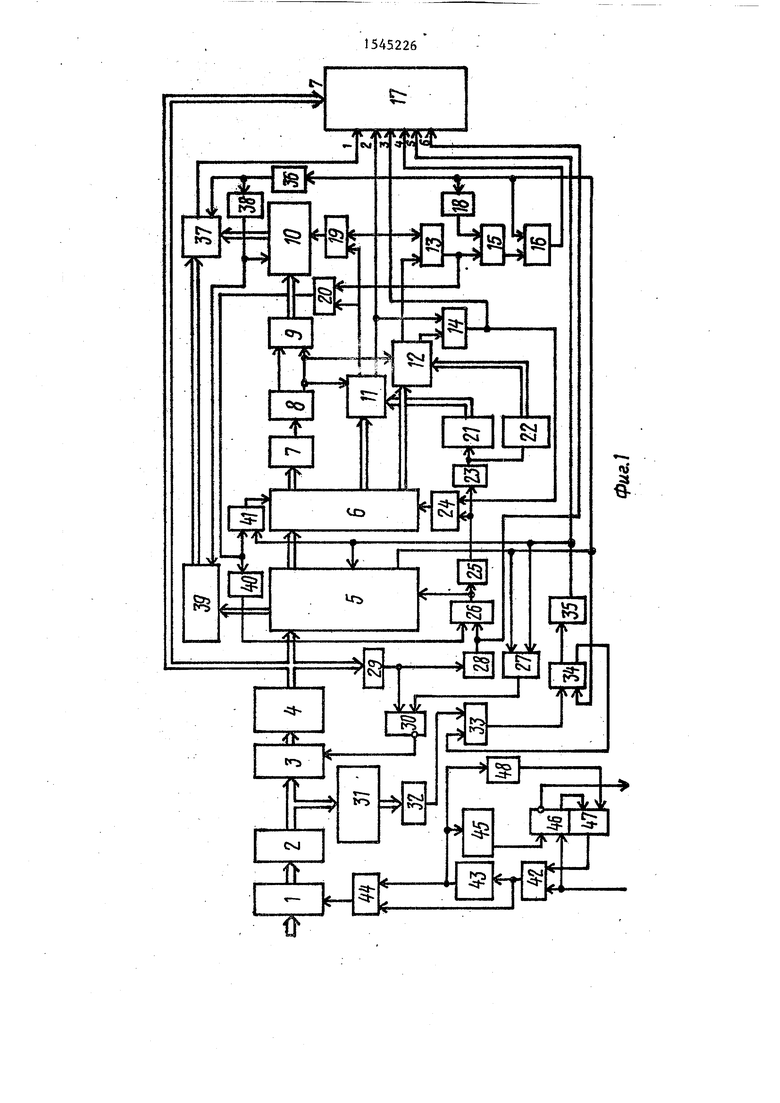

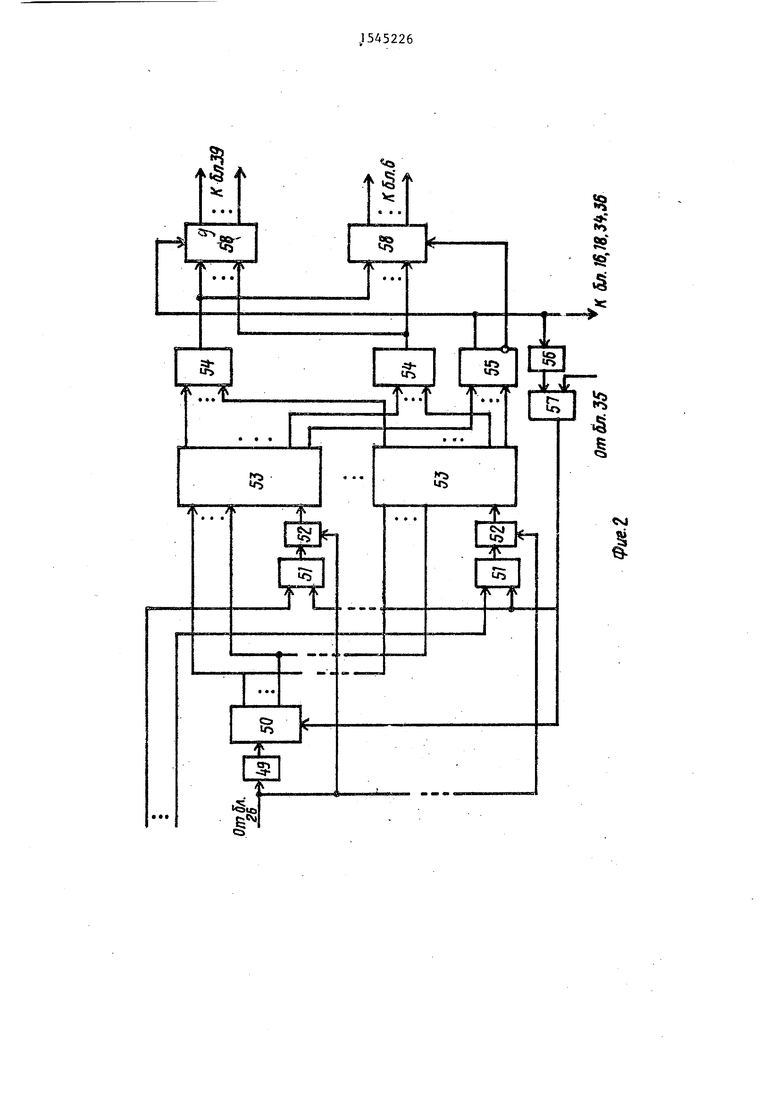

На фиг.1 изображена функциональная схема устройства для моделирования деятельности человека-оператора; на фиг.2 - функциональная схема блока памяти; на фиг.З - схема варианта построения блока счетчиков.

Устройство содержит первый блок 1 элементов И, третий регистр 2 памяти, второй блок 3 элементов И, второй дешифратор 4, блок 5 памяти, первый регистр 6 памяти, генератор 7 ИМПУПЬ

сов случайной длительности, дифференцирующий элемент 8, преобразователь 9 напряжениеткод, сумматор 10, первую 11 и вторую 12 схемы сравнения, второй элемент И 13, первый элемент И 14, пятый триггер 15 четвертый элемент И 16, блок 17 счетчиков, третий элемент 18 задержки, первый элемент ИЛИ 19, второй элемент ИЛИ 20, первый 21 и второй 22 генераторы равномерно распределенных случайных чисел, восьмой элемент 23 задержки, третий элемент ИЛИ 24, седьмой элемент 25 задержки, четвертый 26 и седьмой 27 элементы ИЛИ, пятый элемент 28 задержки, шестой, элемент ИЛИ 29, четвертый триггер Зб, первый дешифратор 31, восьмой элемент ИЛИ 32 пятый элемент И 33, третий триггер 34, формирователь 35 импульсов, n г вый элемент 36 задержки, вторую схему 37 сравнения, четвертый элемент 38 задержки, второй регистр 39 памяти, шестой элемент 40 задержки, восьмой 41 и пятый 42 элементы ИЛИ, таймер 43, первый триггер 44, счетчик 45 циклов моделирования, второй триггер 46, третий элемент И 47, второй элемент 48 задержки.

Блок 5 памяти содержит второй элемент 49 задержки, счетчик 50 импульсов, группу триггеров 51, группу элементов И 52, группу оперативных запоминающих устройств ОЗУ 53, группу элементов ИЛИ 54, второй элемент ИЛИ 55, первый элемент 56 задержки, первый элемент ИЛИ 57, второй 58 и первый 59 блоки элементов И„

Блок 17 счетчиков содержит блоки 60 элементов И, триггеры 61 и группы счетчиков, в каждую из которых входят учетчик 62 числа несвоевременно выполненных алгоритмов, счетчик 63 количества допущенных ошибок при выпол- нении 1-го алгоритма, счетчик 64 количества обнаруженных оператором ошибок, счетчик 65 числа ошибочно выполненных алгоритмов, счетчик 66 числа прерываний и счетчик 67 числа приня- тых к обслуживанию заявок,

Блок 5 памяти устройства предназначен для хранения и выдачи на регистры 6 и 39 памяти временных и вероятностных параметров моделируемой операции. На регистр 6 памяти выдается математическое ожидание М и дисперсия Сз времени выполнения опэр- ции, вероятность правильного выполнения операции Рпе и вероятность обнаружения допущенной ошибки РОБ, а на второй регистр 39 памяти блок 5 памяти выдает по окончании выполнения 1-го алгоритма допустимое время tAon1 выполнения этого алгоритма, хранящееся в последнем слове каждого оперативного запоминающего устройства 53. Последнее слово отличается от предыдущих единицей в старшем разряде, которая сигнализирует об окончании выполнения алгоритма. Таймер 43 используется для установки требуемого временного интервала для одного цикла моделирования. Счетчик 45 циклов моделирования предназначен для задания количества прогонов модели, необходимых для получения статистически достоверных результатов моделирования. Дешифратор 31 применяется для выделения из общего потока приоритетных заявок, требующих срочного вмешательства оператора в процесс управления. Триггер 34 предназначен для обеспечения прерывания оРгл- кивания неприоритетной заявки гг. поступлении приоритетной и для прерывания обслуживаемой приоритетной заявки. Информационный вход устройства представляет собой группу входов, по которым в устроГ-ство поступает последовательность кодов типов заявок (кодов ситуаций, инициирующих включение в блоке 5 памяти соответствующих этим кодам алгоритмов. Выходом устройства является инверсный выход триггера 46, предназначенный для выдачи сигнала о том, что процесс моделирования закончен.

Устройство работает следующим образом.

В исходном состоянии все регистры, триггеры, сумматор 10 и все счетчики обнулены, в ОЗУ 53 блока 5 памяти записаны последовательности временных и вероятных параметров операций, составляющих алгоритмы деятельности оператора, на таймере 43 установлен требуемый временной интервал для одного прогона модели, на счетчике 45 модели записано число -прогонов в обратном коде„

Сигнал . Пуск, пройдя через элемент ИЛИ 42, запускает таймер 43 и поступает на вход триггера 44, переводя его в единичное состояние и открывая тем самым блок 1 элементов И для прохождения последовательности кодов типов заявок (кодов ситуаций) на регистр 2, и через открытый блок 3 элементов И на дешифратор 4, с выхода которого позиционный код ситуации поступает на адресный вход блока 5 памяти, устанавливая, таким образом, соответствующий триггер 51 в единичное состояние, Кроме того, с выхода дешифратора 4 сигнал, пройдя через элемент ИЛИ 29, устанавливает триггер 30 в единичное состояние, закрывая этим блоком 3 элементов И для прохождения кодов ситуаций на дешифратор 4, а также через элемент 28 задержки и элемент ИЛИ 26 поступает на вход считывания блока 5 памяти, разрешая, таким обраом, прохождение сигнала Считывание с триггера 5J, находящегося в единичном состоянии, через соответствующий элемент И 52 на вход одного из ОЗУ 53

Так как в первом слове старший разряд обязательно равен нулю, то с инверсного выхода элемента ИЛИ 55 единичный сигнал разрешает выдачу слова через элементы ИЛИ 54 и блок 58 элементов И на первую группу выходов блока 5 памяти. Сигнал, будучи задержанным на время считывания информации из ОЗУ 53 элементом 9 задержки, поступает также на счетный вход счетчика 50, который на выходе формирует адрес для считывания следующего слова. С выходов блока 5 памяти в регистр 6 памяти переписываются значения M,,G, РПВ, и РОБ1 для моделирования выполнения первой операции заданного алгоритма.,

Сигнал с выхода элемента ИЛИ 26, задержавшись на время гарантированной переписи информации в регисир 6 памяти элементом 25 задержки, через элемент ИЛИ 24 поступает на вход первого регистра 6 памяти, разрешая считывание М и С через первую группу выходов, РПВ через вторую группу выходов и РОВ через третью группу выходов регистра 6 памяти соответственно в генератор 7 импульса случайной длительности, схемы сравнения II и 12. Генератор 7 импульса случайной длительности начинает формирование импульса случайной длительности, который поступает на вход дифференцирующего элемента 8 На генераторы 21 и 22 поступает сигнал, разрешающий считывание случайных чисел в схемы сравнения.

Сигнал Начало с выхода элемента 8 поступает на первый вход преобразователя 9, а сигнал Конец - на второй его вход, формируя код продолжительности временного интервала выполнения моделируемой операции. Одно- ременно сигнал Конец дает команду на сравнение в схемах сравнения, В

Q них сравниваются равномерно распределенные числа X и Хл, вырабатываемые соответственно генераторами 21 и 22, со значениями Рпв и Р06 .

В случае, когда X,PnB, считается,

5 что операция выполнена правильно и единичный сигнал с выхода первой схемы 1I сравнения через элемент ИЛИ 20 поступает через элемент ИЛИ 41 на обнуляющий вход регистра 6 памяти, а

0 также через элемент 40 задержки и элемент ИЛИ 26 обеспечивает выдачу на регистр 6 памяти следующего слова, содержащего временные и вероятностные параметры очередной операции алгорпт5 ма. Кроме того, сигнал с выхода первой схемы 11 сравнения поступает через элемент ИЛИ 19 на вход сумматора 10, разрешая суммирование показаний преобразователя 9 с имеющимся

0 числом на сумматоре.

В случае, когда Х,РПВ, считается, что операция выпол ена с ошибкой. Тогда возможны два исхода: ошибка обнаружена и исправлена или ошибка

, не обнаружена. Поэтому, кроме выдачи единичного сигнала с второго выхода схемы I1 сравнения через элемент ИЛИ 19 на вход сумматора 10 для гуммирования временных затрат на вы0 полнение операции, этот же сигнал поступает на входы элементов И 13 и 14, на один из других входов которых поступает сигнал или с первого выхода схемы 12 сравнения (в случае необпа5 ружения оператором ошибки - ) или с второго ее выхода (в случае обнаружения ошибки - ). В первом случае сигнал с выхода -элемента И 13 поступает на вход установки в ЕДИНИЧ0 ное состояние триггера 15, сигнализируя , что при выполнении алгоритма допущена ошибка и она не обнаружена оператором (индикатор необнаруженной ошибки). Кроме того, этот же сигнал

через элементы ИЛИ 20 и 41 обнупяет регистр b памяти и подготавливает устройство к моделированию очередной операции алгоритма„ В другом случчо сигнал с выхода элемента И 14. сяидетельствуя о факте обнаружения ошибк оператором, поступает через элемент ИЛИ 24 на вход регистра 6 памяти, обеспечивая повторное моделирование операции, что имитирует исправление оператором сшибки.

После выполнения последней операции алгоритма при очередном обращении к блоку 5 памяти происходит счи- тывание сигнала окончания алгоритма - единицы в старшем разряде одного из регистров накопителя ОЗУ 53, которая, пройдя через элемент ИЛИ 55, закрывает блок 58 элементов И и разрешает выдачу кода допустимого времени моделирования через блок 59 элементов И на вторую группу выходов блока 5 памяти, откуда он записывается в регистр 39 памяти, с которого лоступа- ет на первую группу входов схемы 37 сравнения, на вторую группу входов которой поступает код суммарного времени выполнения алгоритма от сумматора 10. Кроме того, единичный сигнал с выхода элементов ИЛИ 55 проходит на выход блока 5 памяти и, задержавшись элементом 56 задержки на время считывания информации из ОЗУ, обнуляет счетчик 50 и установленный ранее в единичное состояние триггер 51, пройдя через элемент ИЛИ 57.

С выхода блока 5 памяти единичный сигнал поступает на разрешающий вход элемента И 16, через который информа- ция с триггера 15 проходит на вход блока 17 счетчиков, затем, задержавшись элементом 18 на время передачи состояния триггера на вход блока 17, обнуляет триггер 150 Также этот сиг- нал, будучи задержанным элементом 36 задержки на время, достаточное для поступления кода допустимого времени на группу входов схемы 37 сравнения, подает команду на сравнение, после чего, задержавшись элементом 38 задержки, обеспечивающим срабатывание схемы 37 сравнения, сигнал поступает на входы сумматора 10 и регистра 39 памяти, устанавливая их в исходное состояние. Единичный сигнал с второго выхода блока 5 памяти поступает, кроме того, через элемент ИЛИ 27 на обнуляющий вход триггера 30, разрешая этим дешифрацию очередного кода си- туации с целью выбора соответствующего данной ситуации алгоритма для моделирования, после чего едини in т сигналом элрмента ИЛИ 29 триггер

вновь устанавливается в единичное состояние до окончания моделирования алгоритма.

Однако если во время моделировани алгоритма на регистр. 2 поступает код, соответствующий приоритетной трупе ситуаций, он дешифрируется дешифратором 31 и, пройдя через элемент ИЛИ 32 и открытый единичным сигналом с инверсного выхода триггера 34 элемент И 33, устанавливает триггер 34 в единичное состояние. На прямом выходе триггера 34 появляется сигнал прерывания, который через элемент ИЛИ 41, будучи преобразованным формирователем 35 в короткий импульс устанавливает в нуль регистр 6 памяти, поступая на вход блока 5 памяти, обеспечивает обнуление триггеров 51 и счетчика 50 через элемент ИЛИ 57, а также через элемент ИЛИ 27 обнуляе триггер 30, разрешая этим дешифрацию поступившего кода ситуации Причем в этом случае любая последующая ситуация не вызывает прерывания до окончания моделирования алгоритма, тал KdK триггер 34 остается в еди- ы.чном состоянии до момента прихода на его обнуляющий вход единичного сигнала с второго выхода блока 5 памяти.

По истечении времени одного цикла моделирования таймер 43 выдает сигнал, обнуляющий триггер 44. Этот сигнал поступает также на счетный вход счетчика 45 и, задержавшись элементом 48 задержки на время, достаточное для срабатывания счетчика 45 и триггера 46, поступает на элемент И 47, через который проходит благодаря наличию единичного сигнала на прямом выходе триггера 46 установленного в это состояние сигналом Пуск. Сигнал с выхода элемента И 47 через элемент ИЛИ 42 поступает на вход установки в единичное состояние триггера 44 и на таймер 43, обеспечивая запуск очередного цикла. После осуществления количества циклов, записанного изначально в обратном коде в счетчике 45, последний вырабатывает сигнал переполнения, который устанавливает в нуль триггер 46, запрещая этим запуск очередного цикла. Кроме того, на инверсном выходе триггера 4 появляется единичный сигнал, который подается на выход устройства, сигнализируя об окончании модетирования,

Результаты моделирования находятся в блоке 17 счетчика, куда они записываются следующим образом о

Позиционный кпд 1-й ситуации с выхода дешифратора 4 поступает на группу входов блока 17 счетчиков, устанавливая соответствующий этому коду триггер 61 в единичное состояние, разр ешая, таким образом, подсчет пос- тупающих на остальное входы блока 17 счетчиков импульсов только данной группой счетчиков 62-67„ Эти импульсы проходя в единицу триггера 61 блок 60 элементов И. Сигнал с выхода элемен- та 28 задержки практически соответствует началу моделирования алгоритма поэтому импульсы с выхода элемента 28 поступают на шестой вход блока 17 счетчиков, увеличивая, соответствен- но, содержимое счетчика 67 количества заявок соответствующего типа, принятых к обслуживанию.

В случае прерывания обслуживания заявки данного типа (пои поступлении заявки с более высоким приоритетом) сигнал прерывания с выхода формирователя 35 импульсов поступает на пятый вход блока 17, увеличивая на единицу содержимое счетчика 66 прерываний. Если на втором выходе схемы 11 сравнения появляется единичный сигнал, то он сигнализирует о том, что при выполнении текущей операции алгоритма допущена ошибка, этот сигнал поступает на второй вход блока 17, обеспечивая подсчет на счетчике 63 числа допущенных ошибок при выполнении данного алгоритма. Если на выхо

нения поячится единичный сигнат, свидетельствующий о несвоевременном выполнении алгоритма, который поступает на счетчик 62 через первый вход блока 17 счетчиков.

Q 0

5

0

5

Формула изобретения

1 . Устройство для моделировать деятельности человека-оператора, содержащее блок памяти, три регистра памяти, три схемы сравнения, три триггера, генератор импульсов случайной длительности, дифференцирующий элемент, преобразователь временной интервал-код, сумматор, семь элементов ИЛИ, первый генератор равномерно распределенных случайных чисел, восемь элементов задержки, четыре элемента И, счетчик циклов моделирования, блок счетчиков импульсов, первая группа информационных выходов блока памяти соединена соответственно с информационными входами первого регистра памяти,первая группа разрядных выходов которого соединена соответственно с управляющими входами генератора импульсов случайной длительности, выход которого подключен к входу дифференцирующего элемента, первый выход которого соединен с входом запуска преобразователя временной интервал-код, вход останова которого и вход разрешения сравнения первой схемы сравнения соединены с вторым выходом дифференцирующего элемента, первая группа информационных входов первой схемы сравнения соеди

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования деятельности человека-оператора | 1990 |

|

SU1778761A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1413640A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1377870A1 |

| Устройство для моделирования деятельности человека-оператора | 1988 |

|

SU1580388A1 |

| Устройство для моделирования деятельности человека-оператора | 1986 |

|

SU1399761A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1432553A1 |

| Устройство для моделирования систем массового обслуживания | 1990 |

|

SU1784993A1 |

| Устройство для моделирования деятельности операторов систем человек-машина | 1986 |

|

SU1388888A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1164726A1 |

Изобретение относится к устройствам имитационного моделирования. Целью изобретения является расширение функциональных возможностей за счет имитации динамики деятельности оператора по обслуживанию потока заявок с учетом отработки конкретных алгоритмов деятельности по каждому типу заявок. Устройство содержит блок памяти, в котором содержатся временные и вероятностные характеристики последовательностей операций в каждом алгоритме

регистры памяти, предназначенные для их временного хранения, а также значения вероятности правильного выполнения операции, обнаружения ошибки и допустимого времени выполнения алгоритма

генератор импульсов случайной длительности, дифференцирующий элемент и преобразователь временной интервал - код - для формирования временного интервала выполнения каждой операции

генераторы равномерно распределенных случайных чисел и схемы сравнения - для моделирования появления событий, соответствующих правильному либо неправильному выполнению операции, обнаружению или необнаружению ошибки, своевременному либо несвоевременному выполнению алгоритма

сумматор

блок счетчиков

дешифраторы

таймер и счетчик: Устройство может быть использовано для анализа и синтеза комплексов средств отображения информации эргатических систем. 1 з.п. ф-лы, 3 ил.

де схемы 12 сравнения также появляет- 4Q нена соответственно с разрядными

ся единичный сигнал, означающий, что в текущей реализации алгоритма ошибка обнаружена, то этот сигнал разрешает прохождение единичного импульса с второго выхода первой схемы 1 сравнения через элемент И 14 на третий вход блока 17, регистрируя, таким образом, на счетчике 64 количество обнаруженных ошибок.

По окончании моделирования алгоритма сигнал с второго выхода блока 5 памяти разрешает считывание индикатора необнаруженной ошибки с триггера 15 через элемент И 16 на четвертый вход блока 17, фиксируя на счетчике 65 количество ошибочных реализаций алгоритма. В случае, когда суммарное время моделирования превышает допустимое, на выходе схемы 37 срав45

50

55

выходами второй группы первого ре стра памяти, а информационные вхо второй группы первой схемы сравне подключены соответственно к выход первого генератора равномерно рас пределенных случайных чисел, выхо преобразователя временной интерва код подключен к информационному в сумматора, информационные выходы торого соединены соответственно с информационными входами первой гр пы второй схемы сравнения, информ ционные входы второй группы котор подключены соответственно к разря ным выходам второго регистра памя выход первого элемента задержки с динен с входом разрешения сравнен второй схемы сравнения, выход Бо ше которой подключен к первому с

5

0

5

выходами второй группы первого регистра памяти, а информационные входы второй группы первой схемы сравнения подключены соответственно к выходам первого генератора равномерно распределенных случайных чисел, выход преобразователя временной интервал- код подключен к информационному входу сумматора, информационные выходы которого соединены соответственно с информационными входами первой группы второй схемы сравнения, информационные входы второй группы которой подключены соответственно к разрядным выходам второго регистра памяти, выход первого элемента задержки соединен с входом разрешения сравнения второй схемы сравнения, выход Больше которой подключен к первому счет111

ному входу блока счетчиков, вход раз решения суммирования сумматора соеди нен с выходом первого элемента ИЛИ, первый вход которого подключен к выходу Меньше или равно первой схемы сравнения и первому входу второго элемента ИЛИ, а выход Больше первой схемы сравнения соединен с вторым счетным входом блока счетчиков, вторым входом первого элемента ИЛИ и первыми входами первого и второго элементов И, выход первого элемента И подключен к первому входу третьего элемента ИЛИ, выход четвертого элемента ИЛИ подключен к входу считывания блока памяти, отличающееся тем, что, с целью расширения функциональных возможностей за счет моделирования обслуживанш приоритетных заявок и исправления ошибок, допущенных в процессе работы оно дополнительно содержит восьмой и девятый элементы ИЛИ, первый и второй блоки элементов И, два дешифратора, формирователь импульсов, пятый элемент И, второй генератор равномерно распределенных случайных чисел, четвертый и пятый триггеры, тай мер, причем информационными входами устройства являются информационные входы первого блока элементов И, уп- равляюшш вход которого соединен с прямым выходом первого триггера, единичный вход которого и вход запуска таймера соединен с выходом пятого элемента ИЛИ, первый вход которого и единичный вход второго тригге ра объединены и являются входом запуска устройства, второй вход пятого элемента ИЛИ подключен к выходу третьего элемента И, первый вход которого соединен с прямым выходом второ го триггера, инверсный выход которого является выходом окончания модели рованпя устройства, а нулевой вход второго триггера подключен к выходу обнуления счетчика циклов моделирова ния, счетный вход которого подключен к выходу таймера, нулевому входу пер вого триггера и входу второго элемен та задержки, выход которого подключен к второму входу третьего элемента И, выходы первого блока элементов И соединены соответственно с информационными входами третьего регистра памяти, разрядные выходы тго- рого подключены гоотпел гтренно дам первого дешифратора и инфрп -i t

45226

12

ционным входам второго блока элементов И, выходы которого соединены соответственно с входами второго дешифратора, выходы которого подключены соответственно к входам шестого элемента ИЛИ, группе информационных входов блока счетчиков и адресным входам блока памяти, выход окончания

. g считывания которого соединен с первым входом седьмого элемента ИЛИ, нулевым входом третьего триггера, первым входом четвертого элемента И, входом третьего элемента задержки и

5 входом первого элемента задержки, выход которого подключен к входу четвертого элемента задержки, выход которого соединен с установочными входами сумматора и второго регистра па7(1 мяти, информационные входы которого подключены соответственно к выходам 7 торой группы блока памяти, выходы первого дешифратора соединены соответственно с входами восьмого эле25 мента ИЛИ, выход которого подключен к первому входу пятого элемента И, второй вход которого соединен с ин- I v f сным выходом третьего триггера, а выход пятого элемента И подключен

3Q к единичному входу третьего триггера, прямой выход которого соединен с входом формирователя импульсов, выход которого подключен к первому входу восьмого элемента ИЛИ, установочному входу блока памяти и второму входу седьмого элемента ИЛИ, выход которого подключен к нулевому входу четвертого триггера, инверсный выход которого подключен к управляющему

дд входу второго блока элементов И, а единичный вход четвертого триггера соединен с выходом шестого элемента ИЛИ и входом пятого элемента задержки, выход которого подключен к Д5 первому входу четвертого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента задержки, а выход четвертого элемента ИЛИ подключен к входу седьмого элемента засп держки, выход которого соединен с входом восьмого элемента задержки и вторым входом третьего элемента ИЛИ, выход которого подключен к входу считывания первого регистра памяти, вход обнуления которого соединен с выходом восьмого элемента ИЛИ, второй вход которого и вход шестого элемента задержки подключены к выходу второго элемента ИЛИ, второй вход

35

торого соединен с единичным входом пятого триггера и выходом второго элемента И, второй вход которого подключен к выходу Больше третьей схемы сравнения, выход Меньше или Равно который соединен с вторым входом первого элемента И, выход которого подключен к третьему счетному входу блока счетчиков, четвертый счетный вход которого соединен с выходом четвертого элемента И, второй вход которого соединен с прямым выходом пятого триггера, нулевой вход которого подключен к выходу третьего элемента задержки, вход разрешения сравнения третьей схемы сравнения подключен к второму выходу дифференцирующего элемента, информационные входы первой группы третьей схемы сравнения соединены соответственно с разрядными выходами третьей группы первого регистра памяти, а информационные входы второй группы третье схемы сравнения подключены сиответ- ственно к выходам второго генератора равномерно распределенных случайных чисел, вход запуска которого и вход запуска первого генератора равномерно распределенных случайных чисел соединены с выходом восьмого элемента задержки, пятый и шестой счетные входы блока счетчиков подключены соответственно к выходам формирователя импульсов и пятого элемента за- держки.

блока памяти являются единичные входы триггеров группы, нулевые входы триггеров группы и установочный вход счетчика импульсов объединены и подключены к выходу перЕюго элемента ИЛИ, первый вход которого является установочным входом блока памяти, а второй вход первого элемента ИЛИ соединен с выходом первого элемента задержки, вход которого соединен с прямым выходом второго элемента ИЛИ, управляющим входом первого блока элементов И и является выходом окончания считывания блока памяти, инверс гый выход второго элемента ИЛИ соединен с управляющим входом второг блока элементов И, выходы которого являются первой группой информационных выходов блока памяти, второй информационной группой выходов которого являются выходы первого бпока элементов И, первые входы элементов И группы и вход второго элемента задержки объединены и являются входом считывания блока памяти, вторые входы элементов И группы подключены соответственно к прямым выходам триггеров группы, а выходы элементов И группы подключены соответственно к входам считывания оперативных запоминающих устройств, адресные входы которых подктючены соотнетСТВРННО к разрядным выходам счетчика импупь- сов, счетный вход которого соединен с выходом второго элемента задержки, К-е информационные выходы оперативных запоминающих устройсгв,(,п) соединены соответственно с входами К-го элемента И1И группы, а выходы окончания считывания оперативных запоминающих устройств соединены соответственно с входами второго элемента ИЛИ, выход К-го элемента ИЛИ группы соединен с К-ми входами первого и второго блокоч элементов И,

Jf т

ж

7

А

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1241254A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1432553A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-23—Публикация

1987-11-13—Подача