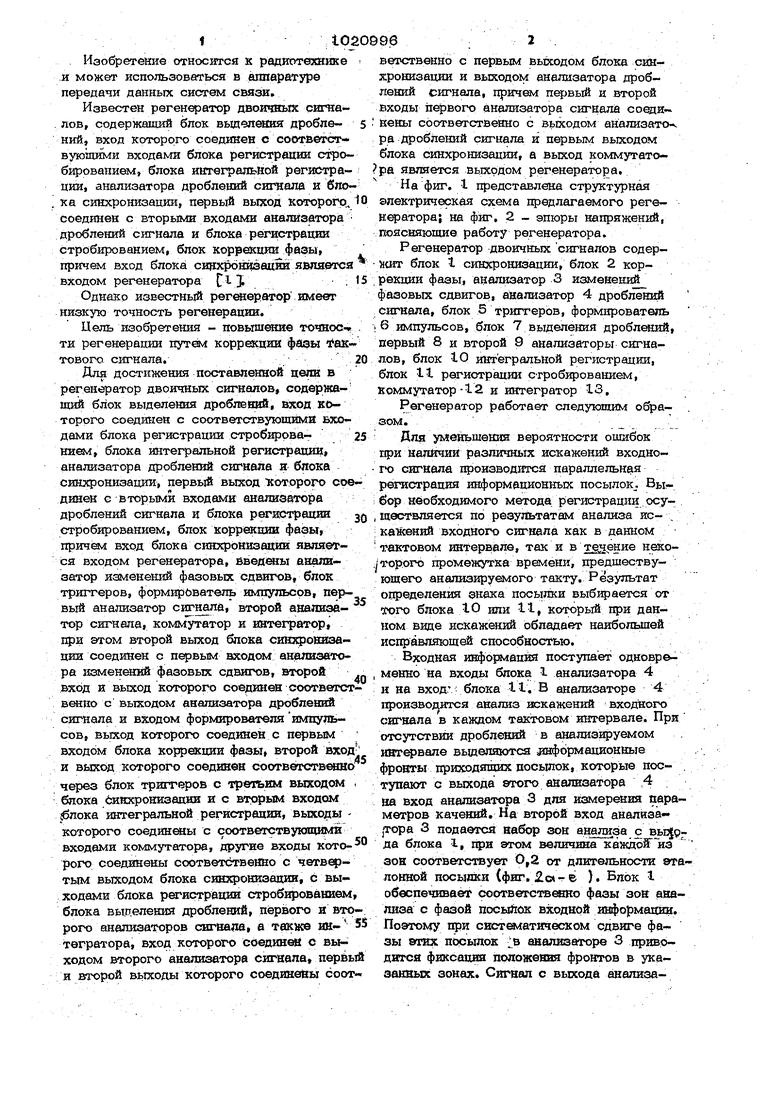

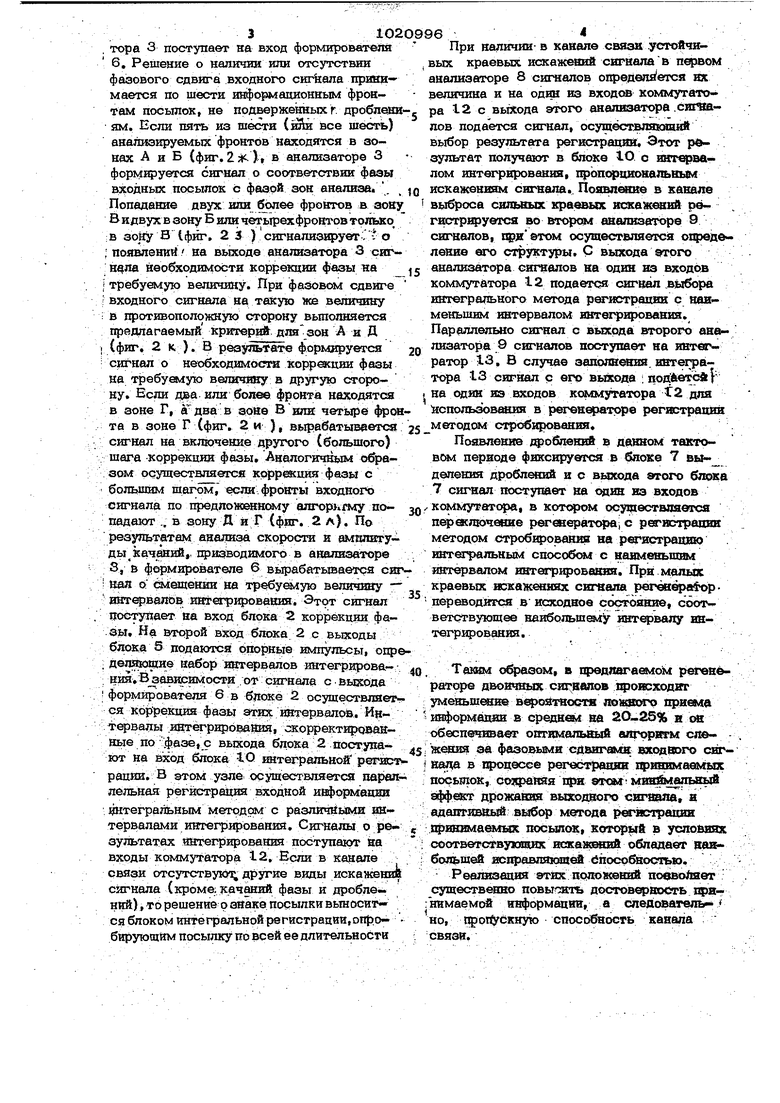

Иэобретенн:в относится к радиотехнике и может использоваться в аппаратуре передачи данных систем связи. Известен реген атор двоичных сигна. лов, содержшцнй блок вьщепешкс дроблеНИИ, вход которого соединен с соответствующими входами блока регистрации стробироваяием, блока интегральной репистрации, анализатора дроблений сигнала и блока синхронизации, первый выход которого.. соединен с вторыми входами анализатора дроблений сигнала и блока регистрации стробированием, блок коррекции фазы, причем вход блока синхронизации является входом регенератора ClJ; Однако известньй pereieparopимеет низкую точность регенерации. Цель изобретения - повышение точное- тн регенерации путём коррекции фазы тового сигнала./ Для достижения поставленной цели в регенератор двоичных сигналов содержащной блок выделения дроблений, вход которого соединен с соответствующими входами блока регистрации стробиррванием, блока интегральной регистрации, анализатора дроблений сигнала и блока синхронизащш, первый выход тсоторого сое динен с вторыми входами анализатора дроблений сигнала и блока регистращи стробированием, блок коррекции фазы, причем вход блока синхронизакш является входом реген атора, введШы анализатор изменений фазовых сдвигов, блок триггеров, формирователь импульсов, первый анализатор сигнала, второй анализатор сигнала, коммутатор и интегратор, 1ФИ этом второй выход блока синхронизации соединен с первым входом анализатора хйзменений фазовых сдвигов, второй вход н выход которого соедкнев соответст BQIHO с выходом анализатора дроблений сигнала и входом формирователя импульсов, выход которого соединен с первым входом блока коррекции фазы, второй вход и выход которого соединен соответственно через блок триггеров с третьим выходом блока t «tJcpoHK3anHH и с вторым входом «блока интегральной регистрации, выходы которого соединшы с соответствукящшгй входами коммутатора, другие входы которого соединены соответственно с четвфтым выходом блока синхронизации, с выходами блока регистрвцин строб1фованием блока выделения дроблений, первого и вто porxj анализаторов снгнада, а текже штвгратора, вход которого соедини с выходом второго анализатора сигнала, первы и второй вьгходы которого соединены соот ветственно с первым выходом блока синхронизации и выходом анализатора дроблений сигнала, причем первый и второй входы первого анализатора сигнала соединены соответственно с вьисодом анализатора дроблений сигнала и первым выходом блока синхронизации, а выход коммутатора является выходом регенератора. На фкг. I представлена структурная электрическая схема предлагаемого регенератора; на фиг. 2 - эпюры напряжений, поясняющие работу регенератора. Регенератор двоичных сигналов содерйогг блок 1 синхронизации, блок 2 коррекции фазы, анализатор 3 изменений фазовых сдвигов, анализатор 4 дроблёнкй сигнала, блок 5 триггеров, формирователь 6 импульсов, блок 7 выделения дроблошй, первый 8 и второй 9 анализаторы сигналов, блок 10 интегральной регистрации, блок tl регистрации стробированием. Коммутатор 12 и интегратор 13, Регенератор работает следующим образом. Для уменьшения вероятности ошибок при наличии различных искажений входногю сигнала производится параллельная регистрация информационных посылок,- Выбор необходимого метода регистрации осушествляется по результатам анализа ис- , каШений входного сигнала как в данном тактовом интервале, так и в т.нение некоторого промежутка времени, предшеству- : юшего анализируемого такту. Результат определения знака посылки выбирается от того блока Л О или II, который при данном ввде искажений обладает наибольшей исправляющей способностью. Входная инфо шапия поступает одновр&менно на входы блока 1 анализатора 4 и на ВХОД: блока 11. В анализаторе 4 производится анализ искажений входного сигнала в каждом тактовом интервале. При отсутствий дроблений в анализируемом итчфвале вьщеляютса даформационные фронты приходящих посылок, которые пос- . тупают с выхода этого анализатора ,4 на вход анализатора 3 для измерения параметров качений. На второй вход анализа- jTopa 3 подается набсф зон анализа с вы:$9да блока 1, гфн этом величина квждо8 из зон соответсшует 0,2 от длительности эталонной посыпки (фиг, ). Блок I обеспечивает соответств по фазы зон анализа с фазой посыйок входной информации. Поэтому гфи систематическом сдвиге фазы этих псюылок в анализаторе 3 приводится фиксация положения фронтов в указанных зонах. С1{гнал с выхода анализа3102тора 3 поступает на вход формироватезгга 6, Решение о наличии или отсутствии фазового сдвига входного прищамается по шести информационным фронтам посылок, не подверженных г дробленн „ - /-м ,- ЯМ. Если пять из шести (iSbi все шесть) анализируемых фронтов находятся в зонах А и Б (фиг.), в анализаторе 3 формируется сигнал о соответствии фазы 8: одньсс посылок с фазой зон анализа, . Попадание двух или ботее фронтов в зону В идвух в зону Б или четырех фронтов тольжо/ :В зону ВЧфйг. 2 3 ) сигнализирует- to ; появлений /на вьшоде анализатора 3 сигнула необходимости коррекции фазы на i трёбуемук) величину. При (фазовом сдвиге ; входного сигнала на такую же величину г в противоположную сторону выполняется предлагаемый KpurrepiHft длязон Аи Д 1 (фиг. 2 к. ). В результате формируется сигнал о необходимости коррекции фазы на требуемую величйку в другую сторону. Если ддаа или боле фронта находятся в зоне Г, адва в зоне В или четыре фро та в зоне Г (фиг. 2 и ), вьфабатываетсда сигнал на включение другого (большого) шага коррекции фазы. Аналогичным образом осуществляется коррекция фазы с большим шаго1м, если фронты входного сигнала по предложеннсялу алгоркшу пошдаадт ., в зону Д и Г (фяг. 2л). По результатам анализа скорости и евлтитагуды качаний,, приэводщгого в анализаторе : 3, в формирователе 6 вырабатывается сй 1 нал о тещении на требуемую величшу ийтервапов интегрщювания. Этсэт сигнал . поступает на вход блока 2 коррекции фазы. На второй вход бтажа 2 с выходы блока 5 додаются опорные нмпульсЫ| опр ; делающие набор 11итервалов штегрирова- ния В зав1к:имости от сигнала с выхода формщ)оватёля 6 в блоке 2 осуществляет ся к6р рекцйя фазы этих и тервалр&.. Щтервапы .вдгёгрнрбэа1;йш, сжорректированHbie по ;.фазе,с выхода бдока 2 поступают на вход бгазка -1Q ш тёгральной рерирт рации. В этом узле осуществляется парал лельная регистрация входной ивфо йлааии интегральным методом с различными интервалами иктегр1фования. Сигналы о |)е зультатах интегрирования поступают на входы коммутатора 12. Если в канале связи отсутствующ другие виды искаданий сигнала (кроме; качаний фазы и дробле НИИ), тЬ решение о знаке посылки вьгаосит-г ся блоком интегральной регисградии,опро- бирующйм посылку по всей ее длительности 6 При наличии- в кайап© связи устойчивых краевых искажений сигналав первом анализаторе 3 сигналов О1федеп /ется юс величина и на один из входов коммутатора 12 с выхода этого анализатора .сиша-. .. - - .„. лов подается сигнал, осущёствлякший выбор результата регистрации. Этот результат получают в блоке Ю с интервалом интегрирования, прЬпоршюнальшлм искажениям сигнала.. Появлвнохе в канатю выброса сильных краевых искаж хий регистрируется во втором анализаторе 9 сигналов, 1фя етом осуществляется определение его ст|руктуры. С вюсода этого анализатора сигналов на один вз входов коммутатора 12 подается сигнал,выбора интегрального метода регисУграцни с наименьш;им интервалом Еоггегрирования. Параллельно сигнал с выхода: второго анв- лизатора 9 свгналст поступает на интегратор 13, В случав запрян хвЕЯ. интегратора 13 сигнал р его ; noriuerci г на один КЗ гасодов коммутатора Г2 для Использования в регенераторе регистрации метед1ом соробирования Появление /фоблений в ивяяом тактовом периоде фиксируется в блоке 7 доения дроблений и с выхода этохч) блока 7 сигнал поступает на один из входов коммутатора, в котором ооущестышется пе|)аслючввие рвгевератора; с регистрадик методом стробирования на регястрадвю . штегральным способ я4 с наяменьщщд интервалом шггвгрировашзя. При малых краевых искажениях скгкеаш регёкфафор переводЗйтся В исясодное сортояние, соответствующее наибольшау1у иа- . тегрщэования. Таиш , в щюддагаемсмм регев&раторе двойчнык сш ввиов происходит умйяьщеняе в ероатнсеяя ложаогр прием 1ш}юрмадяи в среднем т 2О-25% и ш чьбеспечивает овтимальаый алгоритм еле- kesBH за фазовьали сдвигами ВЭСОДЕООГО сжгвада в щюкесее ретчэстршши хфшшмашых посьяюк, сеярешя пря мввзбb {вльшьiй Еффе9к г дрожавхщ ш осодв(ого сшивала, SE адаппшшй выбор метода регжмраиин Прнквмаемых щюьшох, котордый в условаях соответству1с ш1х вскажвввй обладает ааибольш аспфавляюшей бпособвостью. Реаш1зааия этих положений поввоАяет Г существедшо повыгзггь достоверность щаашмаемой ивформаднн, а следовагвд| но.прогб скную способность канала связи.

Фиг./

а)

б)

6)

3wa:ff utl

| название | год | авторы | номер документа |

|---|---|---|---|

| Регенератор двоичных сигналов | 1981 |

|

SU995346A1 |

| Регенератор двоичных сигналов | 1979 |

|

SU794752A1 |

| Электронный распределитель | 1984 |

|

SU1170625A2 |

| Двухступенчатый регенератор | 1985 |

|

SU1317678A2 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU919130A1 |

| Двухступенчатый регенератор | 1983 |

|

SU1197117A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU938420A1 |

| Регенератор двоичных сигналов | 1984 |

|

SU1185630A1 |

| Устройство тактовой синхронизации регенератора | 1985 |

|

SU1283992A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU882012A1 |

РЕГЕНерАТОР ДВОИЧНЫХ CtirHA/K B, содержащий блок вьщеления дроблений4 еход которого соединен с соответствующими входами блока рёгистрании стробированием, блока интегральной регистрации, анализатора дроблений еигйала и блока синхронизации, первый ыдход -которого соединен с вторыми входами анализатора дроблений сигнала и блока регистрами стробированием, блок коррекшш фазы, причем вход блока синхронша1аии является входом регенератора, о т - личак щийся тем, что, с целью повышения точности регистрации путем коррекции фазы тактового сигнала, введены еяализатор изменений фазовьвс сдвигов, блок триггеров, формщзоватеш импульсов, первый анализатор сигнала вто . - 1 хрой анализатор сигнала, коммутатор и инTerpaTopj при этом второй выход блока синхронизации соединен с йервьа входом анайиаатора нзмен осй фазовых сдв11гов, второй вход и выход которого соедннен сбответств«1но с выходом анаяизэтора дроблений сиг{юла и входом фьрмхфова- . теля импульсов выход котфо1ч соёдще { с первым вхбдом блока коррекции фазы, второй вход и выход которого сбедиаек соответственно через блок TpatrrepoB с третьим выходом блока сшсхроиизацЯи и с вторым входом блока интеграта ндй регистрации, выходы. кот«лзеяго сЬедшхеШы с соответствующими входами Коммутагора, другие входы которсго сосоннвны соответственво с четвё|}тым выход( блока синхронизации, с выходами блоха (А регистрации стробйроваййшл, блока выдеС ления д|роблеаий, первого и BTopdro реализаторов сигнала, а также вятеЕратора, вход которого соединен с выходе го анализаторе сигнала, первый и втфрЙ Э ; входы которого соединзяы соответствеее о СО: с первым выходом блока синхронйзацш Э ;о р и выходом анализатора дроблший сигнала, причем первьШ и второй входы первого анализатора сигнала соедин ы соответственно с выходом анализатсфа дроблен 3 сигаала и первом выходом блока сшщювиЗйции, а выход коммутатора является выходом регенератора.

| Л, Авторское сйидетепьство N9 743211, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-05-30—Публикация

1981-09-23—Подача