ны с выходом первого элемента ИЛИ, выход коммутатора подключен к первым входам первого и второго счетчиков, вторые входы которых соединены с другими выходами коммутатора, второй выход блока синхронизации подключен к пе;)вому входу первого ключа, выход которого 11од лючен к первому входу распределителя записи и к первому входу распределителя считывания, соответствующий выход счетчика-распределителя подключен к второму входу распределителя записи, выходы которого через последовательно соединенные блок элементов записи, блок элементов буферной памяти и блок элементов считывания подключены к входам соответствующих второго и третьего элемептов ИЛИ, выходы которых подключены к входам выходного триггера, соответствующий выход распределителя записи подключен к второму входу первого ключа, другой выход которого подключен к второму входу распределителя считывания, выходы которого подключены к другим входам блока элемептов считывания, введепы второй и третий ключи, четвертый и пятый элементы ИЛИ, анализатор щума, анализатор входного сигнала, блок коррекции цикла записи,-.рещакэщий блок, блок проверки фазы сигнала записи, блок определения знака и величины сдвига сигнала записи и блок определения зиака сдвига входного сигнала, при этом выходы первого и второго счетчиков подключены к первым входам соответственно второго и третьего ключей, выходы которых через четвертый и пятый элементы ИЛИ подключены к другим входам соответственно блока добавления и блока вычитания, выход первого элемента ИЛИ подключен к входам анализатора шума и анализатора входного сигнала, выходы которых подключены к вторым и третьим входам второго и третьего ключей, соответствующий выход распределителя считывания подключен к первым входам блока проверки фазы сигнала записи, блока определения знака и величины сдвига, сигнала записи и блока определения знака сдвига входного сигнала, выходы которых через рещающий блок подключены к первому входу блока коррекции цикла записи, выход блока проверки фазы сигнала записи подключен к второму входу блока коррекции цикла записи, выходы которого подключены к другим входам четвертого и пятого элементов ИЛР1, выход первого элемента ИЛИ подключен к второму входу блока определения знака сдвига входного сигнала, соответствующий вход блока элементов записи подключен к вторым входам блока определения знака и величины сдвига сигнала и блока проверкн фазы сигнала записи, третий вход которого соединен с выходом анализатора шума.

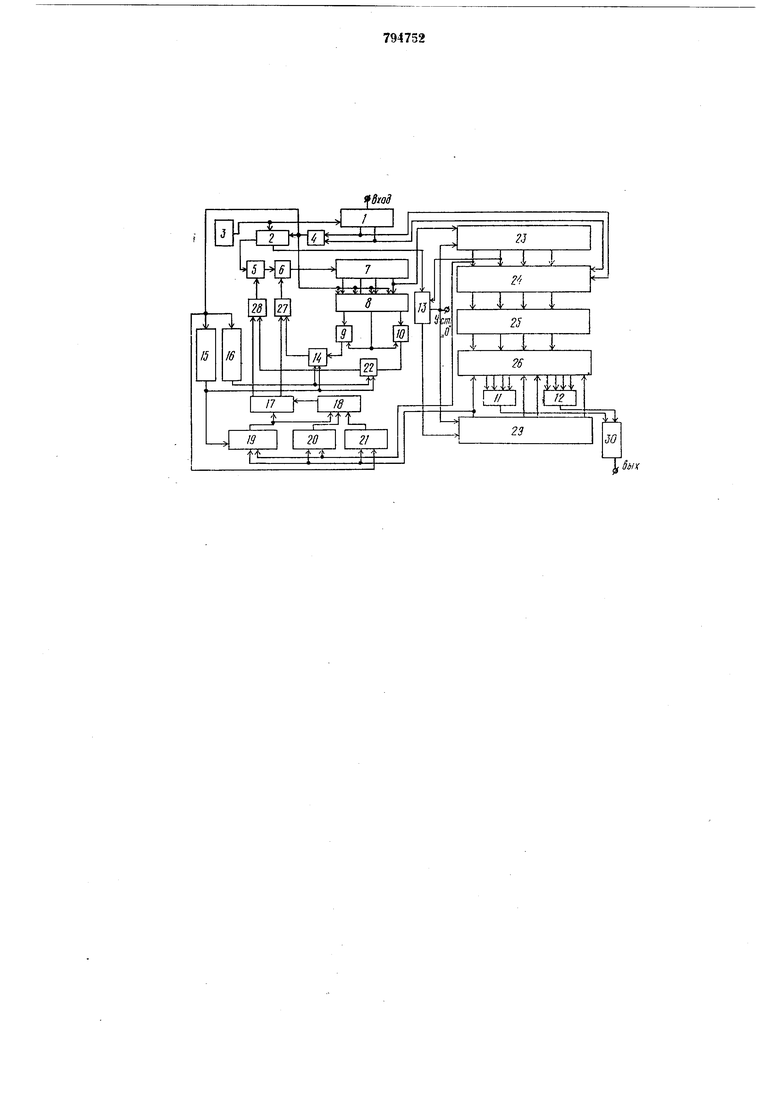

Иа чертеже приведена структурная электрическая схема предлагаемого регенератора.

Регенератор двоичных сигналов содержит асинхронный приемник 1, блок 2 синхронизации, задающий генератор 3, первый элемент ИЛИ 4, блок 5 вычитания, блок 6 добавления, счетчик-распределитель 7, коммутатор 8, первый 9 и второй 10 счетчики, второй 11 и третий 12 элементы ИЛИ, первый 13 и второй 14 ключи, анализатор 15 шума, анализатор 16 входного сигнала, блок 17 коррекции цикла записи, решающий блок 18, блок 19 проверки фазы сигнала записи, блок 20 определения знака и величины сдвига сигнала записи, блок 21 определения знака сдвига входного сигнала, третий ключ 22, распределитель 23 записи, блок 24 элементов записи, SO блок 25 элементов буферной памяти, блок 26 элементов считывания, четвертый 27 и пятый 28 элементы ИЛИ, распределитель 29 считывания, выходной триггер 30.

25 Регенератор двоичных сигналов работает следующим образом.

Сигнал двоичной информации поступает на вход асинхронного приемника i, на выходах которого в зависимости от выход30 пого сигнала формируются импульсы, соответствующие границам элементарных посылок. Сформированные импульсы подаются в блок 24 для запоминания входной информации, а также для подстройки си5 стемы тактовой синхронизации импульсы поступают на вход блока 2. С выхода блока 2 через блоки 5 и 6 на вход счетчикараспределителя 7 поступает импульсный сигнал с частотой, превыщающей в 4 раза тактовую частоту /о. Счетчик-распределитель 7 рассчитан па четыре выхода и одиовременно выполняет функцию обычного счетчика на четыре, поэтому сигнал с четвертого выхода счетчика-распределителя 7 5 имеет тактовую частоту и управляет работой распределителя 23.

Чтобы не появлялись ощибки, когда амплитуда качаний входного сигнала совместно с шумовыми флуктуациями фазы граQ ниц посылок привысит половину длительности посылок, осуществляется слежение за фазой входного сигнала по отношению к опорному сигналу, каковым является сигнал четырехкратной тактовой частоты, g снимаемый с выхода блока 2, и изменение в соответствии с направлением и скоростью качаний фазы сигнала на входе счетчика-распределителя 7, что автоматически приводит к изменению фазы сигнала на входе счетчика-распределителя 7. При отсутствии качапий сигнала на входе регенератора фазовое положение не флуктуирующих границ посылок соответствует середине тактового периода импульсной 5 последовательности с четвертого выхода

счетчика-распределителя 7. Реальные шумовые флуктуации границ посылок не велики и находятся в прохтежутке ±JLTo,

что соответствует второму и третьему состояниям счетчика-распределителя 7.

Это не приводит к изменению фазы сигнала на выходе счетчика-распределителя 7. Сигналом с четвертого выхода счетчикараспределителя 7 управляется распределитель 23.

При наличии качаний входного сигнала для того, чтобы не появлялись ошибки При записи входной инфор.мации, осуществляется слежение за фазой входною сигнала по отношению к опорному сигналу, и изменяется фаза сигнала записи на ± 1/4то в соответствии с направлением и скоростью качаний фазы входного сигнала. Это осуществляется с но.мощью блоков 5 и 6, счетчика-распределителя 7, коммутатора 8 и счетчиков 9 и 10. Таким образом, происходит уменьшение вероятности ложного приема информанни и достигается высокая цикловая устойчивость тактовой синхронизации при быстрых качаниях фазы входного сигнала.

Работа регенератора при следующих возможных состояниях входного сигнала:

смена сильнозашумленного входного сигнал а-нормальным;

незначительное (до то) качание и флуктуация фронта входного сигнала;

медленные значительные (более TO) сдвиги фронтов входного сигнала;

резкие за одну-две посылки скачки фазы входного сигнала величиной более 1/2 То.

Анализаторы 15 и 16, постоянно анализируя входиой сигнал, выдают команды, сигнализирующие о поступлении на вход регенератора шума (сильнозашумленного сигнала) илн нормального входного сигнала. Анализаторы 15 и 16 представляют собой набор счетчиков, на вход которых подаются фронты входного сигнала. Анализ шума илн входного сигнала основан на реальном нормальном законе распределения фронтов входного сигиала в зоне их наиболее вероятного появления. В случае действия шума импульс-команда закрывает ключи 14 и 22. Этим исключается хаотическая подстройка сигнала записи фронтами шумов. Кроме того, тот же импульс сигнализирует о необходи.мости проверки фазы сигнала записи. В случае сдвига фазы сигнала записи, что определяет блок 19, поступает команда в блок 17 для проведения коррекции сигнала записи. Тем самым он подготавливается для записи входной информации в случае ее поступления. Блок 17 представляет собой генератор определенного числа импульсов для добавления их в последовательность импульсов, поступающих на вход счетчика-распреде6

лителя 7, или вычитания из этой последовательности. Число их зависит от величины коррекции, необходимой для восстановления фазы сигнала записи. Величину ухода сигнала записи относительно высокостабильного сигнала считывания постоянно определяет блок 19. При наличии нормального входного сигнала анализатор 16 подает ко.манду на ключи 14 и 22, открывая их и предоставляя воз.можность осуществлять слеженне за качаниями входного снгнала, беспрепятственно пропуская импульсы добавления или вычитания на в.ходы блоков 5 и 6.

При случайных флуктуациях фронтов входного сигнала или их незначительных медленных сдвигах происходит подстройка фазы сигнала записи с помощью счетчикараспределителя 7, коммутатора 8 и счетчиков 9 и 10 путем добавления или вычитания в блоках 5 и 6 одного импульса при смещении границ посылок более чем на 1/4То. Тем самым происходит слежение сигнала записи за смещающимися входными посылками. В блоках 20 и 21 (с тактом записи) определяется направление смещения фронта входного снгнала и подстройки фазы сигнала записи относительно высокостабильного сигнала считывания. А едленные качания фазы входного сигнала могут достигнуть величины, превышающей разрешающую способность буферной памяти, т. е. будет использовано возможное число подстроек, которое определяется емкостью блока 25 и пагом подстройки (емкостью счетчика-рас11редел1ггеля 7). В этом случае решающий блок 18 подает команду на блок 17 па восстановление цикла записи, устраняя тем самым возможные сбои по циклу.

При резких елучайных бросках фазы фронтов входного снгнала на величину больше чем 1/2 TO за одну-две посылки возможны ошибки, когда знаки сдвига фронтов входного сигнала и сигнала записи не будут совпадать в результате того, что неправильно опре/ц,елится критерий подстройки сигнала записи в системе коммутатор 8, счетчик-распределнтель 7, счетчики 9 и 10. Как только сигнал записи сдвинется на один шаг подстройки и знак подстройки не совпадет со знаком сдвига входного сигнала, сразу же по поступающим с блоков 20 и 21 импульсам-командам блок 18 определяет направление коррекции сигнала записи и ее величину, необходимую для исключения сбоев по циклу. По команде блока 18 блок 17 выдает необходимое число импульсов добавления или вычитания на входы блоков 5 или 6, сразу изменяя тем самым знак подстройки снгнала записи, причем изменится не только знак подстройки снгнала запио11 (согласно смещению входного сшпала), но и произойдет необходимая коррекция фазового рассогласования сигнала записи и входного сигнала. Дальнейи1ая подстройка будет производиться в соответстпи с возможными состояниями входного сигнала.

Формула изобретения

Регенератор двоичных сигналов, содержащий асинхронный приемник, выходы которого подключены к входам блока элементов записи и через первый элемент ИЛИ к первому входу блока синхронизации, выход задающего генератора подключен к входу асинхронного приемника и к второму входу блока синхронизации, первый выход которого через последовательно соединенные блок вычитания, блок добавления и счетчик-распределитель подключен к первым входам коммутатора, вторые входы которого соединены с выходом первого элемента ИЛИ, выход коммутатора подключен к первым входам первого и второго счетчнков, вторые входы которых соединены с другими выходами коммутатора, второй выход блока синхронизации подключен к первому входу первого ключа, выход которого подключен к первому входу распределителя записи и к первому входу распределителя считывания, соответствующий выход счетчика-распределителя подключен к второму входу распределителя записи, выходы которого через последовательно соединенные блок элементов записи, блок элементов .буферной памяти и блок элементов считывания подключены к входам соответствующих второго и третьего элементов ИЛИ, которых подключены к входам выходного триггера, соответствующий выход распределителя записи подключен к второму входу первого ключа, другой выход которого подключен к второму входу распределителя считывания, выходы которого подключены к другим входам блока элементов считывания, отличающийся тем, что, с целью повышения достоверности

приема двоичных сигналов, введены второй и третий ключи, четвертый и пятый элементы ИЛИ, анализатор щума, анализатор входного сигнала, блок коррекции цикла записи, рещающий блок, блок проверки фазы сигнала записи, блок определения знака и величины сдвига сигнала записи и блок определения знака сдвига входного сигнала, при этом выходы первого и второго счетчиков подключены к первым входам соответственно второго и третьего ключей, .выходы которых через четвертый и пятый элементы ИЛИ подключены к другим входам соответственно блока добавления и

блока вычитания, выход первого элемента ИЛИ подключен к входам анализатора щума и анализатора входного сигнала, выходы которых подключены к вторым и третьим входам второго и третьего ключей, соответствующий выход распределителя считывания подключен к первым входам блока проверки фазы сигнала записи, блока определения знака и величины сдвига сигнала записи и блока определения

знака сдвига входного сигнала, выходы которых через решающий блок подключены к первому входу блока коррекции цикла записи, выход блока проверки фазы сигнала записи подключен к второму

входу блока коррекции цикла записи, выходы которого подключены к другим входам четвертого и пятого элементов ИЛИ, выход первого элемента ИЛИ подключен к второму входу блока определения знака

сдвига входного сигнала, соответствующий вход блока элементов записи подключен к вторым входам блока определения знака и величины сдвига сигнала записи и блока проверки фазы сигнала записи, третий

вход которого с выходом анализатора щума.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке № 2535144/18-09, кл. Н 04 В 3/02, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Регенератор двоичных сигналов | 1977 |

|

SU743211A1 |

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| Двухступенчатый регенератор | 1983 |

|

SU1197117A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| Способ тактовой синхронизации и регенерации телеграфных сигналов и устройство для его осуществления | 1991 |

|

SU1830188A3 |

| Электронный распределитель | 1984 |

|

SU1170625A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Двухступенчатый регенератор | 1985 |

|

SU1317678A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

Авторы

Даты

1981-01-07—Публикация

1979-02-19—Подача