единичный выход которого соединен с управлякнцим входом второго элемента запрета, нулевой выход триггера является управляющим выходом модели, а информационные выходы счетчиков .начала и окончания работы являются соответственно первым и вторым информационными выходами модели.

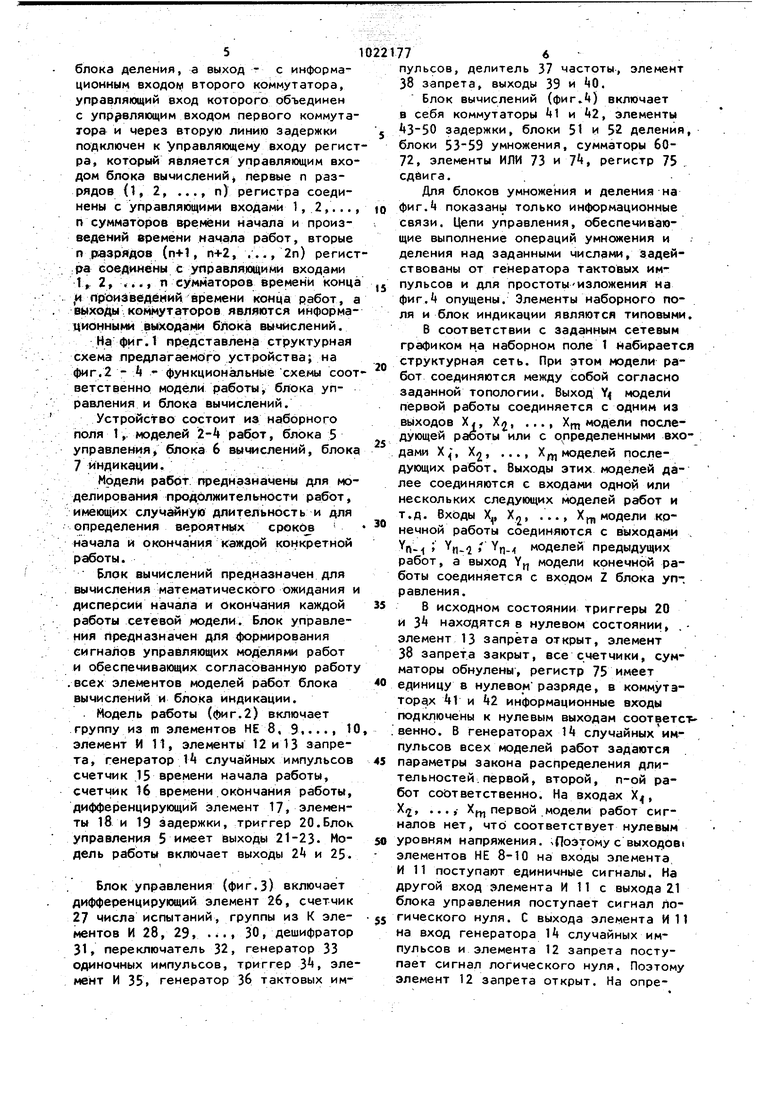

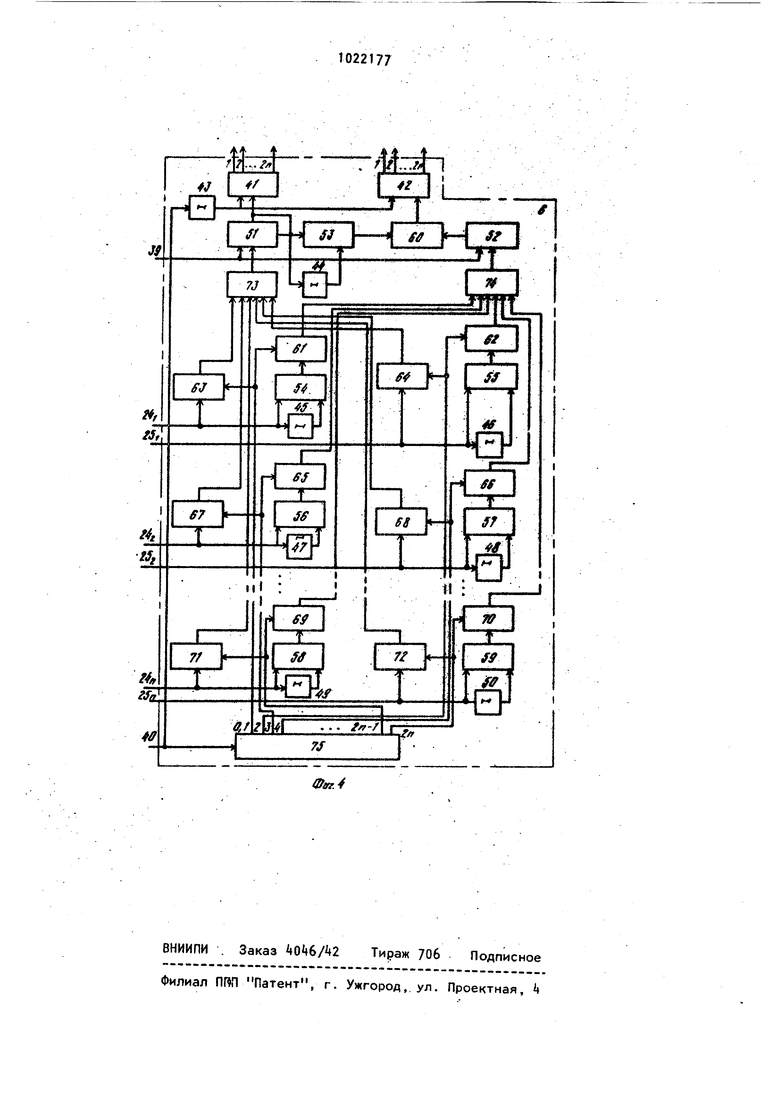

3. Устройство по п,1, о т л и ч .а ю щ е е с я тем, что управления содержит дифференцирующий элемент, вход которого является управляющим входом блока управления, счетчик числа испытаний, группу двухвходовых элементов И, дешифратор, переключатель триггер, генератор одиночных импульсов, триггер, элемент запрета, генератор импульсов, делитель частоты и элемент И, причем выход дифференцирующего элемента является вторым управляющим выходом блока управления и соединен с входом счетчика числа испытаний, разрядные выходы которого соединены с входами дешифратора и информационными входами группы двухвходовых элементов И, выходы которого объединены и являются вторым информационным выходом блока управления, выходы дешифратора подключены к входам neiреключателя, выход которого соединен с нулевым входом триггера, единичный вход которого подключен к выходу ге.нератора одиночных импульсов, единичный выход является первым управляющим выходом блока управления, нулевой выход триггера соединен с управляющим входом элемента запрета и первым входом элемента И, выходкоторого является четвертым управляющим выходом блока управления и соединен с управляющими входами группы двухвходовых элементов И, выход генератора импульсов подключен к входу делителя частоты и информационному входу элемента запрета, выход которого является первым информационным выходом блока управления, а выход делителя частоты соединен с вторым входом элемента И.

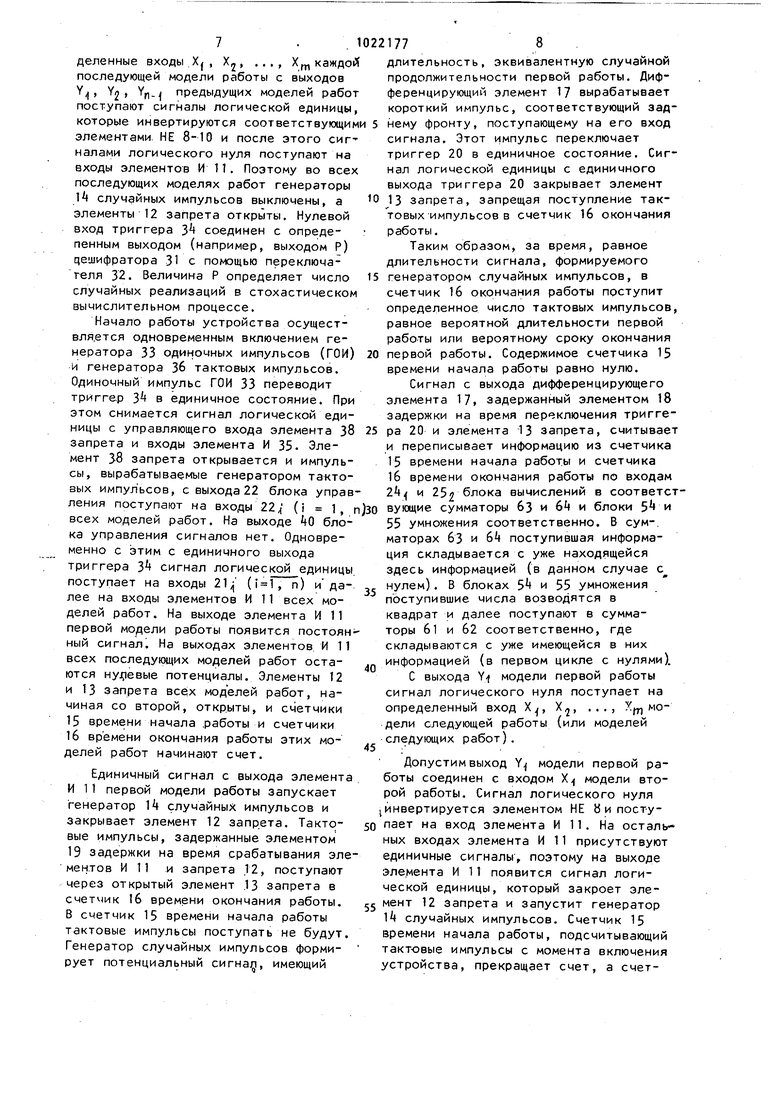

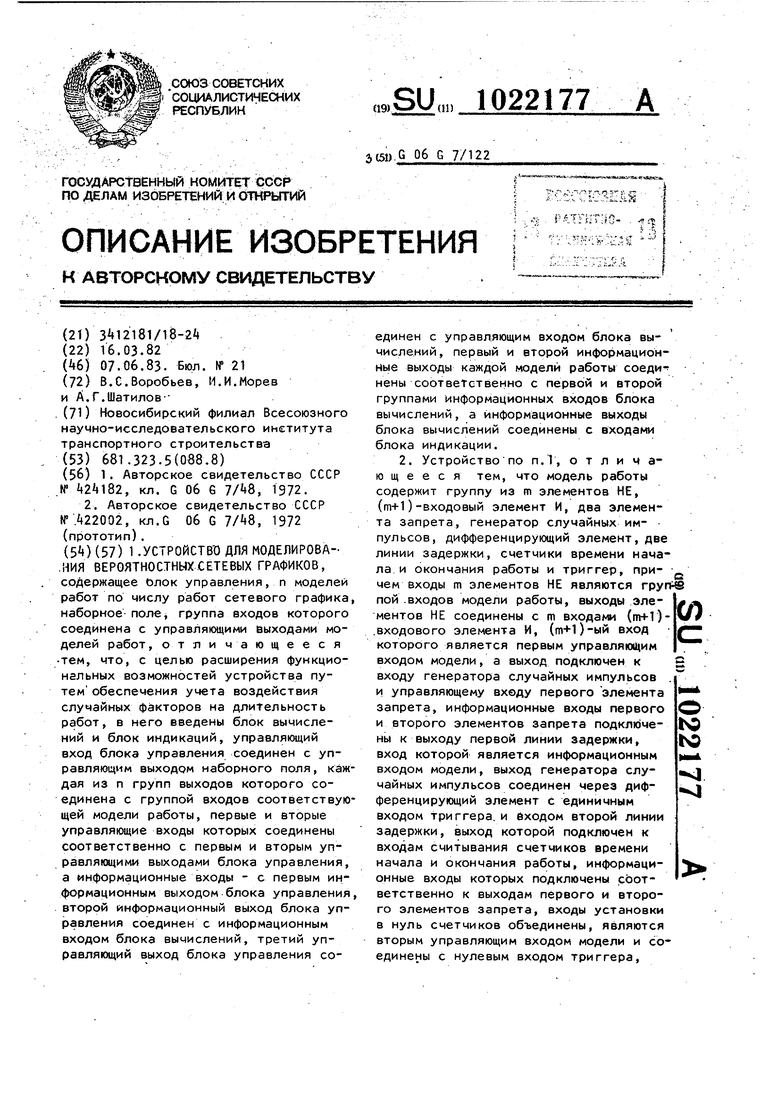

k. Устройство по п.1, о т л и ч аю 1Д е е с я тем, что блок вычислений содержит группы из п сумматоров времени начала и окончания работ, группы из п блоков умножения времени начала и окончания работ, две группы из п линий задержки, группы из п сумматоров произведений времени начала и окончания работ, первый и второй 2пвходовый элемент ИЛИ, первый и второй блоки деления, две линии задержки, блок умножения, сумматор, два коммутатора и 2п-разрядный регистр, причем информационные входы групп сумматоров времени начала и окончания работы объединены по группам, являются первой и второй группами информационных входов блока вычислений и соединены соответственно с первыми информационными входами групп блоков умножения бремени начала и окончания работ и через первую и вторую группы линий задержки - с вторыми информационными входами

блоков умножения времени начала и окончания работ, выходы сумматоров времени начала и окончания работ подключены к входам первого элемента ИЛИ, выходы групп блоков умножений времени начала и окончания работ соединены соответственно с информационными входами групп сумматоров произведений времени начала и окончания работ, выходы которых подключены к входам второго элемента ИЛИ, выходы первого и

втерого элементов ИЛИ соединены соответственно с первыми информационными

входами первого, и второго блоков деления , вторые информационные входы которых объединены и являются информационным входом блока вычислений, выход первого блока деления соединен с информационным входом первого коммутатора, первым информационным входом блока умножения и через первую линию задержки с его вторым информационным входом, выход блока умножения подключен к первому информационному входу сумматора, второй информационный

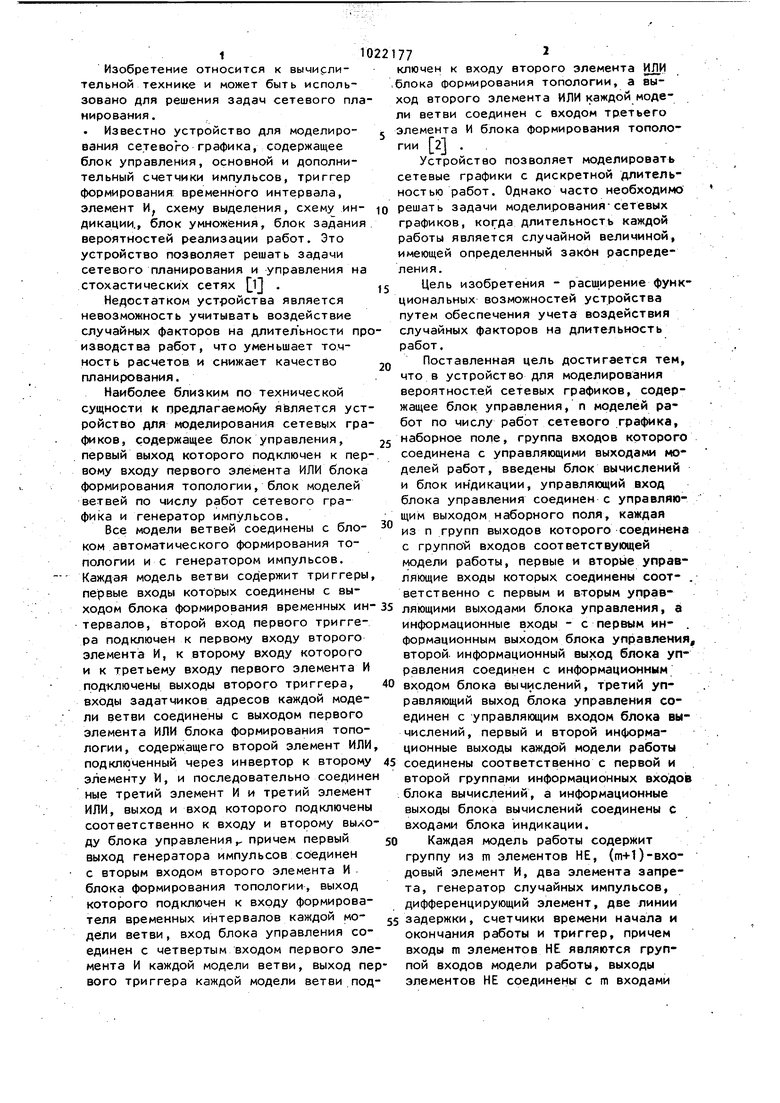

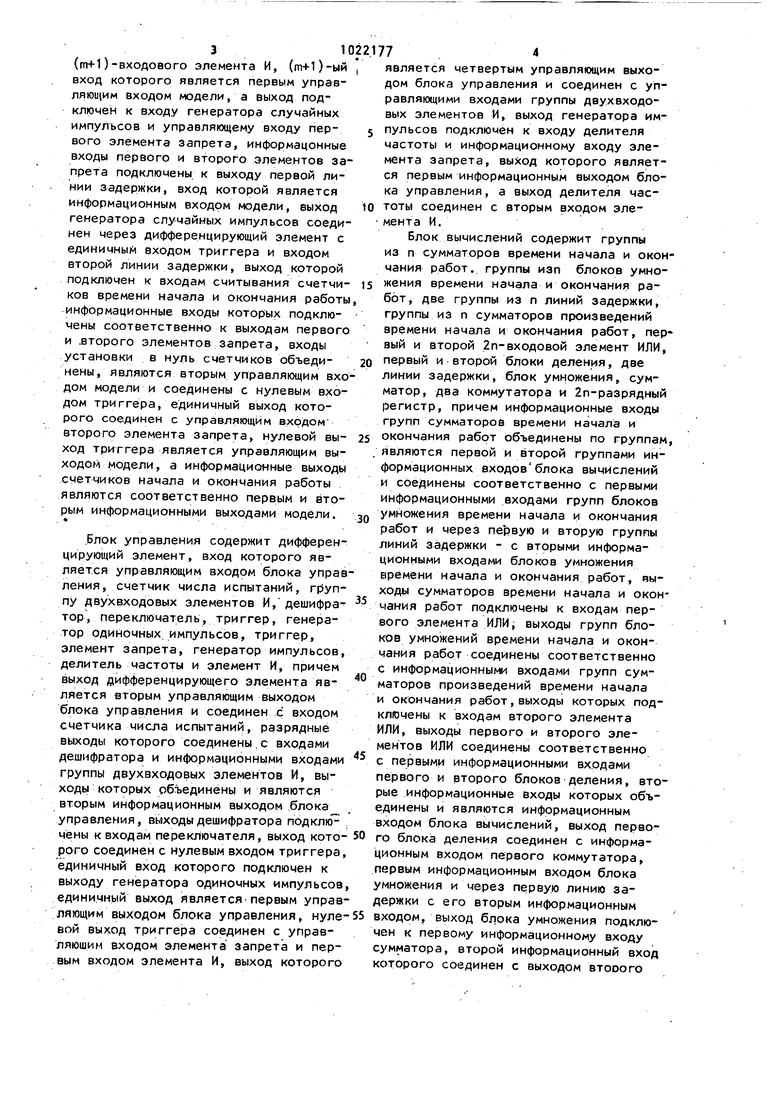

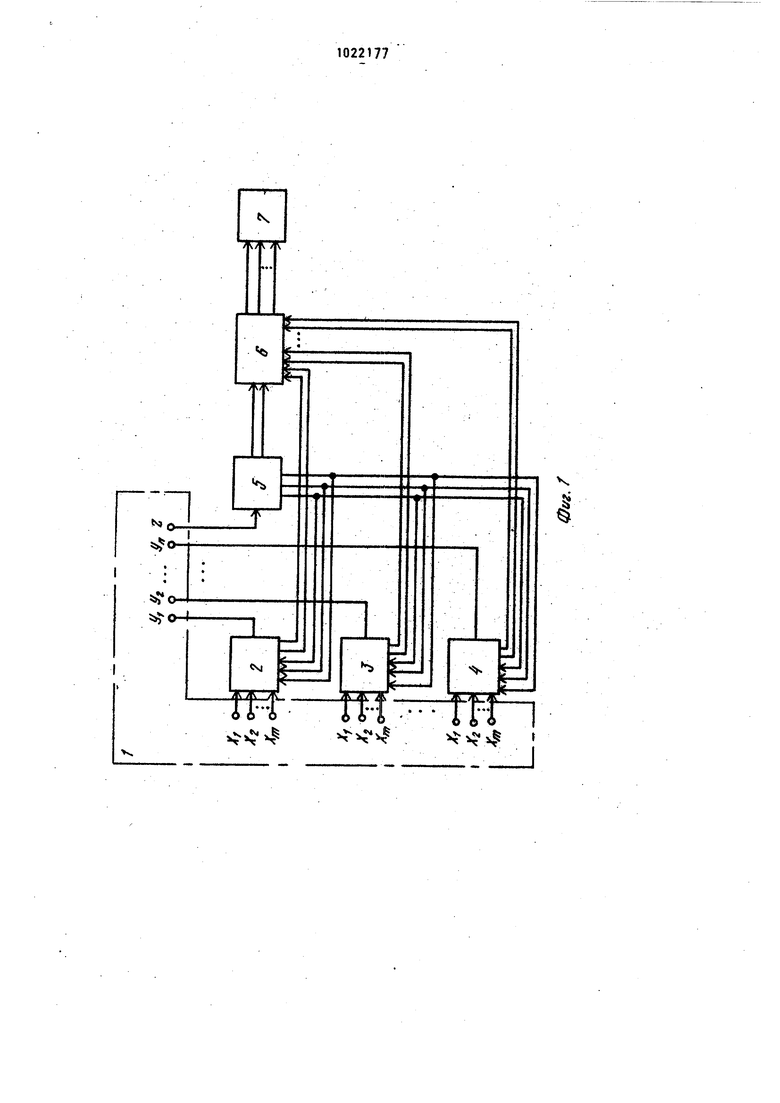

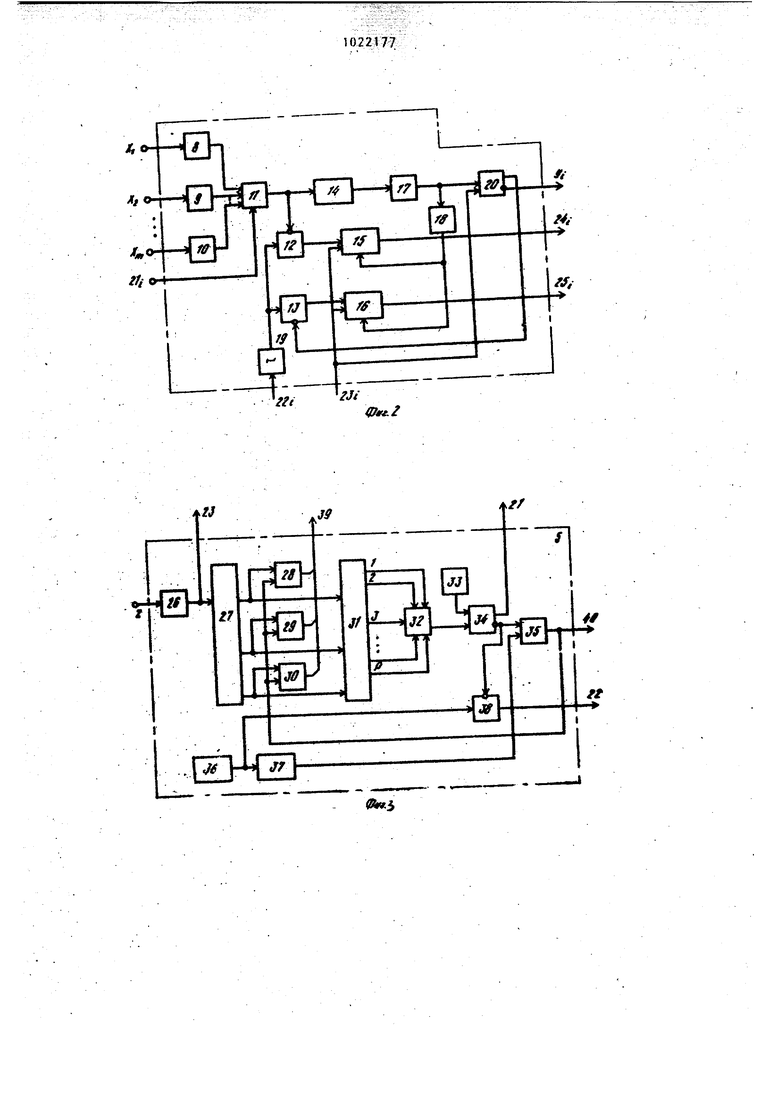

вход которого соединен с выходом второго блока деления, а выход - с информационным входом второго коммутатора, управляющий вход которого объединен с управляющим входом первого коммутатора и через вторую линию задержки подключен к управляющему входу регистра, который является управляющим вхоом блока вычислений, первые п разрядов (1, 2, ..., п) регистра соединены с управляющими входами 1, 2, ..., п сумматоров времени начала и произвеений времени начала работ, вторые п разрядов (п+1, п+2, ..,, 2п) регистра соединены с управляющими входами 1, 2, ..., п сумматоров времени конца и произведений времени конца работ, а выходы коммутаторов являются информационными выходами блока вычислений. 11 Изобретение относится к вычислительной технике и может быть использёвано для решения задач сетевого пла нирования . Известно устройство для моделирования сетевого графика, содержащее блок управления, основной и дополнительный счетчики импульсов, триггер формирования: временного интервала, элемент И, схему выделения, схему индикации., блок умнож1°ния, блок задания вероятностей реализации работ. Это устройство позволяет решать задачи сетевого планирования и управления на стохастических сетях lj , Недостатком устройства является невозможность учитывать воздействие случайных факторов на длительности пр изводства работ, что уменьшает то.чность расчетов и снижает качество планирования. Наиболее близким по технической сущности к предлагаемому является уст ройство для моделирования сетевых гра фиков, содержащее блок управления, первый выход которого подключен к пер вому входу первого элемента ИЛИ блока формирования топологии, блок моделей ветвей по числу работ сетевого графика и генератор импульсов. Все модели ветвей соединены с блоком автоматического формирования топологии и с генератором импульсов. Каждая модель ветви содержит триггеры первые входы которых соединены с выходом блока формирования временных ин тервалов, второй вход первого триггера подключен к первому входу второго элемента И, к второму входу которого и к третьему входу первого элемента И подключены выходы второго триггера, входы задатчиков адресов каждой модели ветви соединены с выходом первого элемента ИЛИ блока формирования топологии, содержащего второй элемент ИЛИ, подключенный через инвертор к второму элементу VI, и последовательно соединен Hbie третий элемент И и третий элемент ИЛИ, выход и вход которого подключены соответственно к входу и второму вылоду блока управления,, причем первый выход генератора импульсов соединен с вторым входом второго элемента И блока формирования топологии, выход которого подключен к входу формирователя временных интервалов каждой модели ветви, вход блока управления соединен с четвертым входом первого элемента И каждой модели ветви, выход пер вого триггера каждой модели ветви под772ключен к входу второго элемента ИЛИ блока формирования топологии, а выход второго элемента ИЛИ каждой модели ветви соединен с входом третьего элемента И блока формирования топологии 2J . , Устройство позволяет моделировать сетевые графики с дискретной длительностью работ. Однако часто необходимо решать задачи моделирования-сетевых графиков, когда длительность каждой работы является случайной величиной, имеющей определенный закбн распределения. Цель изобретения - расширение функциональных возможностей устройства путем обеспечения учета воздействия случайных факторов на длительность работ. Поставленная цель достигается тем, что в устройство для моделирования вероятностей сетевых графиков, содержащее блок управления, п моделей работ по числу работ сетевого графика, наборное поле, группа входов которого соединена с управляющими выходами моделей работ, введены блок вычислений и блок индикации, управляющий вход блока управления соединен с управляющим выходом наборного поля, каждая из п групп выходов которого соединена с группой входов соответствующей модели работы, первые и вторые управляющие входы которых соединены соот- . ветственно с первым и вторым управляющими выходами блока управления, а информационные входы - с первым информационным выходом блока управления, второй информационный выход блока управления соединен с информационным входом блока вычислений, третий управляющий выход блока управления соединен с управляющим входом блока вычислений , первый и второй информационные выходы каждой модели работы соединены соответственно с первой и второй группами информационных входов блока вычислений, а информационные выходы блока вычислений соединены с входами блока индикации. Каждая модель работы содержит группу из m элементов НЕ, (т+1)-входовый элемент И, два элемента запрета, генератор случайных импульсов, дифференцирующий элемент, две линии задержки, счетчики времени начала и окончания работы и триггер, причем входы m элементов НЕ являются группой входов модели работы, выходы элементов НЕ соединены с m входами (m4-1 )-входового элемента И, (т+1)ый вход которого является первым управляющим входом модели, а выход подключен к входу генератора случайных импульсов и управляющему входу первого элемента запрета, информацонные входы первого и второго элементов запрета подключены, к выходу первой линии задержки, вход которой является информационным входом модели, выход генератора случайных импульсов соединен через дифференцирующий элемент с единичный входом триггера и входом второй линии задержки, выход которой подключен к входам считывания счетчиков времени начала и окончания работы информационные входы которых подключены соответственно к выходам первого и .второго элементов запрета, входы установки в нуль счетчиков объедииены, являются вторым управляющим вхо дом модели и соединены с нулевым входом триггера, единичный выход которого соединен с управляющим вхрДом второго элемента запрета, нулевой выход триггера является управляющим выходой модели, а информационные выходы сметчиков начала и окончания работы являются соответственно первым и вторым информационными выходами модели. Блок управления содержит дифференцирующий элемент, вход которого является управляющим входом блока управ ления, счетчик числа испытаний, группу двухвходовых элементов И, дешифратор, переключатель, триггер, генератор одиночных импульсов, триггер, элемент запрета, генератор импульсов, делитель частоты и элемент И, причем выход дифференцирующего элемента является вторым управляющим выходом блока управления и соединен с входом счетчика числа испытаний, разрядные выходы которого соединены.с входами дешифратора и информационными входами группы двухвходовых элементов И, выходы которых рбпэединены и являются вторым информационным выходом .блока управления, выходы дешифратора подклюиены к входам переключателя, выход кото рого соединен с нулевым входом триггера единичный вход которого подключен к выходу генератора одиночных импульсов единичный выход является первым управ ляющим выходом блока управления, нуле аой выход триггера соединен с управляющим входом элемента запрета и первым входом элемента И, выход которого является четвертым управляющим выходом блока управления и соединен с управляющими входами группы двухвходовых элементов И, выход генератора импульсов подключен к входу делителя частоты и информационному входу элемента запрета, выход которого является первым информационным выходом блока управления, а выход делителя частоты соединен с вторым входом элемента И.. Блок вычислений содержит группы из п сумматоров времени начала и окончания работ, группы изп блоков умножения времени начала и окончания работ, две группы из п линий задержки, группы из п сумматоров произведений времени начала и окончания работ, первый и второй 2п-входовой элемент ИЛИ, первый и второй блоки деления, две линии задержки, блок умножения, сумматор, два коммутатора и 2п-разрядный регистр, причем информационные входы групп сумматоров времени начала и окончания работ объединены по группам, являются первой и второй группами информационных входов блока вычислений и соединены соответственно с первыми информационными .входами групп блоков умножения времени начала и окончания работ и через первую и вторую группы линий задержки - с вторыми информационными входами блоков умножения времени начала и окончания работ, выходы сумматоров времени начала и окончания работ подключены к входам первого элемента ИЛИ; выходы групп блоков умножений времени начала и окончания работ соединены соответственно с информационными входами групп сумматоров произведений времени начала и окончания работ,выходы которых подключены к входам второго элемента ИЛИ, выходы первого и второго элементов ИЛИ соединены соответственно с первыми информационными вх.одами первого и второго блоков деления, вторые информационные входы которых объединены и являются информационным входом блока вычислений, выход первого блока деления соединен с информационным входом первого коммутатора, .первым информационным входом блока умножения и через первую линию задержки с его вторым информационным входом, выход блока умножения подключен к первому информационному входу сумматора, второй информационный вход которого соединен с выходом ВТОРОГО 5 блока деления, а выход - с информационным входом второго коммутатора, управляющий вход которого объединен с управляющим входом первого коммутатора и через вторую линию задержки подключен к управляющему входу регист ра, который является управляющим входом блока вычисленийj первые п разрядов {1,2, ..., п) регистра соединены с управляющими входз) 1,2,... п сумматоров времени начала и произведений времени начала работ, вторые п разрядов (п+1, п-н2, ..., 2п) регист :ра соединены с управляющими входами 1 2, ..., п сумматоров времени конца ,й произведений времени конца работ, а коммутаторов являются информационными выходами блока вычислений. На фиг,t представлена структурная схема предлагаемого устройства; на фиг.2 - k функциональные схемы соот ветственно модели работы у блока управления и блока вычислений. Устройство состоит из наборного поля 1.моделей 2-4 работ, блока 5 управления блока 6 вычислений, блока 7 индикации. ; Модели работ предназначены для моделирования продолжительности работ, имеющих случайную длительность и для определения вероятных сроков начала и окончания каждой конкретной работы. блок вычислений предназначен для вычисления математического ожидания и дисперсии н ачала и окончания каждой работы сетевой модели. Блок управления Предназначен для формирования сигналов управляющих моделями работ и обеспечивающих согласованную работу .всех элементов моделей работ блока вычислений и блока индикации. Модель работы (фиг.2) включает группу из m элементов НЕ 8, 9,..., Ю элемент И 11, элементы 12 и 13 запрета, генератор I случайнь х импульсов счетчик 15 времени начала работы, счетчик 16 времени окончания работы, дифференцирующий элемент 17, элементы 18 и 19 задержки, триггер 20.Блок управления 5 имеет выходы 21-23- Модель работы включает выходы 2 и 25. Блок управления (фиг.З) включает дифференцирующий элемент 26, счетчик 27 числа испытаний, группы из К элементов И 28, 29, ..., 30, дешифратор 31, переключатель 32, генератор 33 одиночных импульсов, триггер 3, эле мент И 35, генератор 3$ тактовых им7«пульсов, делитель 37 частоты, элемент 38 запрета, выходы 39 и lO. Блок вычислений (фиг.) включает в себя коммутаторы и 2, элементы 43-50 задержки, блоки 51 и 52 деления, блоки умножения, сумматоры 6072, элементы ИЛИ 73 и 74, регистр 75 . сдйига. Для блоков умножения и деления на фиг.4 показаны только информационные связи. Цепи управления, обеспечивающие выполнение операций умножения и деления над заданными числами, задействованы от генератора тактовых импульсов и для простоты-изложения на фиг.4 опущены. Элементы наборного поля и блок индикации являются типовыми. В соответствии с заданным сетевым графиком н.а наборном поле 1 Забирается структурная сеть. При этом модели работ соединяются между собой согласно заданной топологии. Выход Y модели первой работы соединяется с одним из выходов X/, Xj, ..., Xm модели последующей работы или с определенными вхо- : дами , Х2, ..., Х моделей последующих работ. Выходы этих моделей далее соединяются с входами одной или нескольких следующих моделей работ и т.д. Входы Х, Xj, ..., Xfn модели конечной работы соединяются с выходами УП-Ч n-l моделей предыдущих работ, а выход Y модели конечной работы соединяется с входом Z блока уп-. равления. В исходном состоянии триггеры 20 и 34 находятся в нулевом состоянии, ,элемент 13 запрета открыт, элемент 38 запрета закрыт, все счетчики, сумматоры обнулены, регистр 75 имеет единицу в нулевомразряде, в коммутатордх 41 и 42 информационные входы подключены к нулевым выходам соответственно. В генераторах 14 случайныхимпульсов всех моделей работ задаются параметры закона распределения длительностей, первой, второй, п-ой работ соответственно. На входах Х, Х, ... , Xf первой модели работ сигналов нет, что соответствует нулевым уровням напряжения. Поэтому с выходов элементов НЕ 8-10 на входы элемента И 11 поступают единичные сигналы. На другой вход элемента И 11 с выхода 21 блока управления поступает сигнал логического нуля. С выхода элемента И 11 на вход генератора 14 случайных импульсов и элемента 12 запрета поступает сигнал логического нуля. Поэтому элемент 12 запрета открыт. На определенные входы Xj, Х,, ..., Xf каждой последующей модели работы с выходов 2 предыдущих моделей работ поступают сигналы логической единицы, которые инвертируются соответствующим элементами. НЕ 8-10 и после этого сиг налами логического нуля поступают на входы элементов И 11. Поэтому во всех последующих моделях работ генераторы И случайных импульсов выключены, а элементы 12 запрета открыты. Нулевой вход триггера 34 соединен с опредепенным выходом (например, выходом Р) дешифратора 31 с помощью переключателя 32. Величина Р определяет число случайных реализаций в стохастическом вычислительном процессе. Начало работы устройства осуществляется одновременным включением генератора 33 одиночных импульсов (ГОИ) и генератора 36 тактовых импульсов. Одиночный импульс ГОИ 33 переводит триггер 3 в единичное состояние. При этом снимается сигнал логической единицы с управляющего входа элемента 38 25 ра запрета и входы элемента И 35. Элемент 38 запрета открывается и импуль сы, вырабатываемые генератором такто вых импульсов, с выхода 22 блока упра ления поступают на входы 22 (i 1, всех моделей работ, На выходе tO бло ка управления сигналов нет. Одновременно с этим с единичного выхода триггера З сигнал логической единицы поступает на входы (i 1, п) идалее на входы элементов И 11 всех моделей работ. На выходе элемента И 11 первой модели работы появится постоян ный сигнал. На выходах элементов И 11 всех последующих моделей работ остаются иу 1евые потенциалы. Элементы 12 и 13 запрета всех моделей работ, начиная со второй, открыты, и счетчики 15времени начала .работы и счетчики 16времени окончания работы этих моделей работ начинают счет. Единичный сигнал с выхода элемента И 11 первой модели работы запускает генератор случайных импульсов и закрывает элемент 12 запрета. Тактовые импульсы, задержанные элементом 19 задержки на время срабатывания эле ментов И 11 и запрета .12, поступают через открытый элемент .13 запрета в счетчик 16 времени окончания работы. В сметчик 15 времени начала работы тактовые импульсы поступать не будут. Генератор случайных импульсов формирует потенциальный сигна, имеющий 1 1778 длительность, эквивалентную случайной продолжительности первой работы. Дифференцирующий элемент 17 вырабатывает короткий импульс, соответствующий заднему фронту, поступающему на его вход сигнала. Этот импульс переключает триггер /1U в единичное состояние. Сигнал логической единицы с единичного выхода триггера 20 закрывает элемент 13 запрета, запрещая поступление тактовых импульсов в счетчик 16 окончания работы. Таким образом, за время, равное длительности сигнала, формируемого генератором случайных импульсов, в счетчик 16 окончания работы поступит определенное число тактовых импульсов, равное вероятной длительности первой работы или вероятному сроку окончания первой работы. Содержимое счетчика 15 времени начала работы равно нулю. Сигнал с выхода дифференцирующего элемента 17, задержанйый элементом 18 задержки на время переключения тригге20 и элемента 13 запрета, считывает и переписывает информацию из счетчика 15времени начала работы и счетчика 16времени окончания работы по входам 2 и 252 б-пока вь1числений в соответствующие сумматоры 63 и 6й и блоки 5 и 55 умножения соответственно. В сум-, маторах 63 и 6k поступившая информация складывается с уже находящейся здесь информацией (в данном случае с нулем), В блоках 5 и 55 умножения поступившие числа возводятся в квадрат и далее поступают в сумматоры б1 и б2 соответственно, где складываются с уже имеющейся в них информацией (в первом цикле с нулями). С выхода Y-i модели первой работы сигнал логического нуля поступает на т оопределенный вход Х, Х, дели следующей работы (или моделей следующих работ). Допустим выход Y модели первой работы соединен с входом Х модели второй работы. Сигнал логического нуля инвертируется элементом НЕ Ьипост-упает на вход элемента И 11, На остальных входах элемента И 11 присутствуют единичные сигналы, поэтому на выходе эле.мента И 11 появится сигнал логической единицы, который закроет элемент 12 запрета и запустит генератор 14 случайных импульсов. Счетчик 15 времени начала работы, подсчитывающий тактовые импульсы с момента включения устройства, прекращает счет, а счет91чик 16 окончания работы продолжает счет. Генератор 1 случайных импульсо вырабатывает случайный сигнал, имеющий длительность, эквивалентную случайной п эодолжительности второй работы. Дифференцирующий элемент 17 формирует импульс, соответствующий заднему фронту случайного сигнала. Этот Импульс устанавливает триггер 20 в единичное состояние. Сигнал логической единицы с единичного выхода триггера 20 закрывает элемент 13 запрета и счетчик 16 времени окончания работы прекращает счет. ,С. выхода дифференцирующего элемента 17 импульс, задержанный элементом 18 задержки, поступает на входы чтения счетчика 15 времени начала работы и счетчика 16 времени окончания работы. Информация о вероятных сроках начала и окончания второй работы переписывается по входам 242 и 252 блока вычислений в сумматоры 67 и 68 и блоки 5б и 57 умножения соответственно. В сумматорах 67 и 68 производятся операции сложения информации о начале второй работы с нулем и сложение информации об окончании второй работы с нулем соот ветственно. В блоках 56 и 57 умножения производятся операции по возведе нию в квадрат чисел,, характеризующих время начала и окончания второй рабо ты. С выходов блоков 56 и 57 умножения информация передается на входы .сумматоров 65 и 66, где складывается ,с имеющейся здесь информацией (в пер |вом цикле с нулями). На выходе модели второй работы появляется сигн логического нуля, воздействующий на заданные входы Х, Х, .-.., Х следующих моделей работ. Если выходы .j , ..., Y.2- нескольких моделей работ скоммутированы с входами Х, Х, ..., Xj последующей i-ой модели работы, то на выходе элемента И 11 i-ой модели работы будет присутствовать сигнал логического нуля до тех пор, пока на всех этих входах Х, Х, ..., X: не появятся сигналы логического нуля, т.е. пока триггеры 20.j , i-2, i-1-ой работ не переключатся в единичное состояние. Таким образом, моделирует ся тот факт, что данная работа не мо жет начаться, если не закончены все предшествующие ей работы. При окончании завершающей п-ой ра боты информация о вероятных сроках начала и окончания п-ой работы пере7710исывается по входам 2, 25.п блока вычислений в сумматоры 71 и 72 и блоки 58 и 59 умножения. 8 результате выполнения операций сложения и умноенив получаем в сумматорах. 7 72 информацию о времени начала и окончания п-ой работы, а в блоке 58 умножения, сумматоре 69 и в блоке 59 умножения, сумматоре 70 - квадраты этих величин соответственно. В модели п-ой работы триггер 20 переключается в единичное состояние и с выхода Y на вход 2 блока управления поступает сигнал логического нуля. По перепаду уровней сигнала на входе дифференцирующий элемент 26 формирует импульс, который поступает на вход счетчика 27 числа испытаний и с выхода 23 6лока управления через входы 23; (,n) моделей работ поступает на входы установки в нуль счетчиков 15 начала работ, счетчиков 1б окончания работ и триггеров 20 всех моделей, работ. Счетчики 15 и 1б всех моделей работ обнуляются. Триггеры 20 всех моделей работ переключа- , ются в нулевое состояние, в результате чего элементы .13 запрета всех моделей работ открываются. На входах Yj, Y появляются единичные сигнакоторые, поступая на входы Х, Хп,..., Xf всех моделей работ, начиная со второй, обуславливают открывание элементов 12 запрета этих моде-, лей работ. Элементы 12 запрета модели первой работы остаются закрытыми. В счетчик 27 числа, испытаний записывается единица. В результате первой реализации вычислений для первой работы получаем: содержимое сумматора 63 равно а ; содержимое сумматора .61 равно , где а(,,- время нача-; ла первой работы, полученное в первой испытании.Содержимое сумматорабД рав-. но b f, содержимое сумматора 62 равно Ь ,где . окончания первой работы, полученное в первой реализации. Таким оЬразом, завершен первый цикл расчета (или первое испытание) сетевой модели и устройство автоматически начинает второй цикл. Он начинается с моделирования первой работы и протекает аналогично первому циклу. После выполнения каждой работы результаты моделирования, а именно сроки начала и окончания каждой работы, переписываются из счетчиков 13 времени начала работы и счетчиков 16 времени окончания работы каждой модели работ в соответстёующие сумматоры и блоки умножения, где производятся вычисления. После окончания завершающей работы с выхода Y на вход Z блока управления вновь поступит сигнал, кото рый обнулит счетчики 15 времени нача ла работ, счетчики 16 времени оконча ния работ, триггеры 20 всех моделей работ и добавит в счетчик 27 числа испытаний единицу. Содержимое СЧетчи ка 27 станет равным двум. В результа те вычислений для первой pa6otM полу чаем: содержимое сумматора-63 равно laeM. ьодержимие 1,уммс11u(ja-uj aoпv 1 + a, ; содержимое сумматора 6l а laBKO + з,2 ------ работы, .полученное вс начала первой работы, .полученное во втором испытании; содержимое суммато 1ытании; содержимое суммат ра 6 равно но Ь, + Ь,,2 содержимое 62 равно 4,4 , где сумматора Ь 2. время окончанияпервой работы, полученное во втором испытании. После завершения Р-го цикла с выхода У,-,на вход Z блока управления поступит сигнал, который обнулит счетчики 15 и 16 времени начала и оквнчани я рабсэт и триггеры 20 всех моделей работ и добавит в счетчик числа испытаний очередную единицу. Н выходе Р-го разряда дешифратора 31 появится сигнал, который через переключатель 32 установит триггер 3 в нулевое состояние. На выходе 21 блок управления единичный сигнал исчезнет .Элемент запрета закроется, запретив {прохождение тактовых импульсов на вх ды моделей работ. Через открытый эле мент И 35 с выхода делителя 37 частоты управляющие импульсы поступают на входы группы из К элементов И 28, 29, ..., 30, обеспечивая периодическое чтение содержимого счетчика 27 числа испытаний, и на вход Q блока вычислений. К этому моменту сумматор блока вычислений будут содержать определенную информацию. Например, для первой работы содержимое сумматора 6 ( Р равно Z. Ь.;, . содержимое сумматора |„ 1 т - Р ; 63 равно 51 а i- содержимое суммато ра 61 равно Z а содержимое сумм - i Р /2 тора 62 равно; °t Импульсы, посту1пающие на вход АО блока вычислений, попадают на вход регистра 75 сдвига и переписывая единицу из нулевого разряда в первый, далее во торой, тре177тий и т.д., обеспечивают последовательное формирование сигналов На разрядных выходах регистра 75. При поступлении на вход регистра 75 первого импульса на выходе первого разряда появится сигнал, который считывает информацию из сумматора 63 и б1 и передает ее через соответствующие элементы ИЛИ 73 и 7| в блоки 51 и 52 деления соответственно. По входу 39 в блоки 51 и 52 деления поступает информация из счетчика 27 числа испытаний (а данном случае число). После выполнения операции деления в блоке 51 деления прлучаем математическое ожидание времени начала первой работы; ,., -г Zi 0(л:. Эта информация постут.е. ЛЛ , .пает на первый выход коммутатора 1, поскольку по сигналу, поступившему с выхода Элемента задержки, вход ком;мутатора 1 подключен к его первому ;выходу. Далее информация поступает в блок индикации. Одновременно эта информация поступает в блок 53 умноже.ния, где выполняется операция возведения числа в квадрат. В результате выполнения этой операции на выходе блока 53 умножения получаем число .в результате в.1полнения операции, деления в блоке 52 деления, получаем . промежуточный результат .торыи поступает на первый вход сумматора 60. На второй вход сумматора 60 поступает число из блока 53 умножения. Сумматор 60 выполняет операцию вычитания, в результате чего получаем величину дисперсии для начала первой работы, т.е. -„ Р ч с,,°. выхода сумматора 60.эта величина поступает через первый выход коммутатора 42 в блок индикации. При поступлении на вход регистра 75 второго импульса на выходе второго разряда регистра появится сигнал, который считывает информацию из сумматоров 64 и 62 и передает ее через соответствующие элементы ИЛИ 73 и 74 в блоки 31 и 52 деления соответственно. По входу 39 в блоки 51 и 52 деления поступает число р из счетчика 27 числа испытаний. В блоках деления 51 и 52 блоке 53 умножения, сумматоре 60 производятся соответствующие операции Р . к величинами 13 зультате получаемна выходе блока 51 деления величину математического ожидания окончания первой работы, т.е. М,: о Ц ) Эта информация посту Р fTi коммутатрра il. К этому паетна вход моменту входы коммутаторов 41 и сигналом с выхода элемента задержки переключаются к вторым выходам. Число с второго выхода коммутатора поступает в блок индикации. На выходе сумматора 60 получает) величину дисперсии для окончания первой раРботы, т.е. ,. Число Р- С второго выхода коммутатора поступает в блок индикации. При поступлении на вход регистра 75 третьего, четвертого, ..., 2п-ого 7 ц, шпульсов на выходах 3 . 2п коммутаторов 41 и k2 последовательно получаем величины математического ожидания и дисперсии времени начала, математического ожидания и дисперсии времени окончания второй, третьей, ..., п-ой работ соответственно. Частота импульсов на выходе делителя 37 частоты выбирается такой, чтобы за время между двумя соседними импульсами успели закончиться операции вычисления математического ожидания и дисперсии для начала или окончания очередной работы. Таким образом, предлагаемое устройство позволяет производить расчет сетевых графиков в условиях случайных длительностей отдельных работ.

//

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетевых графиков | 1983 |

|

SU1104524A1 |

| Устройство управления невзрывными источниками сейсмических колебаний | 1985 |

|

SU1267323A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1223244A1 |

| Цифровой коррелометр | 1979 |

|

SU783797A1 |

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

| Устройство для определения производной корреляционной функции | 1985 |

|

SU1305713A1 |

| Генератор случайного процесса | 1982 |

|

SU1068935A1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ИМПУЛЬСОВ | 1992 |

|

RU2032987C1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

М-4 г 4|гзН

Г

Авторы

Даты

1983-06-07—Публикация

1982-03-16—Подача