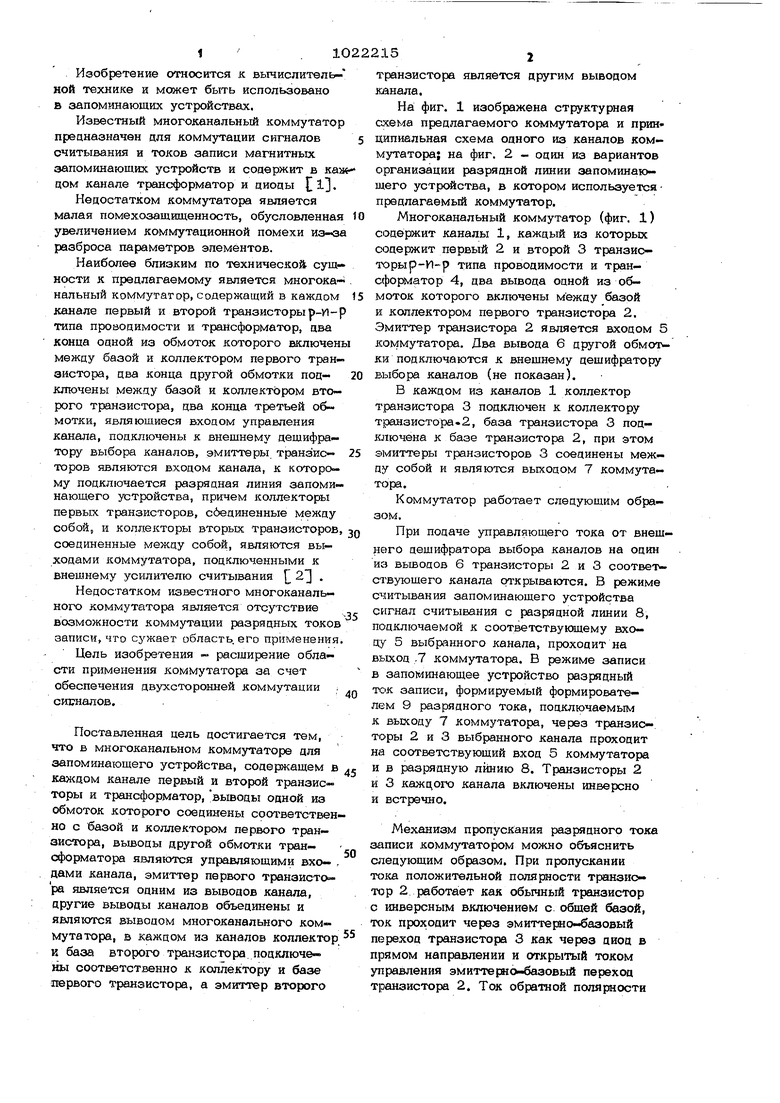

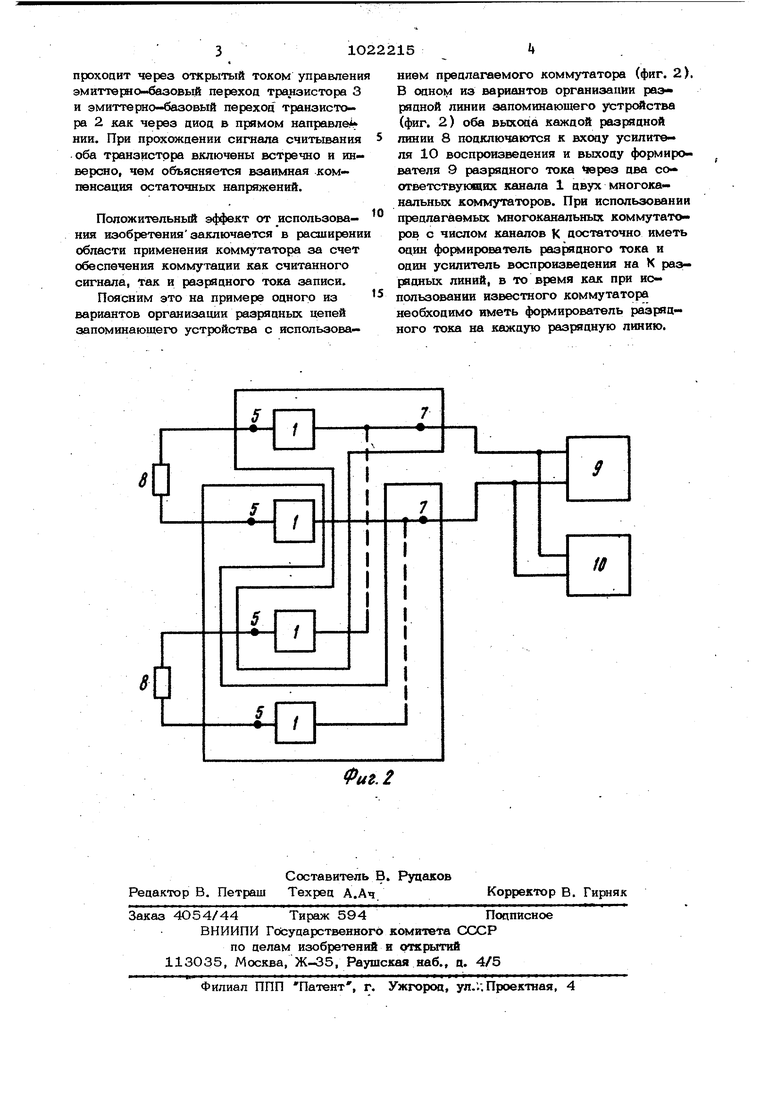

t. 1 Изобретение отнсюится к вычислительной технике и может быть использовано в запоминающих устройствах. Известный многоканальный коммутатор прецназначен для коммутации сигналов считывания и токов записи магнитных запоминающих устройств и содержит в ка дом канале трансформатор и аиоцы 1. Недостатком коммутатора является малая помехозащищенность, обусловленная увеличением коммутационной помехи из-з разброса параметров элементов. Наиболее близким по технической сущности к предлагаемому является многоканальный коммутатор, содержащий в каждом канале первый и второй транзисторы p-xtтипа проводимости и трансформатор, два конца одной из обмоток которого включен между базой и коллектором первого транзистора, два конца другой обмотки под- ключены между базой и коллектором второго транзистора, два конца третьей обмотки, являющиеся входом управления канала, подключены к внешнему дешифратору выбора каналов, эмиттеры транзис- торов являются входом канала, к которому подключается разрядная линия запоминающего устройства, причем коллекторы первых транзисторов, сбединенные между собой, и коллекторы вторых транзисторов соединенные между собой, являются выходами коммутатора, подключенными к внешнему усилителю считывания 2 . Недостатком известного многоканального коммутатора является отсутствие возможности коммутации разрядных токов записи, что сужает область, его применения Цель изобретения расширение области применения коммутатора за счет обеспечения двухсторонней коммутации сигналов. Поставленная цель достигается тем, что в многоканальном коммутаторе для запоминающего устройства, содержащем в камсцом канале первый и второй транзисторы и трансформатор, выводы одной из обмоток которого соединены соо1ветствен но с базой и коллектором первого транзистора, выводы другой обмотки трансформатора яJзляютcя управляющими входами канала, эмиттер первого транзисто- ра $1вляется одним из вывоцов канала, другие выводы каналов объединены и являются выводом многоканального коммутатора, в каждом из каналов коллектор к база второго транзистора подключены соответственно к коллектору и базе первого транзистора, а эмиттер второго 15 транзистора является другим выводом «внала. На: фиг. 1 изображена структурная схема предлагаемого коммутатора и принципиальная схема одного из каналов коммутатора; на фиг. 2 - один из вариантов организации разрядной линии запоминающего устройства, в котором используется предлагаемый коммутатор. Многоканальный коммутатор (фиг. 1) содержит каналы 1, каждый из которых содержит первый 2 и второй 3 транзис- 1Х)рыр-И-р типа проводимости и трансформатор 4, два вывода одной из обмоток которого включены между базой и коллектором первого транзистора 2. Эмиттер транзистора 2 является входом 5 коммутатора. Два вывода 6 другой обмотки подключаются к внешнему дешифратору Еыбора каналов (не показан). В каждом из каналов 1 коллектор транзистора 3 подключен к коллектору транзистора«2, база транзистора 3 подключена к базе транзистора 2, при этом эмиттеры транзисторов 3 соединены между собой и являются выходом 7 коммутатора. Коммутатор работает следующим образом. При подаче управляющего тока от внешнего дешифратора выбора каналов на один из выводов 6 транзисторы 2 и 3 соответствующего канала рткрываются. В режиме считывания запоминающего устройства сигнал считывания с разрядной линии 8, подключаемой к соответствующему входу 5 выбранного канала, проходит на выход .7 коммутатора. В режиме записи в запоминающее устройство разрядный ГОК записи, формируемый формирователем 9 разрядного тока, подключаемым к выходу 7 коммутатора, через транзисторы 2 и 3 выбранного канала проходит на соответствующий вход 5 коммутатора и в разрядную линию 8. Транзисторы 2 и 3 каждого канала включены инверсно и встречно. Механизм пропускания разрядного тока згшиси коммутатором можно объяснить следующим образом. При пропускании тока положительной полярности трашзиотор 2 работает как обычный транзистор с инверсным включением с обшей базой, ток проходит через эмиттерно-базовый переход транзистора 3 как через диод в прямом направлении и открытый током управления эмиттерио-базовый переход Т)занзистора 2. Ток обратной полярности прохоцит через открытый током управлени эмиттерно-базовый перехоа транзистора 3 и эмиттерно-базовый nepexoci транзистора 2 как через анод в прямом направлен НИИ. При прохождении сигнала считывания оба транзистора включены встречно и инверсно, чем объясняется взаимная компенсация остаточных напряжений. Положительный эффект от использования изобретениязаключается в расширени области применения коммутатора за счет обеспечения коммутации как считанного сигнала, так и разрядного тока записи. Поясним это на примере одного из вариантов организации разрядных цепей запоминающего устройства с яспользова- нием предлагаемого коммутатора (фиг. 2). В одном из вариантов организации раз рядной линии запоминающего устройства (фиг. 2) оба выхода каждой разрядной линии 8 подключаются к входу усилителя 10 воспроизведения и выходу формирователя 9 разрядного тока Через два соответствующих канала 1 двух многоканальных коммутаторов. При использовании предлагаемых многоканальных коммутаторов с числом каналов К достаточно иметь один формирователь разрядного тока и один усилитель воспроизведения на К раз рядных линий, в то время как при использовании известного коммутатора необходимо иметь формирователь разрядного тока на каждую разрядную линию.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор сигналов считывания для магнитных запоминающих устройств | 1980 |

|

SU942134A1 |

| Блок адресной выборки для запоминающего устройства | 1980 |

|

SU982083A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Многоканальный стабилизированный источник вторичного электропитания | 1984 |

|

SU1166085A1 |

| Многоканальный коммутатор | 1979 |

|

SU843236A1 |

| Многоканальный коммутатор сигналов считывания для магнитных запоминающих устройств | 1984 |

|

SU1251173A2 |

| Устройство для вывода данных из управляющей цифровой вычислительной машины на обьекты | 1974 |

|

SU507865A1 |

| Многоканальный коммутатор и блок защиты | 1987 |

|

SU1534753A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЗАПОМИНАЮЩИЛ1 БЛОКОМ | 1971 |

|

SU318991A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

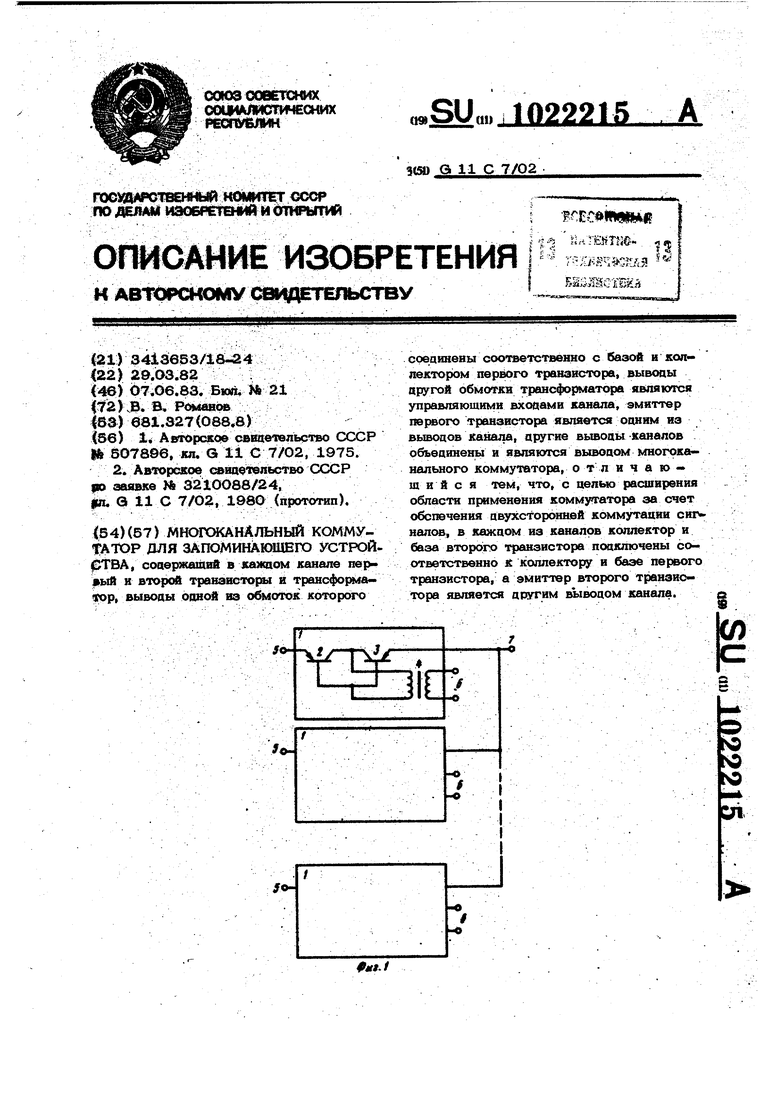

МНОГСЖАНАЛЬНЫЙ КОММУfА ТОР ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙ0ТВА, соаерквшвй в хажюм канале пер и второй транзисторы и трансфо{ аirop, выводы осшой вз обматок которого ; 5 t ibtTEjflJiO- « i Ь -.sI Ч I, .я I Б йЛ СХЕйА среаинены соответственно с базой и коллектором первого транзистора, выводы другой обмоткн трансформатора являются управляющими входами канала, эмиттер первого транзистора является одним из выводов канала, выводы -каналов объединены и являются выводом многоканального коммутатора, о т л и ч a ю - ш и и с я тем, что, с делью расширения области применения коммутатора за счет обспечения двухсторонней коммутации сигналов, в каждом из каналов коллектор и база второго транзистора подключены соответственно к коллектору и базе первого транзистора, a эмиттер второго транзистора является другим выводом канала.

Фиг. 2

Авторы

Даты

1983-06-07—Публикация

1982-03-29—Подача