Изобретение может быть использовано для построения запоминающих устройств на полных токах, применяемых в системах передачи данных и в вычислительной технике.

Известно устройство управления запоминающим блоком, которое содержит магнитный коммутатор с двумя тактовыми обмотками (обмотками переключения и многовитковыми распределяющими обмотками), четыре формирователя импульсов тока (два формирователя импульсов тока считывания и два формирователя импульсов тока подготовки записи), подключенные к началам соответствующих тактовых обмоток коммутатора. Недостатком известного устройства является то, что тип транзистора и схемная реализация формирователей тока считывания и подготовки записи устройства управления запоминающим блоком выбираются в зависимости от величины максимального напряжения, прикладываемого к переходам закрытых транзисторов во время формирования переднего фронта импульсов тока считывания.

Целью предлагаемого изобретения является упрощение устройства и повышение его надежности. Для этого в предлагаемом устройстве имеется только три формирователя вместо четырех в прототипе. Два формирователя, каждый из которых формирует и ток считывания и ток подготовки записи, подключены коллекторами транзисторов к началам соответствующих тактовых обмоток коммутатора, а эмиттерами - к общему резистору обратной связи, ко второму выводу которого и базам транзисторов подключены кремниевые стабилитроны в прямом направлении. Третий формирователь подключен коллектором транзистора к источнику питания, а эмиттером - к резистору обратной связи, второй вывод которого подключен к эмиттерам транзисторов первого и второго формирователей и стабилитрону, который подключается вторым выводом к базе транзистора третьего формирователя в прямом направлении.

Формирование импульса тока подготовки записи, амплитуда которого меньше амплитуды импульса тока считывания, производится путем создания на резисторе обратной связи первых двух формирователей дополнительного напряжения с помощью импульса тока, сформированного третьим формирователем.

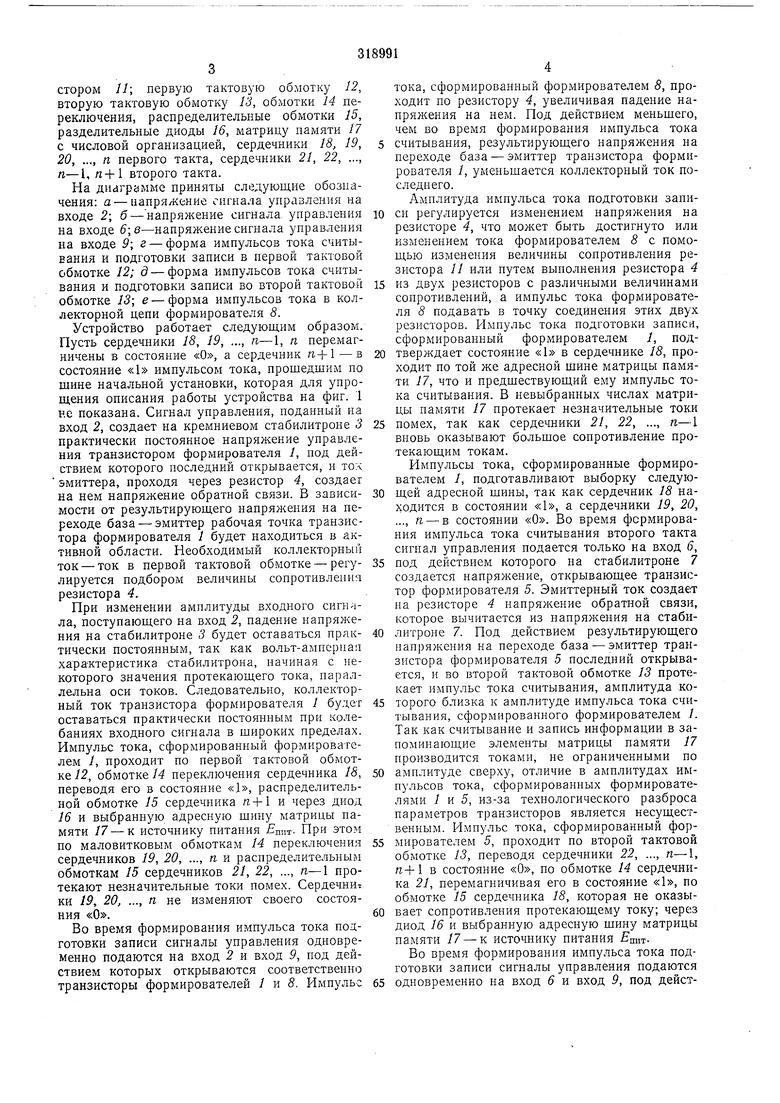

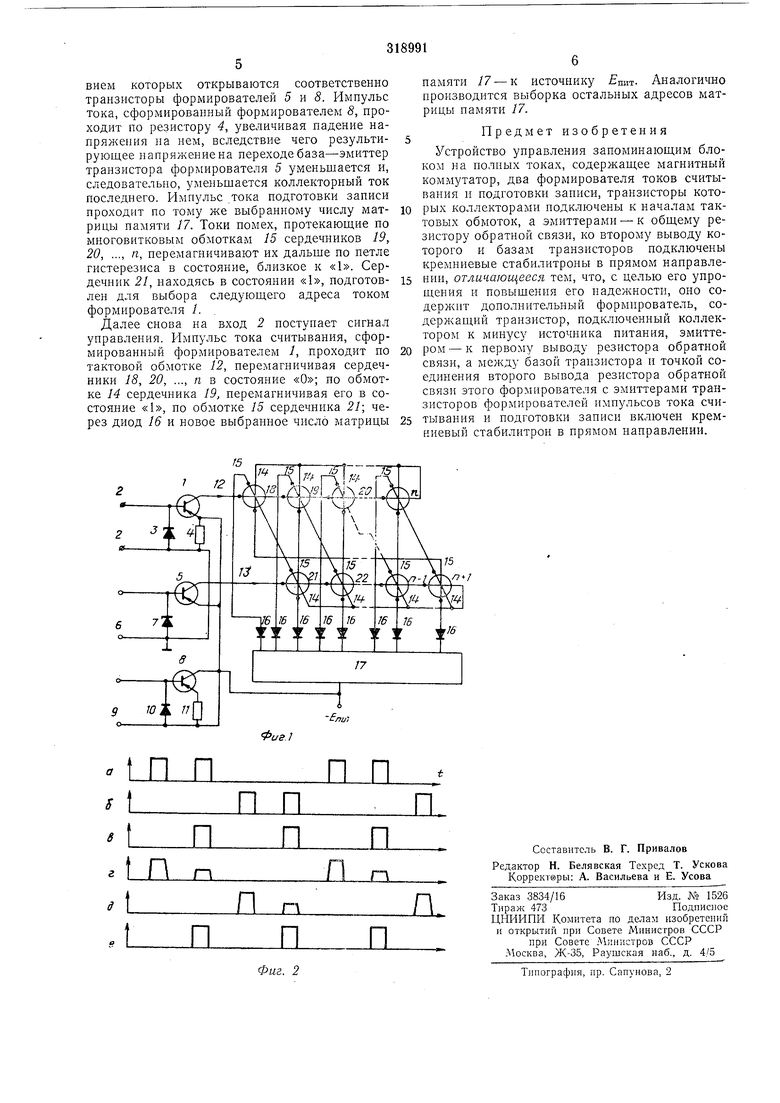

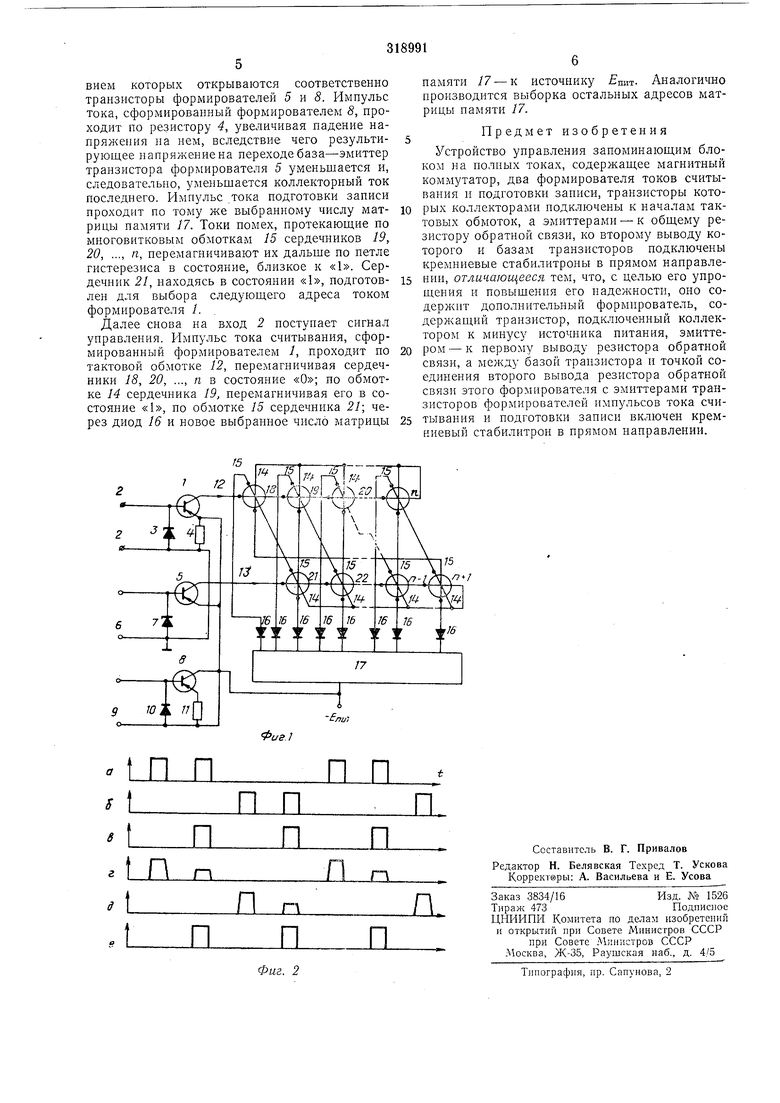

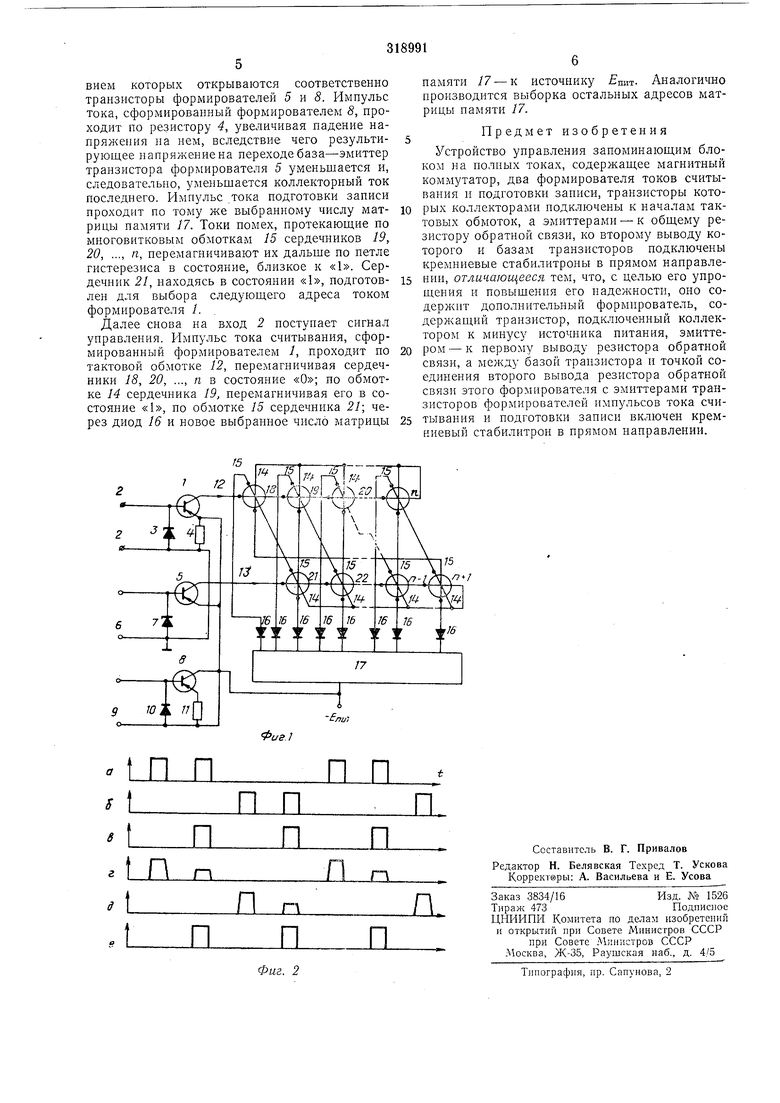

На фиг. 1 приведена схе.ма устройства; на фиг. 2 - временная диаграмма работы устройства управления запоминающим блоком.

Устройство содержит формирователь / тока считывания и подготовки записи со входом 2, кремниевым стабилитроном 3 и резистором 4 отрицательной обратной связи; формирователь 5 тока считывания и подготовки записи со входолг 6, кремниевым стабилитроном 7; формирователь 8 тока управления со входом 9, кремниевым стабилитроном 10 и резистором 11; первую тактовую обмотку 12, вторую тактовую обмотку 13, обмотки 14 переключения, распределительные обмотки 15, разделительные диоды 16, матрицу памяти 17 с числовой организацией, сердечники 18, 19, 20, ..., п первого такта, сердечники 21, 22, ..., п-1, п+1 второго такта.

На диаграмме приняты следующие обозначения: а - напряжение сигнала управления на входе 2; б - напряжение сигнала, управления на входе 6;в-напрялсениесигнала управления на входе 9 г - форма импульсов тока считывания и подготовки записи в первой тактовой обмотке 12; д - форма импульсов тока считывания и подготовки записи во второй тактовой обмотке 13; е - форма импульсов тока в коллекторной цепи формирователя S.

Устройство работает следующим образом. Пусть сердечники 18, 19, ..., п-1, п перемагничены в состояние «О, а сердечник /г+1 -в состояние «1 импульсом тока, прошедшим по шине начальной установки, которая для упрощения описания работы устройства на фиг. 1 не показана. Сигнал управления, поданный на вход 2, создает на кремниевом стабилитроне 3 практически постоянное напрялсение управления транзистором формирователя 1, под действием которого последний открывается, и тох эмиттера, проходя через резистор 4, создает на нем напряжение обратной связи. В зависимости от результирующего напрял ения на переходе база - эмиттер рабочая точка транзистора формирователя / будет находиться в активной области. Необходимый коллекторный ток - ток в первой тактовой обмотке - регулируется подбором величины сопротивления резистора 4.

Нри изменении амплитуды входного сигнала, поступающего на вход 2, падение напрял ;ения на стабилитроне 3 будет оставаться практически постоянным, так как вольт-ампернаи характеристика стабилитрона, начиная с некоторого значения нротекающего тока, параллельна оси токов. Следовательно, коллекторный ток транзистора формирователя I будет оставаться практически ностоянным при колебаниях входного сигнала в широких пределах. Импульс тока, сформированный формирователем /, проходит по первой тактовой обмотке /2, обмотке/4 переключения сердечника 18, переводя его в состояние «1, распределительной обмотке 15 сердечника « + 1 и через диод 16 и выбранную адресную шину матрицы намяти 17 - к источнику питания пит. При этом по маловитковым обмоткам 14 переключения сердечников 19, 20, ..., п и распределительным обмоткам 15 сердечников 21, 22, ..., п-1 протекают незначительные токи помех. Сердечнит ки 19, 20, ..., п не изменяют своего состояния «О.

Во время формирования импульса тока подготовки записи сигналы управления одновременно подаются на вход 2 и вход 9, под действием которых открываются соответственн1Э транзисторы формирователей / и 5. Импульс

тока, сформированный формирователем 8, проходит по резистору 4, увеличивая падение напрялсения на нем. Под действием меньшего, чем во время формирования импульса тока считывания, результирующего напрял ения на нереходе база - эмиттер транзистора формирователя /, уменьшается коллекторный ток последнего.

Амплитуда импульса тока подготовки записи регулируется изменением нанряжения на резисторе 4, что может быть достигнуто или изменением тока формирователем 8 с помощью изменения величины сонротивления резистора 11 или путем выполнения резистора 4 из двух резисторов с различными величинами сопротивлений, а импульс тока формирователя 8 подавать в точку соединения этих двух резисторов. Импульс тока подготовки записи, сформированный формирователем 1, подтверждает состояние «1 в сердечнике 18, проходит по той же адресной шине матрицы памяти 17, что и предшествующий ему импульс тока считывания. В невыбранных числах матрицы памяти 17 протекает незначительные токи помех, так как сердечники 21, 22, ..., п-1 вновь оказывают большое сопротивление протекающим токам.

Импульсы тока, сформированные формирователем Л подготавливают выборку следующей адресной шины, так как сердечник 18 находится в состоянии «1, а сердечники 19, 20, ..., п - в состоянии «О. Во время формирования импульса тока считывания второго такта сигнал управления подается только на вход б, под действием которого на стабилитроне 7 создается напрял ение, открывающее транзистор формирователя 5. Эмиттерный ток создает на резисторе 4 напрял.ение обратной связи, которое вычитается из напрял ения на стабилитроне 7. Под действием результирующего напрял ения на переходе база - эмиттер транзистора формирователя 5 последний открывается, и во второй тактовой обмотке 13 протекает импульс тока считывания, амплитуда которого близка к амплитуде импульса тока считывания, сформированного формирователем ./. Так как считывание и запись информации в запоминающие элементы матрицы памяти 17 производится токами, пе ограниченными по амплитуде сверху, отличие в амплитудах импульсов тока, сформированпых формирователями 1 и 5, из-за технологического разброса параметров транзисторов является несущественным. Импульс тока, сформированный формирователем 5, проходит по второй тактовой обмотке 13, переводя сердечники 22, ..., п-, п+ в состояние «О, по обмотке 14 сердечника 21, перемагничивая его в состояние «1, по обмотке 15 сердечника 18, которая не оказывает сопротивления протекающему току; через диод 16 и выбранную адресную шину матрицы памяти 17 - к источнику питания Ешп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь токов для запоминающего устройства | 1975 |

|

SU595789A1 |

| КОММУТАТОР | 1973 |

|

SU385396A1 |

| Запоминающее устройство | 1971 |

|

SU468302A1 |

| УСТРОЙСТВО для УПРАВЛЕНИЯ ЗАПОЛ\ИНАЮЩИМБЛОКОМ | 1970 |

|

SU272372A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| РАЗРЯДНЫЙ ФОРМИРОВАТЕЛЬ | 1972 |

|

SU327586A1 |

| Устройство записи и считывания информациидля НАКОпиТЕлЕй HA МНОп ТРАНзиСТОРАХ | 1979 |

|

SU830563A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1972 |

|

SU343302A1 |

| Запоминающее устройство | 1974 |

|

SU658600A1 |

Даты

1971-01-01—Публикация