1чЭ

О5

г

Ю

Изобретение относится к вычис.тительной технике и может быть использовано для построения запоминающих устройств на интегральных микросхемах.

Цель изобретения - повьинение быстродействия устройства.

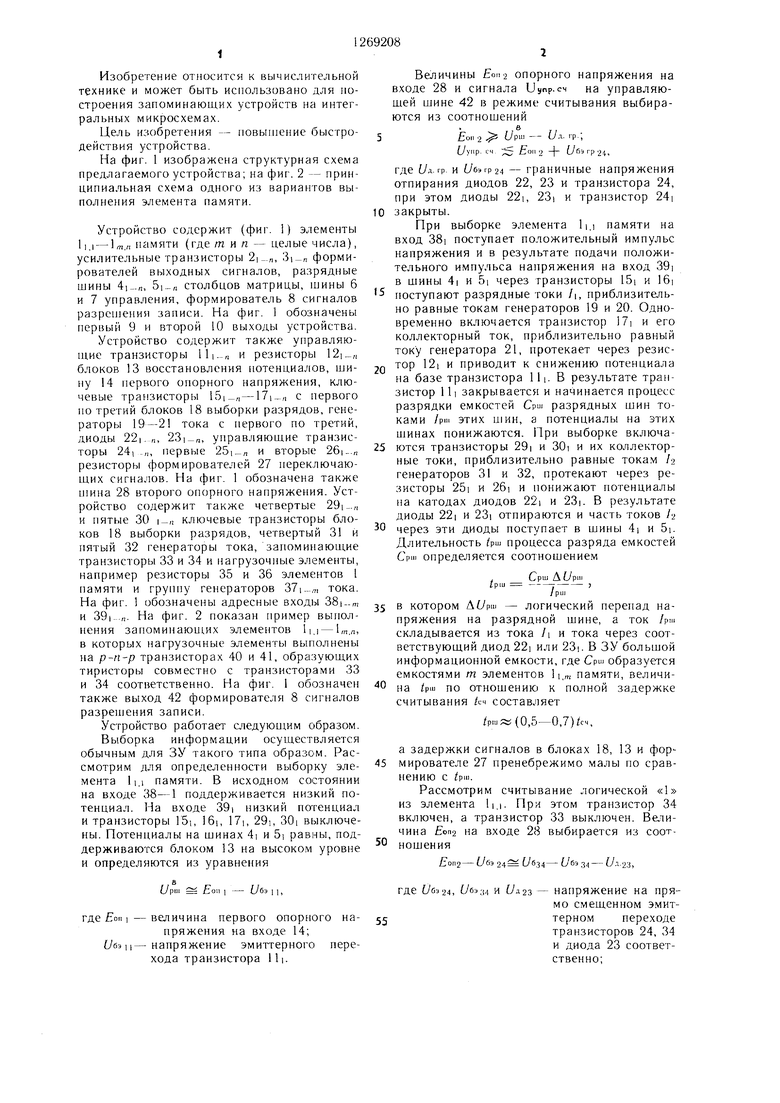

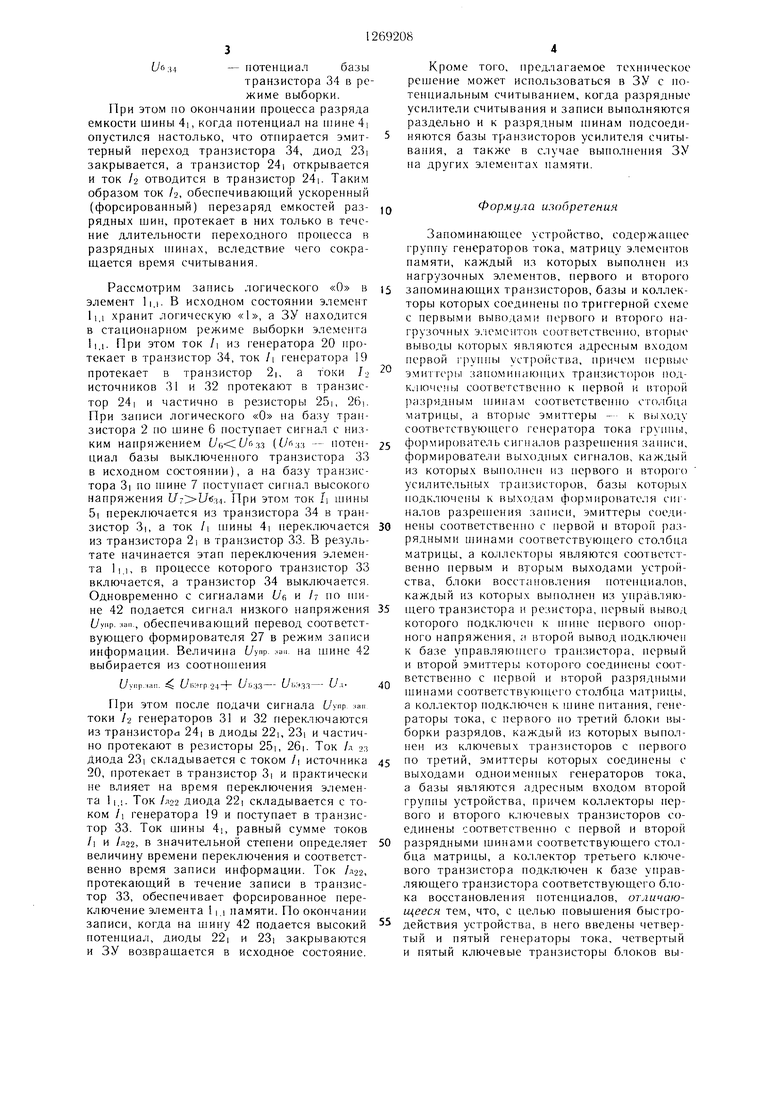

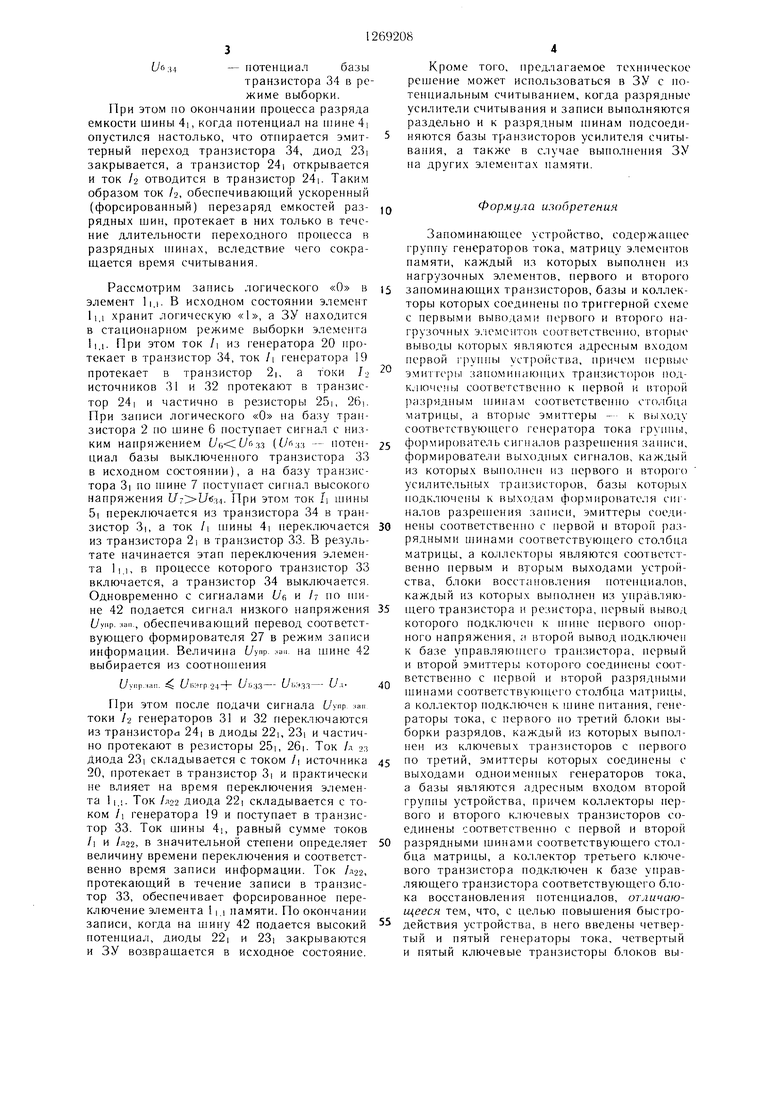

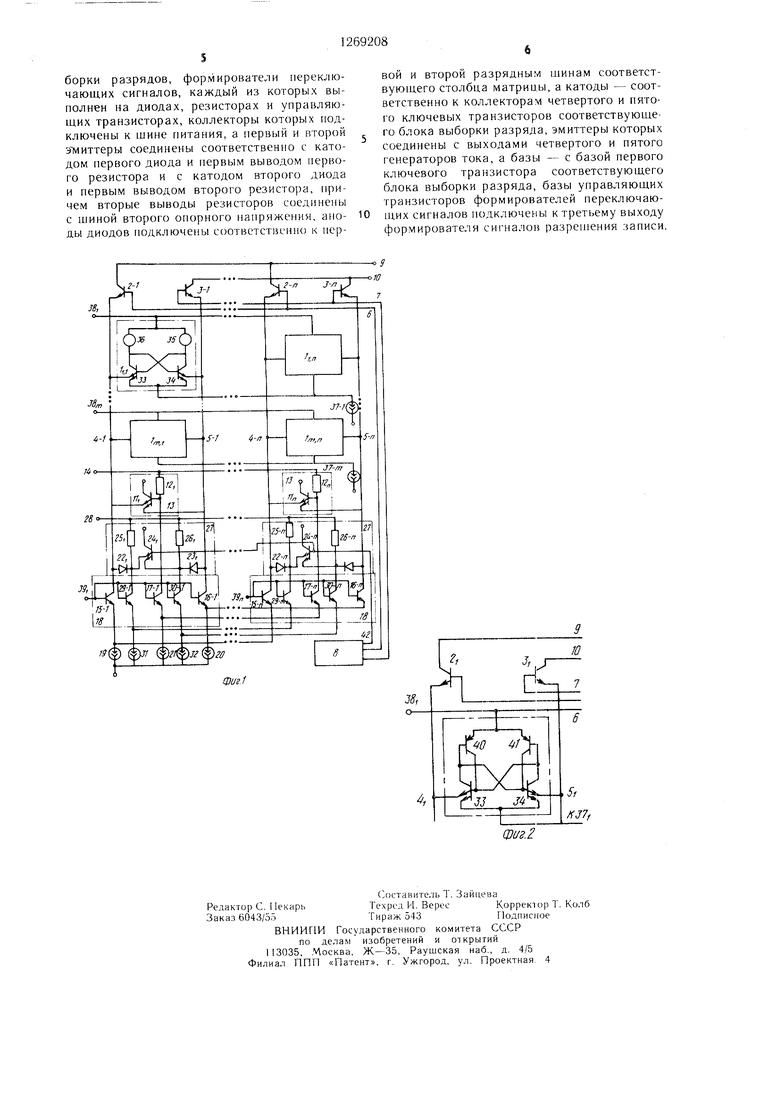

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - принципиальная схема одного из вариантов выполнения элемента памяти.

Устройство содержит (фиг. 1) элементы 1|.| - 1ш.п памяти (где тип - целые числа), усилите;1ьные транзисторы , формирователей выходных сигналов, разрядные шины 4i,n, 5i.n столбцов матрицы, 6 и 7 управления, формирователь 8 сигналов разрешения записи. На фиг. 1 обозначены первый 9 и второй 10 выходы устройства.

Устройство содержит также управляющие транзисторы 111-,, и резисторы блоков 13 восстановления потенциалов, щину 14 первого опорного напряжения, ключевые транзисторы 15|,|-17i,, с первого по третий блоков 18 выборки разрядов, генераторы 19-2 тока с первого по третий, диоды 22|.„, , управляющие транзисторы 24) -„, первые и вторые 26|-.„ резисторы формирователей 27 переключающих сигналов. На фиг. 1 обозначена также тина 28 второго опорного напряжения. Устройство содержит также четвертые 29i.,, и пятые 30 , ключевые транзисторы блоков 18 выборки разрядов, четвертый 31 и пятый 32 генераторы тока, запоминающие транзисторы 33 и 34 и нагрузочные элементы, например резисторы 35 и 36 элементов 1 памяти и группу генераторов 371..-„, тока. На фиг. 1 обозначены адресные входы 38i-m и 39|-.„. На фиг. 2 показан пример выполнения запоминающих элементов lu - Im.n, в которых нагрузочные элементы выполнены на р-п-р транзисторах 40 и 41, образующих тиристоры совместно с транзисторами 33 и 34 соответственно. На фиг. 1 обозначен также выход 42 формирователя 8 сигналов разрешения записи.

Устройство работает следующим образом.

Выборка информации осуществляется обычным для ЗУ такого типа образом. Рассмотрим для определенности выборку элемента li.i памяти. В исходном состоянии на входе 38-1 поддерживается низкий потенциал. На входе 39| низкий потенциал и транзисторы Ъ, 16i, 17i, 29i, 30| выключены. Потенциалы на шинах 4| и 5i равны, поддерживаются блоком 13 на высоком уровне и определяются из уравнения

L/PUl 1О.1 IС/б

3 1 1,

где оп -величина первого опорного напряжения на входе 14; (Убэп-напряжение эмиттерного перехода транзистора lli.

Величины оп2 опорного напряжения на входе 28 и сигнала .сч на управляющей шине 42 в режиме считывания выбираются из соотношений &

о11 2 Upiu - (Ул. гр.;

СУупр. сч 2 |- С7 эгр24,

где L/л.гр. и Ьбзгр24 - граничные напряжения отпирания диодов 22, 23 и транзистора 24, при этом диоды 22i, 23i и транзистор 24|

закрыты.

При выборке элемента l|j памяти на вход 38i поступает положительный импульс напряжения и в результате подачи положительного импульса напряжения на вход 39| в шины 4| и 5i через транзисторы 15i и 16|

поступают разрядные токи , приблизительно равные токам генераторов 19 и 20. Одновременно включается транзистор 17i и его коллекторный ток, приблизительно равный току генератора 21, протекает через резистор 12i и приводит к снижению потенциала на базе транзистора 11|. В результате транзистор 11: закрывается и начинается процесс разрядки емкостей Срш разрядных шин токами /pill этих тин, а потенциалы на этих шинах понижаются. При выборке включаются транзисторы 29: и 30i и их коллекторные токи, приблизительно равные токам /2 генераторов 3 и 32, протекают через резисторы 25i и 26i и понижают потенциалы на катодах диодов 22i и 23|. В результате диоды 221 и 23i отпираются и часть токов /

через эти диоды поступает в шины 4 и 5i. Длительность рш процесса разряда емкостей Срш определяется соотношением

.Срш Д (Урш

/рш ,

/pill

в котором ЛУрш - логический перепад напряжения на разрядной шине, а ток /РШ складывается из тока 1 и тока через соответствующий диод 22i или 23|. В ЗУ большой информационной емкости, где Срш образуется емкостями т элементов Ь. памяти, величина /рш по отношению к полной задержке считывания /сч составляет

/рш(0,5-0,7)/сч,

а задержки сигналов в блоках 18, 13 и фор мирователе 27 пренебрежимо малы по сравнению с рш.

Рассмотрим считывание логической «1 из элемента lij. При этом транзистор 34 включен, а транзистор 33 выключен. Величина оп2 на входе выбирается из соотношения

Еоп2- (Убэ 24 Ьбэ 34- t/.i 2.:)

напряжение на прямо смещенном эмиттерном переходе транзисторов 24, 34 и диода 23 соответственно;

.- потенциал базы

транзистора 34 в режиме выборки.

При этом по окончании процесса разряда емкости шины 4, когда потенциал на Н ине4| опустился настолько, что отпирается эмиттерный переход транзистора 34, диод 23i закрывается, а транзистор 24i открывается и ток /2 отводится в транзистор 24. Таким образом ток /2, обеспечивающий ускоренный (форсированный) перезаряд емкостей разрядных шин, протекает в них только в течение длительности переходного процесса в разрядных шинах, вследствие чего сокраш.ается время считывания.

Рассмотрим запись логического «О в элемент 1|.|. В исходном состоянии элемент li,i хранит логическую «1, а ЗУ находится в стационарном режиме выборки элемента 1|.1. При этом ток /1 из генератора 20 протекает в транзистор 34, ток /i генератора 19 протекает в транзистор 2, а токи источников 31 и 32 протекают в транзистор 24| и частично в резисторы 25|, 26. При записи логического «О па базу транзистора 2 по шине 6 поступает сигнал с низким напряжением U, ((/«.чз -- потенциал базы выключенного транзистора 33 в исходном состоянии), а на базу транзистора 3| по ujHHe 7 поступает сигнал высокого напряжения 77 Ь/«:м. При этом ток Ii шипы 5| переключается из транзистора 34 в транзистор 3|, а ток /I НИНЫ 4: переключается из транзистора 2| в транзистор 33. В результате начинается этап переключения элемента 1|,1, в процессе которого транзистор 33 включается, а транзистор 34 выключается. Одновременно с сигналами Us и h по шине 42 подается сигнал низкого напряжения Lyiip. :iaii., обеспечиваюший перевод соответствуюпдего формирователя 27 в режим записи информации. Величина (7упр. зап. на шине 42 выбирается из соотношения

(Уупр.чап. (Уг.3гр24+ bbiiS(Уь злUлПри этом после подачи сигнала Uynp зап токи /2 генераторов 31 и 32 переключаются из транзистора 24| в диоды 22), 23| и частично протекают в резисторы 25i, 26|. Ток /д 2з Диода 23i складывается с током /i источника 20, протекает в транзистор 3i и практически не влияет на время переключения элемента |,1. Ток /Д22 диода 22| складывается с током /1 генератора 19 и поступает в транзистор 33. Ток шины 4|, равный сумме токов /1 и /Д22, в значительной степени определяет величину времени переключения и соответственно время записи информации. Ток /Д22, протека ощий в течение записи в транзистор 33, обеспечивает форсированное переключение элемента 1 и памяти. По окончании записи, когда па шину 42 подается высокий потенциал, диоды 221 и 23i закрываются и ЗУ возврашается в исходное состояние.

Кроме того, предлагаемое техническое решение может использоваться в ЗУ с потенциальным считыванием, когда разрядные усилители считывания и записи выполняются раздельно и к разрядным шипам подсоединяются базы транзисторов усилителя считывания, а также в случае вьшолнения ЗУ на других элементах памяти.

Формула изобретения

Запоминающее устройство, содержащее группу генераторов тока, матрицу элементов памяти, каждый из которых выполнен из нагрузочных элементов, первого и BTopoix) запоминающих транзисторов, базы и коллекторы которых соединены потриггерной схеме с первыми выводами первого и второго нагрузочпых э.1емеитон соответственно, вторые выводы которых являются адресным входом первой i-pyiHibi устройства, причем первые эмтгеры запомипиюших транзисторов подключены соответственно к первой и второй разря.дным шинам соответственно матрицы, а BTOpi ie эмиттеры - к выходу соответствующего генератора тока грунш), формирователь сигналов разрен1епия записи, фор.мнрователи выходных сигналов, каждый из которых выполнен из первого и BTopoio усилительных транзисторов, базы которых подключены к выходам формирователя сигналов разрешения записи, эмиттеры соединены соответственпо с первой и второй разрядными шипами соответствующего сто.чбца матрицы, а коллекторы являются соответствепно нервым и В1орым выходами устройства, блоки восстановления гштепциалов, каждый из которых выполнен из управ,1Я1ощего транзистора и резистора, первый вывод которого подключен к Н1ине nepBoio онорного напряжения, а второй вывод подключен к базе управляющего транзистора, нервый и второй эмиттеры которого соединены соответственно с первой и второй разрядными П1инами соответствующего столбца матрицы, а коллектор подключен к шине питания, генераторы тока, с первого но третий блоки выборки разрядов, каждый из которых выполнен из ключевых транзисторов с первого по третий, эмиттеры которых соединены с выходами одноименных генераторов тока, а базы Я15ЛЯЮТСЯ адресным входом второй группы устройства, причем коллекторы первого и второго к.;1ючевых транзисторов соединены соответствен по с первой и второй разрядными шинами соответствующего столбца матрицы, а коллектор третьего ключевого транзистора подключен к базе управляющего транзистора соответствуюпхего блока восстановления потенциалов, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены четвертый и пятый генераторы тока, четвертый и пятый ключевые транзисторы блоков вы

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1809466A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1569901A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

Изобретение относится к вычислительной технике и может быть применено для построения запоминающих устройств на интегральных микросхемах. Целью изобрегения является повышение быстродействия устройства. Устройство содержит матрицу запоминающих элементов, формирователи выходных сигналов, блоки восстановления потенциалов, блоки выборки разрядов, выполненные па транзисторах, генераторы тока, формирователь сигналов разрешения записи. Повышение быстродействия достигается путем введения в устройство формирователей переключающих сигналов, каждый из которых выполнен на транзисторе, двух диодах и двух резисторах, четвертого и пятого ключевых транзисторов блоков выборки разрядов, четвертого и пятого генераторов тока, которые обеспечивают форсированное переключение запоминающих транзисторов в элементах памяти при записи и ускоряют процесс перезаряда емкостей разрядных пшн матрицы при считывании за счет протекания Ф дополнительных токов в течение переходных процессов. 2 ил. (Л

| Электронная техника | |||

| Сер | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микроэлектроника, 1975, вып | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| of Solid State Circuits, 1975, p | |||

| Кухонный очаг со ступенчатой плитой и со змеевиком для подогревания воды | 1925 |

|

SU850A1 |

Авторы

Даты

1986-11-07—Публикация

1985-03-11—Подача