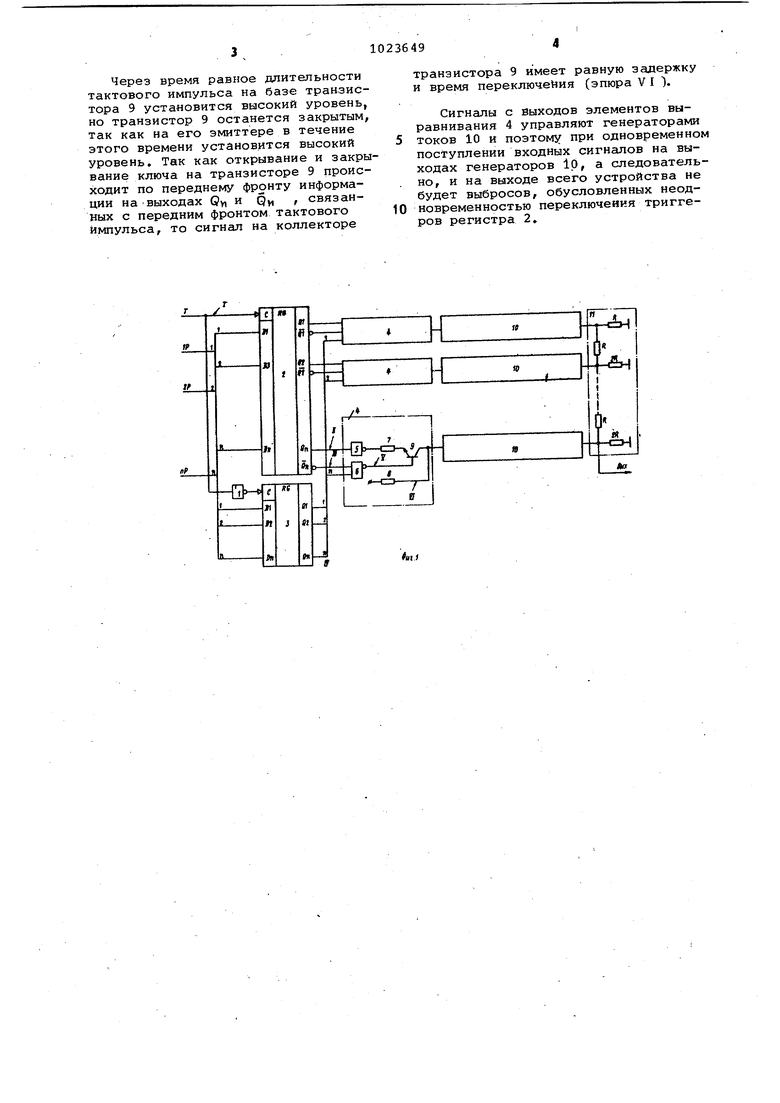

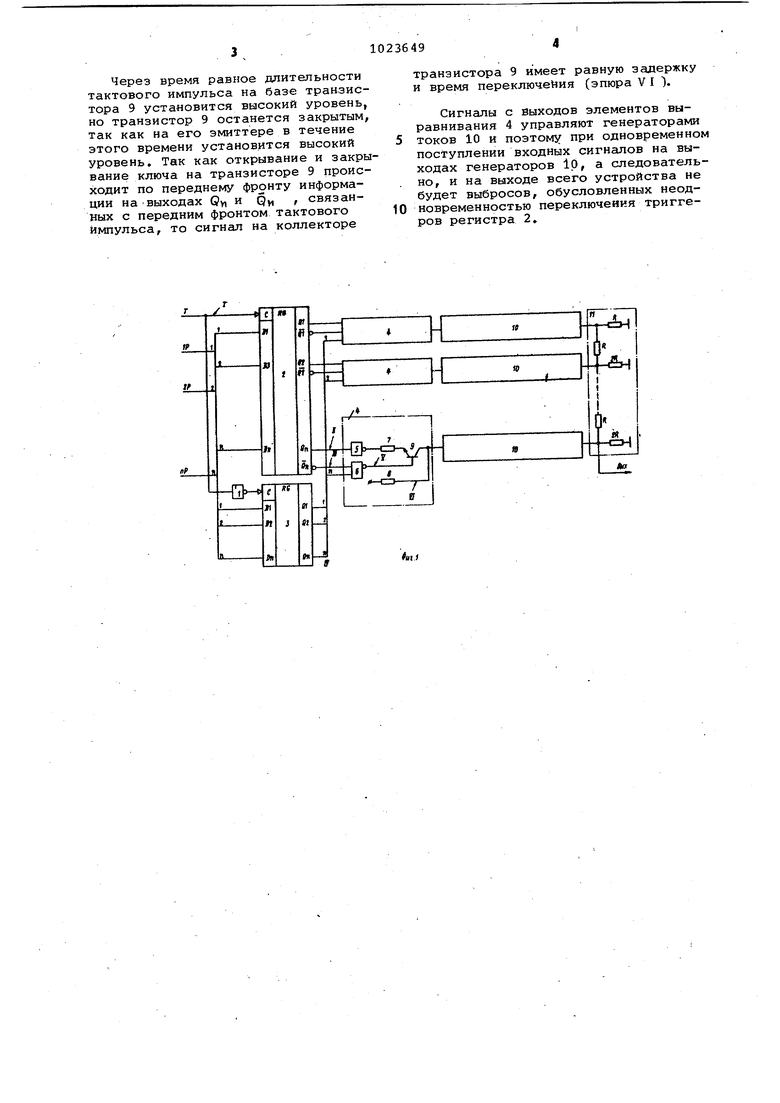

Изобретение относится к области импульсной техники и может использоваться для сопряжения между цифровым процессором и выходным устройством, имеющим линейные характеристики, . Известен цифро-аналоговый преобразователь (ЦАП ), содержащий регистр, дешифратор, ключи, генераторы тока и аналоговый сумматор , Большое количество управляемых генераторов т.ока, подключенных к выходу, усложняет конструкцию и сни жает быстродействие устройства за счет увеличения емкости выхода относительно нулевой шины, что является недостатком данного устройства. Известен также ЦАП, содержащий управляемые генераторы тока и матрицу резисторов R- iR , входы которой соединены с выходами yпpaвляe ш генераторов тока, первый регистр, и формационные входы которого подключ ны к входным кодовым шинам, а вход синхронизации - к шине синхронизации 2. Недостатком данного устройства является наличие выбросов на выходе устройства при изменении входного к да более чем на одном информационно входе регистра, обусловленных неодн временностью переключения сигналов на выходе регистра. Цель изобретения - уменьшение лож ной выходной информации. Поставленная цель достигается тем, что в цифро-аналоговый преобразователь, содержащий управляемые генераторы тока и матрицу регисторо R-1R, входы которой соединены с выходами управляемых генераторов тока первый регистр, информационные входы которого подключены к входным кодовым шинам, а вход синхронизадии к шине синхронизации, введены инвер тор, второй регистр и элементы вырав нивания, первые входы которых соеди нены с прямыми выходами первого регистра, вторые входы - с инверсными выходами первого регистра,третьи с прямыми выходами второго регистра а выходы - с входами управляемых ге нераторов тока, причем информационные входы второго регистра подключе ны к информационным входам первого регистра, вход синхронизации которо го через инвертор соединен с входом синхронизации второго регистра. Кроме того, каждый элемент- вырав нивания выполнен на транзисторе дву резисторах, инверторе и элементе И-НЕ, при этом первый вход элемента выравнивания соединен через инвертор с первым выводом первого резистора, второй вывод которого подключен к эмиттеру транзистора, второй вход элемента выравнивания соединен с первым входом элемента И-НЕ, второй вход которого подключен к третьему входу элемента выравнивания, а выход - к базе транзистора, коллектор которого соединен с выходом элемен-i та выравнивания и через второй резистор с шиной источника питания. На фиг, 1 приведена принципиальная электрическая схема ЦАП на фиг, 2 - временные диаграммы, поясняющие его работу, ЦАП состоит из инвертора 1, регистров 2 и 3 информационные входы которых соединены с входными кодовыми шинами 1... VI , Шина тактового импульса соединена с входом синхронизации регистра 2 и через инвертор 1 с входом синхронизации регистра 3, Выходы регистров соединены с элементами выравнивания 4, каждый из которых содержит инвертор 5, элемент И-НЕ 6, резисторы 7,8, транзистор 9, эмиттер транзистора соединен через резистор 7, инвертор 5 с прямым выходом QV, регистра 2, база - с выходом элемента И-НЕ 6, входы которого соединены с инверсным выходом Qv, ре-,, гистра 2 и прямым выходом Qyi регистра 3, Коллектор транзистора 9 соединен через резистор 8 с шиной источника питания Е. , Выходы элементов выравнивания 4 соединены с входами управляе1 ых генераторов тока 10, выходы которых соединены с входами матрицы резисторов R.-2A 11, На фиг, 2 показаны эпюры в следующих точках устройства: 1 - эпюра тактовых импульсов на входе синхронизации регистра 2 и инвертора llj II сигналы на выходе Оу, регистра 2; III сигналы на выходе рц регистра 2; IV сигналы на выходе Q.n регистра 3f У сйгналы на базе транзистора 9; VI .сигналы на коллекторы транзистора 9, Работу ЦАП удобно рассматривать при изменении информации на входе и старшего разряда в течении трех тактов. При поступлении на входы регистров 2 и 3 тактовых импульсов Т (эпюра I ) на выходах Qy,Q у, регистры 2 и выходе Qy, регистра 3 информация изменяется в соответствии с эпюргши II, III, IV, Передний фронт информации на выходах GVI ц регистра 2 привязан к переднему фронту тактового импульса с задержкой -Ьз , С выхода регистра 2 информации через инвертор 5 и резистор 7 поступает на эмиттер транзистора 9, открывая последний по переднему фронту (эпюра Г,1 ), При этом на базе транзистора 9 высокий уровень (эпюра V ), Закрывается транзистор 9 по переднему фронту информации, поступающей с выхода Qy, (эпюра Ш) через элемент И-НЕ 6 на базу данного транзистора (эпюра V), на базе транзистора устанавливается низкий потенциал.

Через время равное длительности тактового импульса на базе транзистора 9 установится высокий уровень, но транзистор 9 останется закрытым, так как на его эмиттере в течение этого времени установится высокий уровень. Так как открывание и закрывание ключа на транзисторе 9 происходит по переднему фронту информации на выходах Qy, и Qy, , связанных с передним фронтом тактового импульса, то сигнал на коллекторе

транзистора 9 имеет равную задержку и время переключения (эпюра VI %

Сигналы с Выходов элементов выравнивания 4 управляют генераторами токов 10 и поэтому при одновременном поступлении входных сигналов на выходах генераторов 1р, а следовательно, и на выходе всего устройства не будет выбросов, обусловленных неод0новременностью переключения триггеров регистра 2

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Широтно-импульсный модулятор для стабилизированного преобразователя | 1985 |

|

SU1305842A1 |

| Устройство для формирования последовательностей импульсов | 1989 |

|

SU1653140A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Формирователь импульсов | 1989 |

|

SU1704276A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Детектор @ -зубца электрокардиосигнала | 1984 |

|

SU1260004A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО КОНТРОЛЯ ТЕМПЕРАТУРЫ | 2015 |

|

RU2631018C2 |

| Цифроаналоговый преобразователь | 1989 |

|

SU1735999A1 |

/III

У

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника, | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Клебанский Р.Б | |||

| Преобразователи кода в напряжение, м., Энергия, 1973, с | |||

| Экономайзер | 0 |

|

SU94A1 |

Авторы

Даты

1983-06-15—Публикация

1980-08-01—Подача