Изобретение относится к области вычислительной цифровой техники и может быть использовано для контроля функционирования цифровых узлов и блоков с проверкой их работоспособности при оптимальных (граничных) значениях входных уровней воздействующих сигналов и проверкой оптимальных (граничных) значений уровней выходных сигналов.

- Целью изобретения является расширение номенклатуры контролируемых узлов и блоков и расширение функциональных возможностей за счет ориентации дополнительных режимов контроля.

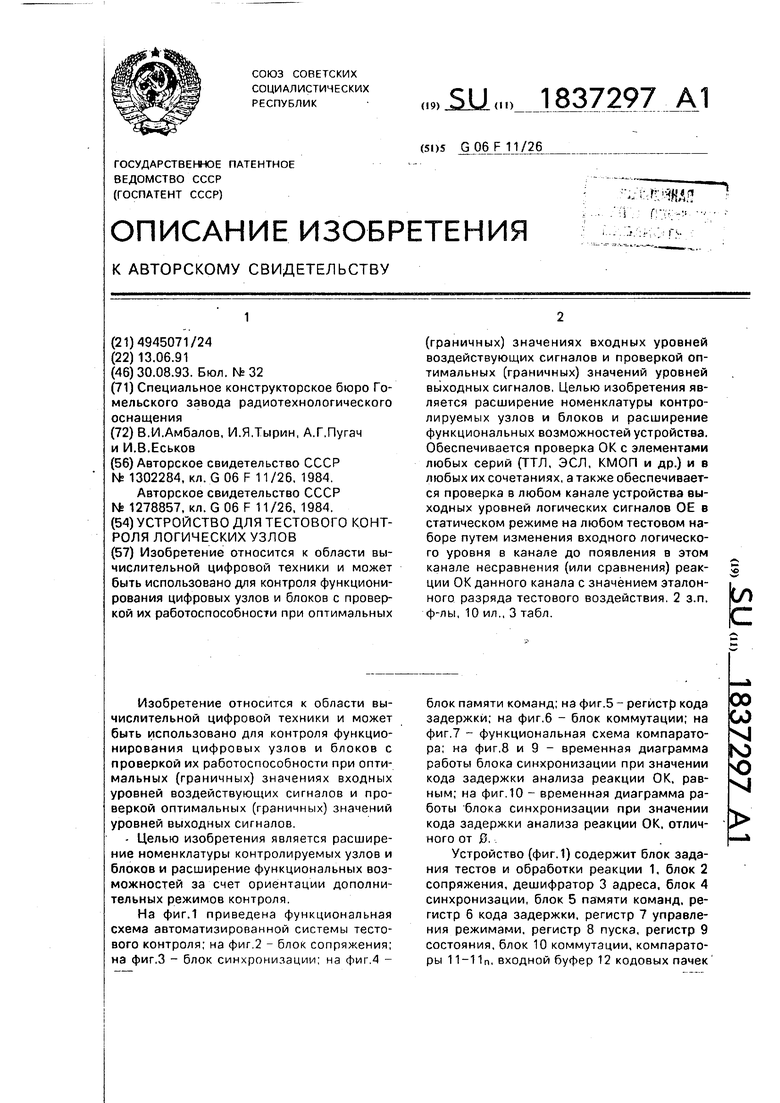

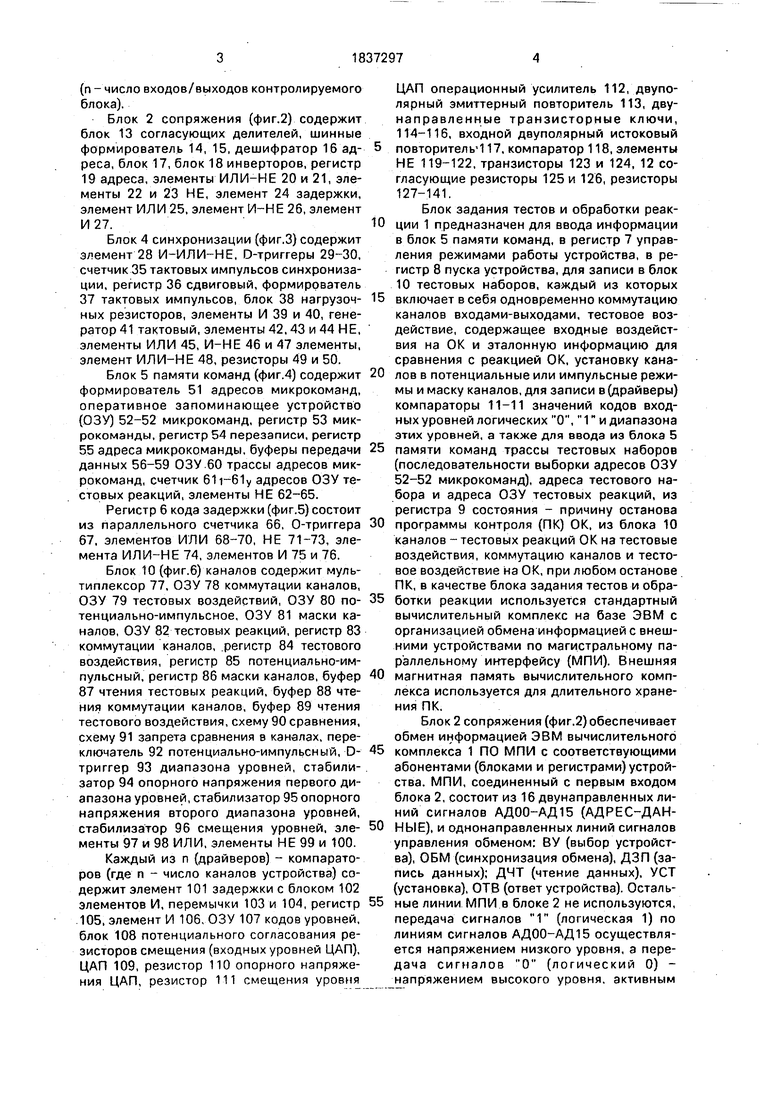

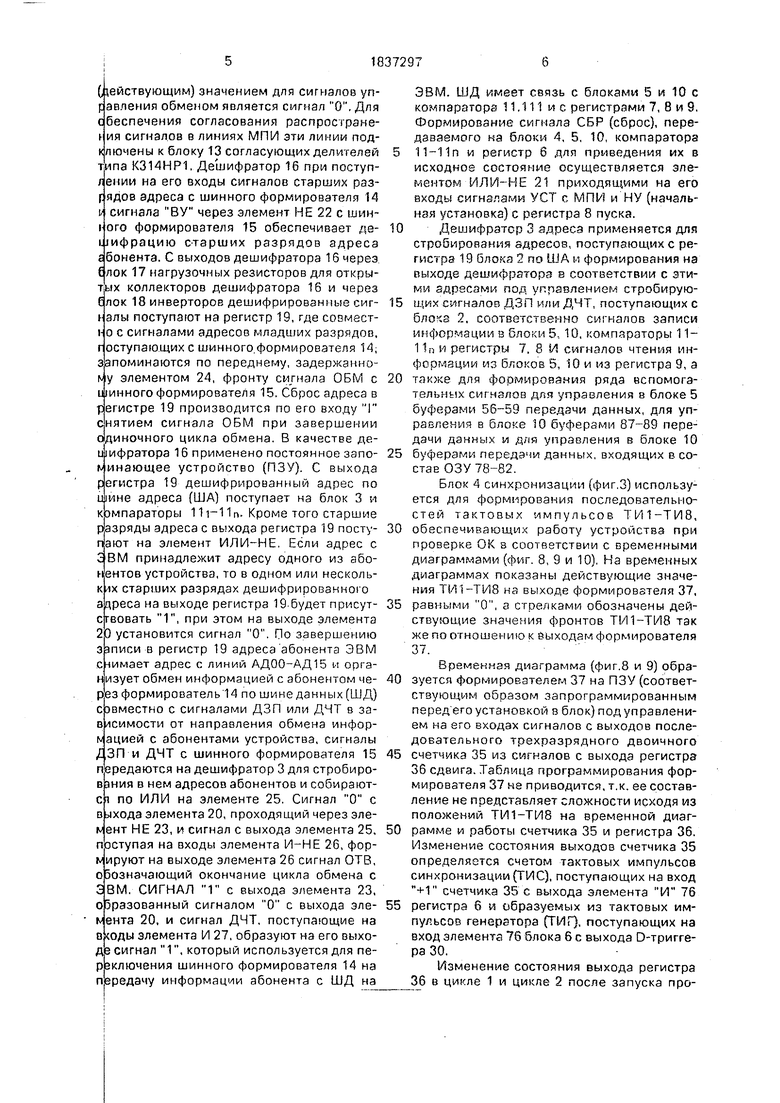

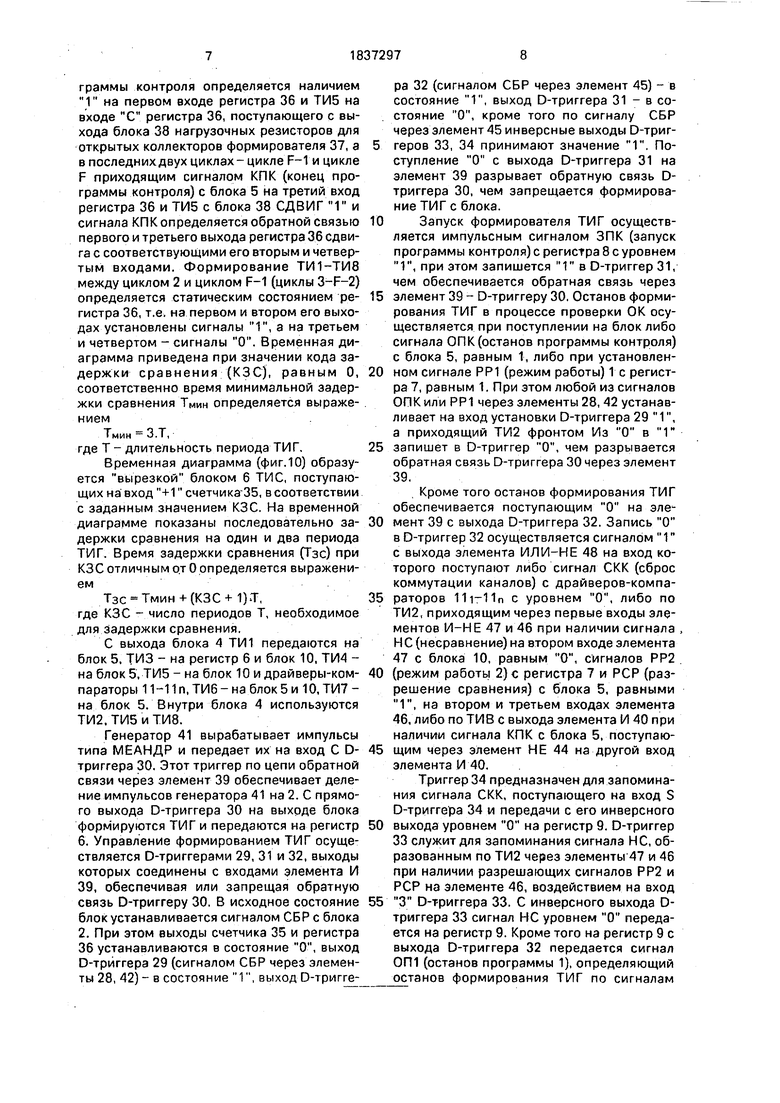

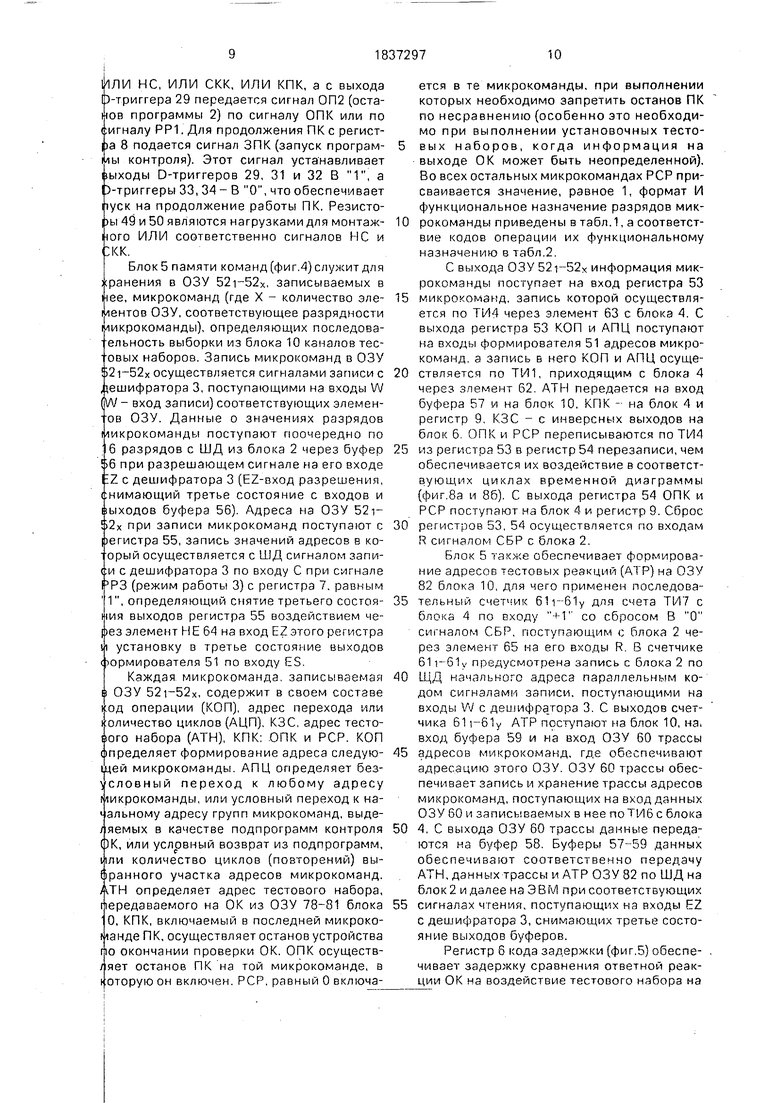

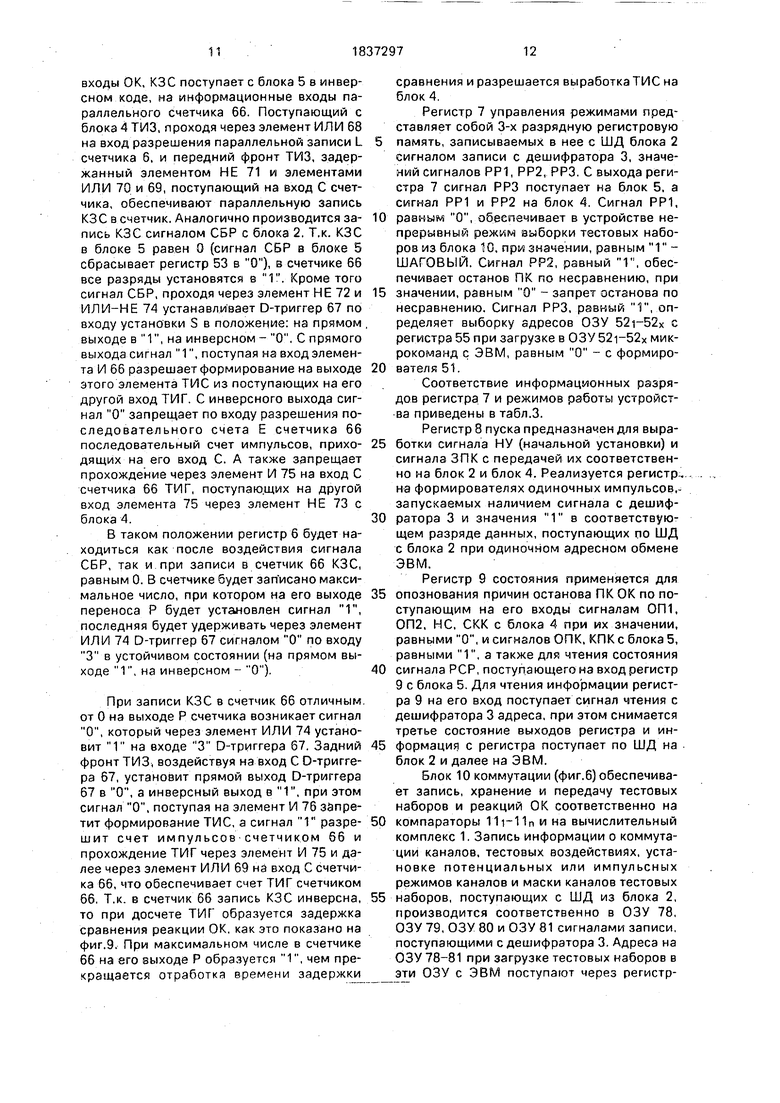

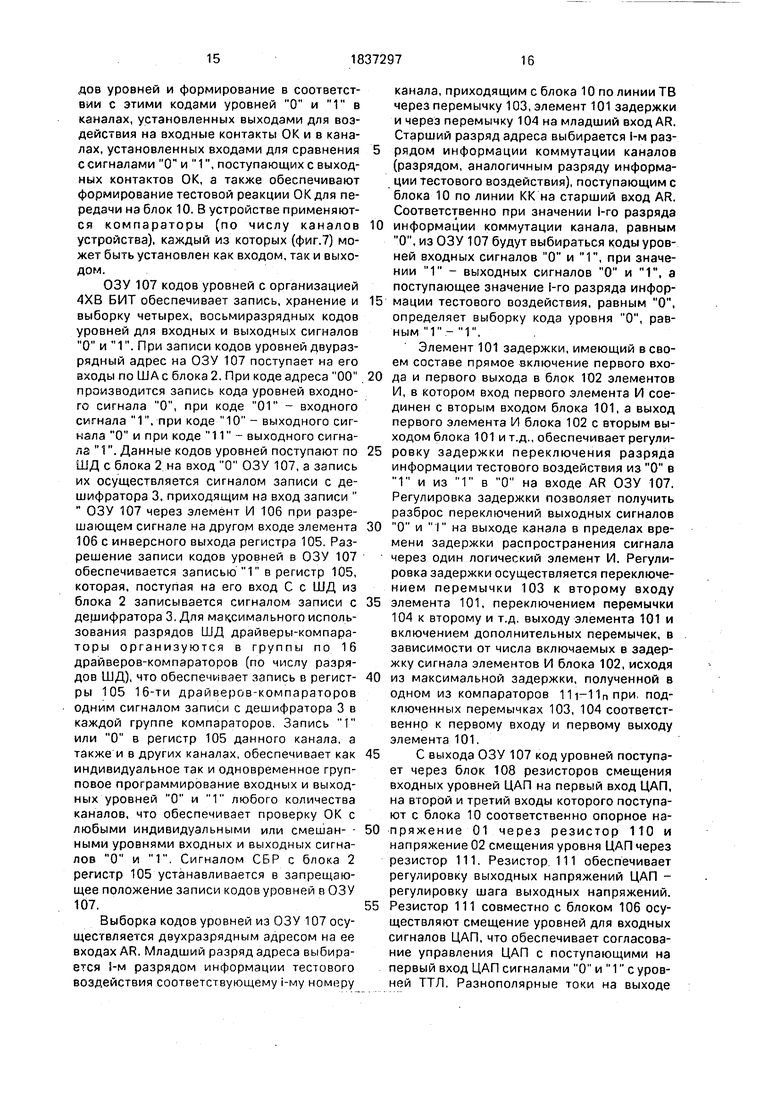

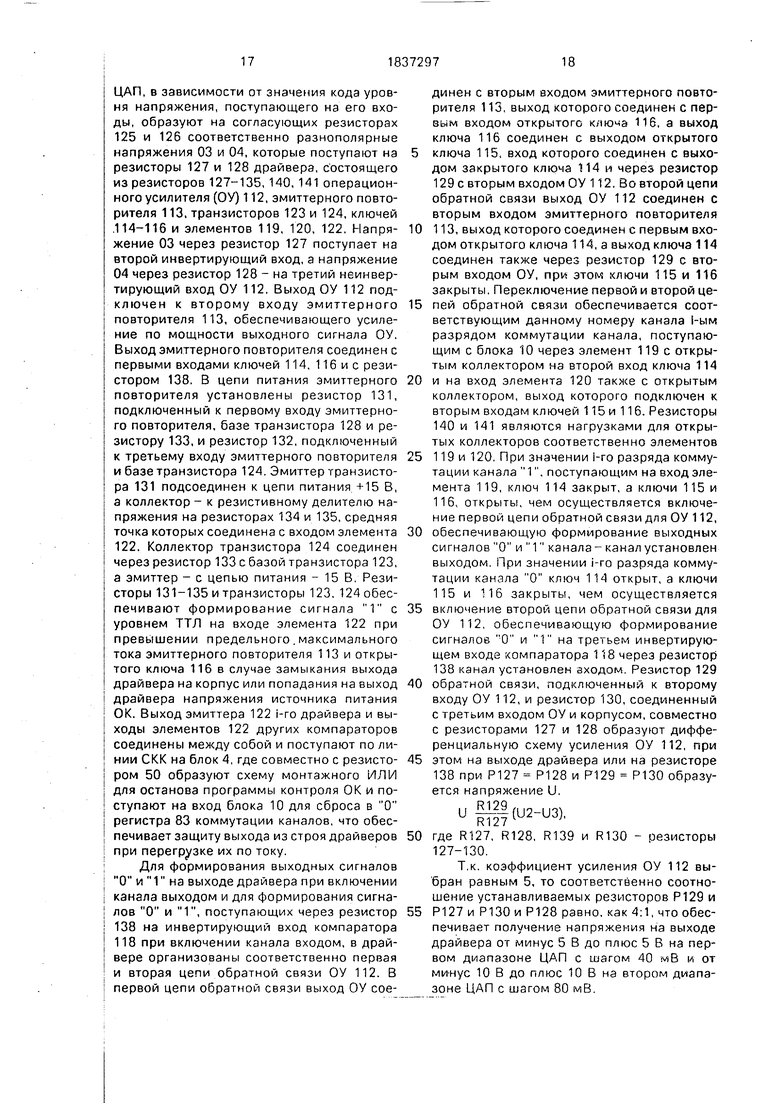

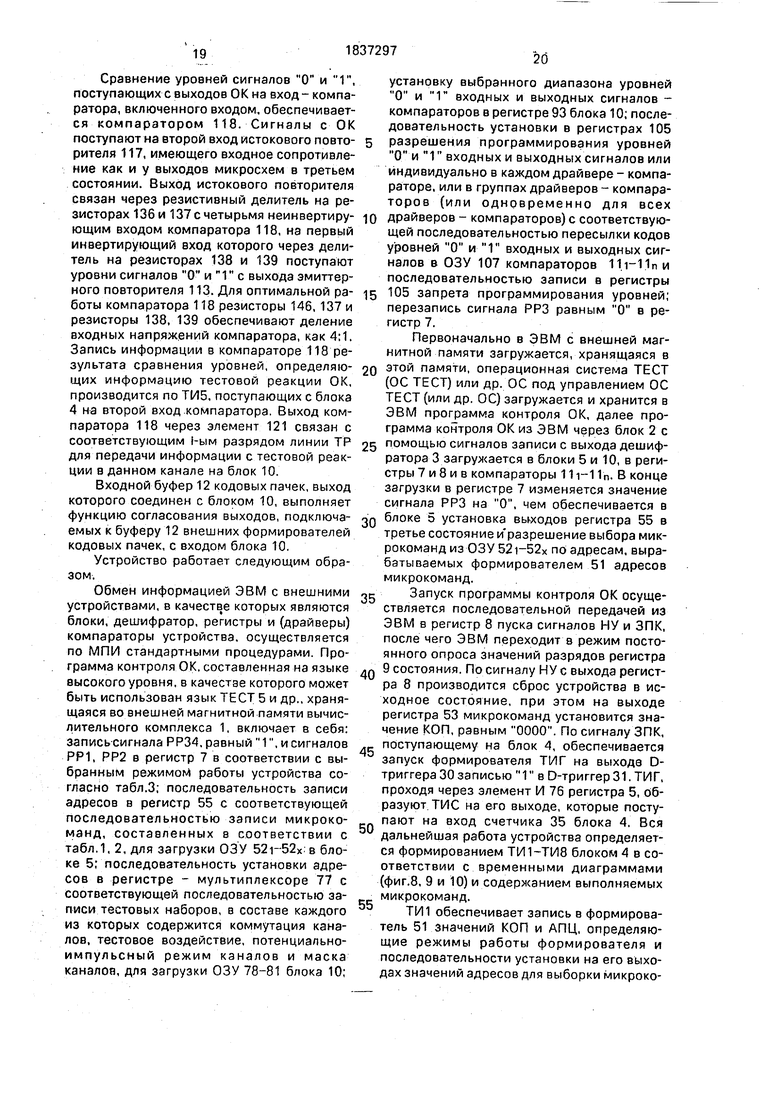

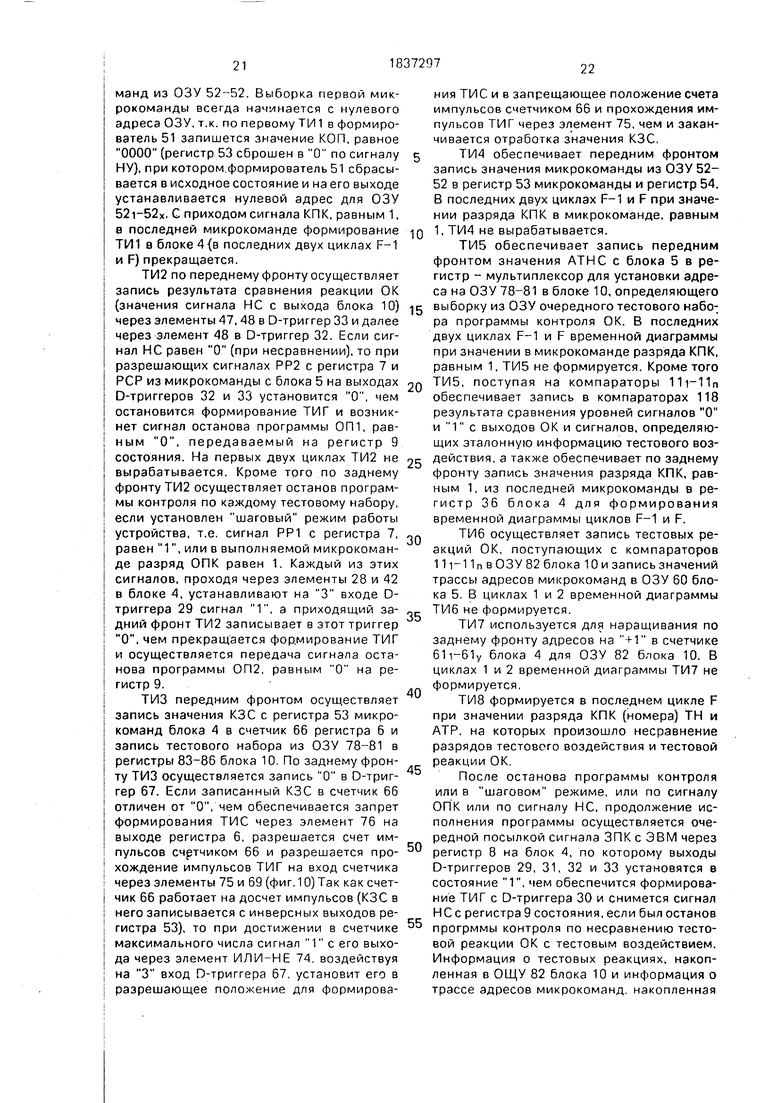

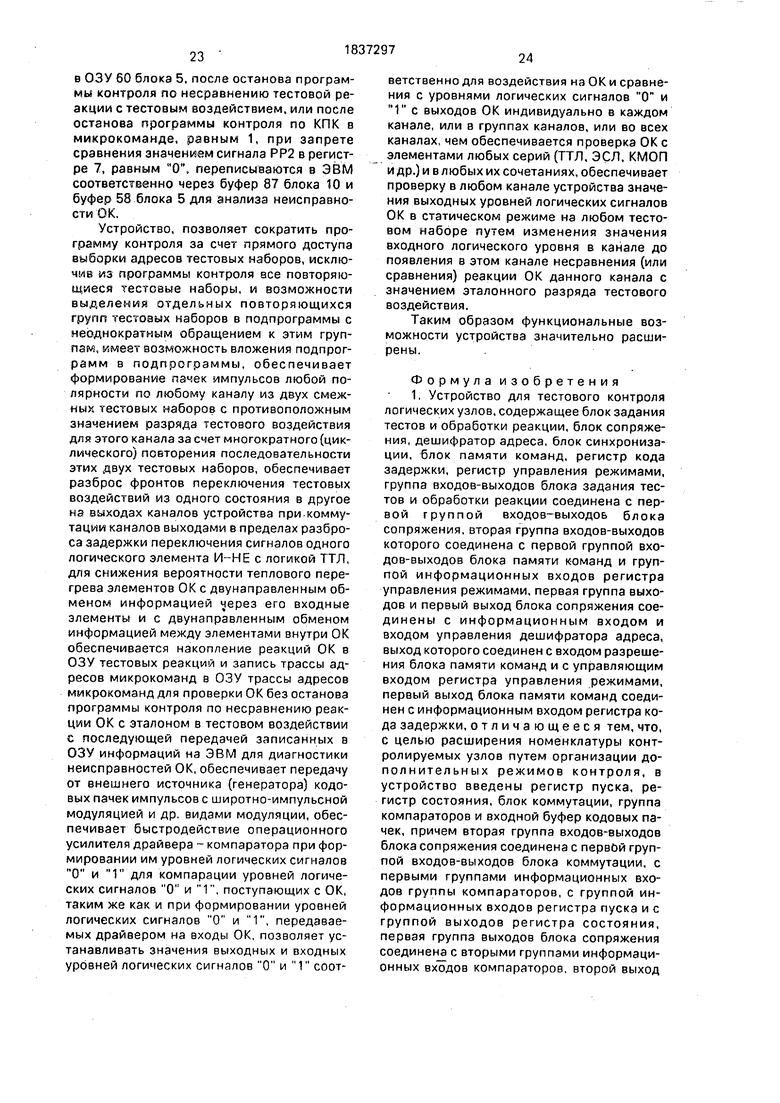

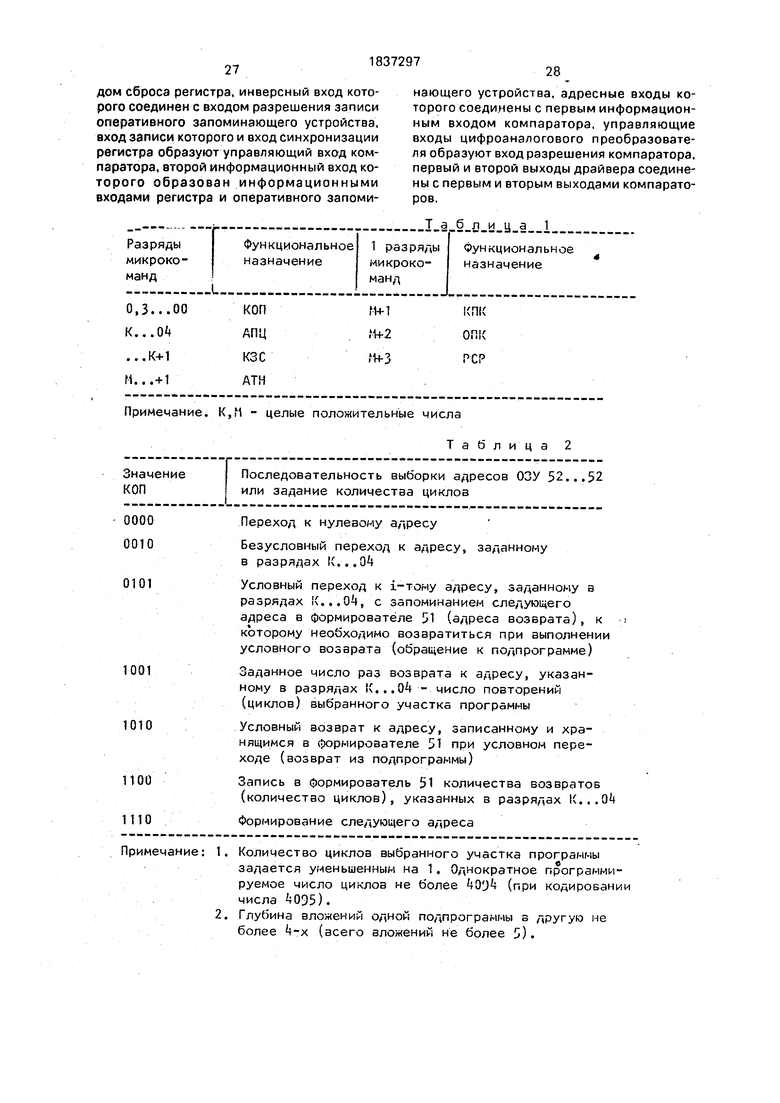

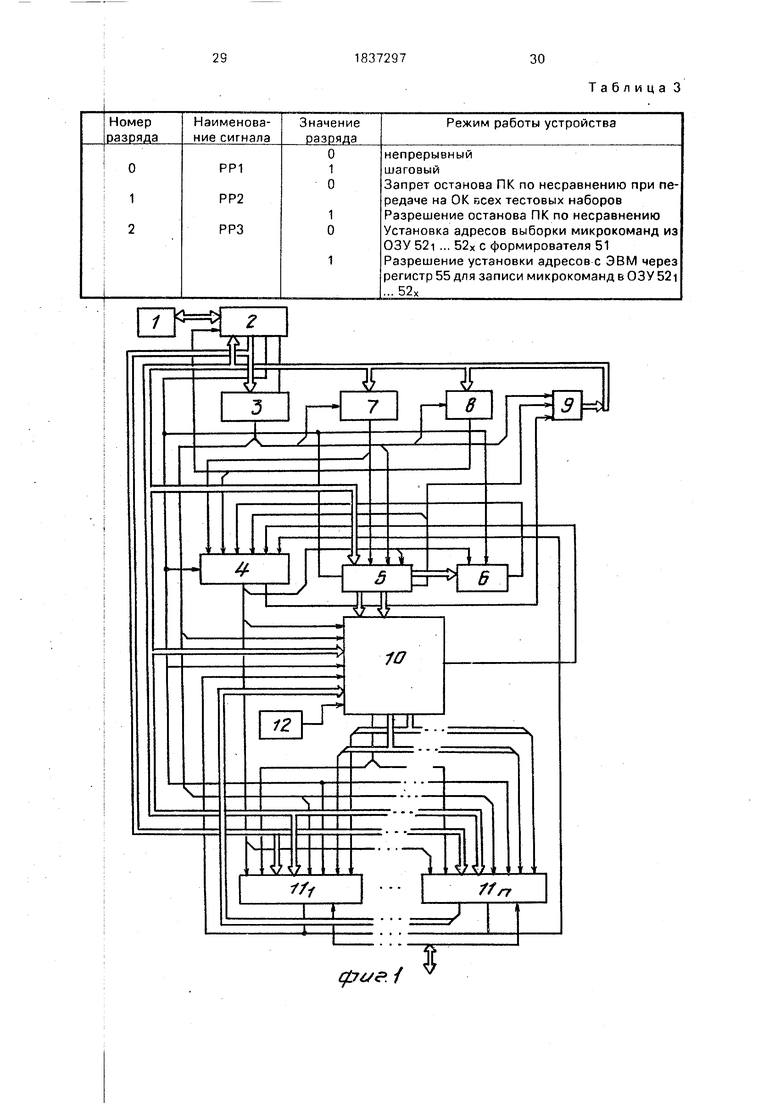

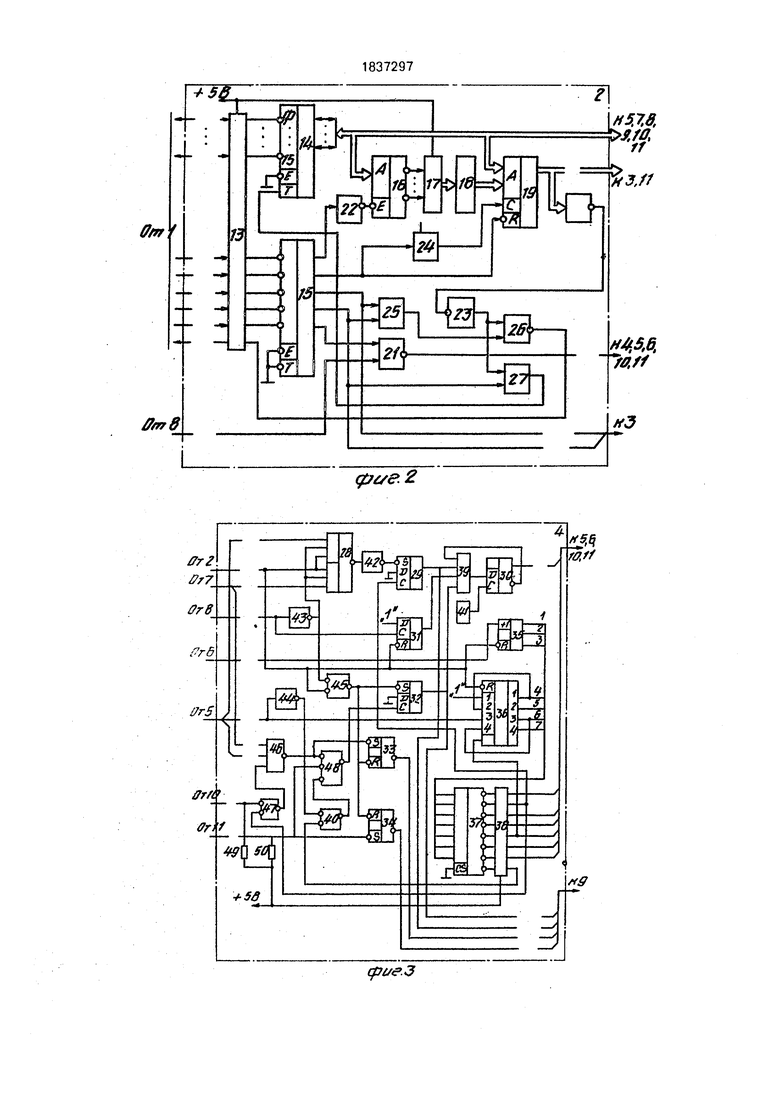

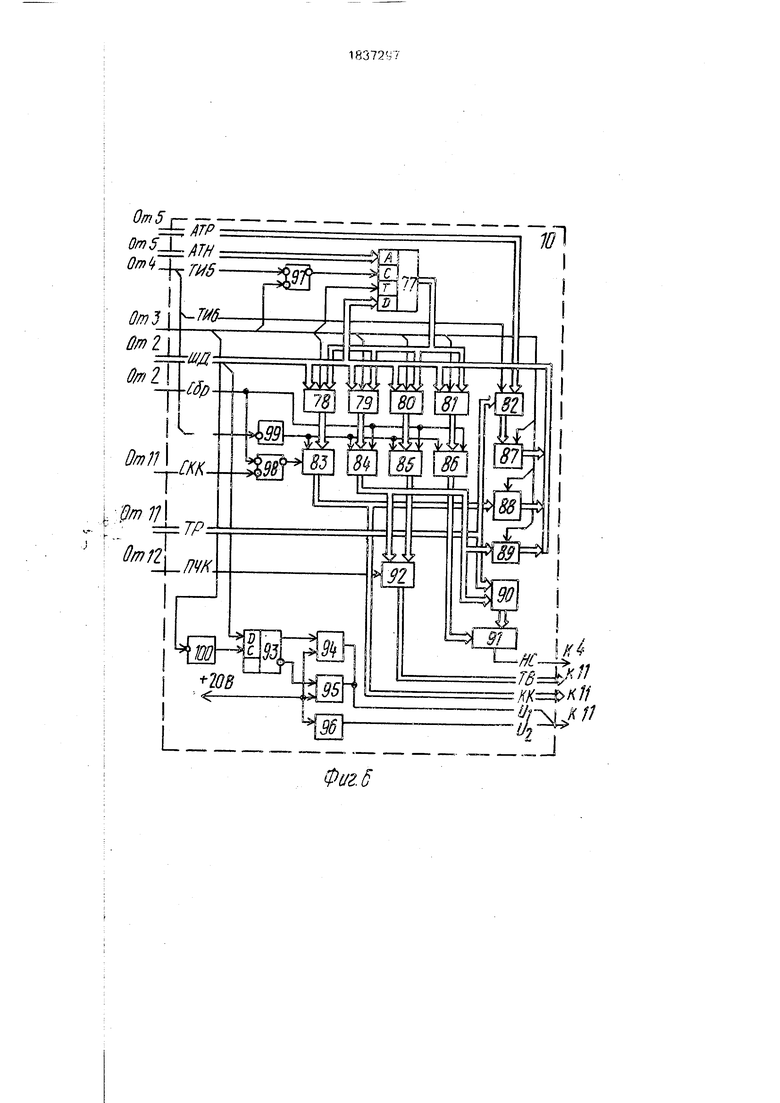

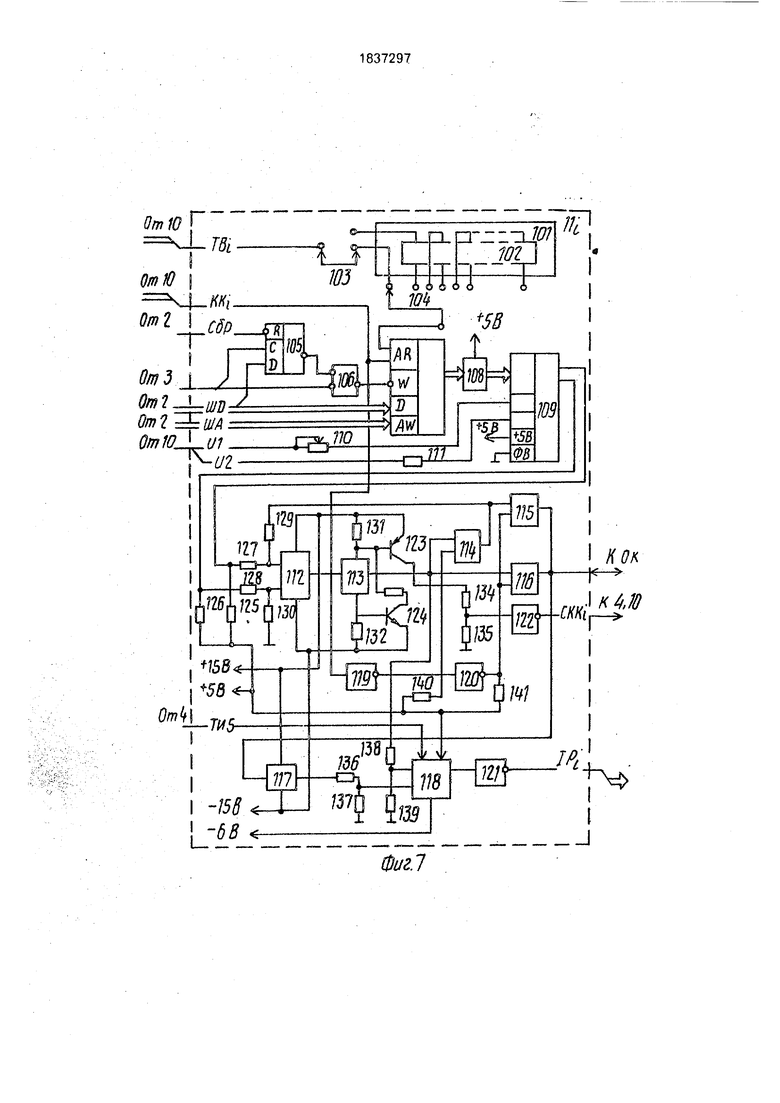

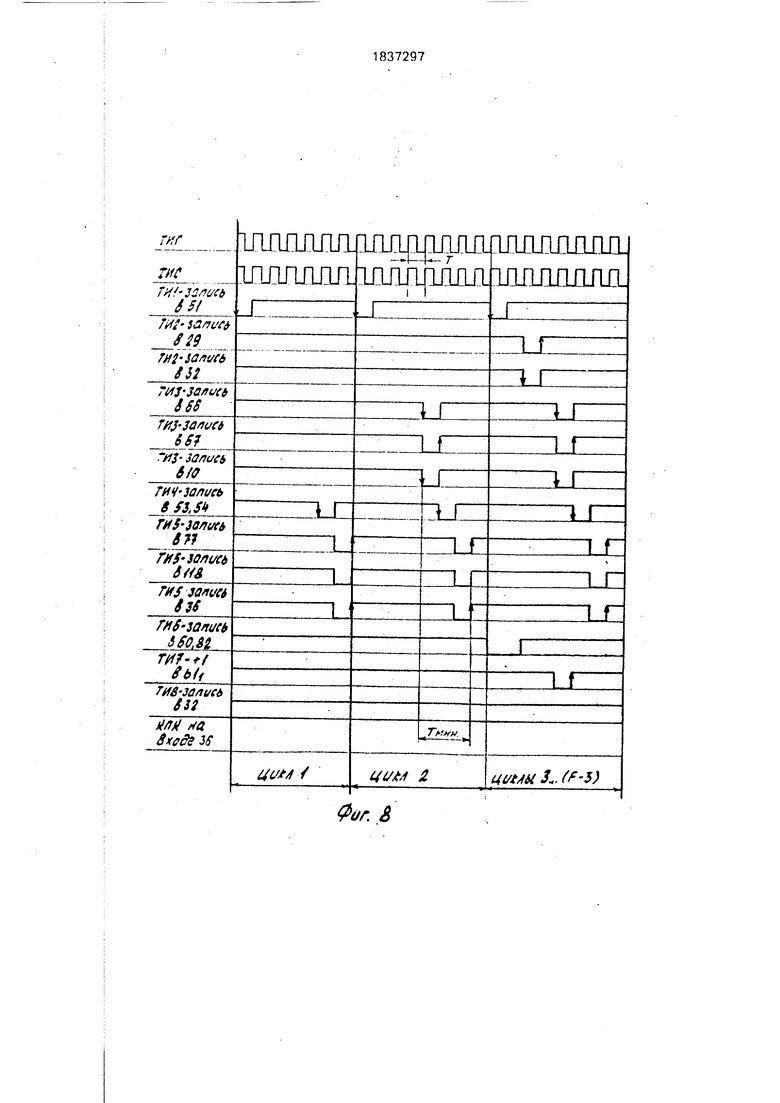

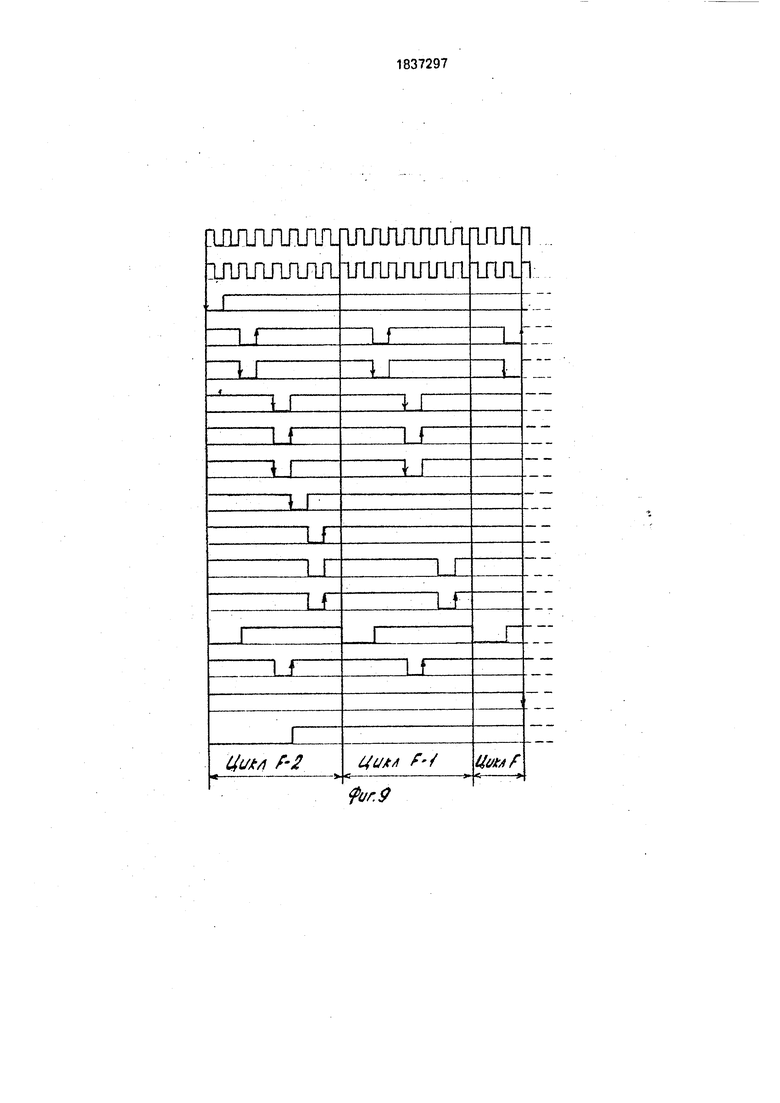

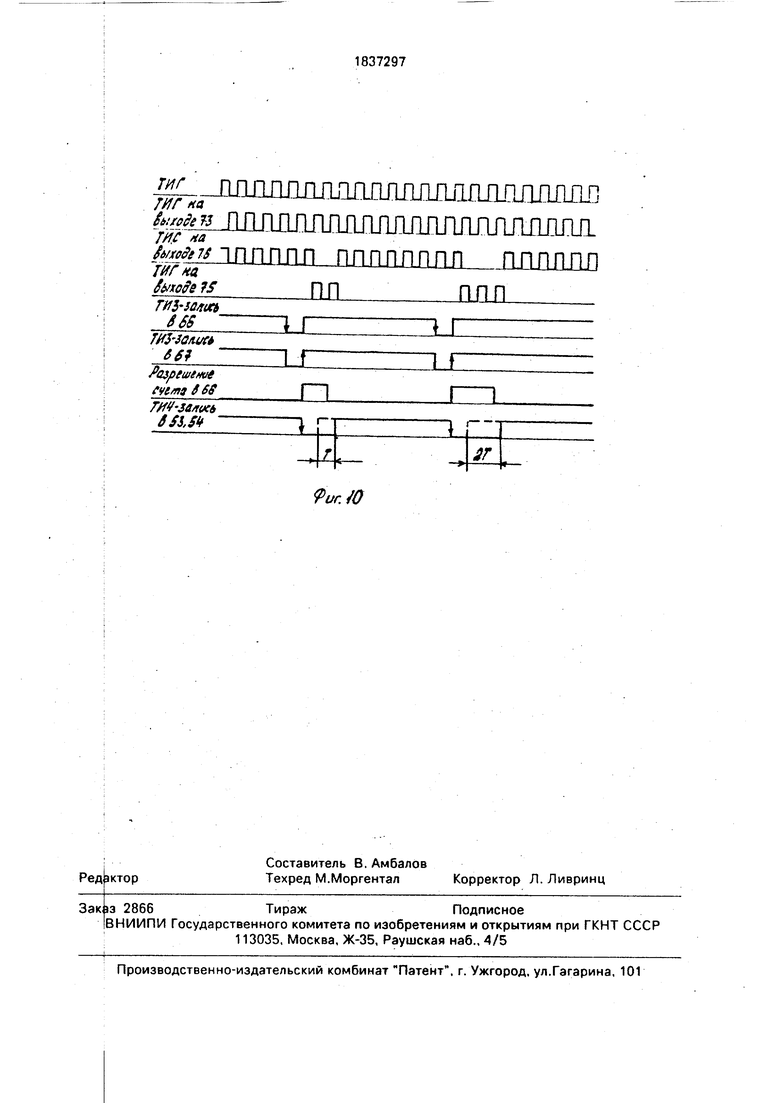

На фиг.1 приведена функциональная схема автоматизированной системы тестового контроля; на фиг.2 - блок сопряжения; на фиг.З - блок синхронизации; на фиг.4 блок памяти команд; на фиг.5 - регистр кода задержки; на фиг.6 - блок коммутации; на фиг.7 - функциональная схема компаратора; на фиг.8 и 9 - временная диаграмма работы блока синхронизации при значении кода задержки анализа реакции ОК, равным; на фиг. 10 - временная диаграмма работы блока синхронизации при значении кода задержки анализа реакции ОК, отличного от J3, .

Устройство (фиг.1) содержит блок задания тестов и обработки реакции 1, блок 2 сопряжения, дешифратор 3 адреса, блок 4 синхронизации, блок 5 памяти команд, регистр 6 кода задержки, регистр 7 управления режимами, регистр 8 пуска, регистр 9 состояния, блок 10 коммутации, компараторы 11-11П, входной буфер 12 кодовых пачек

оо

00

VI

(n - число входов/выходов контролируемого блока).

Блок 2 сопряжения (фиг.2) содержит блок 13 согласующих делителей, шинные формирователь 14, 15, дешифратор 16 ад- реса, блок 17, блок 18 инверторов, регистр 19 адреса, элементы ИЛИ-НЕ 20 и 21, элементы 22 и 23 НЕ, элемент 24 задержки, элемент ИЛИ 25, элемент И-НЕ 26, элемент И 27.

Блок 4 синхронизации (фиг.З) содержит элемент 28 И-ИЛИ-НЕ, D-триггеры 29-30, счетчик 35 тактовых импульсов синхронизации, регистр 36 сдвиговый, формирователь 37 тактовых импульсов, блок 38 нагрузоч- ных резисторов, элементы И 39 и 40, генератор 41 тактовый, элементы 42.43 и 44 НЕ, элементы ИЛИ 45, И-НЕ 46 и 47 элементы, элемент ИЛИ-НЕ 48, резисторы 49 и 50.

Блок 5 памяти команд (фиг.4) содержит формирователь 51 адресов микрокоманд, оперативное запоминающее устройство (ОЗУ) 52-52 микрокоманд, регистр 53 микрокоманды, регистр 54 перезаписи,регистр 55 адреса микрокоманды, буферы передачи данных 56-59 ОЗУ 60 трассы адресов микрокоманд, счетчик адресов ОЗУ тестовых реакций, элементы НЕ 62-65.

Регистр 6 кода задержки (фиг.5) состоит из параллельного счетчика 66, 0-триггера 67, элементов ИЛИ 68-70, НЕ 71-73, элемента ИЛИ-НЕ 74, элементов И 75 и 76.

Блок 10 (фиг.6) каналов содержит мультиплексор 77, ОЗУ 78 коммутации каналов, ОЗУ 79 тестовых воздействий, ОЗУ 80 по- тенциально-импульсное, ОЗУ 81 маски каналов, ОЗУ 82 тестовых реакций, регистр 83 коммутации каналов, .регистр 84 тестового воздействия, регистр 85 потенциально-импульсный, регистр 86 маски каналов, буфер 87 чтения тестовых реакций, буфер 88 чтения коммутации каналов, буфер 89 чтения тестового воздействия, схему 90 сравнения, схему 91 запрета сравнения в каналах, переключатель 92 потенциально-импульсный, D- триггер 93 диапазона уровней, стабилизатор 94 опорного напряжения первого диапазона уровней, стабилизатор 95 опорного напряжения второго диапазона уровней, стабилизатор 96 смещения уровней, эле- менты 97 и 98 ИЛИ, элементы НЕ 99 и 100.

Каждый из п (драйверов) - компараторов (где п - число каналов устройства) содержит элемент 101 задержки с блоком 102 элементов И, перемычки 103 и 104, регистр .105, элемент И 106, ОЗУ 107 кодов уровней, блок 108 потенциального согласования резисторов смещения (входных уровней ЦАП), ЦАП 109, резистор 110 опорного напряжения ЦАП, резистор 1-11 смещения уровня

ЦАП операционный усилитель 112, двупо- лярный эмиттерный повторитель 113, двунаправленные транзисторные ключи, 114-116, входной двуполярный истоковый повторитель 117, компаратор 118, элементы НЕ 119-122, транзисторы 123 и 124, 12 согласующие резисторы 125 и 126, резисторы 127-141.

Блок задания тестов и обработки реакции 1 предназначен для ввода информации в блок 5 памяти команд, в регистр 7 управления режимами работы устройства, в регистр 8 пуска устройства, для записи в блок 10 тестовых наборов, каждый из которых включает в себя одновременно коммутацию каналов входами-выходами, тестовое воздействие, содержащее входные воздействия на ОК и эталонную информацию для сравнения с реакцией ОК, установку каналов в потенциальные или импульсные режимы и маску каналов, для записи в (драйверы) компараторы 11-11 значений кодов входных уровней логических О, 1 и диапазона этих уровней, а также для ввода из блока 5 памяти команд трассы тестовых наборов (последовательности выборки адресов ОЗУ 52-52 микрокоманд), адреса тестового набора и адреса ОЗУ тестовых реакций, из регистра 9 состояния - причину останова программы контроля (ПК) ОК, из блока 10 каналов - тестовых реакций ОК на тестовые воздействия, коммутацию каналов и тестовое воздействие на ОК, при любом останове ПК, в качестве блока задания тестов и обработки реакции используется стандартный вычислительный комплекс на базе ЭВМ с организацией обмена информацией с внешними устройствами по магистральному параллельному интерфейсу (МПИ). Внешняя магнитная память вычислительного комплекса используется для длительного хранения ПК.

Блок 2 сопряжения (фиг.2) обеспечивает обмен информацией ЭВМ вычислительного комплекса 1 ПО МПИ с соответствующими абонентами (блоками и регистрами) устройства. МПИ, соединенный с первым входом блока 2, состоит из 16 двунаправленных линий сигналов АДОО-АД15 (АДРЕС-ДАННЫЕ), и однонаправленных линий сигналов управления обменом: ВУ (выбор устройства), ОБМ (синхронизация обмена), ДЗП (запись данных); ДЧТ (чтение данных), УСТ (установка), ОТВ (ответ устройства). Остальные линии МПИ в блоке 2 не используются, передача сигналов 1 (логическая 1) по линиям сигналов АДОО-АД15 осуществляется напряжением низкого уровня, а передача сигналов О (логический 0) - напряжением высокого уровня, активным

(действующим) значением для сигналов уп- р авления обменом является сигнал О. Для обеспечения согласования распростране- t ия сигналов в линиях МПИ эти линии подключены к блоку 13 согласующих делителей типа К314НР1. Дешифратор 16 при поступлении на его входы сигналов старших разрядов адреса с шинного формирователя 14 i сигнала ВУ через элемент НЕ 22 с шин- i ото формирователя 15 обеспечивает де- иифрацию старших разрядов адреса абонента. С выходов дешифратора 16 через Елок 17 нагрузочных резисторов для открыть х коллекторов дешифратора 16 и через Ёлок 18 инверторов дешифрированные сиг- калы поступают на регистр 19, где созмест- i-o с сигналами адресов младших разрядов, г вступающих с шинного.формирователя 14; запоминаются по переднему, задержанно- Ny элементом 24, фронту си/нала ОБМ с шинного формирователя 15. Сброс адреса в регистре 19 производится по его входу I снятием сигнала ОБМ при завершении одиночного цикла обмена. В качестве дешифратора 16 применено постоянное запо- г инающее устройство (ПЗУ). С выхода регистра 19 дешифрированный адрес по шине адреса (ША) поступает на блок 3 и компараторы 111-11 п. Кроме того старшие разряды адреса с выхода регистра 19 поступают на элемент ИЛИ-НЕ. Если адрес с ЗВМ принадлежит адресу одного из абонентов устройства, то в одном или нескольких старших разрядах дешифрированного адреса на выходе регистра 19.будет присутствовать 1, при этом на выходе элемента 20 установится сигнал О. По завершению записи в регистр 19 адреса абонента ЭВМ снимает адрес с линий АДОО-АД15 и организует обмен информацией с абонентом через формирователь 14 по шине данных (ШД) сэвместно с сигналами ДЗП или ДЧТ в зависимости от направления обмена информацией с абонентами устройства, сигналы /J3F1 и ДЧТ с шинного формирователя 15 передаются на дешифратор 3 для стробиро- вэния в нем адресов абонентов и собирают- ci по ИЛИ на элементе 25. Сигнал О с выхода элемента 20, проходящий через элемент НЕ 23, и сигнал с выхода элемента 25, поступая на входы элемента И-НЕ 26, формируют на выходе элемента 26 сигнал ОТВ, обозначающий окончание цикла обмена с ЭВМ. СИГНАЛ 1 с выхода элемента 23, образованный сигналом О с выхода элемента 20, и сигнал ДЧТ. поступающие на элемента И 27, образуют на его выходе сигнал 1, который используется для переключения шинного формирователя 14 на передачу информации абонента с ШД на

ЭВМ. ШД имеет связь с блоками 5 и 10 с компаратора 11.111 и с регистрами 7, 8 и 9, Формирование сигнала СБР (сброс), передаваемого на блоки 4, 5, 10, компаратора

11-11п и регистр 6 для приведения их в исходное состояние осуществляется элементом ИЛИ-НЕ 21 приходящими на его входы сигналами УСТ с МПИ и НУ (начальная установка) с регистра 8 пуска.

0 Дешифратор 3 адреса применяется для стробирования адресов, поступающих с регистра 19 блока 2 по ША и формирования на выходе дешифратора в соответствии с этими адресами под управлением стробирую5 щих сигналов ДЗП или ДЧТ, поступающих с блока 2, соответственно сигналов записи информации в блоки 5, 10, компараторы 11- 11П и регистры 7, 8 1Л сигналов чтения информации из блоков 5, 10 и из регистра 9, а

0 также для формирования ряда вспомогательных сигналов для управления в блоке 5 буферами 56-59 передачи данных, для управления в блоке 10 буферами 87-89 передачи данных и для управления в блоке 10

5 буферами передачи данных, входящих в состав ОЗУ 78-82.

Блок 4 синхронизации (фиг.З) используется для формирования последовательностей тактовых импульсов ТИ1-ТИ8,

0 обеспечивающих работу устройства при проверке ОК в соответствии с временными диаграммами (фиг. 8, 9 и 10). На временных диаграммах показаны действующие значения ТИ1-ТИ8 на выходе формирователя 37,

5 равными О, а стрелками обозначены действующие значения фронтов ТИ1-ТИ8 так же по отношению к выходам формирователя 37.

Временная диаграмма (фиг.З и 9) обра0 зуетсл формирователем 37 на ПЗУ (соответствующим образом запрограммированным перед его установкой в блок) под управлением на его входах сигналов с выходов последовательного трехразрядного двоичного

5 счетчика 35 из сигналов с выхода регистра 36 сдвига. Таблица программирования формирователя 37 не приводится, т.к. ее составление не представляет сложности исходя из положений ТИ1-ТИ8 на временной диаг0 рамме и работы счетчика 35 и регистра 36. Изменение состояния выходов счетчика 35 определяется счетом тактовых импульсов синхронизации (ТИС), поступающих на вход +1 счетчика 35 с выхода элемента И 76

5 регистра б и образуемых из тактовых импульсов генератора (ГИГ), поступающих на вход элемента 76 блока 6 с выхода D-тригге- ра 30.

Изменение состояния выхода регистра 36 в цикле 1 и цикле 2 после запуска программы контроля определяется наличием 1 на первом входе регистра 36 и ТИ5 на входе С регистра 36, поступающего с выхода блока 38 нагрузочных резисторов для открытых коллекторов формирователя 37, а в последних двух циклах-цикле F-1 и цикле F приходящим сигналом КПК (конец программы контроля) с блока 5 на третий вход регистра 36 и ТИ5 с блока 38 СДВИГ 1 и сигнала КПК определяется обратной связью первого и третьего выхода регистра 36 сдвига с соответствующими его вторым и четвертым входами. Формирование ТИ1-ТИ8 между циклом 2 и циклом F-1 (циклы 3-F-2) определяется статическим состоянием ре- гистра 36, т.е. на первом и втором его выходах установлены сигналы 1, а на третьем и четвертом - сигналы О. Временная диаграмма приведена при значении кода задержки сравнения (КЗС), равным 0, соответственно время минимальной задержки сравнения ТМин определяется выраже- нием.

Тмин З.Т,

где Т - длительность периода ТИГ.

Временная диаграмма (фиг.Ю) образуется вырезкой блоком 6 ТИС, поступающих на вход +1 счетчика-35, в соответствии с заданным значением КЗС. На временной диаграмме показаны последовательно за- держки сравнения на один и два периода ТИГ. Время задержки сравнения (Тзс) при КЗС отличным от 0 определяется выражением

Тзс - Тмин + (КЗС + 1)Т,

где КЗС -. число периодов Т, необходимое для задержки сравнения.

С выхода блока 4 ТИ1 передаются на блок 5, ТИЗ - на регистр 6 и блок 10, ТИ4 - на блок 5, ТИ5 - на блок 10 и драйверы-ком- параторы 11-11п,ТИ6-на блок 5 и 10, ТИ7 - на блок 5. Внутри блока 4 используются ТИ2,ТИ5иТИ8.

Генератор 41 вырабатывает импульсы типа МЕАНДР и передает их на вход С D- триггера 30. Этот триггер по цепи обратной связи через элемент 39 обеспечивает деление импульсов генератора 41 на 2. С прямого выхода D-триггера 30 на выходе блока формируются ТИГ и передаются на регистр 6. Управление формированием ТИГ осуществляется D-триггерами 29, 31 и 32, выходы которых соединены с входами элемента И 39, обеспечивая или запрещая обратную связь D-триггеру 30. В исходное состояние блок устанавливается сигналом СВР с блока 2. При этом выходы счетчика 35 и регистра 36 устанавливаются в состояние О, выход D-трйггера 29 (сигналом СВР через элементы 28, 42)- в состояние 1, выход D-триггера 32 (сигналом СВР через элемент 45) - в состояние 1, выход D-триггера 31 - в состояние О, кроме того по сигналу СВР через элемент 45 инверсные выходы D-триг- геров 33, 34 принимают значение 1. Поступление О с выхода D-триггера 31 на элемент 39 разрывает обратную связь D- триггера 30, чем запрещается формирование ТИГ с блока.

Запуск формирователя ТИГ осуществляется импульсным сигналом ЗПК (запуск программы контроля) с регистра 8 с уровнем 1, при этом запишется 1 в D-триггер 31, чем обеспечивается обратная связь через элемент 39 - D-триггеру 30, Останов формирования ТИГ в процессе проверки ОК осуществляется при поступлении на блок либо сигнала ОПК (останов программы контроля) с блока 5, равным 1, либо при установленном сигнале РР1 (режим работы) Т с регистра 7, равным 1. При этом любой из сигналов ОПК или РР1 через элементы 28,42 устанавливает на вход установки D-триггера 29 1, а приходящий ТИ2 фронтом Из О в 1 запишет в D-триггер О, чем разрывается обратная связь D-триггера 30 через элемент 39.

Кроме того останов формирования ТИГ обеспечивается поступающим О на эле мент 39 с выхода D-триггера 32. Запись О в D-триггер 32 осуществляется сигналом Г с выхода элемента ИЛИ-НЕ 48 на вход которого поступают либо сигнал СКК (сброс коммутации каналов) с драйверов-компараторов 11i-11n с уровнем О, либо по ТИ2, приходящим через первые входы элементов И-НЕ 47 и 46 при наличии сигнала , НС (несравнение) на втором входе элемента 47 с блока 10, равным О, сигналов РР2 (режим работы 2) с регистра 7 и РСР (разрешение сравнения) с блока 5, равными 1, на втором и третьем входах элемента 46, либо по ТИВ с выхода элемента И 40 при наличии сигнала КПК с блока 5, поступающим через элемент НЕ 44 на другой вход элемента И 40. .

Триггер 34 предназначен для запоминания сигнала СКК, поступающего на вход S D-триггера 34 и передачи с его инверсного выхода уровнем О на регистр 9. D-триггер 33 служит для запоминания сигнала НС, образованным по ТИ2 через элементы 47 и 46 при наличии разрешающих сигналов РР2 и РСР на элементе 46, воздействием на вход 3 D-триггера 33. С инверсного выхода D- триггера 33 сигнал НС уровнем О передается на регистр 9. Кроме того на регистр 9 с выхода D-триггера 32 передается сигнал ОП1 (останов программы 1), определяющий останов формирования ТИГ по сигналам

1ЛИ НС, ИЛИ СКК, ИЛИ КПК, а с выхода -триггера 29 передается сигнал ОП2 (оста- юв программы 2) по сигналу ОПК или по :игналу РР1. Для продолжения ПК с регист- )а 8 подается сигнал ЗПК (запуск программы контроля). Этот сигнал устанавливает (ыходы D-триггеров 29, 31 и 32 В 1, а -триггеры 33, 34 - В О, что обеспечивает туск на продолжение работы ПК. Резисто- ы 49 и 50 являются нагрузками для монтаж- юго ИЛИ соответственно сигналов НС и

:кк.

Блок 5 памяти команд (фиг.4) служит для ;ранения в ОЗУ 52i-52x, записываемых в ше, микрокоманд (где X - количество элементов ОЗУ, соответствующее разрядности микрокоманды), определяющих последова- ельность выборки из блока 10 каналов тесовых наборов. Запись микрокоманд в ОЗУ осуществляется сигналами записи с дешифратора 3, поступающими на входы W W вход записи) соответствующих элемен- ов ОЗУ. Данные о значениях разрядов микрокоманды поступают поочередно по 6 разрядов с ШД из блока 2 через буфер 6 при разрешающем сигнале на его входе :Z с дешифратора 3 (EZ-вход разрешения, нимающий третье состояние с входов и ыходов буфера 56). Адреса на ОЗУ 521- Ь2Х при записи микрокоманд поступают с егистра 55, запись значений адресов в ко- орый осуществляется с ШД сигналом запи- :и с дешифратора 3 по входу С при сигнале 5РЗ (режим работы 3) с регистра 7. равным 1, определяющий снятие третьего состояния выходов регистра 55 воздействием че- ез элемент НЕ 64 на вход EZэтого регистра установку в третье состояние выходов ормирователя 51 по входу ES.

Каждая, микрокоманда, записываемая ОЗУ , содержит в своем составе код операции (КОП), адрес перехода или оличество циклов (АЦП), КЗ С, адрес тесто- ого набора (АТН), КПК: ОПК и РСР. КОП пределяет формирование адреса следую- 1|цей микрокоманды. АПЦ определяет безусловный переход к любому адресу микрокоманды, или условный переход к на- 1альному адресу групп микрокоманд, выде- / яемых в качестве подпрограмм контроля (Ж, или условный возврат из подпрограмм, или количество циклов (повторений) выбранного участка адресов микрокоманд. АТН определяет адрес тестового набора, передаваемого на ОК из ОЗУ 78-81 блока О, КПК, включаемый в последней микрокоманде ПК, осуществляет останов устройства по окончании проверки ОК. ОПК осуществляет останов ПК на той микрокоманде, в которую он включен. РСР. равный 0 включается в те микрокоманды, при выполнении которых необходимо запретить останов ПК по несравнению (особенно это необходимо при выполнении установочных тестовых наборов, когда информация на выходе О К может быть неопределенной). Во всех остальных микрокомандах РСР присваивается значение, равное 1, формат И функциональное назначение разрядов мик0 рокоманды приведены в табл.1, а соответствие кодов операции их функциональному назначению в табл.2.

С выхода ОЗУ информация микрокоманды поступает на вход регистра 53

5 микрокоманд, запись которой осуществляется по ТИ4 через элемент 63 с блока 4. С выхода регистра 53 КОП и АПЦ поступают на входы формирователя 51 адресов микрокоманд, а запись в него КОП и АПЦ осуще0 ствляется по ТИ1, приходящим с блока 4 через элемент 62. АТН передается на вход буфера 57 и на блок 10, КПК - на блок 4 и регистр 9, КЗС - с инверсных выходов на блок 6. ОПК и РСР переписываются по ТИ4

5 из регистра 53 в регистр 54 перезаписи, чем обеспечивается их воздействие в соответствующих циклах временной диаграммы (фиг.ба и 86). С выхода регистра 54 ОПК и РСР поступают на блок 4 и регистр 9. Сброс

0 регистров 53, 54 осуществляется по входам R сигналом СВР с блока 2.

Блок 5 также обеспечивает формирование адресов тестовых реакций (АТР) на ОЗУ 82 блока 10, для чего применен последова5 тельный счетчик 61-|-61у для счета ТИ7 с блока 4 по входу +1 со сбросом В О сигналом СВР, поступающим с блока 2 через элемент 65 на его входы R. В счетчике 611-61у предусмотрена запись с блока 2 по

0 ЩД начального адреса параллельным кодом сигналами записи, поступающими на входы W с дешифратора 3. С выходов счетчика 61 АТР поступают на блок 10, на, вход буфера 59 и на вход ОЗУ 60 трассы

5 адресов микрокоманд, где обеспечивают адресацию этого ОЗУ. ОЗУ 60 трассы обеспечивает запись м хранение трассы адресов микрокоманд, поступающих на вход данных ОЗУ 60 и записываемых в нее лоТИбс блока

0 4, С выхода ОЗУ 60 трассы данные передаются на буфер 58. Буферы 57-59 данных обеспечивают соответственно передачу АТН, данных трассы и АТР ОЗУ 82 по ШД на блок 2 и далее на ЭВМ при соответствующих

5 сигналах чтения, поступающих на входы EZ с дешифратора 3, снимающих третье состояние выходов буферов.

Регистр 8 кода задержки (фиг.5) обеспечивает задержку сравнения ответной реакции ОК на воздействие тестового набора на

входы OK, K3C поступает с блока 5 в инверсном коде, на информационные входы параллельного Счетчика 66. Поступающий с блока 4 ТИЗ, проходя через элемент ИЛИ 68 на вход разрешения параллельной записи L счетчика 6, и передний фронт ТИЗ, задержанный элементом НЕ 71 и элементами ИЛИ 70 и 69, поступающий на вход С счетчика, обеспечивают параллельную запись КЗС в счетчик. Аналогично производится за- пись КЗС сигналом СВР с блока 2. Т.к. КЗС в блоке 5 равен 0 (сигнал СВР в блоке 5 сбрасывает регистр 53 в О), в счетчике 66 все разряды установятся в 1. Кроме того сигнал СВР, проходя через элемент НЕ 72 и ИЛИ-НЕ 74 устанавливает D-триггер 67 по входу установки S в положение: на прямом выходе в 1, на инверсном - О. С прямого выхода сигнал 1, поступая на вход элемента И 66 разрешает формирование на выходе этого элемента ТИС из поступающих на его другой вход ТИГ. С инверсного выхода сигнал О запрещает по входу разрешения по- следовательного счета Е счетчика 66 последовательный счет импульсов, прихо- дящих на его вход С. А также запрещает прохождение через элемент И 75 на вход С счетчика 66 ТИГ, поступаю.щих на другой вход элемента 75 через элемент НЕ 73 с блока 4.

В таком положении регистр 6 будет находиться как после воздействия сигнала СВР, так и при записи в счетчик 66 КЗС, равным 0. В счетчике будет записано максимальное число, при котором на его выходе переноса Р будет установлен сигнал 1, последняя будет удерживать через элемент ИЛИ 74 D-триггер 67 сигналом О по входу 3 в устойчивом состоянии (на прямом выходе 1, на инверсном - О).

При записи КЗС в счетчик 66 отличным от 0 на выходе Р счетчика возникает сигнал О, который через элемент ИЛИ 74 установит 1 на входе 3 D-триггера 67. Задний фронт ТИЗ, воздействуя на вход С 0-тригге- ра 67, установит прямой выход D-триггера 67 в О, а инверсный выход в 1, при этом сигнал О, поступая на элемент И 76 запретит формирование ТИС, а сигнал 1 разре- шит счет импульсов счетчиком 66 и прохождение ТИГ через элемент И 75 и далее через элемент ИЛИ 69 на вход С счетчика 66, что обеспечивает счет ТИГ счетчиком 66. Т.к. в счетчик 66 запись КЗС инверсна, то при досчете ТИГ образуется задержка сравнения реакции ОК. как это показано на фиг.9. При максимальном числе в счетчике 66 на его выходе Р образуется 1, чем прекращается отработка времени задержки

сравнения и разрешается выработка ТИС на блок 4.

Регистр 7 управления режимами представляет собой 3-х разрядную регистровую память, записываемых в нее с ШД блока 2 сигналом записи с дешифратора 3, значений сигналов РР1, РР2, РРЗ. С выхода регистра 7 сигнал РРЗ поступает на блок 5, а сигнал РР1 и РР2 на блок 4. Сигнал РР1, равным О, обеспечивает в устройстве непрерывный режим выборки тестовых наборов из блока 10. при значении, равным 1 - ШАГОВЫЙ. Сигнал РР2, равный 1, обеспечивает останов ПК по несравнению, при значении, равным О - запрет останова по несравнению. Сигнал РРЗ, равный 1, определяет выборку адресов ОЗУ 52i-52x с регистра 55 при загрузке в ОЗУ 52i-52x микрокоманд с ЭВМ, равным О - с формирователя 51.

Соответствие информационных разрядов регистра 7 и режимов работы устройства приведены в табл.3.

Регистр 8 пуска предназначен для выработки сигнала НУ (начальной установки) и сигнала ЗПК с передачей их соответственно на блок 2 и блок 4. Реализуется регистр;, на формирователях одиночных импульсов,- запускаемых наличием сигнала с дешифратора 3 и значения 1 в соответствующем разряде данных, поступающих по ШД с блока 2 при одиночном адресном обмене ЭВМ.

Регистр 9 состояния применяется для опознования причин останова ПК ОК по поступающим на его входы сигналам ОП1, ОП2, НС, СКК с блока 4 при их значении, равными О, и сигналов ОПК, КПК с блока 5, равными 1, а также для чтения состояния сигнала РСР, поступающего на вход регистр 9 с блока 5. Для чтения информации регистра 9 на его вход поступает сигнал чтения с дешифратора 3 адреса, при этом снимается третье состояние выходов регистра и информация с регистра поступает по ШД на блок 2 и далее на ЭВМ.

Блок 10 коммутации (фиг.6) обеспечивает запись, хранение и передачу тестовых наборов и реакций О К соответственно на компараторы и на вычислительный комплекс 1. Запись информации о коммутации каналов, тестовых воздействиях, установке потенциальных или импульсных режимов каналов и маски каналов тестовых наборов, поступающих с ШД из блока 2, производится соответственно в ОЗУ 78, ОЗУ 79, ОЗУ 80 и ОЗУ 81 сигналами записи, поступающими с дешифратора 3. Адреса на ОЗУ 78-81 при загрузке тестовых наборов в эти ОЗУ с ЭВМ поступают через регистрмультиплексор 77 с ШД из блока 2, Запись щресов в регистр-мультиплексор 77 осуществляется сигналом записи, проходящим с дешифратора 3 через элемент ИЛИ 97 на }ход записи С при соответствующем сигна- те переключения на входе Т регистра-мультиплексора с дешифратора 3. С выходов ЭЗУ 78-81 информация тестовых наборов юступает на входы регистров 83-86. Запись тестовых наборов в эти регистры осу- дествляется по ТИЗ с блока 4, проходящим (врез элемент НЕ 99. Запись АТН, приходя- дих с блока 5 при работе ПК, осуществляется по ТИБ с блока 4, поступающим на вход С регистра-мультиплексора через элемент ЛЛИ 97.

Установку выходов регистров 84-86 в состояние О осуществляется сигналом 2БР с блока 2, а регистра 83 коммутации саналов - сигналом СКК с драйверов-компа- заторов 111-11пИли, сигналом СВР через )лемент ИЛИ 98. Свыхода регистра 83 информация о коммутации каналов (КК) посту- 1ает на драйверы-компараторы и на вход эуфера 88, обеспечивающего чтение инфор- нации о коммутации каналов текущего тес- ового набора. Информация тестового юздействия с регистра 84 поступает на вто- юй вход переключателя 92, на третий вход которого поступает информация с регистра 35. При значении О разрядов информации с регистра 85 через переключатель 92 будет передаваться информация тестового набо- эа с регистра 84. при значении любого раз- эяда (любых разрядов), равный 1, на 5ыход переключателя по этим разрядам (каналам) будут передаваться сигналы кодовых тачек ПЧК, поступающих на первый вход переключателя 92 с буфера 12 (по остальным каналам будет передаваться информа- дня тестового воздействия). С выхода переключателя 92 информация тестового юздействия (ТВ) поступает на драйверы- сомпараторы.

Кроме того информация о тестовом воз- действии поступает на вход схемы 90 сравнения и на вход буфера 89, выход которого соединен с ШД для передачи текущего зна- енйя тестового воздействия на блок 2 сигналом чтения с дешифратора 3.

Схема §0 сравнения обеспечивает сравнение поступающих на ее вход информации тестовых воздействий с регистра 84 с информацией тестовых реакций (ТР) с драйве- эов-компараторов. С выхода схемы 90 результат сравнения поступает на второй зход схемы 91 запрета сравнения, на пер- зый вход которой поступает информация с эегистра 86 о разрешении передачи результата сравнения в к.аналах при значении разрядов, равными 1 и запрета передачи результата сравнения - при значении разрядов, равным О. Все выходы каналов в схеме 91 объединены в монтажное ИЛИ. С выхода схемы 91 сигнал НС при несравнении СВ разрешенных каналах сравнения передается на блок 4.

Запись тестовых реакций в ОЗУ 82, поступающих на ее первый вход по линии ТР с компараторов , осуществляется по ТИ6 приходящих с блока 4 на второй вход ОЗУ 82. Адреса для записи тестовых реакций поступают на третий вход ОЗУ 82 по линии АТР с блока 5. Передача информации о тестовых реакциях с выхода ОЗУ 82 по ШД на блок 2 производится через буфер 87 по сигналу чтения, поступающего на вход буфера, с дешифратора 3.

Стабилизатор 94 опорного напряжения первого диапазона уровней, стабилизатор 95 опорного напряжения второго диапазона уровней и стабилизатор 96 смещения уровней обеспечивает питающее напряжение высокой стабильности для ЦАП компараторов 111-11п.

Переключение опорных напряжений, вырабатываемых по линии 1, осуществляется выходными сигналами D-триггера 93, прямой выход которого, равным О, включает стабилизатор 94, а инверсный - равный О, стабилизатор 95. С объединенных выходов стабилизаторов 94 и 95 опорное напряжение передается на драйверы-компараторы . Запись информации О или 1 в D-триггер 93 осуществляется с ШД из блока 2, сигналом записи с дешифратора 3, поступающим через элемент НЕ 100 на вход С D-триггера 93.

Стабилизатор 96 вырабатывает напряжение смещения, равным 58, которое с его выхода по линии передается на компараторы 111-11п, чем обеспечивается работа ЦАП в компараторах сигналами с уровнями ТТЛ, поступающими на информационные, входы ЦАП.

Стабилизаторы 94, 95 и 96 выполнены по классической схеме параметрического стабилизатора с преобразованием напряжения +20 В в регулируемое напряжение на выходе стабилизатора 94 в-пределах от 6 до 10 В, на выходе стабилизатор 93 - от 9 до 15 В, чем обеспечивается регулировка выходных логических уровней компараторов 11i 11П на первом диапазоне в пределах от минус 5 до плюс 5 В с шагом 40 мВ, на втором диапазоне - от минус 10 до плюс 10 В с шагом 80 мВ.

Компараторы 111-11П каналов осуществляют коммутациию каналов устройства входами-выходами, запись и хранение кодов уровней и формирование в соответствии с этими кодами уровней О и 1 в каналах, установленных выходами для воздействия на входные контакты ОК и в каналах, установленных входами для сравнения с сигналами 0м и 1, поступающих с выходных контактов ОК, а также обеспечивают формирование тестовой реакции ОКдля передачи на блок 10. В устройстве применяются компараторы (по числу каналов устройства), каждый из которых (фиг.7) может быть установлен как входом, так и выходом.

ОЗУ 107 кодов уровней с организацией 4ХВ БИТ обеспечивает запись, хранение и выборку четырех, восьмиразрядных кодов уровней для входных и выходных сигналов О и 1. При записи кодов уровней двуразрядный адрес на ОЗУ 107 поступает на его входы по ШАс блока 2. При коде адреса 00 производится запись кода уровней входного сигнала О, при коде 01 - входного сигнала 1, при коде 10 - выходного сигнала О и при коде 11 - выходного сигнала 1. Данные кодов уровней поступают по ШД с блока 2 на вход О ОЗУ 107, а запись их осуществляется сигналом записи с дешифратора 3, приходящим на вход записи ОЗУ 107 через элемент И 106 при разрешающем сигнале на другом входе элемента 106 с инверсного выхода регистра 105. Разрешение записи кодов уровней в ОЗУ 107 обеспечивается записью 1 в регистр 105, которая, поступая на его вход С с ШД из блока 2 записывается сигналом записи с дешифратора 3. Для максимального использования разрядов ШД драйверы-компараторы организуются в группы по 16 драйверов-компараторов (по числу разрядов ШД), что обеспечивает запись в регист- ры 105 16-ти драйверов-компараторов одним сигналом записи с дешифратора 3 в каждой группе компараторов. Запись 1 или О в регистр 105 данного канала, а также и в других каналах, обеспечивает как индивидуальное так и одновременное групповое программирование входных и выходных уровней О и 1 любого количества каналов, что обеспечивает проверку ОК с любыми индивидуальными или смешан- - ными уровнями входных и выходных сигналов О и 1. Сигналом СВР с блока 2 регистр 105 устанавливается в запрещающее положение записи кодов уровней в ОЗУ 107.

Выборка кодов уровней из ОЗУ 107 осуществляется двухразрядным адресом на ее входах AR. Младший разряд адреса выбирается i-м разрядом информации тестового воздействия соответствующему i-му номеру

канала, приходящим с блока 10 по линии ТВ через перемычку 103, элемент 101 задержки и через перемычку 104 на младший вход AR. Старший разряд адреса выбирается i-м разрядом информации коммутации каналов (разрядом, аналогичным разряду информации тестового воздействия), поступающим с блока 10 по линии КК на старший вход AR. Соответственно при значении 1-го разряда информации коммутации канала, равным О, из ОЗУ 107 будут выбираться коды уровней входных сигналов О и 1, при значении 1 - выходных сигналов О и 1, а поступающее значение i-ro разряда информации тестового воздействия, равным О, определяет выборку кода уровня О, равным 1 - 1.

Элемент 101 задержки, имеющий в своем составе прямое включение первого входа и первого выхода в блок 102 элементов И, в котором вход первого элемента И соединен с вторым входом блока 101, а выход первого элемента И блока 102 с вторым выходом блока 101 и т.д., обеспечивает регулировку задержки переключения разряда информации тестового воздействия из О в 1 и из 1 в О на входе AR ОЗУ 107. Регулировка задержки позволяет получить разброс переключений выходных сигналов О и 1 на выходе канала в пределах времени задержки распространения сигнала через один логический элемент И. Регулировка задержки осуществляется переключением перемычки 103 к второму входу элемента 101, переключением перемычки 104 к второму и т.д. выходу элемента 101 и включением дополнительных перемычек, в зависимости от числа включаемых в задержку сигнала элементов И блока 102, исходя из максимальной задержки, полученной в одном из компараторов 11i-11nnpn, подключенных перемычках 103, 104 соответственно к первому входу и первому выходу элемента 101.

С выхода ОЗУ 107 код уровней поступает через блок 108 резисторов смещения входных уровней ЦАП на первый вход ЦАП, на второй и третий входы которого поступают с блока 10 соответственно опорное напряжение 01 через резистор НО и напряжение 02 смещения уровня ЦАП через резистор 111. Резистор. 111 обеспечивает регулировку выходных напряжений ЦАП - регулировку шага выходных напряжений. Резистор 111 совместно с блоком 106 осуществляют смещение уровней для входных сигналов ЦАП, что обеспечивает согласование управления ЦАП с поступающими на первый вход ЦАП сигналами О и 1 с уровней ТТЛ. Разнополярные токи на выходе

ЦАП, в зависимости от значения кода уровня напряжения, поступающего на его входы, образуют на согласующих резисторах 125 и 126 соответственно разнополярные напряжения 03 и 04, которые поступают на резисторы 127 и 128 драйвера, состоящего из резисторов 127-135, 140, 141 операционного усилителя (ОУ) 112, эмиттерного повторителя 113, транзисторов 123 и 124, ключей .114-116 и элементов 119, 120, 122. Напряжение 03 через резистор 127 поступает на второй инвертирующий вход, а напряжение 04 через резистор 128 - на третий неинвертирующий вход ОУ 112. Выход ОУ 112 подключен к второму входу эмиттерного повторителя 113, обеспечивающего усиление по мощности выходного сигнала ОУ. Выход эмиттерного повторителя соединен с первыми входами ключей 114, 116 и с резистором 138. В цепи питания эмиттерного повторителя установлены резистор 131, подключенный к первому входу эмиттерного повторителя, базе транзистора 128 и резистору 133, и резистор 132, подключенный к третьему входу эмиттерного повторителя и базе транзистора 124. Эмиттер транзистора 131 подсоединен к цепи питания +15 В, а коллектор - к резистивному делителю напряжения на резисторах 134 и 135, средняя точка которых соединена с входом элемента 122. Коллектор транзистора 124 соединен через резистор 133 с базой транзистора 123, а эмиттер - с цепью питания -15В; Резисторы 131-135 и транзисторы 123, 124 обеспечивают формирование сигнала 1 с уровнем ТТЛ на входе элемента 122 при превышении предельного.максимального тока эмиттерного повторителя 113 и открытого ключа 116 в случае замыкания выхода драйвера на корпус или попадания на выход драйвера напряжения источника питания ОК. Выход эмиттера 122 i-ro драйвера и выходы элементов 122 других компараторов соединены между собой и поступают по линии СКК на блок 4, где совместно с резистором 50 образуют схему монтажного ИЛИ для останова программы контроля ОК и поступают на вход блока 10 для сброса в О регистра 83 коммутации каналов, что обеспечивает защиту выхода из строя драйверов при перегрузке их по току.

Для формирования выходных сигналов О и 1 на выходе драйвера при включении канала выходом и для формирования сигналов О и 1, поступающих через резистор 138 на инвертирующий вход компаратора 118 при включении канала входом, в драйвере организованы соответственно первая и вторая цепи обратной связи ОУ 112. В первой цепи обратной связи выход ОУ соединен с вторым входом эмиттерного повторителя 113, выход которого соединен с первым входом открытого ключа 116, а выход ключа 116 соединен с выходом открытого

ключа 115, вход которого соединен с выходом закрытого ключа 114 и через резистор 129 с вторым входом ОУ 112. Во второй цепи обратной связи выход ОУ 112 соединен с вторым входом эмиттерного повторителя

113, выход которого соединен с первым входом открытого ключа 114, а выход ключа 114 соединен также через резистор 129 с вторым входом ОУ, при этом ключи 115 и 116 закрыты. Переключение первой и второй цепей обратной связи обеспечивается соответствующим данному номеру канала 1-ым разрядом коммутации канала, поступающим с блока 10 через элемент 119 с открытым коллектором на второй вход ключа 114

и на вход элемента 120 также с открытым коллектором, выход которого подключен к вторым входам ключей 115 и 116. Резисторы 140 и 141 являются нагрузками для открытых коллекторов соответственно элементов

119 и 120. При значении 1-го разряда коммутации канала 1, поступающим на вход элемента 119, ключ 114 закрыт, а ключи 115 и 116, открыты, чем осуществляется включение первой цепи обратной связи для ОУ 112,

обеспечивающую формирование выходных сигналов О и 1 канала - канал установлен выходом. При значении i-ro разряда коммутации канала О ключ 114 открыт, а ключи 115 и 116 закрыты, чем осуществляется

включение второй цепи обратной связи для ОУ 112, обеспечивающую формирование сигналов О и 1 на третьем инвертирующем входе компаратора 118 через резистор 138 канал установлен входом. Резистор 129

обратной связи, подключенный к второму входу ОУ 112, и резистор 130, соединенный с третьим входом ОУ и корпусом, совместно с резисторами 127 и 128 образуют дифференциальную схему усиления ОУ 112, при

этом на выходе драйвера или на резисторе 138 при Р127 Р128 и Р129 Р130 образуется напряжение U.

U |jff (U2-U3),

где R127, R128, R139 и R130 - резисторы 127-130.

Т.к. коэффициент усиления ОУ 112 вы- бран равным 5, то соответственно соотношение устанавливаемых резисторов Р129 и

Р127 и Р130и Р128 равно, как 4:1, что обеспечивает получение напряжения на выходе драйвера от минус 5 В до плюс 5 Б на первом диапазоне ЦАП с шагом 40 мВ и от ми-нус 10 В до плюс 10 В на втором диапазоне ЦАП с шагом 80 мВ.

Сравнение уровней сигналов О и 1, поступающих с выходов ОК на вход- компаратора, включенного входом, обеспечивается компаратором 118. Сигналы с ОК поступают на второй вход истокового повторителя 117, имеющего входное сопротивление как и у выходов микросхем в третьем состоянии. Выход истокового повторителя связан через резистивный делитель на резисторах 136 и 137 с четырьмя неинвертирующим входом компаратора 118, на первый инвертирующий вход которого через делитель на резисторах 138 и 139 поступают уровни сигналов О и 1 с выхода эмиттер- ного повторителя 113. Для оптимальной работы компаратора 118 резисторы 146, 137 и резисторы 138, 139 обеспечивают деление входных напряжений компаратора, как 4:1. Запись информации в компараторе 118 результата сравнения уровней, определяющих информацию тестовой реакции ОК, производится по ТИ5, поступающих с блока 4 на второй вход компаратора. Выход компаратора 118 через элемент 121 связан с соответствующим i-ым разрядом линии ТР для передачи информации с тестовой реакции в данном канале на блок 10.

Входной буфер 12 кодовых пачек, выход которого соединен с блоком 10, выполняет функцию согласования выходов, подключаемых к буферу 12 внешних формирователей кодовых пачек, с входом блока 10.

Устройство работает следующим образом.

Обмен информацией ЭВМ с внешними устройствами, в качестве которых являются блоки, дешифратор, регистры и (драйверы) компараторы устройства, осуществляется по МПИ стандартными процедурами. Программа контроля ОК, составленная на языке высокого уровня, в качестве которого может быть использован язык ТЕСТ 5 и др., хранящаяся во внешней магнитной памяти вычислительного комплекса 1, включает в себя: записьсигнала РР34, равный 1, и сигналов РР1, РР2 в регистр 7 в соответствии с выбранным режимом работы устройства согласно табл.3; последовательность записи адресов в регистр 55 с соответствующей последовательностью записи микрокоманд, составленных в соответствии с табл.1, 2, для загрузки ОЗУ 52г-52х в блоке 5; последовательность установки адресов в регистре - мультиплексоре 77 с соответствующей последовательностью записи тестовых наборов, в составе каждого из которых содержится коммутация каналов, тестовое воздействие, потенциально- импульсный режим каналов и маска каналов, для загрузки ОЗУ 78-81 блока 10;

установку выбранного диапазона уровней О и 1 входных и выходных сигналов - компараторов в регистре 93 блока 10; последовательность установки в регистрах 105

разрешения программирования уровней О и 1 входных и выходных сигналов или индивидуально в каждом драйвере - компараторе, или в группах драйверов - компара- торов (или одновременно для всех

0 драйверов - компараторов) с соответствующей последовательностью пересылки кодов уровней О и 1 входных и выходных сигналов в ОЗУ 107 компараторов 11.1-1 In и последовательностью записи в регистры

5 105 запрета программирования уровней; перезапись сигнала РРЗ равным О в регистр 7.

Первоначально в ЭВМ с внешней магнитной памяти загружается, хранящаяся в

0 этой памяти, операционная система ТЕСТ (ОС ТЕСТ) или др. ОС под управлением ОС ТЕСТ (или др. ОС) загружается и хранится в ЭВМ программа контроля ОК, далее программа контроля ОК из ЭВМ через блок 2 с

5 помощью сигналов записи с выхода дешифратора 3 загружается в блоки 5 и 10, в регистры 7 и 8 и в компараторы 111-11П. В конце загрузки в регистре 7 изменяется значение сигнала РРЗ на О, чем обеспечивается в

0 блоке 5 установка выходов регистра 55 в третье состояние и разрешение выбора микрокоманд из ОЗУ 52i-52x по адресам, вырабатываемых формирователем 51 адресов микрокоманд.

с Запуск программы контроля ОК осуществляется последовательной передачей из ЭВМ в регистр 8 пуска сигналов НУ и ЗПК, после чего ЭВМ переходит в режим постоянного опроса значений разрядов регистра

0 9 состояния. По сигналу НУ с выхода регистра 8 производится сброс устройства в исходное состояние, при этом на выходе регистра 53 микрокоманд установится значение КОП, равным 0000. По сигналу ЗПК, поступающему на блок 4, обеспечивается запуск формирователя ТИГ на выходе D- триггера 30 записью 1 в 0-триггер31.ТИГ, проходя через элемент И 76 регистра 5, Образуют. ТИС на его выходе, которые поступают на вход счетчика 35 блока 4. Вся дальнейшая работа устройства определяется формированием ТИ1-ТИ8 блоком 4 в соответствии с временными диаграммами (фиг.8, 9 и 10) и содержанием выполняемых

5

0

микрокоманд.

ТИ1 обеспечивает запись в формирователь 51 значений КОП и АПЦ, определяющие режимы работы формирователя и последовательности установки на его выходах значений адресов для выборки микрокоманд из ОЗУ 52-52. Выборка первой микрокоманды всегда начинается с нулевого адреса ОЗУ, т.к. по первому ТИ1 в формирователь 51 запишется значение КОП, равное 0000 (регистр 53 сброшен в О по сигналу НУ), при котором.формирователь 51 сбрасывается в исходное состояние и на его выходе устанавливается нулевой адрес для ОЗУ 52i-52x. С приходом сигнала КПК, равным 1, а последней микрокоманде формирование ТИ1 в блоке 4 {в последних двух циклах F-1 и F) прекращается.

ТИ2 по переднему фронту осуществляет запись результата сравнения реакции ОК (значения сигнала НС с выхода блока 10) через элементы 47,48 в D-триггер 33 и далее через элемент 48 в D-триггер 32. Если сигнал НС равен О (при несравнении), то при разрешающих сигналах РР2 с регистра 7 и РСР из микрокоманды с блока 5 на выходах D-триггеров 32 и 33 установится О, чем остановится формирование ТИГ и возникнет сигнал останова программы ОП1, равным О, передаваемый на регистр 9 состояния. На первых двух циклах ТИ2 не вырабатывается. Кроме того по заднему фронту ТИ2 осуществляет останов программы контроля по каждому тестовому набору, если установлен шаговый режим работы устройства, т.е. сигнал РР1 с регистра 7, равен 1, или в выполняемой микрокоманде разряд ОПК равен 1. Каждый из этих сигналов, проходя через элементы 28 и 42 в блоке 4, устанавливают на 3 входе D- триггера 29 сигнал 1, а приходящий задний фронт ТИ2 записывает в этот триггер О, чем прекращается формирование ТИГ и осуществляется передача сигнала останова программы ОП2, равным О на регистр 9.

ТИЗ передним фронтом осуществляет запись значения КЗС с регистра 53 микрокоманд блока 4 в счетчик 66 регистра 6 и запись тестового набора из ОЗУ 78-81 в регистры 83-86 блока 10. По заднему фронту ТИЗ осуществляется запись О в D-триггер 67. Если записанный КЗС в счетчик 66 отличен от О, чем обеспечивается запрет формирования ТИС через элемент 76 на выходе регистра 6, разрешается счет импульсов счетчиком 66 и разрешается прохождение импульсов ТИГ на вход счетчика через элементы 75 и 69 (фиг. 10) Так как счетчик 66 работает на досчет импульсов (КЗС в него записывается с инверсных выходов регистра 53), то при достижении в счетчике максимального числа сигнал 1 с его выхода через элемент ИЛИ-НЕ 74. воздействуя на 3 вход D-триггера 67. установит его в разрешающее положение для формирова0

5

0

5

0

5

0

5

0

5

ния ТИС и в запрещающее положение счета импульсов счетчиком 66 и прохождения импульсов ТИГ через элемент 75, чем и заканчивается отработка значения КЗС.

ТИ4 обеспечивает передним фронтом запись значения микрокоманды из ОЗУ 52- 52 в регистр 53 микрокоманды и регистр 54. В последних двух циклах F-1 и F при значении разряда КПК в микрокоманде, равным 1, ТИ4 не вырабатывается,

ТИБ обеспечивает запись передним фронтом значения АТНС с блока 5 в регистр - мультиплексор для установки адреса на ОЗУ 78-81 в блоке 10, определяющего выборку из ОЗУ очередного тестового набора программы контроля ОК. В последних двух циклах F-1 и F временной диаграммы при значении в микрокоманде разряда КПК, равным 1, ТИ5 не формируется. Кроме того ТИ5, поступая на компараторы 11i-11n обеспечивает запись в компараторах 118 результата сравнения уровней сигналов О и 1 с выходов ОК и сигналов, определяющих эталонную информацию тестового воздействия, а также обеспечивает по заднему фронту запись значения разряда КПК, равным 1, из последней микрокоманды в регистр 36 блока 4 для формирования временной диаграммы циклов F-1 и F.

ТИ6 осуществляет запись тестовых реакций ОК, поступающих с компараторов 111-11П в ОЗУ 82 блока 10 и запись значений трассы адресов микрокоманд в ОЗУ 60 блока 5. В циклах 1 и 2 временной диаграммы ТИ6 не формируется.

ТИ7 используется для наращивания по заднему фронту адресов на +1 в счетчике 61i-61y блока 4 для ОЗУ 82 блока 10. В циклах 1 и 2 временной диаграммы ТИ7 не формируется.

ТИЗ формируется в последнем цикле F при значении разряда КПК (номера) ТН и АТР. на которых произошло несравнение разрядов тестового воздействия и тестовой реакции ОК.

После останова программы контроля или в шаговом режиме, или по сигналу ОПК или по сигналу НС, продолжение исполнения программы осуществляется очередной посылкой сигнала ЗПК с ЭВМ через регистр 8 на блок 4, по которому выходы D-триггеров 29, 31, 32 и 33 установятся в состояние 1, чем обеспечится формирование ТИГ с D-триггера 30 и снимется сигнал НСс регистра 9 состояния, если был останов прогрммы контроля по несравнению тестовой реакции ОК с тестовым воздействием. Информация о тестовых реакциях, накопленная в ОЩУ 82 блока 10 и информация о трассе адресов микрокоманд, накопленная

в ОЗУ 60 блока 5, после останова программы контроля по несравнению тестовой реакции с тестовым воздействием, или после останова программы контроля по КПК в микрокоманде, равным 1, при запрете сравнения значением сигнала РР2 в регистре 7, равным О, переписываются в ЭВМ соответственно через буфер 87 блока 10 и буфер 58 блока 5 для анализа неисправности ОК.

Устройство, позволяет сократить программу контроля за счет прямого доступа выборки адресов тестовых наборов, исключив из программы контроля все повторяющиеся тестовые наборы, и возможности выделения отдельных повторяющихся групп тестовых наборов в подпрограммы с неоднократным обращением к этим группам, имеет возможность вложения подпрограмм в подпрограммы, обеспечивает формирование пачек импульсов любой полярности по любому каналу из двух смежных тестовых наборов с противоположным значением разряда тестового воздействия для этого канала за счет многократного (циклического) повторения последовательности этих двух тестовых наборов, обеспечивает разброс фронтов переключения тестовых воздействий из одного состояния в другое нз выходах каналов устройства при.коммутации каналов выходами в пределах разброса задержки переключения сигналов одного логического элемента И-НЕ с логикой ТТЛ, для снижения вероятности теплового перегрева элементов ОК с двунаправленным обменом информацией через его входные элементы и с двунаправленным обменом информацией между элементами внутри ОК обеспечивается накопление реакций ОК в ОЗУ тестовых реакций и запись трассы адресов микрокоманд в ОЗУ трассы адресов микрокоманд для проверки ОК без останова программы контроля по несравнению реакции ОК с эталоном в тестовом воздействии с последующей передачей записанных в ОЗУ информации на ЭВМ для диагностики неисправностей ОК, обеспечивает передачу от внешнего источника (генератора) кодовых пачек импульсов с широтно-импульсной модуляцией и др. видами модуляции, обеспечивает быстродействие операционного усилителя драйвера - компаратора при формировании им уровней логических сигналов О и 1 для компарации уровней логических сигналов О и 1, поступающих с ОК, таким же как и при формировании уровней логических сигналов О и 1, передаваемых драйвером на входы ОК, позволяет устанавливать значения выходных и входных уровней логических сигналов О и 1 соответственно для воздействия на ОК и сравнения с уровнями логических сигналов О и 1 с выходов ОК индивидуально в каждом канале, или в группах каналов, или во всех каналах, чем обеспечивается проверка ОК с элементами любых серий (ТТЛ, ЭСЛ, КМОП и др.) и в любых их сочетаниях, обеспечивает проверку в любом канале устройства значения выходных уровней логических сигналов ОК в статическом режиме на любом тестовом наборе путем изменения значения входного логического уровня в канале до появления в этом канале несравнения (или сравнения) реакции ОК данного канала с значением эталонного разряда тестового воздействия.

Таким образом функциональные возможности устройства значительно расширены.

Формула изобретения 1. Устройство для тестового контроля логических узлов, содержащее блок задания тестов и обработки реакции, блок сопряжения, дешифратор адреса, блок синхронизации, блок памяти команд, регистр кода задержки, регистр управления режимами, группа входов-выходов блока задания тестов и обработки реакции соединена с первой группой входов-выходов блока сопряжения, вторая группа входов-выходов которого соединена с первой группой входов-выходов блока памяти команд и группой информационных входов регистра управления режимами, первая группа выходов и первый выход блока сопряжения соединены с информационным входом и входом управления дешифратора адреса, выход которого соединен с входом разрешения блока памяти команд и с управляющим входом регистра управления режимами, первый выход блока памяти команд соединен с информационным входом регистра кода задержки, отличающееся тем, что, с целью расширения номенклатуры контролируемых узлов путем организации до- полнительных режимов контроля, в устройство введены регистр пуска, регистр состояния, блок коммутации, группа компараторов и входной буфер кодовых пачек, причем вторая группа входов-выходов блока сопряжения соединена с первой группой входов-выходов блока коммутации, с первыми группами информационных входов группы компараторов, с группой информационных входов регистра пуска и с группой выходов регистра состояния, первая группа выходов блока сопряжения соединена с вторыми группами информационных входов компараторов, второй выход

блика сопряжения соединен с первым режимным входом блока синхронизации, входами сброса блока памяти команд, регистра кода задержки, входом разрешения блока коммутации и входами сброса группы компараторов, выход дешифратора адреса сое- ди 1ен с управляющими входами регистра пуска, регистра состояния, блока коммутации и группы компараторов, первый выход блока синхронизации соединен с входом синхронизации блока памяти команд, регистра кода задержки, блока коммутации и группы компараторов, второй выход блока синхронизации соединен с входами синхронизации регистра состояния, выход регистра кода задержки соединен с вторым режимным входом блока синхронизации, выход регистра управления режимами соединен соответственно с третьим режимным входом блока синхронизации и управляющим входом блока памяти команд, выход регистра пучка соединен с входом разрешения блока сопряжения и с четвертым режимным входом блока синхронизации, второй выход блока памяти команд соединен с первым информационным входом блока коммутации, пятый выход блока памяти команд соединен с пятым режимным входом блока синхронизации и информационным входом регистра состояния, четвертый выход блока памяти команд соединен с вторым информационным входом блока коммутации, первый выход которого соединен с шестым режимным входом блока синхронизации, второй,третий и четвертый выходы блока коммутации соединены соответственно с треггьим, четвертым информационными входами и входом разрешения компараторов, входного буфера кодовых пачек соединен с третьим информационным входом блока коммутации, первые и вторые выходы KONпараторов группы соединены с четвертым информационным входом блока коммутации и седьмым режимным входом блока синхронизации, а также с пятым информационным входом блока коммутации, входы-выходы компараторов являются вхо- даг и-выходами устройства для подключения к входам-выходам контролируемого логического блока.

2. Устройство по п. 1, о т л ичающе- е с|я тем, что блок сопряжения содержит бло согласующих делителей, два шинных формирователя, дешифратор адреса, блок инвертора, регистр адреса, два элемента ИЛ1-НЕ, два элемента НЕ. элемент задержки, элемент ИЛИ. элемент И-НЕ, элемент И, причем первая группа входов блока соединена с входами-выходами блока согласующих делителей, первая группа входов-выходов которого через первый шинный формирователь соединена с второй группой входов-выходов блока, с информационными входами дешифратора адреса и первой группой информационных входов регистра адреса, выход которого образует первую группу выходов блока и через первый элемент ИЛИ-НЕ и первый элемент НЕ соединен с первым входом элемента И и элемента И-НЕ, выходы которых соединены с входом блока согласующих делителей и управляющим входом первого шинного формирователя соответственно, инверсные выходы дешифратора адреса через блок инверторов соединены с второй группой информационных входов регистра адреса, синхровход которого соединен через элемент задержки с первым выходом второго шинного формирователя и инверсным входом сброса регистра адреса, второй выход второго шинного формирователя через второй элемент задержки соединен с инверсным управляющим входом дешифратора адреса, вторая группа выходов блока согласующих делмтелей соединена с группой инверсных входов второго шинного формирователя, третий выход которого соединен с первыми входами элемента ИЛИ и первым разрядом первого выхода блока, второй разряд которого соединен с четвертым выходом второго шинного формирователя, вторыми входами элемента ИЛИ и элемента И, пятый выход второго шинного формирователя соединен с первым входом элемента ИЛИ-НЕ, второй вход и выход которого соединены с входом пуска блока и вторым выходом блока соответственно.

3. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что каждый компаратор группы содержит регистр, оперативное запоминающее устройство, узел потенциального согласования, цифроаналоговый преобразователь, элемент задержки и драйвер, причем третий информационный вход компаратора через элемент задержки соединен с входом чтения оперативного запоминающего устройства, выходы которого через узел потенциального согласования соединены с информационными входами цифроаналогового преобразователя, выходы которого соединены с первым информа- ционным входом драйвера, второй информационный вход которого соединен с входом-выходом компаратора, четвертый информационный вход которого соединен с входом разрешения чтения оперативного запоминающего устройства и входом управления драйвера, синхровход которого соединен с синхровходом компаратора, вход сброса которого соединен с инверсным входом сброса регистра, инверсный вход которого соединен с входом разрешения записи оперативного запоминающего устройства, вход записи которого и вход синхронизации регистра образуют управляющий вход компаратора, второй информационный вход которого образован информационными входами регистра и оперативного запоминающего устройства, адресные входы которого соединены с первым информационным входом компаратора, управляющие входы цифроаналогового преобразователя образуют вход разрешения компаратора, первый и второй выходы драйвера соединены с первым и вторым выходами компараторов,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

Изобретение относится к области вычислительной цифровой техники и может быть использовано для контроля функционирования цифровых узлов и блоков с проверкой их работоспособности при оптимальных (граничных) значениях входных уровней воздействующих сигналов и проверкой оптимальных (граничных) значений уровней выходных сигналов, Целью изобретения является расширение номенклатуры контролируемых узлов и блоков и расширение функциональных возможностей устройства. Обеспечивается проверка ОК с элементами любых серий (ТТЛ, ЭСЛ, КМОП и др.) и в любых их сочетаниях, а также обеспечивается проверка в любом канале устройства выходных уровней логических сигналов ОЕ в статическом режиме на любом тестовом наборе путем изменения входного логического уровня в канале до появления в этом канале несравнения (или сравнения) реакции ОК данного канала с значением эталонного разряда тестового воздействия. 2 з.п. ф-лы, 10 ил., 3 табл. СО с

Примечание. К,М - целые положительные числа

Таблица 2

J.

Последовательность выборки адресов ОЗУ 52, или задание количества циклов

0000 0010

0101

1001 1010

1100 1110

Переход к нулевому адресу

Безусловный переход к адресу, заданному в разрядах К...04

Условный переход к i-тону адресу, заданному в разрядах К...04, с запоминанием следующего адреса в формирователе 51 (адреса возврата), к которому необходимо возвратиться при выполнении условного возврата (обращение к подпрограмме)

Заданное число раз возврата к адресу, указанному в разрядах (.. .04 - число повторений (циклов) выбранного участка программы

Условный возврат к адресу, записанному и хранящимся в формирователе 51 при условном переходе (возврат из подпрограммы)

Запись в формирователь 51 количества возвратов (количество циклов), указанных в разрядах К...0 +

Формирование следующего адреса

Примечание: 1

Количество циклов выбранного участка программы задается уменьшенным на 1. Однократное программируемое число циклов не более 401)4 (при кодировании числа 4095).

Глубина вложений одной подпрограммы з другую не более 4-х (всего вложений не более 5).

.52

cpue.1

Таблица 3

ffrZ ff/7

0r8

r5

ffr5

ffr/C

ffrif

(pt/e.2

&

31

ffff

cpЈ/e.3

I62Z.C81

,

- I I -I- H ...

M I ищ I

:щ

-W-f-fwo

,/.вгЈШ

ОтЮ Г

TBi

s

cdlp

W

ОглЗ От 1 UJA

Om10j ui

г.иг

1Г,

КОК

к4,Ю

Фиг.7

9or. &

j -jiiimmniL

ГИГ «а

faM к ЛЛ ЛЯП П П П П П ПШПЛЛЛЛШШЛ № а

Аи 7/ТПЛЛЛЛ ПППППППП ПЛПП.ПЛ

Фиг. JO

| Устройство для контроля и диагностики логических блоков | 1985 |

|

SU1302284A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

Авторы

Даты

1993-08-30—Публикация

1991-06-13—Подача