Изобретение относится к цифроанаяоговой вычислительной технике и может быть использовано в цифровых системах управления, измерения и контроля.

Известен экстраполирующий преобразователь (ЭП) кода в аналоговый сигнал, содержащий источник опорного напряжения, дешифратор, два сумматора, три функциональных и два линейных преобразователя кода в напряжение СО

Недостаток указанного ЭП - сложность функциональной схемы.

Известен также экстраполирующий преобразователь кода.а аналоговый сигнал, содержащий первый и второй преобразователи «ода в напряжение (ток), первые входы которых подключены соответственно к первой и второй шинам входного кода, первый и второй суммато|%1, элемент задержки, вход которого соединен с шиной тактовых импульсов, а выход - с вторыми входами прес радоват еЙ кода в напряжение (ток), аналоговый ключ, вход которого соединен с о&цей шиной, и интегратор, вход которого подклк чен -к выходу первого сумматора, Шйход к входу аналогового ключа и к первому входу ВТОРОГО сумматора второй вход которого соединен с выходом nejpBoro преобразоватеяя кор в напряжение (ток) -и первым входом первого cywiaтора, второй &ХОД кото|Х)го подключен к выходу второго преобраэО&ателя кода в напряжение (ток} 2.

Недостатком известного устройства является его ограниченные функциональные возможности, связанные с отсутствием варьируемьрс параметров, вследствие чего при заданной входной

последовательности х( , con; частота и др.) форма выходного сигнала ЗЛ U(t) строго фиксирована и не может меняться в процессе эксплуатации.

Цель изобретения - расширение функциональных возможностей устройства.

Поставленная 14ель достигается тем, что в экстраполирующий преобразователь кода в аналоговый сигнал, содержащий первый и второй преобразователи кода внапряжение (ток), первые входы которых подключены соответственно к Первой и второй шинам входного кода, первый и второй сумматоры, элемент задержки, вход которого

соединен с шиной тактовых импульсов, а выход.- с ВТОРЫМИ входами преобразователей кода в напряжение (ток), аналоговый ключ, выход которого соединен с общей шиной, и интегратор вход которого подключен к выходу первого сумматора, выход - к входу аналогового ключа и к первому входу второго сумматора, второй вход которого соединен с Выходом первого преобразователя кода в напряжение (ток) и первым входом первого сумматора, второй вход которого подключен к выходу второго преобразователя кода

5 в напряжение (ток), введены три элемента ИЛИ и временной распределитель, первый вход которого соединен с выходом элемента задержки, второй вход подключен к шине тактовых импульсов,

0 третьи входы - к шинам регулировки, выходы - к первым входам соотаетствуюи их элементов ИЛИ, вторые входы которых соединеных с шиной тактовых импульсов, при этом выходы первого

5 и второго элементов ИЛИ подключены к третьим входам соответствующих преобразователей кода в напряжение (ток), а выход третьего элемента ИЛИ соединен с управляющим входом анало0 ГОвого ключа.

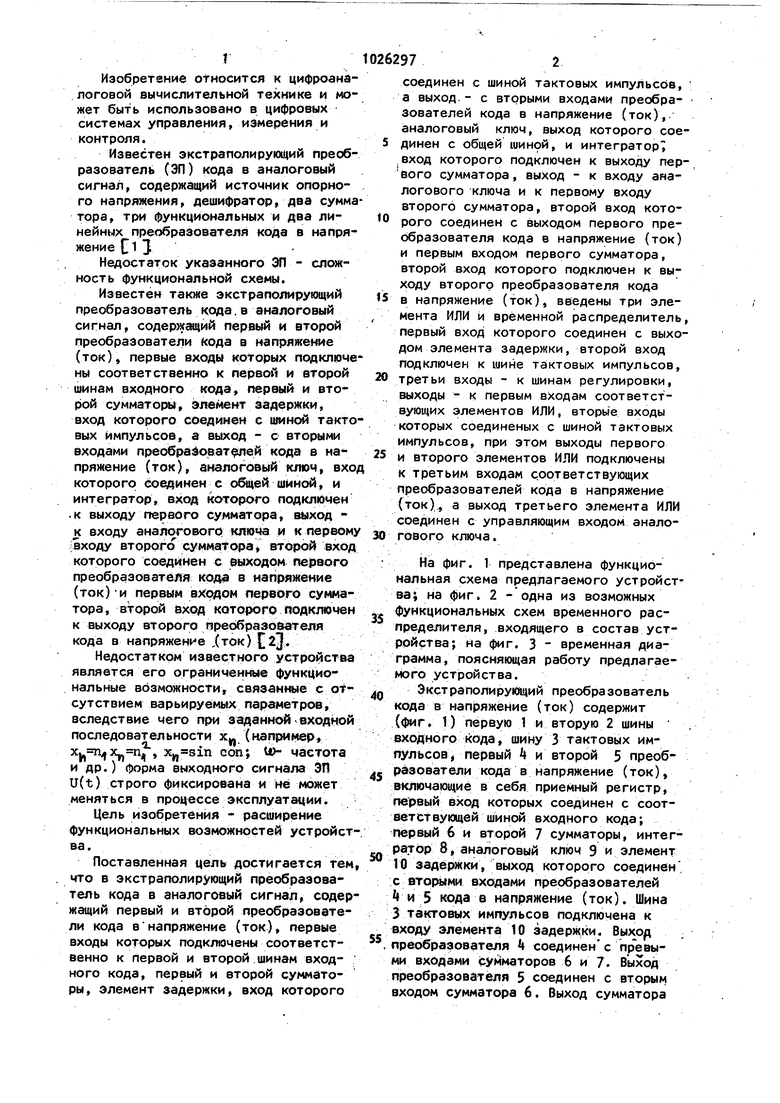

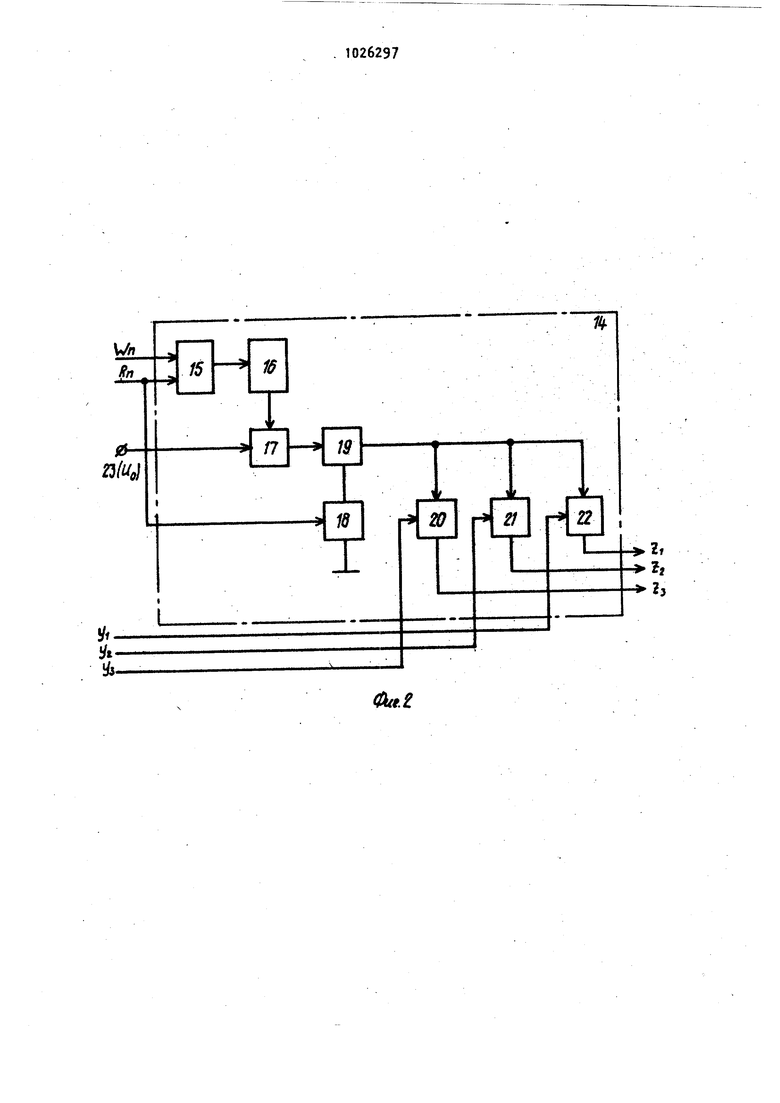

: На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - одна из возможных

. функциональных схем временного распределителя, входящего в состав устройства; на фиг. 3 - временная диаграмма , поясняющая работу предлагаемого устройства.

д Экстраполирущий преобразователь кода в нап)эяжёние (ток) содержит (Г. 1) первую 1 и вторую 2 шины входного кода, шину 3 тактовых импульсов, первый 4 и второй 5 преоб, разователи кода в напряжение (ток), включаюи иё в себя приемный регистр, первый вход которых соединен с соответствующей шиной входного кода; Первый 6 и второй 7 сумматоры, интегратор 8, аналоговый ключ 9 и элемент 10 задержки, выход которого соединен , с вторыми входами преобразователей и и 5 кода в напряжение (ток). Шина

3 тактовых импульсов подключена к входу элемента 10 задержки. ;

. преобразователя k соединенс превыми входами cyfiMaTopoB 6 и 7. Выход преобразователя 5 соединен с вторым входом сумматора 6. Выход сумматора

7 является выходом экстраполирующего преобразователя. Выход сумматора 6 соединен с входом интегратора 8, выход которого подключен к второму входу сумматора 7 и к сигнальному входу аналогового ключа 9. Выход ключа 9 подключен к шине нулевого потенциала .

Кроме того, экстраполирующий преобразователь снабжен первым 11, вторым 12 и третьим 13 элементами ИЛИ и временным распределителем 1k, Временной распределитель Т имеет пять входов и три выхода. Первый его вход (вход запуска) связан с выходом элемента ТО задержки (сигнал W); второй вход (вход возврата в исходное положение) соединен с шиной 3 тактовых импульсов; три остальные входа являются настроечными и подключены к шинам настройки у , у, и у. Выход первого элемента ИЛИ 11 подключен к третьему входу преобразователя 4, выход второго элемента ИЛИ 12 - к третьему входу преобразователя 5 выход третьего элемента ИЛИ 13 - к управляющему входу аналогового клю.ча 9- Первые входы элементов ИЛИ 1113 связаны с соответствующими выход.ными шинами временного распределителя k, а вторые входы - с шиной 3 тактовых импульсов. В процессе работы, состоящем из отдельных циклов экстраполяции, в|земеннс)й распределитель 1 вырабатывает на своих выходных шинах сигналы Z в моменты времени tJ , где , , 2i,3. Величина интервалов времени tr мож.ет регулироваться независимо от длительности двугих интервалов при помощи соответствующих сигналов настройки у .

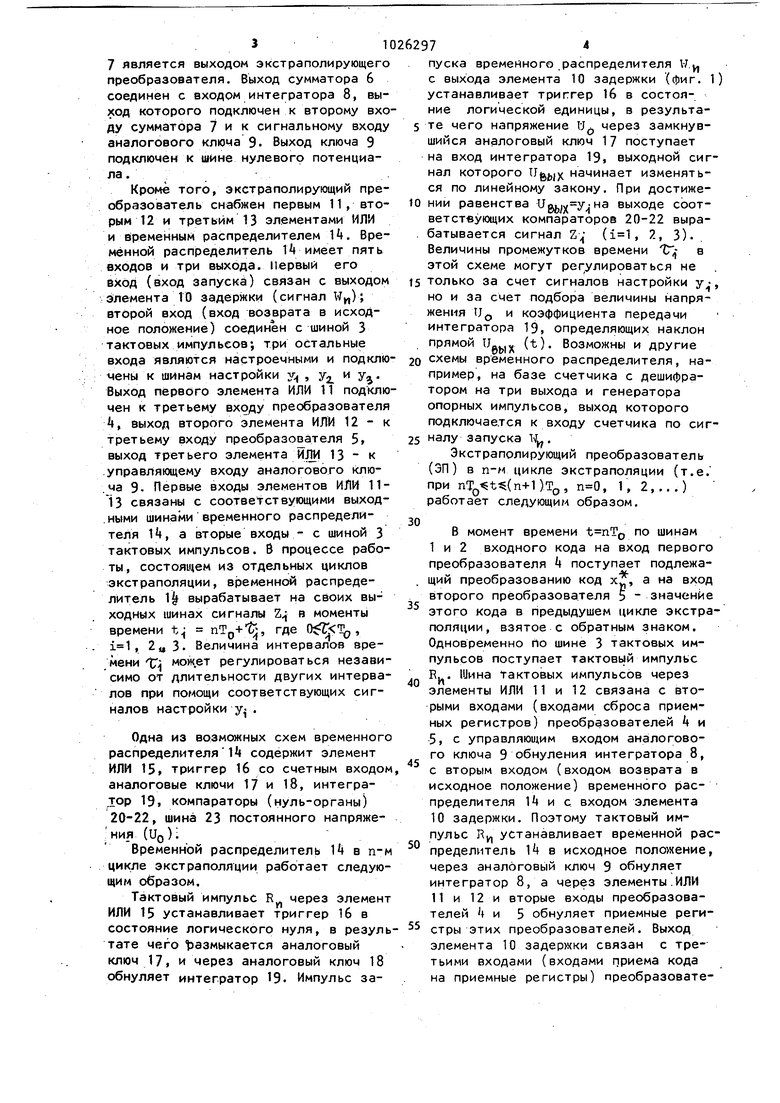

Одна из возможных схем временного распределителяИ содержит элемент ИЛИ 15 триггер 16 со счетным входом аналоговые ключи 17 и 18, интегратор 19, компараторы (нуль-органы) 20-22, шина 23 постоянного напряжения (Uo)i

Временной распределитель 14 в п-м цикле экстраполяции работает следующим образом.

Тактовый импульс R через элемент ИЛИ 15 устанавливает триггер 16 в состояние логического нуля, в результате чего размыкается аналоговый ключ 17, и через аналоговый ключ 18 обнуляет интегратор 19. Импульс запуска временного .распределителя VJ.y, с выхода элемента 10 задержки (фиг. 1) устанавливает триггер 16 в состояние логической единицы, в результате чего напряжение U через замкнувшийся аналоговый ключ 17 поступает на вход интегратора 19, выходной сигнал которого ,jj( начинает изменяться по линейному закону. При достиже0 НИИ равенства ( выходе соответствующих компараторов 20-22 выра. батывается сигнал Z- (, 2, 3). . Величины промежутков времени в этой схеме могут регулироваться не

5 только за счет сигналов настройки у-, но и за счет подбора величины напряжения UQ и коэффициента передачи интегратора 19, определяющих наклон прямой Ug,5 (t). Возможны и другие

0 схемы временного распределителя, например, на базе счетчика с дешифратором на три выхода и генератора опорных импульсов, выход которого подключается к входу счетчика по сигналу запуска W.

Экстраполирующий преобразователь (ЗП) в п-н цикле экстраполяции (т.е. при nTQ«t(n+1)To, , 1,2,...) работает следующим образом.

0

В момент времени (j по шинам

Iи 2 входного кода на вход первого преобразователя t поступает подлежа. щий преобразованию код х, а на вход второго преобразователя 5 - значение

5 этого кода в предыдушем цикле экстраполяции, взятое с обратным знаком. Одновременно rto шине 3 тактовых импульсов поступает тактовь1й импульс R.. Шина Тактовых импульсов через элементы ИЛИ 11 и 12 связана с вторыми входами (входами сброса приемных регистров) преобразователей t и 5, с управляющим входом аналогового ключа 9 обнуления интегратора 8,

5 с вторым входом (входом возврата в исходное положение) временного распределителя И и с входом элемента 10 задержки. Поэтому тактовый импульс Ки устанавливает временной расO

пределитель 1ч в исходное положение, через аналОговь1й ключ 9 обнуляет интегратор 8, а через элементы.ИЛИ

IIи 12 и вторые входы преобразователей и 5 обнуляет приемные регистры этих преобразователей. Выход элемента 10 задержки связан с третьими входами (входами приема кода на приемные регистры) преобразователей 4 и 5 и первым входом (входом запуска) временного распределителя И. Поэтому через небольшой промежуток времени, определяемый элементом 10 задержки и необходимый для затуха ния переходных процессов обнуления приемных регистров преобразователей А и 5, интегратора 8 и возврата временного распределителя 14 в исходное полон &ние, задержанный тактовый имзапускает временной распрепульс W 14 и осуществляет прием делитель кодов X и Xj с шин 1 и 2 входных соответственно на привходного кода емные регистры преобразователей 4 и 5, Q результате чего (после затухания соответствующих переходных процессов) на выходах преобразователей k и 5 формируются постоянные (в пределах каждого цикла экстраполяции) аналоговые сигналы U (через хи обозначен десятич ный эквивалент кода ). Временной распределитель 14 вырабатывает на своих выходных шинах сиг налы Z в моменты времени t nT+t (, 2, 3)j где каждый из промежутков времени 1Г: может регулироваться в пределах от О до Т( при помощи подаваемого извне настроечного сигнала у- временного распределителя 14. В простейшем случае настроечные сигналы устанавливаются оператором перед включением ЭП в работу, в результате чего промежутки времейиТГ i; , С- остаются постоянными в течение всей работы ЭП. Пусть t,-n nTo-bt;4;j, где Т -„минимальный из промежутков времени t.Tj ,Г,,. Тогда при nTjjSft ty -, ЭП работает следующим образом. Сигнал 11 поступает на первые входы сумматоров 6 и 7, а сигнал U/j - на второй вход сумматора 6, выходной сигнал которого kp&Xyj k() подается на вход интегратора 8, коэффициент передачи которого выбран равным I/To Выходной сигнал интегратора В (t-пТ0)/Т(5 поступает на второй вход сумматора 7, на выходе которого формируется выходной сигнал ЭП U(t)--U, + ,-hU) (i-HV/ToJ (.twv,) . И) При ,-y, выходные сигналы Z , Z;j и Й- временного распределителя через соответствующие элементы ИЛИ 7 11-13 обнуляют: в момент времени t -сигнал Ui, в момент времени t сигнал и ; в момент времени t - ci rнал и, вызывая исключение соответ ствующих членов из выходного сигнала (1) ЭП. В результате вместо формулы (1) выходной сигнал ЭП описывается выражением U()C(Tr-r,)ttXv,1(T-r,)-Ху,.и(г-Г)| 1{С-с.)5, ЪеСиТо,иТо+То 1,Ш гдеC t-nT-j - время, отсчитываемое от начала п-го цикла экстраполяции; ),еслм z-co если Z 70 так называемая единичная ступенчатая функция. Как видно, в предлагаемом ЭП выходной сигнал l(t) в отличие от прототипа зависит от трех параметров ТГ., IX, .значения которых можно варьировать при помощи сигналов настройки у , ул и у. Поэтому при заданной последовательности х форму выходного сигнала U(t) можно менять в широких пределах. Некоторые из возможных вариантов показаны на фиг. 3 для случая х| О, . Диаграмма а соответствует тому случаю, когда сигналом Z| в момент времени , обнуляется только сигнал IJ, а сигналы (в схеме на фиг. 2 этот режим е5удет обеспечен, если настроечу- и У- взять большими, ные сигналы jf) нежели максимально возможное значение выходного напряжения UaLjy интегратора 19), при этом в формуле (3) Диаграмма сГ соответствует 5% сбросу сигналом Z,- в момент + jpocy сигналом Z, в момент t + 1 только сигнала U-( в формуле {3) ). На фиг. З изображен случай сброса в момент t,, только сигнала , в формуле (З)Т ). Комбинируя эти три основных варианта, мбжно конструировать выходные сигналы ЭП самой разнообразной формы. В качестве примера на иг. 3 t показан случай 0 1 Г2; Ц Tj,; а на фиг. 3 д- случай Т кГ гТ Технический эффект от использования предлагаемого устройства по сравению с известным заключается в расширении функциональных возможностей ЭП за счет изменения в широких пределах формы ВЫХОДНОГОсигнала ЭП в процессе эксплуатации. этом сигналы настройки ЭП j , у и у, определяющие форму его выходного сигнала, могут меняться как вручную (например, перед включением ЭП в работу), так и автоматически .(например, от устройства самонастройки), что придает ЭП свойства адаптации. Указанное йзменение формы выходного сигнала полезно в цифровых системах управления « и контроля, позволяя значительно упростить цифровую часть системы.

Так, применение ЭП с формой выходного сигнала, показанной на фиг в цифровом контуре угловой стабилизации самолета, позволяет получить выигрыш в оборудовании на с со.ответствуюцим снижением массы, габаритов и стоимости.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный экстраполятор | 1981 |

|

SU1023349A1 |

| Телеизмерительная система | 1982 |

|

SU1099322A1 |

| Преобразователь кода в импульсы ступенчатой формы | 1981 |

|

SU974569A1 |

| Устройство для формирования окружностей | 1981 |

|

SU1005172A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU892703A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Линейный экстрополятор | 1987 |

|

SU1571625A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Линейный интерполятор | 1979 |

|

SU842914A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1562972A1 |

ГЗь

f.e

а О,

/ «

- fj

9

-1

&

9

М

jL-, I V

«

Авторы

Даты

1983-06-30—Публикация

1981-07-07—Подача