Изобретение относится к цифро-аналоговой вычислительной технике и может быть использовано в цифровых системах управления, измерения и контроля {различного назначения.

Известен преобразователь кода в импульсы сложной , содержащий преобразователь кода в напряжение, вход которого соединен с шиной входного кода, а выход - с сигнальными входами основного блока аналоговых ключей, выходы которых через резисторную матрицу подключены к выходной шине устройства.

Недостатком этого устройства является то, что для получения выходных импульсов сложной формы требуется сложная схема управления. Причем во многих радиоэлектронных системах управления возникает задача преобразования кода в амплитудно-модулированный импульс сложной формы в соответ ствии с уравнением

;U(.t;--KoX,,6Ct-nTo), иТо(и)То, C-l)

:где 5Ct) функция, опис,ывающая фор. му выходных импульсов/

у У) - входной код (и о, 1,2. i .) ;

KO - коэффициент пропорциональности ,

Тд время нахождения входного с . кода на приемном регистре.

Так, в цифровых системах управления часто требуется преобразование кода в импульс ступенчатой формл

10 S(t)--ci АЛ t,.,-, ic.z,...,(j,, (i) .

где g - натуральное числом

оС - постоянные коэффициенты и

О «-toS-tA.-.-j-etcv-TO15

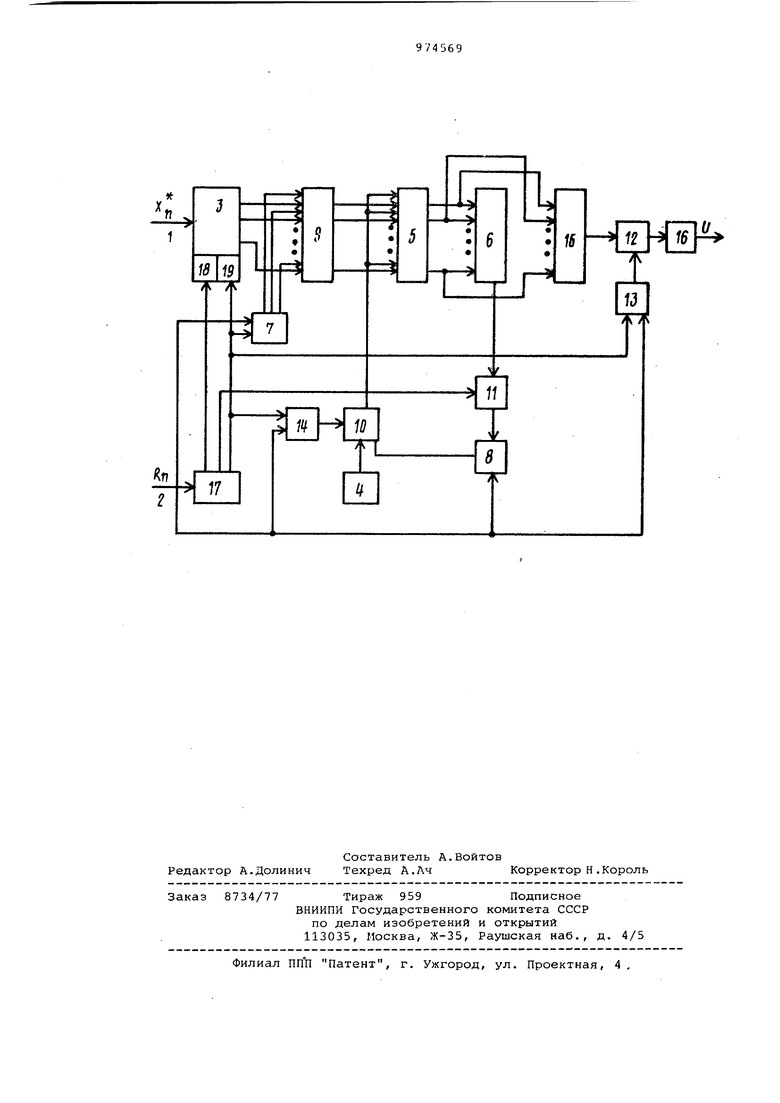

Известен также преобразователь кода в импульсы ступенчатой формы, со2Q держащий преобразователь кода в напряжение, вход которого соединен с пшной входного кода, а выход - с сигнальными входами основного блока аналоговых ключей, выходы которых через резистивную матрицу подключе25ны к выходной шине устройства, последовательно соединенные регистр, дополнительный блок ключей, счетчик, временной распределитель, регистр блокировки, элемент И и блок ключей бло30кировки, вцхо.ды которых соединены с управляющими входами основного блок аналоговых ключей, а управляющие входы - с выходом регистра блокиров ки, вход регистра блокировки .соедин сшиной кода блокировки, выход временного распределителя соединен с п вым входом элемента И, второй вход которого соединен с шиной тактовых импульсов, а третий вход - с выходом счетчика и сигнальными входами дополнительного блока ключей, выход элемента И подключен к упрс1вляющему входу счетчика, входы регистра и счетчика подключены к шине кода, управляющего длительностью импульсов Г2. Недостатком устройства является его сложность, обусловленная тем, что кроме приемного регистра, блока аналоговых ключей и резистивной матрицы, входящих в состав типового преобразователя кода в напряжение (ПКН),он дополнительно содержит еще один блок аналоговых ключей, два дополнительных блока ключей, два регистра, счетчик, трехвходовой элемент И, резистивную матрицу и генератор опорных импульсов. Кроме того вследствие использования для формирования коэффициентов резистивной матрицы все коэффициентной; оказываются одного знака, не превосходя единицы по модулю и величина их зависит от сопротивления нагрузки. В результате точность преобразователя оказывается невысокой (особенно при переменной нагрузке), а класс воспроизводимых выходных импульсов ограничен однополярными импульсами. Цель изобретения - повышение точности и упрощение преобразователя. Поставленная цель достигается тем что в преобразователь кода в импульсы ступенчатой формы, содержащи входную шину, тактовую шину, приемный регистр, первый вход которого подключен к входной шине, источник эталонного напряжения, блок аналоговых ключей, резистивную матрицу, раз рядные входы которой соединены с соответствующими выходами блока аналоговых ключей, и временной распределитель, дополнительно введены аналоговая запоминающая ячейка, блок элементов ИЛИ, аналоговый переключатель, первый и второй аналоговые ключи, первый и второй дополнительные элементы ИЛИ, блок умножения на постоянные коэффициенты, выходной усилитель и блок местного управления при этом выходы приемного регистра подключены к первым входам блока эле ментов ИЛИ, вторые входы которого соединены с соответствующими выходам временного распределителя, а выходы с управляющими входами блока аналоговых ключей, выходы которого соеди нены с соответствующими входами бло ка умножения на постоянные коэффициенты, выход которого подключен к сигнальному входу второго аналогового ключа, выход которого соединен со входом выходного усилителя, сигнальные входы блока аналоговых ключей подключены к выходу аналогового переключателя, первый сигнальный вход которого соединен с выходом источника эталонного напряжения, а второй - с выходом аналоговой запоминающей ячейки, первый вход которой соединен с выходом первого аналогового Ключа, вход которого подключен к выходу резистивной матрицы, причем тактовая шина соединена со входом блока местного управления, вторым входом аналоговой запоминающей ячейки, входом установки в исходное положение временного распределителя и первыми входами первого и второго дополни:тельных элементов ИЛИ, а первый выход блока местного управления подключен ко второму входу приемного регистра, второй выход - к управляющему входу первого аналогового ключа, третий выход - к третьему входу приемного регистра, к входу запуска временного распределителя и ко вторым входам первогО и второго дополнительных элементов ИЛИ. На чертеже представлена функциональная схема предлагаемого устройства. Преобразователь кода .в импульс ступенчатой формы содержит входную шину 1, тактовую шину 2, приемный регистр 3, вход которого подключен к входной шине, источник эталонного напряжения 4, блок аналоговых ключей 5, резистивную матрицу 6, разрядные входы которой связаны с соответствующими выходами блока аналоговых ключей 5, временной распределитель 7, аналоговую запоминающую ячейку САЗЯ) 8, блок элементов ИЛИ 9, аналоговый переключатель 10, первый 11 и второй 12 аналоговые ключи, первый 13 и второй 14 дополнительные элементы ИЛИ, блок 15 умножения на постоянные коэффициенты, выходной усилитель 16 и блок местного управления С ЕМУ ; 17. Управляющие входы блока аналоговых ключей 5 подключены к соответствующим выходам приемного регистра 3 через блок элементов ИЛИ 9. Выходы блока аналоговых ключей 5 подключены к рези стивной матрице 6 и к соответствующим входам блока 15 умножения на постоянные коэффициенты of., выход которого через аналоговый ключ 12 соединен со входом выходного усилителя 16. Сигнальные входы блока аналоговых ключей 5 соединены с выходом аналогового переключателя 10, первый сигнальный вход которого связан с выходом источника эталонного напряжения 4, второй - с выходом ЛЗЯ 8. Первый вход запоминающей ячейки 8 подключен к выходу ключа 11, вход которого связан с выходо реэистивной матрицы 6. Первые входы блока элементов ИЛИ 9 связаны с выходами приемного регистра 3, а вто рые - с соответствуюцими выходами временного -распределителя 7. Тактовая шина 2 преобразователя соединена со входом ЕМУ 17, вторым входом (вхо дом сброса) АЗЯ 8, входом установки в исходное положение временного рас пределителя 7 и первыми входами первого 13 и второго 14 дополнитель ных элементов ИЛИ. Первый выход ВМУ 17 подключен ко входу приема 18 кода Х на приемный регистр 3, второй к управляющему входу аналогового ключа 11, третий - к второму входу первого 13 и второго 14 дополнитель ных элементов ИЛИ, к основному вход (входу запуска) временного распределителя 7 и ко входу сброса 19 при емного регистра 3. Число двухвходовых элементов ИЛИ в блоке 9 равно числу аналоговых ключей в блоке 5, числу устройств умножения на постоянные коэффициенты в блоке 15 и сов падает с разрядностью m числовой час ти преобразуемого кода х Рассмотрим работу предлагаемого преобразователя в ц-м цикле преобразования, т.е. при и TO 5-t (-( )TO. Каждый цикл начинается с прихода очередного тактового импульса R на шину 2 и входного кода на входную шину 1. Тактовый импульс сбрасывает в ноль ЛЗЯ 8, возвращает в исходное положение временной распределитель 7 через первый 13 и второй 14 дополнительные элементы ИЛИ, подключает к выходу аналогового переключателя 10 источник эта лонного напряжения 4 и размыкает ана логовый ключ 12, а также запускает БМУ 17 (который может быть выполнен например, в виде последовательно включенных D -триггеров, на сдвигаю 1дем регистре, линии задержки с отводами и др.ХИНУ 17 формирует на своих трех выходных шинах последовательност сдвинутых во времени импульсов. Импульс на первом выходе БМУ 17 формируется через промежуток времени, дос таточный для затухания переходных процессов сброса в АЗЯ 8 и поступает на вход 18 регистра 3. Этот импульс осуществляет прием входного ко да X;Jj на приемный регистр 3. Так ка сигналы на выходных шинах временного распределителя 7 в это время отсутствуют, то сигналы с выхода регистра 3 через блоки 9 и 5 поступают на вход резистивной матрицы 6, осу,ществляя преобразование входного кода Х в пропорциональное ему напря жение (или ток). После затухания пе реходних процессов в преобразователе сигнал на втором выходе БМУ 17 открывает первый аналоговый ключ 11 на время, необходимое для запоминания результата преобразования коданалог в АЗЯ 8, после чего сигнал с третьего выхода БМУ 17 через вход 19 сбрасывает в ноль приемный регистр 3 через дополнительные элементы ИЛИ 13 и 14, подключает к выходу аналогового переключателя 10 АЗЯ 8 и замыкает второй аналоговый ключ 12, а также запускает временной распределитель 7. Временной распределитель 7 в моменты времени -fcr-ti формирует на своих Во ходных шинах серию импульсов ПОСТОЯННО амплитуды .с длительностями --t ---ti, i 1, 2,.... , g , обеспечивающих очередное последовательное во времени открывание ключей блока 5 на промежутки времени номер ключа), в результате чего выходной сигнал АЗЯ 8 в блоке 15 последовательно во времени умножается на постоянные коэффициентыс, . Таким образом, на выходе усилителя 16 получается импульс ступенчатой формы, описываемый выражениями( иС2), параметры которого . и Т можно менять в широких пределах за счет настройки блоков 15 и 7. Временной распределитель 7 может быть выполнен, например, в виде интегратора, на вход которого по сигналу с БМУ 17 подключается постоянный сигнал, а выход через нуль-органы (компараторы) подключен к выходным шинам распределителя 7. Меняя постоянный входной сигнал и пороговые сигналы компараторов, можно в широких пределах менять промежутки времени ТГ,- . Таким образом, предлагаемый преобразователь кода в импульсы ступенчат той формы обладает более простой схемой, по сравнению с известными более высокой точностью и более широкими функциональными возможностями. Количество оборудования зависит от |разрядности преобразуемого кода. Гак, для десятиразрядного преобразователя, построенного на интегральных схемах общего применения, выигрыш в числе корпусов интегральных схем по сравнению с прототипом составляет 10-15%. Введение блока элементов ИЛИ 9, аналогового переключателя 10, аналогового ключа 11 и АЗЯ 8 позволяет использовать один и тот же блок аналоговых ключей 5 как для коммутации элементов резистивной матрицы 6, так и для коммутации элементов блока 15 устройств умножения на постоянные коэффициенты, и в два раза сократить число аналоговых ключей в преобразователе . Применение блока 15 умножения на постоянные коэффициенты (выполненного

например, иа операционных усилителях вместо дополнительной резистивной матрицы прототипа позволяет реализовать коэффициенты любого знака и любой (в пределах технической возможности; величины. Использование выходного усилителя 16 позволяет исключить зависимости точности преобразователя от сопротивления нагрузки.

Формула изобретения

Преобразователь кода в импульсы ступенчатой формы, содержасций входную шину, тактовую шину, приемный регистр, первый вход которого подключен к входной шине, источник эталонного напряжения, блок аналоговых ключей, резистивную матрицу, разрядные входы которой соединены с .соответствующими выходами блока аналоговых ключей, и временной распределитель , отличающийся тем, что, с целью повышения точности и упрощения преобразования, .в него введены аналоговая запоминающая ячейка, блок элементов ИЛИ, аналоговый переключатель, первый и второй аналоговые ключи, первый и второй дополнительные элементы ИЛИ, блок умножения на постоянные коэффициенты, выходной усилитель и блок местного управления, при этом выходы приемного регистра подключены к первым входам блока элементов ИЛИ, вторые входы которого сое.динены с соответствующими выходами временного распределителя, а выхо.ды - с управляющими входами блока аналоговых ключей, выходы которого

соединены с соответствующими входами блока умножения на постоянные коэффициенты, выход которого подключен к сигнальному входу второго аналогового ключа, выход которого соединей со входом выходного усилителя, сигнальные входы блока аналоговых ключей подключены к выходу аналогового переключателя, первый сигнальный вход которого соединен с выходом источника эталонного напряжения, а второй - с выходом аналоговой запоминающей ячейки, первый вход которой соединен с выходом первого аналогового ключа, вход которого подключен к выходу резистивной матрицы, причем тактовая шина соеди.нена со входом блока местного управления вторым входом аналоговой запоминающей ячейки, входом установки в исходное положение временного распределителя и первыми входс1ми первого и второго дополнительных элементов ИЛИ, а первый выход блока местного управления подключен

5 ко второму входу приемного регистра, второй выход - к управляющему входу первого аналогового ключа,третий выход - к третьему входу приемного регистра, к входу запуска временного распределителя и ко вторым вхйдам первого и второго дополнительных элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе 35 1. Клебанский Р.Б. Преобразователи кода в напряжение. М., Энергия, 1973, с.18-19.

2. Авторское свидетельство СССР № 617831, кл. Н 03 К 13/02, 15.11.76 40 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода в импульсы сложной формы | 1976 |

|

SU617831A1 |

| Экстраполирующий преобразователь кода в аналоговый сигнал | 1981 |

|

SU1026297A1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

| СИСТЕМА ТЕЛЕВИДЕНИЯ | 2007 |

|

RU2339183C1 |

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2326508C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2007 |

|

RU2356179C1 |

| СИСТЕМА ЦИФРОВОГО ЦВЕТНОГО ТЕЛЕВИДЕНИЯ | 1993 |

|

RU2103839C1 |

| СИСТЕМА РАДИОВЕЩАНИЯ | 2011 |

|

RU2479926C1 |

Авторы

Даты

1982-11-15—Публикация

1981-03-24—Подача