(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗАПОМИНАЮЩИХ 1 Изобретение относится к запоминаю щим устройствам. Известно устройство для контроля ферритовых запоминсшяцих матриц, содержащее блок управления, регистр адреса, дешифратор адреса, блок генераторов импульсов тока, блок контроля, блок считывания, блоки коммута торов, схему блокировки, счетчиК|Дешифрйторн tl . Недостаток зтого устройства состо ит в том, что в нем невозможно опера тивнЬ осуществлять проверку амплитуды импульсов генераторов импульсов тока и настройку порогов дискриминации блока считывания, что снижает точность и достоверность контроля запоминакщих матриц. Наиболее близким техническим реше нием к изобретению является устройст во для,контроля запоминающих матриц, которое содержит блок управления, ре гистры адреса, дешифраторы, усилители считывания, блок;сравнения, многокаскадные генераторы токов, коммутаторы, блок выполнения диагностических тестов, шаблон для контролируемой ферритовой матрицы, блок задания и анализа режимов, блок регист рации результатов к.онтроля, регистри МАТРИЦ рунвдий прибор. Это устройство позволяет контролировать ферритовые запоминающие матрицы с определением полной или частичной области хранения информации ОХИ) с ручной или автоматической регистрацией результатов контроля. Предельные значения амплитуд импульсов токов при определении ОХИ устанавливаются оператором вручную с панели управления. ОХИ определяется путем перебора комбинаций адресного и разрядного токов, значения которых скачкообразно автоматически изменяются в диапазоне предельных значений 2. Однако в этом устройстве невозможно проверить взаимное расположение координатных обмоток и обмотки записи-считывания, нарушение во взаимном расположении которых ведет к ложной работе контролируемой матрицы. Кроме того, в данном устройстве невозможно проверить нарушение в подключении соседних координатных обмоток, что также ведет к ложной работе контролируемой матрицы. Устройство не обеспечивает при ручном контроле достаточную точность установки амплитуды импульсов токов

и точность установки напряжения порога дискриминации, а также оперативный контроль амплитуды импульсов токов в выходных цепях устройства и напряжения порогов дискриминации блока усилителя считывания, что снижает достоверность проверки контролируемой матрицы и не обеспечивает высокую производительность устройства.

Цель изобретения - повышение быстродействия устройства, точности и достоверности .контроля.

Поставленная цель достигается тем что в устройство для контроля запоминающих матриц, содержащее регистры адреса, дешифраторы адреса, коммутаторы, усилитель считывания, схему сравнения , генераторы тока и блок управления, причем одни из выходов регистров адреса подключены ко входам дешифраторов адреса, одни из входов коммутаторов подключены к выходам дешифраторов адреса и одним из выходов генераторов тока, выходы коммутаторов подключены к первому входу усилителя считывания, первый выход которого соединен с первым входом схемы сравнения, управляющие входы регистров адреса, дешифраторов адреса, схемы сравнения, усилителя считывания, коммутаторов, генераторов тока подключены к выходам блока управления, первый выход схемы сравнения и другие выходы регистров адреса соединены с одним из входов блока управления, введен блок логического анализа и блок обнаружения ошибок в прошивке запоминающей матрицы, входы которого подключены соответственно к первому выходу усилителя считывания и второму выходу схемы сравнения, выходы - роответственно к второму входу схемы сравнения и одному из входов блока логического анализа, другие входы которого соединены со вторым выходом усилителя считывания и другими выходами генераторов тока, а выходы - со вторым входом усилителя считывания, входами генераторов тока и другим входом блока управления, одни из выходов которого соединены с управляющими входами блока обнаружения ошибок в прошивке запоминающей матрицы и блока логического анализа.

При этом блок обнаружения ошибок в проиивке запоминающей матрицы целесообразно выполнить в виде блока, содержсцдего амплитудно-временные селекторы, формирователи сигналов ошибок и элемент ИЛИ, входы которого подключены к выходам формирователей сигналов ошибок, одни из входов которых подключены к одним из выходов амплитудно-временных селекторов, другие входы которых и выход элемента ИЛИ являются выходами блока обнаружения ошибок в прошивке запоминающей матрицы, входами которого являются входы амплитудно-временных селекторов и другие входы фор миров ате лей сигналов ошибок.

Кроме того, блок логического анализа выполнен в виде блока, содержащего формирователи эталонных сигналов, схелы сравнения, формирователь калиброванных сигналов, измерительный узел, узел индикации и блок местного управления, одни из выходов и входов которого подключены соответственно к управляющим входам схем сравнения, измерительного узла и формирователя калиброванных сигналов и к одним из выходов схем сравнения, другие выходы которых и выход измерительного узла соединены со входами узла индикации, выходы формирователей эталонных сигналов подключены к одним из входов схем сравнения другие входы которых соединены соответственно с выходом измерительног узла и первым выходом формирователя калиброванных сигналов, первый вход которого соединен с выходом одного из формирователей эталонных сигналов , второй выход формирователя калиброванмых сигнсшов и другие выходы блока местного управления являются выходами блока логического анализа, входами которого являются вход измерительного узла второй и третий входы формирователя калиброванных сигналов и другой вход блока местного управления.

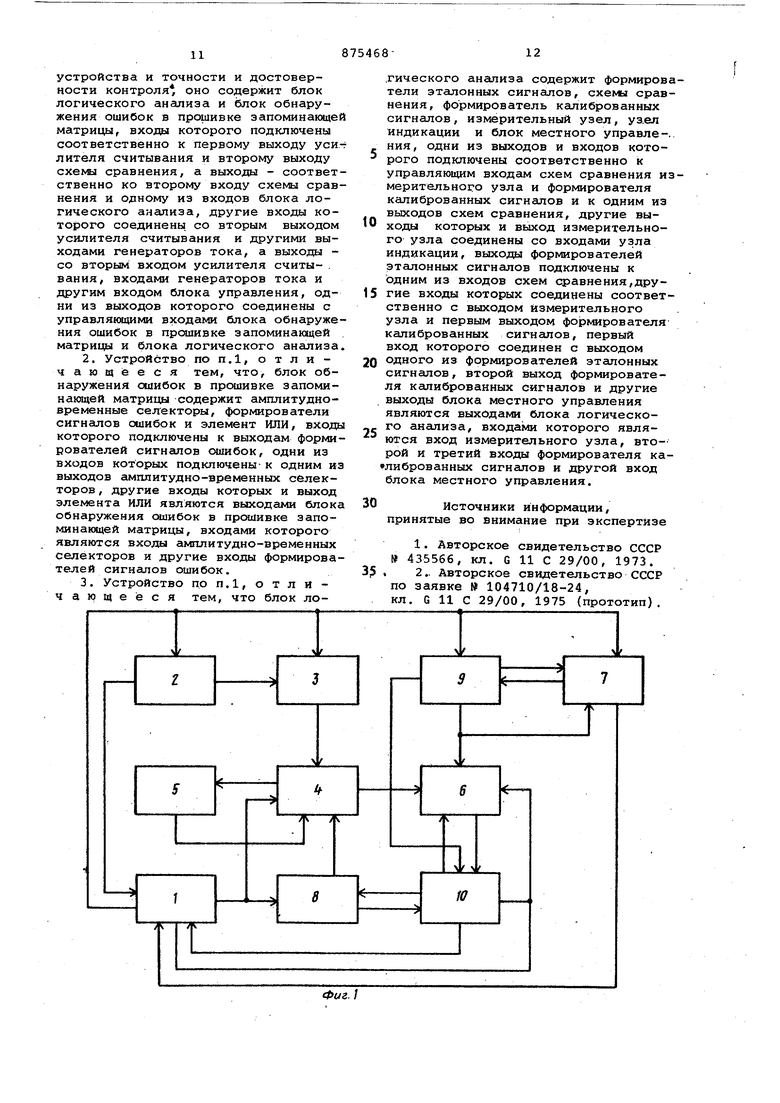

На фиг.1 изображена структурная схема устройства для контроля запоМингиощих матриц; на фиг. 2 - структурная схема блока управления; на фиг.З - то же, блок; обнаружения ошибок в прошивке запоминающей матрицы; на фиг.4 - то же, блок /югического анализа.

Устройство содержит (фиг.1) блок 1 управления, регистры 2 адреса, дешифраторы 3 адреса, коммутаторы 4, приспособление 5 для подключения проверяемой матрицы, усилитель 6 считывания , схему 7 сравнения, генераторы 8 тока, блок 9 обнаружения ошибок в прошивке запоминающей матрицы и блок 10 логического анализа.

Первый выход схемы 7 сравнения подключен к одному из входов блока 1, а первый вход - к первому выходу усилителя 6. Одни из выходов генераторов 8 соединены со входами коммутаторов 4. Входы блока 9 подключены соответственно к первому выходу усилителя б и второму выходу схемы 7 сравнения, а выходы соответственно ко второму входу схемы 7 сравнения и одному из входов блока 10, другие входы которого соединены со вторым выходом усилителя б и другими выходами генераторов 8. Первый вход усилителя 6 подключен к выходам коммутуторов 4. Выходы блока 10 соединены со вторым входом усилителя 6, входамй генераторов 8 и другим входом блока 1, одни из выходов которого соединены с управляницими входами блока 10.

Блок управления 1 (фтлг.2) содержит формирователь 11 синхросигналов коммутатор 12, схему 13 выбора теста, формирователь 14 сигналов записи , формирователь 15 тактов обращения, формирователь 16 счетных импульсов, панель 17 оператора, формирователь 18 временной диаграммы.

Формирователь 11 синхросигналов предназначен для выработки серий импульсов с частотой 26,6 МГц и 100кГц он разрешает работу и останов устройства по сигналу Ошибка.

Коммутатор 12 распределяет импульсы с частотой 100 кГц на запуск либо формирователя 18 временной диаграк1мы либо на блок 10, либо на схему 13 выбора теста в зависимости от состояний регистров 2 адреса, схемы 7 сравнения и формирователя 11 синхроимпульсов .

Схема 13 выбора теста обеспечивает выбор необходимого теста вручную или автоматическое последовательное включение очередного теста после окончания предыдущего и выдает сигнал на схему проверяемой запоминающей матрицы после окончания выполнения всех тестов по данному разряду.

Формирователь 14 сигналов записи обеспечивает автоматическое формирование кода числа (1 tvivi О) в соответствии с включенным тестом проверки и кодом евдреса ячейки памяти.

Формирователь 15 тактов обращения обеспечивает восьмикратное обращение ко всем ячейкам памяти, выдает сигнал разрешения контроля считанной информации на схему 7 сравнения, а также сигналы, разрешающие смену теста или точки проверки.

Формирователь 16 счетных импульсов предназначен для выработки счетных импульсов на регистры 2 адреса, а также формирования программа прохождения теста (100-кратная запись по Ксисдому адресу с 90-кратным контролем считанной информации). Панель 17 оператора служит для оперативного управления работой устройства и контроля состояний основных узлов и схем устройства по индикации,: формирователь 18 временной диаграммы обеспечивает формирование временного соотношения между сигналами запуска генераторов 8 тока и другими сигнсшами, определяющими такты чтения и записи.

Блок 9 (фиг.З) предназначен для автоматического определения нарушений взаимного расположения координатных обмоток и обмотки записисчитывания, проходящие через ферритовые сердечники запоминающей матрИ цы, а также проверки нарушений подключения соседних координатных обмоток на ее входных контактах. Елок 9 содержит амплитудно-временные селекторы 19 и 20J формирователи, 21 и 22 сигналов ошибок и элемент ИЛИ 23, входы которого подключены к выходам формирователей 21 и 22, одни из входов которых подключены к одним из выходов селекторов 19 и 20, дру0гие входы которых и выход элемента ИЛИ 23 являются выходами блока 9, входами которого являются входы селекторов 19 и 20 и другие входы формирователей 21 и 22,

5 Формирователи 21 и 22 формируют соответственно сигналы о нарушении взаимного расположения координатных обмоток и нарушении подключения соселщих координатных обмоток контролируемой запоминающей матрицы.

Элемент ИЛИ 23 передает сигналы Ошибка прошивки с формирователей 21 или 22 на схему 7 сравнения (для формирования сигнала остановка устройства и на индикацию характера ошибки) . Блок 10 (фиг.4) предназначен для установки необходимых значений амплитуд импульсов токов генераторов 8 и .J порогов срабатывгшия селекторов 19 и 20 в ручном режиме работы устройства и для автоматического контроля этих же параметров при автоматическом режиме работы устройства с вьща чей сигнала разрешения проверки матрицы.

: Блок 10 содержит блок 24 местного ;управления, измерительный узел 25, первую схему 26 сравнения, формирователь 27 эталонных сигналов, формирователь 28 калиброванных сигналов, вторую схему 29 сравнения, формирователь 30 эталонных сигналов, узел 31 индикации.

Одни из выходов и входов блока 24 5 подключены соответственно к управляющим входам схем 26 и 29 сравнения, узла 25 и формирователя 28 и к одним из выходов схем 26 и 29 сравнения, другие выходы которых и выход Q узла 25 соединены со входами узла 31. Выходы формирователей 27 и 30 подключены к одним из входов схем 26 и 29 сравнения, другие входы кото|РЫХ соединены соответственно с выходс 4 узла 25 и первым выходом формирователя 28, первый вход которого соединен с выходом формирователя 30. Второй выход формирователя 28 и другие выхода блока 24 являются выходами блока 10, выходами которого 0 являются вход узла 25, второй и третий входы формирователя 28 и другой вход блока 24.

Блок 24 предназначен для формирования сигналов, управляющих подклю5 .чением генераторов 8 тока с узла

25, формирователя 28 к усилителю считывания б при ручном или автоматическом режиме работы устройства, и управления работой блока 10,

Узел 25 осуществляет измерение амплитуды импульсов токов о геиераторов 8 тока и вьщачу результатов измерения на десятичную индикацию и на сравнение.

, Фоомиоователь 28 формирует импуль ы калибрационного напряжения,амплитуда которых пропорционгшьна коду, поступающему с формирователя 30, задающего код порога при ручном режи;ме работы, и монотонно увеличивающиеся импульсы калибрационного напряжения с дискретностью 0,1 мВ от О до 19,9 MB в автоматическом режиме работы устройства.

Схемы 26 и 29 сравнения выполняют сравнение ходов эталонного значения, поступающих с формирователя 27 (кодов токов) и с формирователя 30 кодов порогов) с измеренными кодами токов, поступающими с узла 25 и с измеренными кодами порога дискриминации, поступающими с формирователя 28, анализируют результаты сравнения и в автоматическом режиме работы устройства вьадают сигнал о несоответствии проверяемого параметра заданному и характер несоответствия (больше или меньше эталонного). При величине отклон.ения больше 2-х единиц младшего разряда выдают также сигнал на останов устройства.

Узел индикации 31 осуществляет десятичную индикацию амплитуды импульсов токов, индицирует результаты выполнения сравнения и проверяемой параметр.

Устройство работает следующим образом.

Перед проверкой запоминакяцей матрицы ее необходимо подключить к разъeMciM устройства посредством приспособления 5, затем вручную в блоке 10 в формирователях 27 и 30 устанавливаются значения кодов токов и кодов порогов дискриминации согласно соответствукадему документу на,проверяемую матрицу, на панели оператора 17 блока 1 управления устанавливаются соответствующий режим .работы устройства, программа контроля и производится пуск устройства. ПО сигналу пуска устройства формирователь 11 синхросигналов разрешают подачу на один из входов коммутатора 12 импульсов частотой 100 кГц. На другой вход коммутатора поступает сигнал с регистров 2 адреса,который опредляет направление передачи импульсов 100 кГц. По первому пуску эти импульсы поступают на блок 10, который формирует сигналы на поочередное подключение генераторов 8 к узлу 25 и разрешает работу схемы 26 сравнения. С формирователя 18 на генераторы 8 поступают сигналы на включение определенного генератора тока. В узле 25 происходит измерение амплитуды импульсов соответствующего генератора тока. Результат измерения в двоично-десятичном коде поступает на узел 31 индикации, где преобразуется в десятичный код и индицируется десятичное значение амплитуды импульсов тока проверяемого генератора, и на схему сравнения 26, где сравнивается с двоично-десятичным кодом, поступающим с формирователя 27. Результаты сравнения анализируются и/ в случае несоответствия амплитуды импульсов тока проверяемого генератора тока, он вьвдает сигнал блоку 1 управления на останов устройства.

В узле 31 индикации индицируется значение амплитуды импульсов тока и номер генератора тока, наличие ошибки и указание в большую или меньшую сторону необходимо изменить амплитуду импульсов тока проверяемого генератора тока.

В случае соответствия измеренной амплитуды импульсов тока заданному сз4ема 26 сравнения выдает сигнал блоку 24 на переход к проверке амплитуды импульсов тока следуквдего генератора тока, контролирует его, эьщает сигнал на переход к следующему и т.д.

После выполнения проверки амплитуды импульсов тока последнего генератора тока схема 26 сравнения выдает блоку 24 сигнал на переход к проверке порогов дискриминации селекторов 19 и 20. Елок 24 выдает сигналы формирователю 28, схеме сравнения 29, разрешает работу этих узлов, после чего начинается поочередная проверка настройки порога дискриминации всех селекторов. Формирователь 28 выдает на усилитель 6 считывания монотонно увеличивающееся импульсное калибрационное напряжение с дискретностью 0,1 мВ, где оно усиливается и поступает на выбранный селектор 19 и 20, вызывая его срабатывание при определенной амплитуде калибрационных импульсов напряжения. Сигнал срабатывания поступает в формирователь 28 и запрещает изменение амплитуды импульсов калибрационного напряжения, при этом двоично-десятичный код, соответствующий калибрационному напряжению в момент срабатывания выбранного селектора из формирователя 28, поступает в схему 29 сравнения и сравнивается с двоично-десятичным кодом, поступившим из формирователя 30.

Результат сравнения анализируется в схеме 29 сравнения и, в случае несоответствия настройки уровня порога дискриминации проверяемого селектора, выдает сигнал на останов устройства. При этом в узел 31 индикации индицируется наличие ошибки номер селектора и указание в большую или меньшую сторону необходимо изменить настройку порога дискрими нации селектора, в случае соответствия настройки схема 29 сравнения выдает сигнал блоку 24 на переход к проверке .следующего селектора и т.д После выполнения проверки настрой ки порога дискриминации последнего селектора из блока 24 выдается на блок 1 управления (на коммутатор 12) сигнал об окончании выполнения теста проверки, что свидетельствует о точной настройке генераторов тока и селекторов. Коммутатор 12 по этому сигналу разрешает подачу импульсов 100 кГц на схему 13 выбора теста и через нее на формирователь 16 счетных импульсов. В схеме 13 выбора теста происхо дит включение первого выбранного тес та согласно установленной программы проверки и подается разрешающий сигнал на формирование информации на запись в форьшрователе 14 информации на запись, т.е. вырабатываются сигнсшы запуска регистров 2 адреса,дешифраторов 3 адреса, коммутаторов 4, схемы 7 сравнения, генераторов 8 тока, после чего производится восьмикратная запись информации в проверяе мую матрицу. При восьмом обращении.к проверяемой матрице формирователь 15 тактов обращения ввдхает сигнал, разрешающий контроль считанной информации в схеме 7 сравнения, который сравнивает информацию, записывае мую в каждую ячейку памяти запоминги щей матрицы со считанной из этих же ячеек памяти и усиленной в усилителе б считывания и, в случае несоотв.етст ВИЯ, выдает сигнал в блок 1 управле ния на останов устройства. На узле 31 индикации фиксируется адрес дефектной ячейки памяти и характер де фекта. Для продолжения процесса про верки необходимо произвести снова пуск устройства. По окончании Л-го такта обргццени с регистров 2 адреса поступает сигнал , разрешающий смену теста (на ком мутатор 12) . Происходит включение следующего теста и матрица проверяется по следующему тесту. По окончании проверки матрицы по всем тестам происходит смена проверяемого разряда, после чего производится провер ка следующего разряда согласно щ ограмме 51роверки и т.д. После окончания проверки последне го разряда матрицы по всей программе проверки производится останов устройства и индицируется сигнал i окончания проверки. Для вьтолнения тестов обнаружения дефектов прошивки считанная из ячеек памяти информации усиливается усилителем 6 считывания и поступает в блок 9 на селекторы 19 и 20, где стробируется сигналами, поступающими со схемы 7 сравнения. Селекторы 19 и 20 осуществляют амплитудно-временную селекцию поступивших с усилителя 6 считывания сигналов и выдают информацию, на формирователи 21 и 22. В случае обнаружения с злемента ИЛИ 23 сигнал ошибки поступает на останов устройства и на индикацию характера нарушения (нарушение взаимнога расположения координатных обмоток и обмотки записи-считывания или нарушения в подключении соседних координатных обмоток. Тенденция увеличения быстродействия в выполнении операций ЭВМ неукоснительно требует уменьшения габаритов запоминающих матриц, увеличения плотности их монтажа, в связи с этим при изготовлении запоминающих матриц появились новые виды ошибок прошивки, так как нарушение взаимного расположения координатных обмоток и обмотки записи-считывания и нарушение в подключении соседних координатных обмоток. Описанное устройство позволяет обнаруживать эти ошибки. В Процессе проверки запоминающих матриц наблкщается также дрейф генераторов тока и порога срабатывания селекторов, что снижает точность и достоверность контроля. Введение оперативного контроля амплитуды им-ч пульсов токов и порога срабатывания селекторов перед каждой проверкой матриц позволяет повысить точность и достоверность контроля. Формула изобретения 1. Устройство для контроля запоминающих матриц, содержащее регистры адреса, далифраторы адреса, коммутаторы, усилитель считывания, схему : сравнения, генераторы тока и блок управления, причем одни из выходов регистров гщреса подключены ко входам деши а1оров адреса, одни из входов коммутаторов подключены к выходам дешифраторов адреса и одним из выходов генераторов тока, выходы коммутаторов подключены к первому входу усилителя считывания, первый выход которого соединен с первым входом cxetta сравнения, управлякхцие входы регистров гщреса, дешифраторов адреса, схемл сравнения, усилителя считывания, коммутаторов , генераторов тока подключены к выходам блока управления, первый выход схемы сравнения и другие выходы регистров адреса соединены с одними из входов блока управления, отличающее ся тем, что, с целью повышения быстродействия

устройства и точности и достоверности контроля оно содержит блок логического анализа и блок обнаружения ошибок в прошивке запоминающей матрицы, входы которого подключены соответственно к первому выходу усилителя считывания и второму выходу схема сравнения, а выходы - соответственно ко второму входу схемы сравнения и одному из входов блока логического анализа, другие входы которого соединены, со вторым выходом усилителя считывания и другими выходами генераторов тока, а выходы со вторым входом усилителя считы- . вания, входами генераторов тока и другим входом блока управления, одни из выходов которого соединены с управляницими входа1 м блока обнаружения ошибок в прошивке запоминающей матрицы и блока логического анализа

2.Устройство по П.1, отличающееся тем, что, блок обнаружения ошибок в прошивке запоминающей матрицы содержит амплитудновременные селекторы, формирователи сигналов ошибок и элемент ИЛИ, входы которого подключены к выходам формирователей сигналов ошибок, одни из входов которых подключены-к одним из выходов амплитудно-временных селекторов , другие входы которых и выход элемента ИЛИ являются выходами блока обнаружения ошибок в прошивке запоминающей матрицы, входами которого являются входы амплитудно-временных селекторов и другие входы формирователей сигналов ошибок.

3.Устройство по П.1, о т л и чающееся тем, что блок ло.гического анализа содержит формирователи эталонных сигналов, cxeNbi сравнения, формирователь калиброванных сигналов , измерительный узел, уз.ел индикации и блок местного управле-. ния, одни из выходов и входов которого подключены соответственно к управляющим входам схем сравнения измерительного узла и формирователя Ксшиброванных сигналов и к одним из выходов схем сравнения, другие выходы которых и выход измерительного узла соединены со входами узла индикации, выходы формирователей эталонных сигналов подключены к одним из входов схем сравнения,другие входы которых соединены соответственно с выходом измерительного узла и первым выходом формирователя калиброванных сигналов, первый вход которого соединен с выходом одного из формирователей эталонных сигналов, второй выход формирователя калиброванных сигналов и другие выходы блока местного управления являются выходами блока логического анализа, входами которого являются вход измерительного узла, второй и третий входы формирователя калиброванных сигналов и другой вход блока местного управления.

0 Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР 435566, кл. G 11 С 29/00, 1973. , 2.. Авторское свидетельство СССР по заявке 104710/18-24, кл. G 11 С 29/00, 1975 (прототип).

Фие.Ь

Отв

2.5

K€

18 Отб

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля ферритовых матриц | 1975 |

|

SU736176A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1981 |

|

SU963110A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1984 |

|

SU1200346A1 |

| Устройство для контроля матриц памяти на цилиндрических магнитных пленках с неразрушающим считыванием информации | 1986 |

|

SU1387045A1 |

| Запоминающее устройство | 1982 |

|

SU1062787A1 |

| Устройство для контроля матриц на ферритовых сердечниках | 1977 |

|

SU658601A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для контроля электронных изделий | 1978 |

|

SU951323A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

К8

Omf

I

26

i

27

/С/

f(6

i

w

Фие.

Авторы

Даты

1981-10-23—Публикация

1979-08-30—Подача