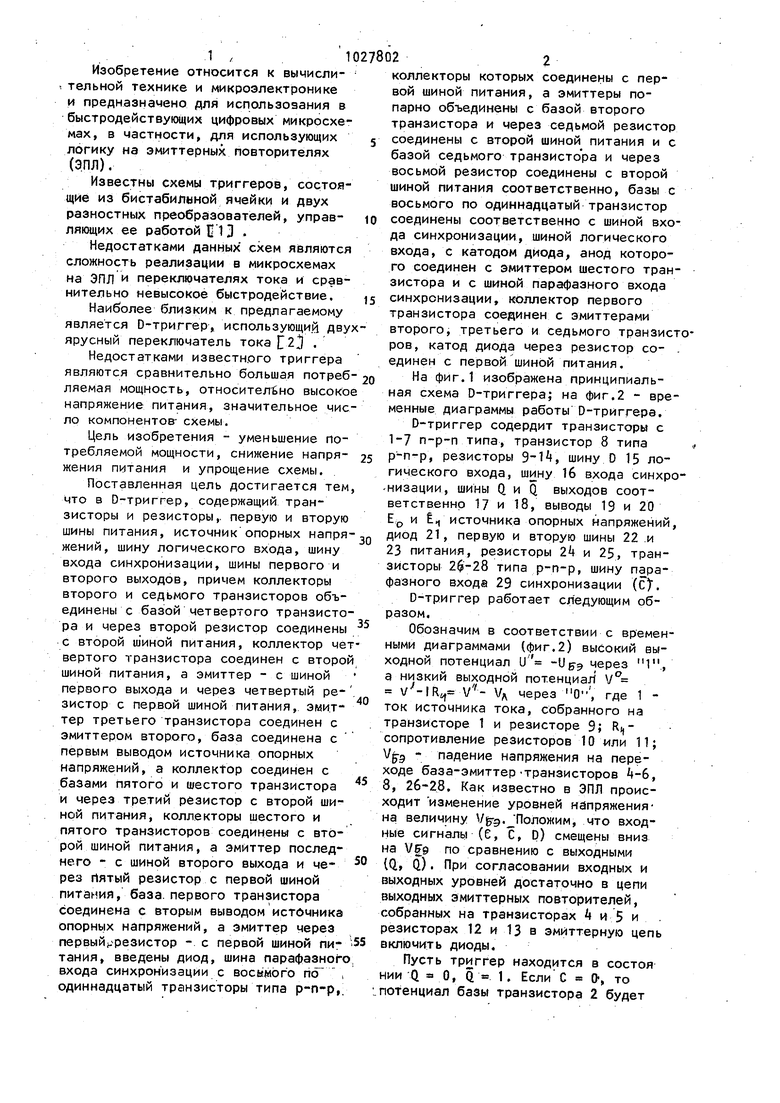

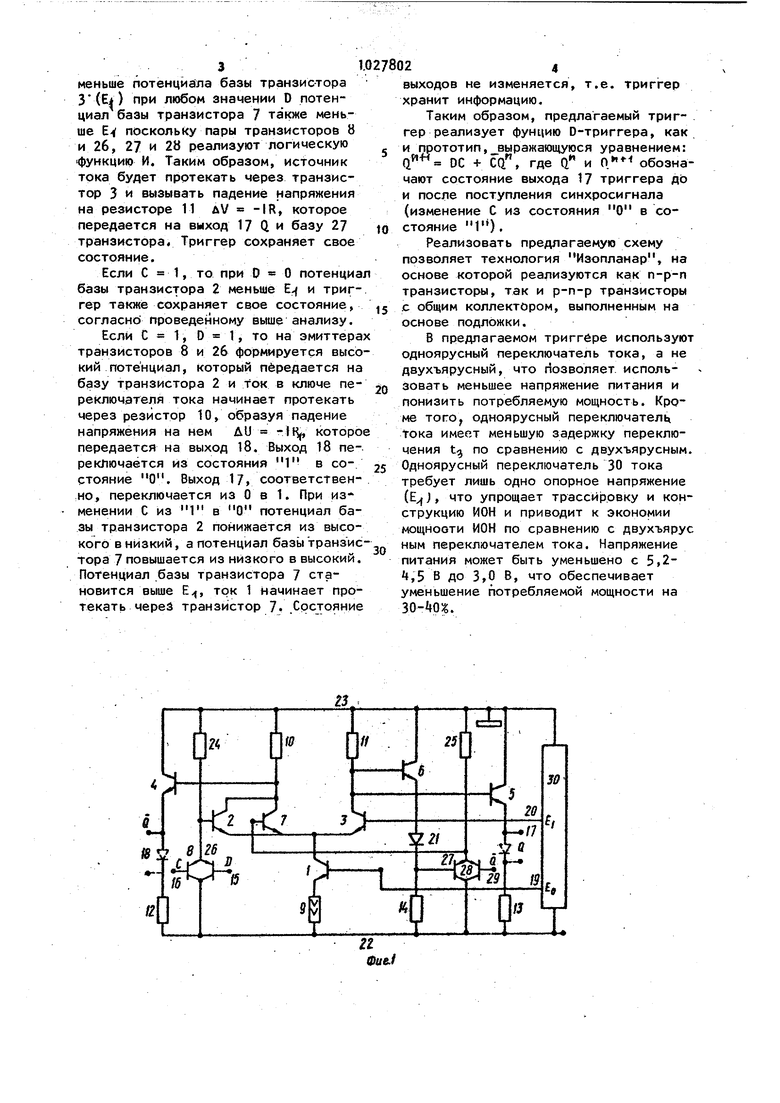

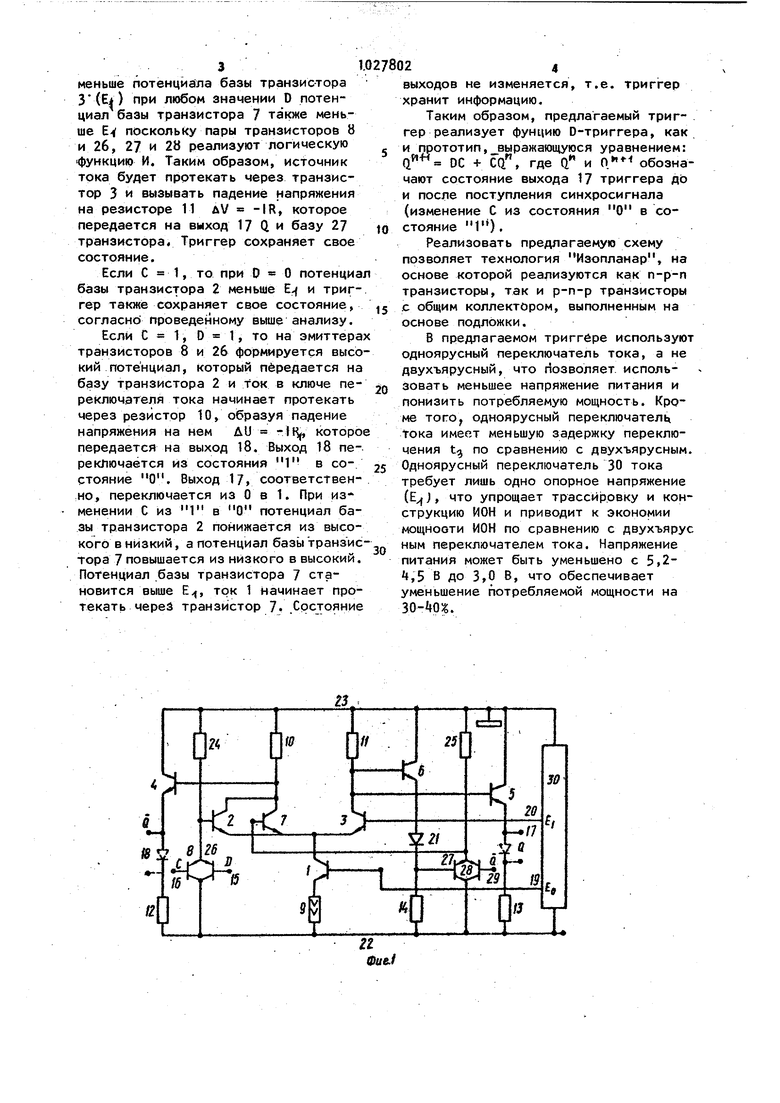

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для использования в быстродействующих цифровых микросхемах, в маетности, для использующих логику на эмиттерных повторителях (ЭПЛ). Известны схемы триггеров, состоящие из бистабильной ячейки и двух разностных преобразователей, управляющих ее работой Ц 13 Недостатками данных схем являются сложность реализации в микросхемах на ЭПЛ и переключателях тока и сравнительно невысокое быстродействие. Наиболее близким к предлагаемому является D-триггер, использующий дву ярусный переключатель тока 2 . Недостатками известного триггера являются сравнительно большая потреб ляемая мощность, относительно высоко напряжение питания, значительное чис ло компонентов- схемы. Цель изобретения уменьшение потребляемой мощности, снижение напряжения питания и упрощение схемы. Поставленная цель достигается тем что в D-триггер, содержащий транзисторы и резисторы,, первую и вторую шины питания, источник опорных напря жений, шину логического входа, шину входа синхронизации, шины первого и второго выходов, причем коллекторы второго и седьмого транзисторов объединены с базой четвертого транзисто ра и через второй резистор соединены с второй шиной питания, коллектор че вертого транзистора соединен с второ шиной питания, а эмиттер - с шиной первого выхода и через четвертый ре. W зистор с первой шиной питания, эмит тер третьего транзистора соединен с эмиттером второго, база соединена с первым выводом источника опорных напряжений, а кoллeкtop соединен с базами пятого и шестого транзистора и через третий резистор с второй шиной питания, коллекторы шестого и пятого транзисторов соединены с второй шиной питания, а эмиттер последнего - с шиной второго выхода и через Иятый резистор с первой шиной питания, база, первого транзистора соединена с вторым выводом источника опорнь1х напряжений, а эмиттер через первый;..резистор - с первой шиной питания, введены диод, шина парафаз ногвхода синхронизации с восьмого rid одиннадцатый транзисторы типа р-п-р, коллекторы которых соединены с первой шиной питания, а эмиттеры попарно объединены с базой второго транзистора и через седьмой резистор соединены с второй шиной питания и с базой седьмого транзистора и через восьмой резистор соединены с второй шиной питания соответственно, базы с восьмого по одиннадцатый транзистор соединены соответственно с шиной входа синхронизации, шиной логического входа, с катодом диода, анод которого соединен с эмиттером шестого транзистора и с шиной парафазного входа синхронизации, коллектор первого транзистора соединен с эмиттерами второго, третьего и седьмого транзисторов, катод диода через резистор со- . единен с первой шиной питания. На фиг.1 изображена принципиальная схема D-триггера; на фиг.2 - временные диаграммы работы D-триггера. D-триггер содердит транзисторы с 1-7 п-р-п типа, транзистор 8 типа р-п-р, резисторы 9-1, шину D 15 логического входа, шину 16 входа синхронизации, шины Q и Q выходов соответственно 17 и 18, выводы 19 и 20 Ер и ЕЧ источника опорных напряжений, диод 21, первую и вторую шины 22 .и 23 питания, резисторы 24 и 25, транзисторы 2$-28 типа р-п-р, шину па рафазного входа 29 синхронизации (Cj, D-триггер работает следующим образом. Обозначим в соответствии с временными диаграммами (фиг.2) высокий выходной потенциал U -Ug- через 1., а низкий выходной потенциал 1 v-lR V- Уд через , где 1 ток источника тока, собранного на транзисторе 1 и резисторе 9 Ri)сопротивление резисторов 10 или 11; - падение напряжения на переходе база-эмиттерТранзисторов k-6, 8, 26-28. Как известно в ЭПЛ происходит изменение уровней напряженияна величину Уg-g.Положим, что входные сигналы (с. С, р) смещены вниз на yg9 по сравнению с выходными (0., Q). При согласовании входных и выходных уровней достаточно в цепи выходных эмиттерных повторителей, собранных на транзисторах k и 5 и резисторах 12 и 13 в эмиттерную цепь включить диоды. Пусть триггер находится в состоя НИИ Q О, Q - 1, Если С О-, то пoteнциaл базы транзистора 2 будет меньше потенцййла базы транзис-тора 3(Е) при любом значении О потенциал базы транзистора 7 также меньше Е поскольку пары транзисторов 8 и 26, 27 и 28 реализуют логическую функцию И. Таким образом, источник тока будет протекать через транзистор 3 и вызывать падение напряжения на резисторе 11 AV -IR, которое передается на выход 17 Q и базу 27 транзистора. Триггер сохраняет свое состояние. Если С 1, то при D О потенциа базы транзистора 2 меньше Е. и триггер также сохраняет свое состояние, согласно проведенному выше анализу. Если С 1, D 1, то на эмиттера транзисторов 8 и 26 формируется высо кий потенциал, Который передается на базу транзистора 2 и ток в ключе переключателя тока начинает протекать через резистор 10, образуя падение напряжения на нем ди rlHp которо передается на выход 18. Выход 18 переключается из состояния 1 в состояние О. Выход 17, соответствен;НО, переключается из О в 1. При из менении С из 1 в О потенциал базы транзистора 2 понижается из высокого в низкий, а потенциал базы транзис тора 7 повышается из низкого в высокий. Потенциал базы транзистора 7 становится выше Е, ток 1 начинает протекать через транзистор 7. Состояние выходов не изменяется, т.е. триггер хранит информацию. Таким образом, предлагаемый триггер реализует фунцию D-триггера, как и прототип, выражающуюся уравнением: Q DC -и CQ, где а и обозначают состояние выхода 17 триггера до и после поступления синхросигнала (изменение С из состояния О в состояние 1). Реализовать предлагаемую схему позволяет технология Изопланар, на основе которой реализуются как п-р-п транзисторы, так и р-п-р транзисторы с общим коллектором, выполненным на основе подложки. В предлагаемом триггере используют одноярусный переключатель тока, а не двухъярусный, что позволяет использовать меньшее напряжение питания и понизить потребляемую мощность. Кроме того, одноярусный nepeключaтeл Тока имеет меньшую задержку переключения ц по сравнению с двухъярусным. Одноярусный переключатель 30 тока требует лишь одно опорное напряжение (Е J, что упрощает трассй|эовку и конструкцию ИОН и приводит к экономии мощности ИОН по сравнению с двухъярус ным переключателем тока. Напряжение питания может быть уменьшено с 5,2k,S В до 3,0 В, что обеспечивает уменьшение потребляемой мощности на O-ifO.

J

У

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер | 1983 |

|

SU1132343A1 |

| Близостный переключатель | 1988 |

|

SU1539855A1 |

| Троичный счетный триггер | 1979 |

|

SU864503A1 |

| Универсальный Д(Т)-триггер | 1988 |

|

SU1561200A1 |

| Логический элемент "исключительное ИЛИ | 1982 |

|

SU1045397A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| Троичный фронтальный Д-триггер | 1980 |

|

SU917307A1 |

| Мостовой троичный триггер | 1984 |

|

SU1231581A1 |

| Д-триггер с селектором на входе | 1989 |

|

SU1707741A1 |

Q

Фие.2.

| , 1 | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Я.БУДИНСКИЙ | |||

| Логические цепи в цифровой технике | |||

| М., Связь, 1977, с.37«, рис.7.90 (прототип). | |||

Авторы

Даты

1983-07-07—Публикация

1982-03-05—Подача