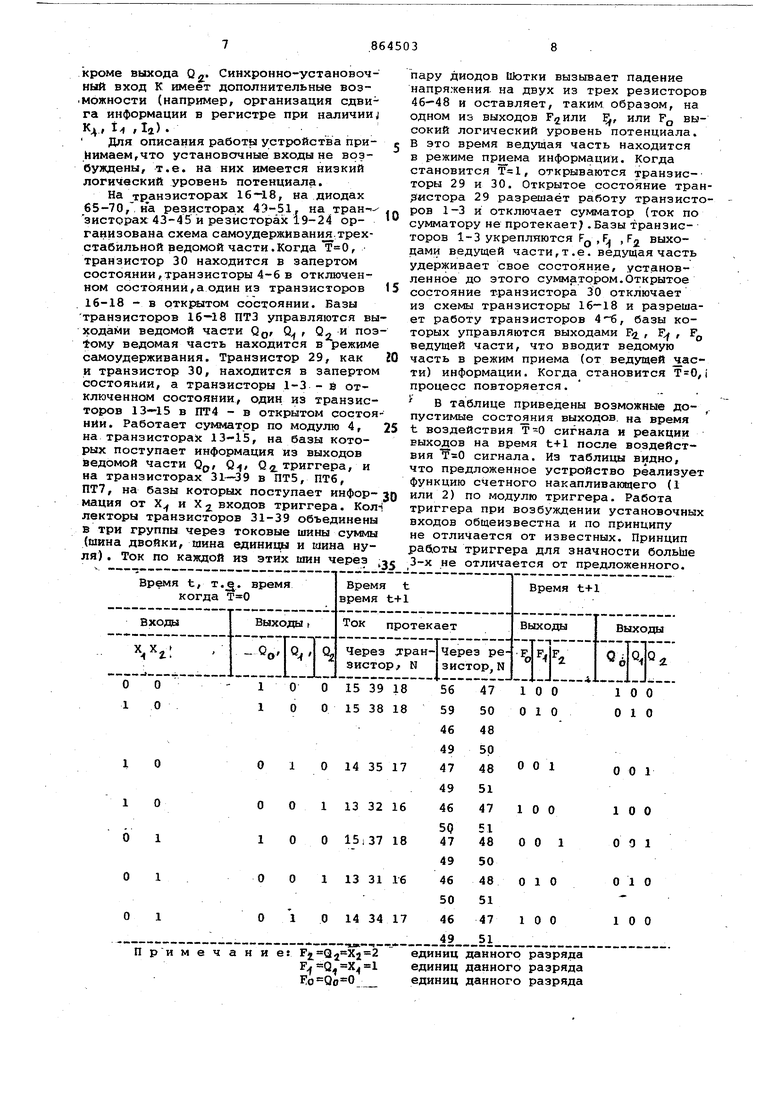

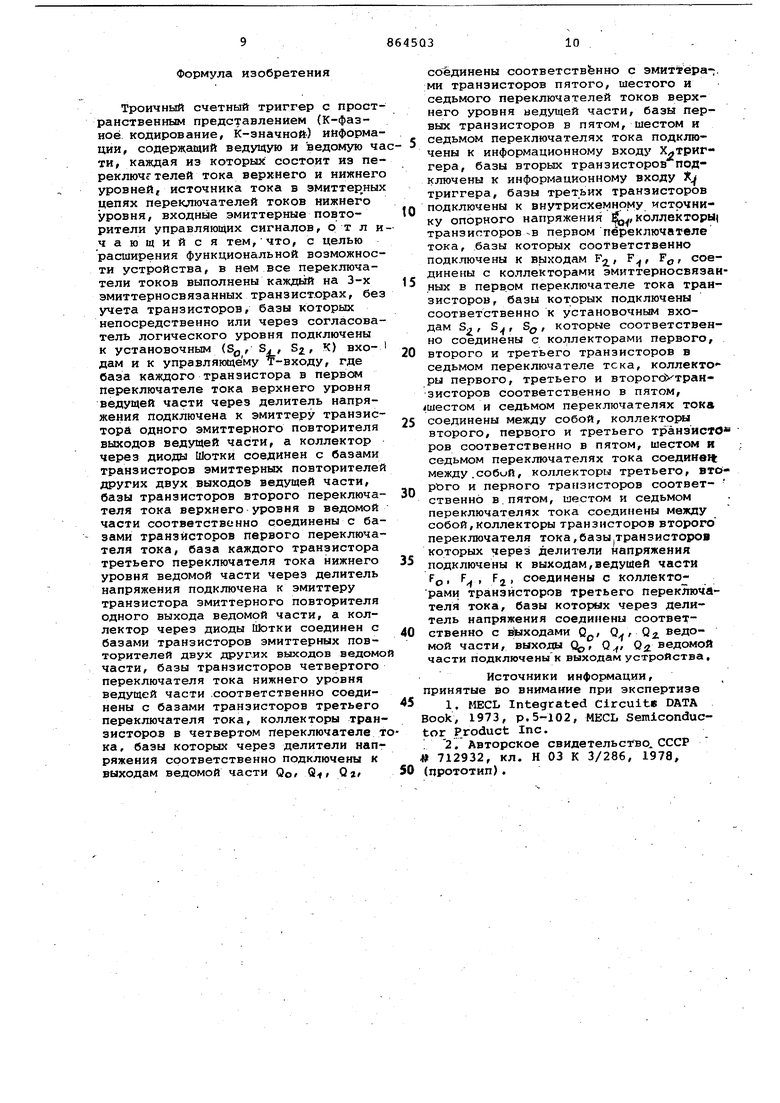

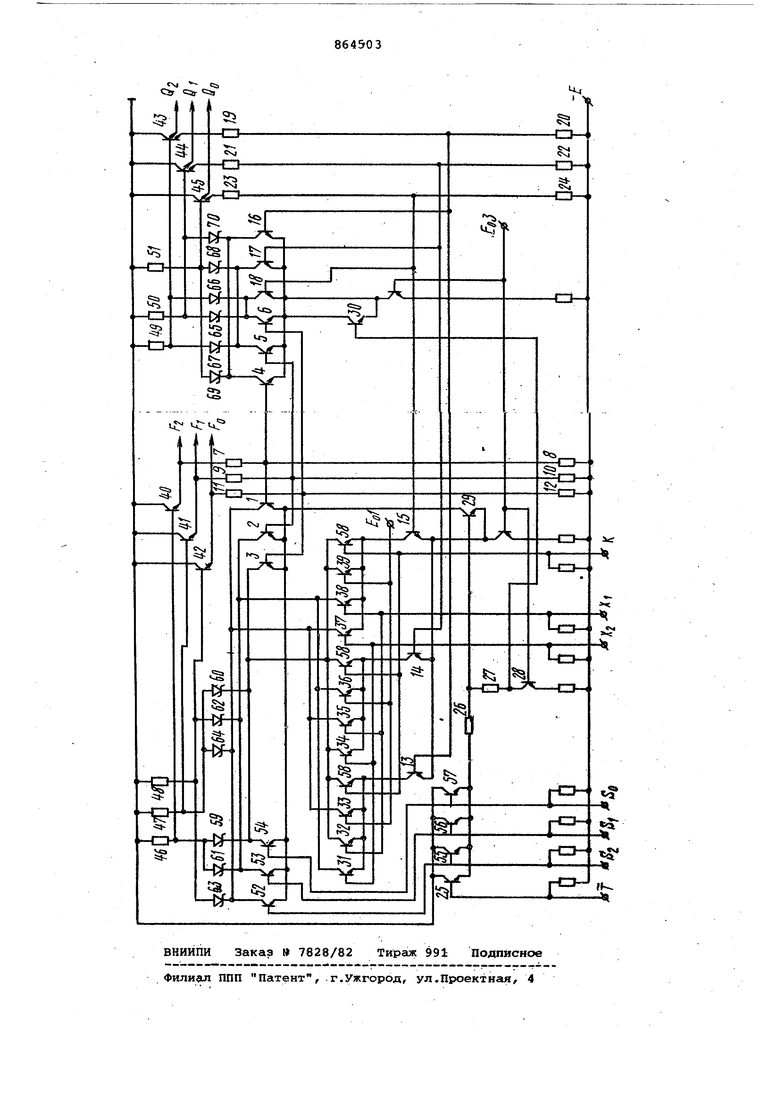

Изобретение относится к многозначным потенциальным логическим элементам с пространственным представлением (К-фазное кодирование, К-значной:) информации, в частности к счетньол накапливающим по модулю триггерам в интегральном исполнении. Известен 1-К-триггер, содердаций ведущую и ведомую части, каждая из которых состоит из переключателей тока варх-него, среднего и нижнего уровней, два источника тока, источники четырех опорных напряжений и входные эмиттерные повторители l. Недостатком устройства являются узкие функциональные возможности. Известен триггер, содержгиций ведущую и ведомую части и в каждой из них переключатели тока верхнего и нижнего уровней, в том числе первый переключатель тока ПТ1 верхнего уровня, обеспечивающий работу в режиме самоудержания ведущей части, коллекторкаждого, транзистора, в котором через эмиттерный повторитель (ЭП) подключен к одному выходу части и оттуда че рез делитель напряжения на резисторах соединен взаимно с базой другого эмит |Терно-связанного транзистора ПТ2 верх шего уровня, обеспечивающий прием (от ведущего) информации ведомой частИ| базы транзисторов которых соединен с базами транзисторов ПТ1 соответственно, а коллекторы с базами транзисторов ЭП выходов ведомой части соответственно ПТЗ нижнего уровня ведомой части, обеспечивающий работу в режиме самоудерживания ведомой части,коллекторы каждого транзистора в котором соединены с базой транзистора ЭП одного выхода ведомой части, а база через делитель напряжения подключена к эмиттеру транзистора ЭП другого выхода ведомой части, ПТ4 нижнего уровня ведущей части, базы транзисторов которого соединены с базами транзисторов ПТЗ соответственно, а коллектора - с эмиттерами транзисторов ПТ5 и ПТ6 верхнего уровня соответственно , базыинформационного транзистора в одном из которых подключен к входу К , а в другом из которых ко входу I. Ведущая часть снабжена дополнительна- транзистором, коллектор которого соединен с эмиттерами транзисторов ПТ1, а эмиттер - с 3MHTt терами транзисторов ПТ4, ведомая часть снабжена дополнительныг транзистором, коллектор которого соединен с эмиттерами транзисторов ПТ2, а эмитг тер - с эмиттерами транзисторов ПТЗ, базы дополнительных транзисторов через согласователь логического уровня подключен к входам CRS устройства 2. Недостатком данных устройств яв ляются узкие функциональные возможности, отсутствие возможности работы для К-основания считывания, отличного от 2-х. | Цель изобретения - расширение функциональной возможности устройства. Для достижения поставленной цели в троичном счетном триггере с пространственным представлением (К-фазное кодирование К-значной информации), содержащем ведущую и ведомую части, каждая из которых состоит из переключателей тока верхнего и нижнего -уровней, источника тока в эмиттерных переключателей токов нижнего уровня, входные эмиттерные повторители управляющих сигналов, все переключатели тока выполнены каждый на 3-х эмиттерносвязанных транзисторах, без учета транзисторов, базы которых непосредственно или через согласовател логического уровня подключены к уста новочным ( S , S2f :к) входам, и к управляющему Т-входу, где база каждого транзистора в первом переключателе тока верхнего уровня веду1цей части через делитель напряжения подключена к эмиттеру транзистора одного эмиттерного повторителя выходов веду щей части, а коллектор через дибды Шотки соединен с базами транзисторов эмиттерных повторителей других двух выходов ведущей части,базы транзисторов второго переключателя тока вёрнего уровня в ведомой части соответственно соединены с базами транзисто ров первого переключателя тока, база кааодого транзистора третьего переклю чателя -тока нижнего уровня ведомой части через делитель напряжения подключена к эмиттеру транзистор эмиттерного повторителя одного ЭП одного выхода ведомой части, а коллектор через диоды Шотки соединен с базами транзисторов эмиттерных повторителей других двух выходов ведомой части, базы транзисторов четвертого переключателя тока нижнего уровня ве дущей части соответственно соединены с базами транзисторов третьего перек лючателя тока, коллекторы транзисторов в четвертом переключателе тока, базы которых через делители напряжения соответственно подключены к вых дам ведомой части Qjj, Q, Q, соединены соответственно с эмиттерами транзисторов пятого, шестого и седьмого переключателей токов верхнегоуровня ведущей части, базы первых транзисторов в пятом,, шестом и седьмом переключателях тока подключены к информационному входу Х триггера, базы вторых транзисторов подключены к И(1формационному входу X. триггера, базы третьих транзисторов подключены к внутрисхемному источнику опорного напряжения Е, коллекторы транзисторов в первом переключателе тока, базы которых соответственно подключены к выходам F2, F , Р,, соединены с коллекторами эмиттерно-связанных в первом переключателе тока транзисторов, базы которыхподключены соответственно к установочным входам Srtf Syf которые соответственно соединены с коллекторами первого,второго и третьего транзисторов в седьмом переключателе тока, коллекторы первого,третьего и второго транзисторов соответственно в пятом, шестом и седьмом переключателях тока соединены между собой, коллекторы второго, первого и третьего транзисторов соответственно в пятом, шестом и седьмом переключателях тока соединены мезкду собой, коллекторы третьего, второго и первого транзисторов соответственно в пзтом, шестом и седьмом переключателях тока соединены между собой, коллекторы транзисторов второго переключателя тока, базы транзисторов которых через делители 1апряжения подключены к выходам ведущей части F , F , Fg .соединены с коллекторами транзисторов третьего переключателя тока, базы которых через делитель напряжения соединены .соответс.твенно с выходами ведомой части Qo,Q,Q2 выходы Q(.j,Q.Qj ведомой части подключены к выходам устройства.. На чертеже представлена принципиальная электрическая схема предложенного устройства. Устройство солеожит ведущую и ведомую части, каждая снабженная 3-мя выходами FQ , F, F и Q, Q,,, Ц 2 соответственно Выходы ведомой части Q(j, Q, Qg подключены к выходам устройства. Опорные напряжения ПТ верхнего и нижнего уровня обозйачены как Ед и Некоторые опорные напряжения явно не выделяются, так как они организованы на рёзисторных делителях между вы-ходами Р,, F , F, Qp, Q, Qg и шиной питания - Б. База 3-х эмиттерносвязанных транзисторов 1-3 в первом переключателе тока (ПТ1) верхнего .уровня, обеспечивающем режим самоудерживания ведущей части, и базы .эмиттерно-связанных транзисторов 4-6 в ПТ2 верхнего уровня, обеспечивающем режим приема информации (от ведущей) ведомой части, через делители напряжения на резисторы 7 и 8 9 и 10,11 и 12 подключены к выходам ведущей части соответственно. Базы 3-х транзисторов 13-15 в ПТ4 нижнего уровня, обеспечивающем режим приема информации ведущей час1ти, и базы 3-х транзисторов 16-18 в ПТЗ нижнего уровня, обеспечивающем режим самоудерживания ведомой части, через делители напряжения на резисторах 19 и 20, 21 и 22, 23 и 24 подключены к выходам ведомой части Q/j. QO соответственно. Синхронизирующий Т вход устройства подключен к базе транзистора 25 эмиттерного повторителя (ЭП). В эмиттерную цепь транзистора ЭП включены пос ледовательно два резистора 26 и 27 и генератор тока (ГТ) на транзисторе 28. Точка между резисторами 26 и 27ЭП подключена к бгзе дополнительного транзистора 29, обеспечивающего переключение режима ведущей части, коллектор которого,соединен с эмитте рами транзисторов 1-3 в ПТ1, а эмиттер транзистора 29 соединен с эмиттерами транзисторов 13-15 в ПТ4 и че рез ГТ- с шиной питания -Е. Точка между резистором 27 и транзистором Г 28подключена к базе дополнительного транзистора 30, обеспечивающего пере лючение режима ведомой части, коллек тор которого соединен с эмиттерами транзисторов 4-6 в ПТ2, а эмиттер транзистора 30 соединен с эмиттерами транзисторов 16-18 в ПТЗ и через ГТс шиной питания -Е. В коллекторной ц пи транзистора 13 в ПТ4, база которо го через делитель напряжения подключена к выходу Q, включен ПТ5 на транзисторах 31-33. В коллекторной цепи транзистора 14 в ПТ4, базы кото .рого через делитель напряжения подключены к выходу QJ.включен ПТ6 на транзисторах 34-36. В коллекторной цепи транзисторов 15 в ПТ4, база которого через делитель напряжения на резисто рах 21, 22 подключена к выходу Qp, включен ПТ7 на транзисторах 37-39. Нумерация транзисторов в ПТ5, ПТб, ПТ7 произведена нарастанием слева направо. Базы первых слева транзисторов 31,34,37вПТ5 ПТ7 подключены к входу X-jj устройства для приема информации второй фазы входного операнда. Базы вторых слева транзисторов 32, 35, 38 в ПТЗ, ПТ6, ПТ7 подключены к вход Х, для приема информации первой Лазы входного операнда. Базы последних слева транзисторов 33, 36, 39 псдкяю чёны к источнику ЕО. Коллектор второ го слева транзистора 32 соединен с коллектором первого слева транзистора 34 в ПТ6. Коллектор третьего слева транзистора 33 в ПТ5 соединен с коллектором второго слева транзистора 35 в ПТ6 и с коллектором первого слева транзистора 37 в ПТ7. Коллектор последнего слева транзистора 36 в ПТ6 соединен с коллектором второго слева транзистора 38 в ПТ7. Коллектор первого слева транзистора 31 в IITS соединен с коллектором последнего слева транзистора 36 в ПТ6. Коллектор пос 1еднего слева транзистора 39 в ПТ7 соединен с коллектором первого слева транзистора 34 в ПТ6, Вазы выходных транзисторов 40-45 соответственно через резисторы 46-51 подключены к общей шине, а эмиттеры - к выходам ве о V 2 ведомой часдущей части F, ти Qj, , Q соответственно. ПТ1 снабжен дополнительно тремя эмиттерносвязанными транзисторами 5254 , базы которых подключены соответственно к асинхронно-установочным входам S,, S, SQ устройства. К асинхронно-установочным входам подключены также брзы транзисторов 55-57, эмиттерносвязанные с транзистором 25 в ЭП, база которого подключена к входу устройства. Коллектор транзистора 54 в ПТ1, база которого подключена к входу Sp, коллектор транзистора 3 в ПТ1, база которого через делитель напряжения на резисторах 11, 12 подключе-) на к выходу Гр,и коллектор транзистора 39 в ПТ7, база 58 которого подключена к EQ , соединены между собойг и через диоды Шотки 59 и 6.0 подключены к базам всех исходных транзисторов ведщей части, кроме выхода FO , Коллектор транзисторов 53 и 2 в ПТ1,базы которых подключены к асинхронноустановочному (ВХОДУ S, через делитель напряжения на резисторах 9, 10 к выходу F и коллектор .транзистора 38 в ПТ7, база которого подключена к выходу X., соединены между собой и через диоды Шотки 61 и 62 подключены к базам всех выходных транзисторов ведущей части, кроме выхода Fj . Коллектор транзистора 52, 37 и 1, базы которых подключены к асинхронноустановочному входу S. к входу Xj и через делитель резисторах напряжения - к выходу F., соединены между собой и через диоды Шотки 63 и 64 подключены к базам всех выходных транзисторов ведущей части, кроме выхода F . Коллекторы транзисторов 6 и 18 в ПТ2 и ПТЗ, базы которых через делители напряжения на резисторах, 11, 12 и 23, 24: соответственно подключены к выходам ведущей части F и ведомой части Q, соединены между собой и через диоды Шотки 65 и 66 подключены к базам всех выходных транзисторов ведомой части,кроме выхода Од. Коллекторы транзисторов 5 и 17 в ПТ2 и ПТЗ, базы которых через елители напряжения на резисторах 9, 10 и 21, 22 соответственно подклюены к выэсодам F и Q, соединеы между собой и через диоды Шотки 67 и 68 подключены к базам всех выодных транзисторов ведомой части, кроме выхода Q. Коллекторы транзисоров 4 и 16 в ПТ2 и ПТЗ, базы кото-, ых через делители напряжения на ре- зисторах 7, 8 и 19, 20 соответственно подключены к выходам и Q j г оединены между собой и через диоды 9 и 70 подключены к базам всех выодных транзисторов ведомой частн. кроме выхода Q. Синхронно-установочный вход К имеет дополнительные воз.можности (например, организация сдвига информации в регистре при наличии К il J 1а) Для описания работы устройства прийимаем,что установочные входы не возбуждены, т.е. на них имеется низкий логический уровень потенциала. На транзисторах 16-18, на диодах 65-70, на резисторах 43-51, на тран зисторах 43-45 и резисторах 19-24 организована схема самоудержмван1ш трехстабильной ведомой части.Когда , транзистор 30 находится в запертом состоянии,транзисторы 4-6 в отключенном состоянии,а один из транзисторов 16-18 - в открытом состоянии. Базы транзисторов IS-I8 ПТЗ управляются вы ходами ведомой части QQ, Q Q и поз Юму ведомая часть находится в режиме самоудерживания. Транзистор 29, как и транзистор 30, находится в запертом состоянии, а транзисторы 1-3 - в отключенном состоянии, один из транзисторов 13-15 в 1174 - в открытом состоя нии. Работает сумматор по модулю 4, на транзисторах 13-15, на базы которых поступает информация из выходов ведомой части Qp, Q, Qj, триггера, и на транзисторах 31-39 в ПТ5, ПТ6, ПТ7, на базы которых поступает информация от Х , входов триггера. Кол лекторы транзисторов 31-39 объединены в три группы через токовые шины суммы (шина ДВОЙКИ, шина единицы и шина нуля) . Ток по каждой из этих шин через пару диодов Шотки вызывает падение напряжения, на двух из трех резисторов 46-48 и оставляет, таким образом, на одном из выходов , или PQ высокий логический уровень потенциала. В это время ведущая часть находится в режиме nptjeMa информации. Когда становится , открываются транзисторы 29 и 30. Открытое состояние транЭистора 29 разрешает работу транзисторов 1-3 и отключает сумматор (ток по сумматору не протекает). Базы Транзисторов 1-3 укрепляются FQ ,F. , Fg выходами ведущей части,т.е. ведущая часть удерживает свое состояние, установленное до этого сумматрром.Открытое состояние транзистора 30 отключает из схемы транзисторы 16-18 и разрешает работу транзисторов 4, базы которых управляются выходами Ej. , F , F ведущей части, что вводит ведомую часть в режим приема (от ведущей ч асти) информации. Когда становится , i процесс повторяется. В таблице приведены возможные допустимые состо яния выходов, на время t воздействия сигнала и реакции выходов на время t+1 после воздействия Т«0 сигнала. Из таблищл видно, что предложенное устройство реализует функцию счетного накапливающего (1 или 2) по модулю триггера. Работа триггера при возбуждении установочных входов общеизвестна и по принципу не отличается от известных. Принцип раб1оты триггера для значности больше 3-х не отличается от предложенного. Формула изобретения Троичный счетный триггер с прост ранственным представлением (К-фазноё кодирование, К-эначной) информа ции, содержащий ведущую и ведомую ч ти, каждая из которых состоит иэ пе реключгтелей тока верхнего и нижнег уровней источника тока в эмиттер ны цепях переключателей токов нижнего уровня, входные эмиттерные повторители управляющих сигналов, от л и чающийся тем, что, с целью расширения функциональной возможнос ти устройства, в нем все переключатели токов выполнены каждь1й на 3-х эмиттерносвязанных транзисторах, бе учета транзисторов, базы которых непосредственно или через согласова тель логического уровня подключены к установочным (S, S, S, К) входам и к управляющему т-входу, где база каждого транзистора в первом переключателе тока верхнего уровня ведущей части через делитель напряжения подключена к эмиттеру транзистора одного эмиттерного повторителя выходов ведущей части, а коллектор через диоды Шотки соединен с базами транзисторов эмиттерных повторителей других двух выходов ведущей части, базы транзисторов второго переключателя тока верхнего уровня в ведомой части соответственно соединены с базами транзисторов первого переключателя тока, база каждого транзистора третьего переключателя тока нижнего уровня ведомой части через делитель напряжения подключена к эмиттеру транзистора эмиттерного повторителя одного выхода ведомой части, а коллектор через диоды Шотки соединен с базами транзисторов эмиттерных повторителей двух других выходов ведомо части, базы транзисторов четвертого переключателя тока нижнего уровня ведущей части .соответственно соединены с базами транзисторов третьего переключателя тока, коллекторы транзисторов в четвертом переключателе т ка, базы которых через делители напряжения соответственно подключены к выходам ведомой части Qo Qj/ соединены соответственно с эмиттера-, ми транзисторов пятого, шестого и седьмого переключателей токов верхнего уровня ведущей части, базы первых транзисторов в пятом, шестом и седьмом переключателях тока подключены к информационному входу Х триггера, базы вторых транзисторов подключены к информационному входу t. триггера, базы третьих транзисторов подключены к внутрисхемному источнику опорного напряжения , коллекторы транзисторов-в первом переключателе тока, базы которых соответственно подключены к выходам F, F, F,, соединены с кoллeктopa 4и эмиттерносвязанных в первом переключателе тока транзисторов, базы которых подключены соответственно к установочным входам S, S, S, которые соответственно соединены с коллекторами первого, второго и третьего транзисторов в седьмом переключателе тска, коллекторы первого, третьего и второгоХтранзисторов соответственно в пятом, шестом и седьмом переключателях тока соединены между собой, коллекторы второго, первого и третьего транзисто ров соответственно в пятом, шестом и седьмом переключателях тока соединвЦг между.собой, коллекторы третьего, вторЬго и первого транзисторов соответственно в,пятом, шестом и седьмом переключателях тока соединены между собой,коллекторы транзисторов второго переключателя тока,базы транзисторов которых через делители напряжения подключены к выходам,ведущей части f0, f, Fj, соединены с коллекторами транзисторов третьего переключателя тока, базы которых через делитель напряжения соединены соответственно с 1(ыходами Q , Q, Qf. ведомой части, выходы Q, Q, Q ведомой части подключенык выходам устройства. Источники информации, ринятые во внимание при экспертизе 1. MECL Integrated Circuite DATA ook, 1973, p.5-102, MECL Semiconducor Product Inc. 2, Авторское свидетельство. СССР 712932, кл. Н 03 К 3/286, 1978, прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВИБРАЦИЙ ИНФРАНИЗКИХ ЧАСТОТ | 1966 |

|

SU216298A1 |

| Усилитель | 1991 |

|

SU1818678A1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2003 |

|

RU2234797C1 |

| Фронтальный D-триггер | 1979 |

|

SU896758A1 |

| ТРЕХВХОДОВЫЙ СУММАТОР | 1972 |

|

SU429422A1 |

| Троичный фронтальный Д-триггер | 1980 |

|

SU917307A1 |

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

| -К-триггер | 1978 |

|

SU712932A1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ ТОКОВОЙ ОБРАТНОЙ СВЯЗЬЮ | 2006 |

|

RU2321157C1 |

| Логический элемент | 1984 |

|

SU1200413A1 |

Авторы

Даты

1981-09-15—Публикация

1979-07-24—Подача