второго и третьего, четвертого диодов катоды первого и третьего диодов подключены соответственно к первому и второму информационным входам, катоды второго и четвертого диодов - к базам соответственно девятого и восьмого транзисторов, эмиттеры двадцатого и двадцать первого транзисторов подключены соответственно к базам девятнадцатого и восемнадцатого транзисторов и через соответственно вось113 мой и девятый источники тока - к шине питания, дополнительные эмиттеры четырнадцатого, пятнадцатого и эмиттеры восемнадцатого, девятнадцатого транзисторов соединены с коллектором четвертого транзистора, вторые выводы первого и второго резисторов через-девятый резистор, а вторые выводы пятого и шестого резисторов через десятый резистор соединены с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный усилитель мощности для магнитофона | 1979 |

|

SU902205A1 |

| Формирователь импульсов управления | 1987 |

|

SU1522387A2 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Стереодекодер для системы стереофонического радиовещания с полярной модуляцией | 1991 |

|

SU1748269A1 |

| Мостовой троичный триггер | 1987 |

|

SU1448390A1 |

| Полный троичный сумматор | 1979 |

|

SU826342A1 |

| Программируемый приемник сигналов для коммутационных сред | 1988 |

|

SU1718236A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Входное устройство схемы сравнения токов | 1989 |

|

SU1626360A1 |

| Входное устройство схемы сравнения токов | 1988 |

|

SU1529434A1 |

ТРИГГЕР, содержащий двадцать один транзистор, девять резисторов, три диода и семь источников тока, база первого транзистора прдключена к тактовому входу, коллекторк общей шине, эмиттер - к базам . второго и третьего транзисторов ,и, через первый источник тока - к шине , питания, эмиттеры второго и третьего транзисторов соединены соответственно с эмиттерами четвертого и пятого транзисторов и соответственно через второй и третий источники тока с шиной питания, базы четвертого и пятого транзисторов соединены с входом опорного напряжения, коллекторы третьего и пятого транзисторов соединенЫ соответственно с эмиттерами шестого, седьмого и восьмого, девятого транзисторов, коллектор шестого транзистора соединен с первым выводом первого резистора, коллектором восьмого транзистора и базами десятого и одиннадцатого транзисторов, коллекторы которых подключены к общей шине, коллектор седьмого транзистора соединен с первым выводом второго резисто-. ра, коллектором девятого транзистора и базами двенадцатого и тринадцатого транзисторов, коллекторы которых подключены к обцей -шине, эмиттеры одиннадцатого и тринадцатого транзисторов подключены соответствеино к первому и второму выходам триг-; гера, эмиттеры десятого и двенадцатого транзисторов соединены соответ-г ственно с базами девятого и восьмого транзисторов и соответственно через четвертый и пять источники тока с шиной питания, базы шестого и седь- мого транзисторов соединены соответственно с базами четырнадцатого и пятнадцатого транзисторов, соответственно через шестой и седьмой источники тока - с шняой питания, соответственно через третий и четвертый резисторы - с эмиттерами шестнадцатого и семнадцатого транзисторов, коллекторь которых соединены с общей шиной, а базы соответственно00 N9 с первьв4И выводами шестого и пятого резисторов и соответственно с коллекторами пятнадцатого, восемнад00 цатого и четырнадцатого, девятнадцаNU того т ранзисторов, эмиттеры четырUd надцатого и пятнадцатого транзисторов соединены с коллектором второго транзистора, отличающийся тем, что, с целью уменьшения потребляемой мощности, в него введены десятый резистор, четвёртый диод, восьмой и девятый источники тока, коллекторы двадцатого и двадцать первого транзисторов подключены к общей шине, базы соответственно через седьмой и восьмой резисторы - к общей шине и к анодам соответственно первого..

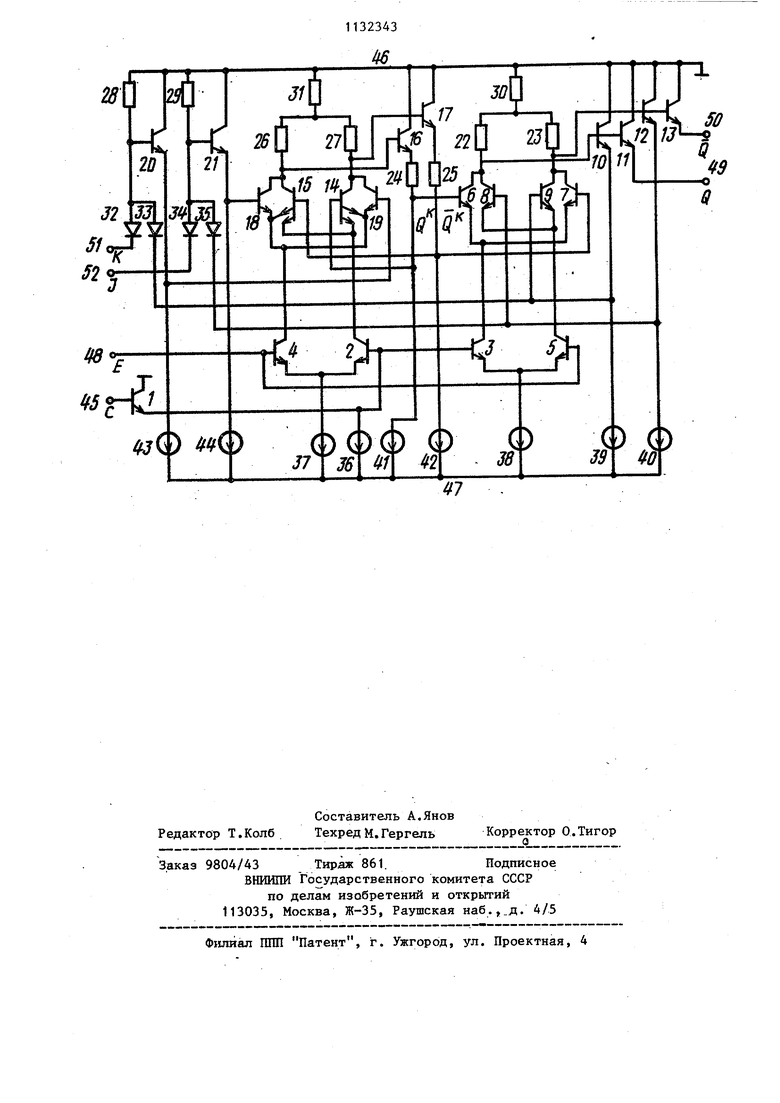

Изобретение относится к импульсной технике, а именно к устройствам с двумя устойчивыми состояниями, и может быть использовано в цифровых микросхемах на переключателйх тока. Известен триггер, построенный в базисе низкоуровневой эмиттерносвязанной логики с обратной связью р . Недостатком известного триггера является малое быстродействие и низкая помехоустойчивость. Наиболее близким к изобретению является триггер, содержапщй двадцать три транзистора. Девять резисторов, три диода и семь источников тока, база первого транзистора подключена к тактовому входу, коллектор к общей шине, эмиттер через первый д од и седьмой резистор - к базам второго и третьего транзисторов и через первый источник тока к шине питания, эмиттеры второго и третьего транзис торов соединены соответственно с . эмиттерами четвертого ri пятого транзисторов и соответственно через второй и третий источники тока с шиной питания, базы четвертого и пятого транзисторов соединены с входом опор ного напряжения, коллекторы третьего и пятого транзисторов соединены соответственно с эмиттерами шестого, седьмого и восьмого, девятого транзисторов, коллектор шестого транзистора соединен с первым выводом пер-, вого резистора, коллектором восьмого транзистора и базами десятого и один «адцатого транзисторов, коллекторы которых подключены к общей шине, коллектор седьмого транзистора соединен с первым выводом второго резис тора, коллектором девятого транзистора и базами двенадцатого и тринадцатого транзисторов, коллекторы которых подключены к общей шине, эмиттеры одиннадцатого и тринадцатого транзисторов .подключены соответственно к первому и второму выходам триггера, эмиттеры десятого и двенадцатого транзисторов соединены соответственно через второй диод, восьмой резистор и через третий диод и девятый резистор с базами девятого и восьмого транзисторов и соотвеуственно через четвертый и пятый источники тока с шиной питания, базы шестого и седьмого транзисторов соединены соответственно с базами четырнадцатого и пятнадцатого тр,анзисторов, соответственно через шестой и седьмой источники тоКа - с шиной питания, соответственно через третий и четвертый резисторы - с эмиттерами шестнадцатого и семнадцатого транзисторов, коллекторы которых соедйненй с общей шиной, а базы - соответственно с первыми выводами пятого и шестого резисторов и соответственно с коллекторами пятнадцатого, восемнадцатого и четырнадцатого, девятнадцатого транзисторов, эмиттеры четырнадцатого и пятнадцатого транзисторов соединены с коллектороь второго транзистора, вторые выводы первого, второго, пятого, шестого резисторов, соединены с общей шиной, базы восем- надцатого и девятнадцатого транзисторов соединены соответственно с перв.ым и вторым информационными входами, эмиттеры - соответственно с эмиттерами двадцатого и двадцать первого транзисторов и соответственно с коллекторами двадцать второго и двадцать третьего транзисторов, эмиттеры которых подключены к коллектору.четвертого транзистора. Недостатком известного триггера является большая потребляемая мощность из-за повьшенного напряжения питания, связанного с применением в триггере трехярусньк переключателей тока. Цель изобретения - уменьшение потребляемой мощности. Для достижения поставленной цели в триггер, содержащий двадцать один транзистор, девять резисторов, три диода и семь источников тока, база первого транзистора подключена к тактовому входу, коллектор - к общей шине, эмиттер - к базам второго и третьего транзисторов и через первый источник тока - к шине питания, эмиттеры второго и третьего транзисторов соединены соответственно с эмиттерами четвертого и пятого транзисторов и соответственно через второй и третий источники тока с шиной питания, базы четвертого и пятого транзисторов соединены с входом опорного напряжения, коллекторы третьего и пятого транзисторов соединены соответственно с эмиттерами шестого, седьмого и восьмого, девятого транзисторов, коллектор шестого транзистора соединен с первым выводом первого резистора, .коллектором восьмого транзистора и базами д сятого и одиннадцатого транзисторов коллекторы которых подключены к обще шине, коллектор седьмого транзисто- ра соединен с первым выводом второг резистора, коллектором девятого тран зистора и базами двенадцатого и тринадцатого транзисторов, коллекторы которых подключены к общей шине, эмиттеры одиннадцатого и тринадцатого транзисторов подключены соответственно к первому и второму выходам триг ;;ера, эмиттеры десятого и двенадцатого транзисторов соединены со ответственно с базами девятого и во мого транзисторов и соответственно через четвертый и пятый источники т ка - с шиной питания, базы шестого и седьмого транзисторов, соединены соответственно с базами четырнадцатого и пятнадцатого транзисторов, с ответственно через шестой и седьмой источники тока - с шиной питания, соответственно через третий и четвёртый резисторы - с эмиттерами шестнадца- того и семнадцатого транзисторов, коллекторы которых соединены с общей шиной, а базысоответственно - с первыми выводами шестого и пятого резисторов и соответственно с коллекторами пятнадцатого, восемнадцатого и четырнадцатого, девятнадцатого транзисторов, эмиттеры четырнадцатого и пятнадцатого транзисторов соединены с коллектором второго транзистора, введены десятый резистор, четвертый диод, восьмой и девятый источники тока, коллекторы двадцато-. го и двадцать первого транзисторов подключены к общей шине, базы соответственно через седьмой и восьмой резисторы - к общей шине и к анодам соответственно первого, второго и третьего, четвертого диодов, катоды первого и третьего диодов подключены соответственно к первому и второму информационным входам, катоды второго и четвертого диодов - к базам соответственно девятого и восы мого транзисторов, э иттepы двадцатого и двадцать первого транзисторов подключены соответственно к базам девятнадцатого и восемнадцатого транзисторов и через соответственно восьмой и девятый источники тока к шине питания, дополнительные эмиттеры четырнадцатого,-пятнадцатого и эмиттеры восемнадцатого, девятнадцатого транзисторов соединены с коллектором -четвертого транзистора, вторые выводы первого и второго резисторов через девятый резистор, а вторые выводы пятого и шестого резисторов через десятый резистор соединены с общей шинойС27. На чертеже представлена принципиальная схема предложенного триггера; Триггер содержит двадцать один транзистор 1-21, десять резисторов 22-31, четыре диода 32-35 и девять источников тока 36-44, база первого транзистора 1 подключены к тактовому входу 45, коллектор - к общей шине 46, эмиттер - к базам второго и третьего транзисторов 2 и 3 и через первый источник тока 36 - к шине питания 47, эмиттеры второго и третьего транзисторов 2 и 3 соединены соответственно с эмиттерами четвертого и пятого транзисторов 4 и 5 и соот11ветственно через второй и третий источники тока 37 и 38 с шиной питания 47, базы четвертого-и пятого транзис торов 4 н 5 соединены с входом опорнбго напряжения 48, коллекторы треть его и пятого тра,н:зисторов 3 и 5 соединены соот ветственно с эмиттерами шестого, седьмого тн. восьмого, девятого траизисторов 6, 7 и 8, 9, кол лектор шестого транзистора.6 соеди;Нен с первым выводом первого резистр ра 22, коллекторам восьмого транзис;тора 8 и базами десятого и одиннад|цатого транзисторов 10 и 11, коллекторы которых подключены к общей шине 46, коллектор седьмого транзистора 7 соединен с первым вьгаодом второго резистора 23, коллектором девятого транзистора 9 и баэаг и двенадцатого и тринадцатого транзисторов 12 и l3, коллекторы которых псадключены к общей вине 46, эмиттеры одиннадцатого н тринадцатого транзисторов- 11 и 13 подклхгаены соответственяо к первому и второму выходам 49 и 50 триггера, эмиттеры десятого и двенадцатого транзисторов 10 и 12 соединены соответственно с базами девятого и восьмого транзисторов 9 и 8 и срответ- , ственно через четвертый и источники тока 39 и 40 с шиной питания, базы шестого и седьмого транзисторов 6 и 7 соединены соответственно с базами четырнадцатого и пятнадцатого транзисторов 14 и 15, соответственно через шестой и седьмой источники тока 41 и 42 - с вшной питанин 47, соответственно через трети и четвертый резисторы 24 и 25 - с эмиттерами шестнадцатого и семнадцатого транзисторов 16 и 17, коллекторы которых соединены с общей шиной 46, а базы - соответственно с первыми выводами пятого и шестого резисторов 26 и 27 и соответственно с коллекторами пятнадцатого, восемнадцатого и четырнадцатого, девят-. I надцатого транзисторов 15, 18 и 14, 19, эмиттеры четьфнадцатого и пятнад цатого.транзисторов 14 и 15 соединены с коллектором второго транзистора 2 коллекторы двадцатого и двадцать первого транзисторов 20 и.21 подключены к общей шине 46, базы соответственно через седьмой и восьмой ре-зисторы 28 и 29 - к общей шине 46 и к анодам соответственно первого, , второго и третьего, четвертого диот 36 дов 32, 33 и 34, 35, катоды первого и третьего диодов 32 и 34 подключены соответственно к первому и второму информационным входам 51 и 52, катоды второго и четвертого диодов 33 и 35 - к базам соответственно девятого и восьмого транзисторов 9 и 8, эмиттеры двадцатого и двадцать первого транзисторов 20 и 21 подключены, соответственно к базам девятнадцатого и восемнадцатого транзисторов 19 и 18 .и через соответственно восьМОЙ и девятый источники тока 43 и 44 к шине питания 47, дополнительные эмиттеры четырнадцатого, пятнадцатого и эмиттеры восемнадцатого, девятнадцатого транзисторов 14, 15, 18 и 19 соединены с коллектором четвертого транзистора 4, вторые выводы первого и второго резисторов 22 и 23 через девятый резистор 30, а вторые выводы пятого и шестого резисторов 26 и 27 через десятый резистор 31 соединены с общей шиной. , Триггер работает следующим образом. Логические уровни положим совместим1 в 1и с уровнями малосигнальной змиттерно связанной логики (МЭСЛ), совместимой по порогу переключения . с ЭСЛ, Высокий логический уровень 1, низкий логический уровень - О. Положим , О 1, где К -вход 51, С1 -вход 52. Диоды 32, 33 и 34, 35 в положительной логике реализуют логическую функцию конъюнкции. При подаче на катоды диодов 32-35 высоких потенциалов на базах транзисторов 20 и 21, соединенньк с анодами диодов 32-35, формируется высокий потенциал. Если к диодам 3235.подключены хотя бы один низкий потенциал, то низкий потенциал формируется и на их соединенных анодах. Пусть Q Г, Q 0, где Q-выход 49, Q -выход 50. Тогда на базе транзистора 20 будет формироваться высокий потенциал, а на базе транзистора 21 - низкий. Высокий потенциал будет через транзистор 20 передаваться на базу транзистора 19, а низкий потенциал через транзистор 21 будет подаваться на базу транзистора 18. Вследствие использования резисторов 24 и 25 потенциалы, подаваемые на базы транзисторов 15 и 14, смещены вниз относительно потенциалов, подаваемых на базы траНзисторов 18 и 19. Поэтому последние управляют переключением тока. При С 0, где С -вход 45, ток источника тока (ИТ) 37 будет протекать через транзистор 4 и транзистор 19. На базе транзистора 17 формируется низкий, а на базе транзистора 16 высокий потенциалы. Соответственно на промежуточном выходе (Q ), соединенном с базойтранзистора 14, фор- мируется 1,, а на промежуточном выходе (Q), соединенном с базой транзистора 15 О. При С 1 состояние выходов Q и Q не изменяется, Ппи С 0 состояние выходов Q и Q не изменяется, поскольку ток ИТ-38 управляется сигналами Q иО поданными на базы транзисторов 8 и 9 Поэтому состояние выходов Q и Q мо жёт изменяться лишь при С 1. При С 1 ток ИТ-38 протекает через транзистор 3. На базу транзистора 6 подан высокий потенциал (Q 1 а на базу транзистора 7 - низкий (). Поэтому ток протекает через транзистор 6. На базе транзисторов 12 и 13 устанавливается высокий потенциал, а на базе транзисторов 19 и 11- низкий, т.е. 0, . Пусть q 0, Q 1, тогда на базе транзистора 21 будет поддерживаться высокий, а на базе транзистора 20 - низкий потенциал. При С 0 ток ИТ-37 будет протекать через транзистор 18, поэтому . При С 1 ток ИТ-38 будет протекать через транзисторы 3 и 7, поэтому устанавливается Q i и . Таким образом, при К 1,, 3 1 состояние выходов изменяется на противоположное при поступлении с,инхросигналов 0-1. Положим k 1 j 0, пусть Q 1, Q 0. Тогда на базе транзистора 21 будет уста навливаться низкий, а на базе транг зистора 20 - высокий потенциалы. При С 0 ток ИТ-37 будет протекат через транзистор 19, тогда 1, . При С 1 ток ИТ-38 будет протекать через транзистор 16 и устанавл ивается Q 0 Q 1. Пусть Q 0, Q 1. Тогда на базах транзисторов 20 и 21 будут формироваться низкие потеницалы. Состояние выходов Q и Q не изменяет ся. При переключении С состояние выходов Q 0 и Q 1 возможно лишь при Q 1,Q 0, поскольку при q 0, Q 1, состояние выходов при с 1 устанавливается Q 1, q 0. Итак, при Q 0, Q 1 и К 1, У 0 устройство сохраняет информацию на выходах. Та-. КИМ образом, при К 1, О (У устанавливается состояние О 0,Q 1 при поступлении синхросигналов 0-1. Положим К 0, j 1. Пусть ,q 0. Тогда на базах транзисторов 20 и 21 будут поддерживат-ься низкие потеницалы. Состояние выходов Q и Q не изменяется. При переключении С состояние Q 1, б 0 возможно лишь при , q 1,поскольку при 0, 1, рК 0, состояние выходов при С 1 устанавливается Q 0, Q 1. Таким образом, при Q 1, Q 0, , 3 1, устройство сохраняет состояние выходов. Пусть Q 0, q 1, Тогда на базе транзистора 41 устанавливается низкий, а на базе транзистора 21 - высокий потенциалы. При С 0 ток ЙТ-37 протекает через транзисторы 4 и 18, поэтомуQ 0, . При С 1 ток ИТ-38 будет протекать через транзисторы 3 и 7, . поэтому Q 1, Q 0. Следовательно при К 0, 3 1, Q 1, Q 0 при переключении синхросигналов 0-1. Положим К 0, 3 0. При таких сигналах на базах транзисторов 20 и 21 формируются низкие потенциалы, которые передаются на базы транзисторов 18 и 19. Состояние выходов Q и Q , как было показано, не изменяется при q 0, Q 1 и и Q 0 и переключении синхросигнала, т.е. при К 0, j 0 устройство сранит информацию на выходах Q и Q . Итак .описанное устройство реализует функции О К -триггеру, причем .переключение выходов Q, и Q,. осхщ ствляется при переключении из О и-- -- - . Таким образом, уменьшается потребляемая мощность и уменьшается напряжение питания. Дополнительное снижение потребляемой мощности возможно при подаче на вход опорного напряжения сигнала, парофазного относительно сигнала синхронизации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Валиев К.А | |||

| и др | |||

| Микромощные интегральные схемы | |||

| М., Советское радио, 1975, с | |||

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Агапанян Т.М | |||

| и др | |||

| Интегральные триггеры устройств автоматики | |||

| М., Машиностроение, 1978, с | |||

| Способ изготовления струн | 1924 |

|

SU345A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| (прототип) | |||

Авторы

Даты

1984-12-30—Публикация

1983-05-10—Подача