Изобретение относится к импульсной техзгаке и может быть использовано ijpH построении генераторов тактового питания приборов с зарядовой связью, трехфазных распределителей.

По основному авт. св. № 784004 известно устройство, содержащее в каждом разряде триггер, прямой вьссод которого подключен к первому входу элемента И-НЕ, а также инвертор, вход которого подключен к входной шине, входы синхронизации триггеров пощапочены к входной шине, вторые входы элементов И-UE подсоединены к тегходу инвертора, а выход каждого элемента,И-НЕ соединен с инверсным входом триггера предыдущего разряда С 1

Недостатком известного устройства являются ограниченные функциональные возможности, так Kajc длительность, перекрытия выходных импульсов делителя на двух выходах делителя равна сумме длительности входного тактового импульса плкх: задержка переключения триггера по установочному входу, что исключае применение этого устройства.

Цель изобретения - расширение функциональных возможностей.

Указанная цель достигается тем , что в делитель ча:стоты на три, содержащий в каждом разряде триггер, прямой выход которого подключен к первому входу элемента И-НЕ, а также инвертор, вход которого подключен к входной шине, вход синхронизации триггеров подключены к входной шине, вторые входы элементов И НЕ подключены к выходу инвертора, а выход каждого элемента И-НЕ соедине с инверсным входом триггера предыдущего разряда, введены элемент И и в каждьй разряд элемент НЕ и дополнительный элемент И-НЕ, выход которого соединен с входом элемента НЕ, первый вход - с прямым выходом триггера этого же разряда, второй вход дополнителького элемента И-НЁ второго и третьего разряда - с инверсным выходом триггера предыдушего разряда, а второй вход дополнительного элемента И-НЕ первого разряда соединен с инверсным выходом триггера третьего разряда, прямой выход которого соединен с первым входом элемента И, второй вход которого подключен к прямому выходу триггера вто рого разряда.

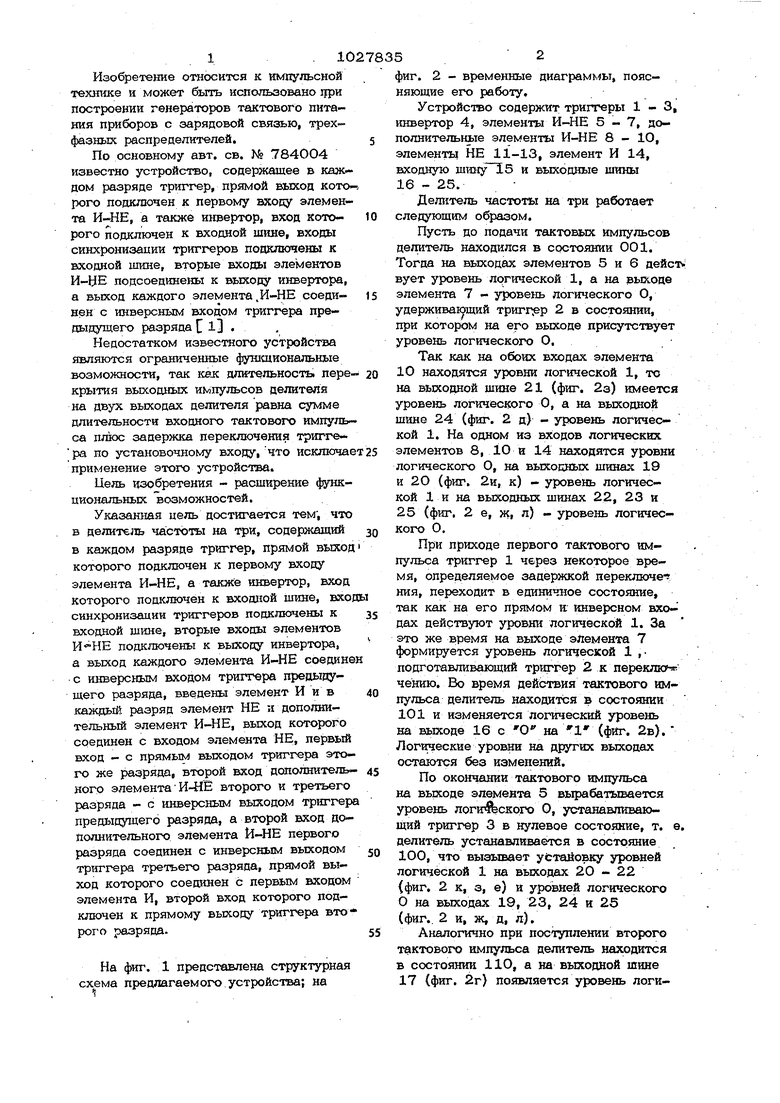

На фиг. 1 представлена структурная

схема предлагаемого устройства; на

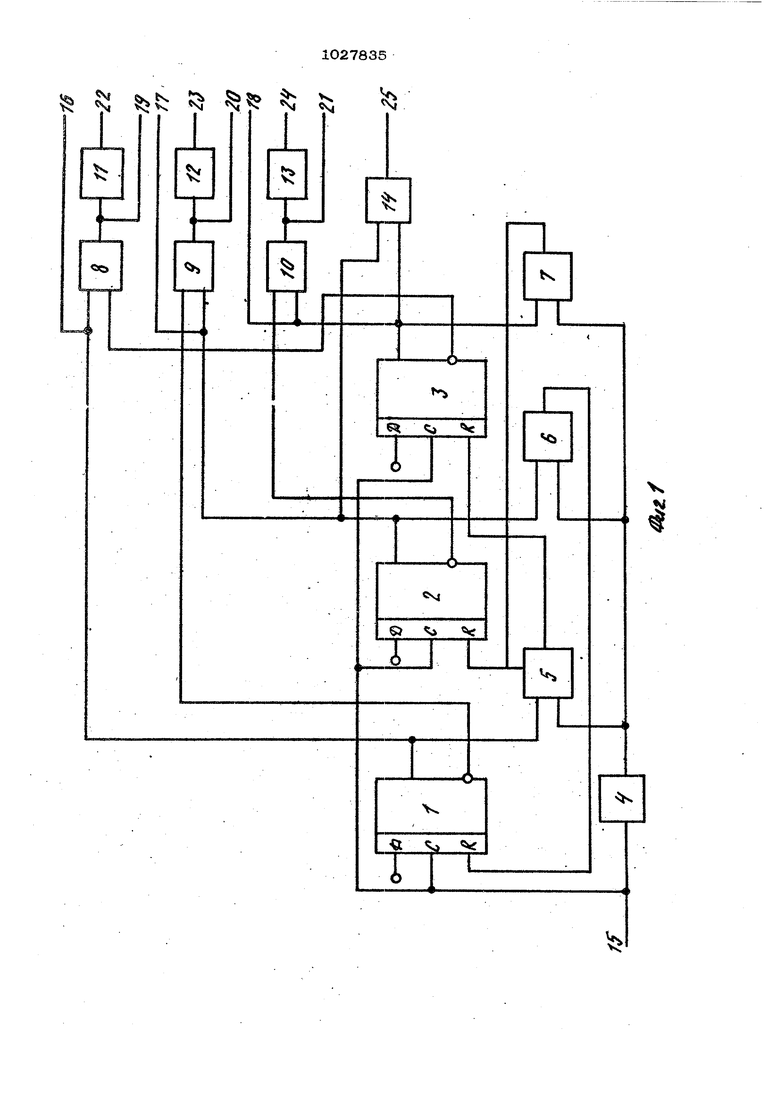

фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит триггеры 1-3 инвертор 4, элементы И-НЕ 5-7, дополнительные элементы И-НЕ 8 - 1О, элементы НЕ 11-13, элемент И 14, входную шинуТ 5 и выходные шины

16- 25.

Делитель частоты на три работает следующим образом.

Пусть до подачи т«1ктовых импульсов делитель находился в состоянии 001. Тогда на выходах элементов 5 и 6 деис вует уровень логической 1, а на выходе элемента 7 - уровень логического О, удерживагущий триггер 2 в состоянии, при котором на его выходе присутствует уровень логического О.

Так как на обоих входах элемента 10 находятся уровни логической 1, то на выходной шине 21 (фиг. 2з) имеетс уровень логического О, а на выходной шине 24 (фиг. 2 д) - уровень логической 1. На одном из входов логических элементов 8, 1О и 14 находятся уровни логического О, на выходных шинах 19 и 2О (фиг. 2и, к) - уровень логической 1 и на выходных шинах 22, 23 и 25 (фиг. 2 е, jK| л) - уровень логического О.

При приходе первого тактового импульса триггер 1 через некоторое время, определяемое задержкой переключе- ния, переходит в единичное состояние, так как на его прямом а инверсном входах действуют уровни логической 1. За это же время на выходе элемента 7 формируется уровень логической 1 ,подготавливающий трщгер 2 к переклку чению. Во время действия тактового импульса делитель находится в состоянии 101 и изменяется логический уровень на выходе 16 с О на (фиг. 2в). Логические уровни на других выходах остаются без изменений.

По окончании тактового импульса на выходе элемента 5 вырабатывается уровень логического О, устанавливающий триггер 3 в нулевое состояние, т. делитель устанавливается в состояние 1ОО, что вызьшает устайовку уровней логической 1 на выходах 20-22 (фиг. 2 к, 3, е) и уровней логического О на выходах 19, 23, 24 и 25 (фиг.. 2 и, ж, д, л).

Аналогично при поступлении второго тактового импульса делитель находится в состоянии 110, а на выходной шине

17(фиг. 2г) появляется уровень логической 1, по окончании второго тактового импульса делитель устанавливается в .состо5оше 010 и на выходных шинах 19, 21-и 23 (фиг. 2 и, 3, ж) устанавливаются уровни логической 1, а на выходных шинах 20, 22, 24 v 25 (фиг. 2 к, е, д, л) - уровни логического О, при поступлении третьего тактового импульса делитель находится в состоянии 011, а на выходных шинах IS и 25

(фиг, 26, л) nosmnsooTcfi уровни логической 1, по окончании третьего тактового импульса делитель гстававливается в coCTOfflrae О01, .появляются уровни логической 1 на ылходных шинах 19, 20 и 24 (фиг, 2 и, к. дУ и уровень логического О на выходных шинах 21, 22,23 и 25 (фиг. 2 а, е, ж, л), т. е. деш1тель устанавливается в начальное состояние.

Исходя из этого длительность перекрьг ия вьосодных импульсов на выходньрс шинах 16 - 18 (фиг, 2 в, г, б) равна длительности тактового импульса шпос задержка переключения триггера по установочному входу, что может быть использовано при построении генерато ров тактового питания приборов с зарядовой связью, Выходшыю ШЕНЫ 22 - 24 (фиг, -2 е, ж, д) формируют выходные импульсыг шгатефноЬть которых равна периоду следова1 ия кшдных нмщгльсов, а период равен трем я{эриодам входных импульсов. На выходных шнвах 19 - 21 2 и, к, з) форнируюфся выхошоые

импульсы, длительность которых равял двум периодам входных импуш сов, а период равен трем периодам входньос импульсов, что может быть использовано при построении трехфазных распределителей. На выходной шине 25 (фиг. 2л) по каждому третьему входному имйульсу появляется положительный импульс, длительность которого равна длительности входного импульса, что может быть использовано при построении пересчетных схем по модулю три./

Предлагаемый делитель на три может 6ыта выполнен в интегральном исполне НИИ.

Таким образом, за счет незначительных изменений электрической схемы делителя на три получена возможность использовать его при построении как генераторов тактового питания приборов с зарядовой связью, так и трехфазных распре целителей и пересче-шых схем по wod 3.

По сравнешоо с делителем на тра, выполенннрм ш Д)-триггерах согласно (Х)Т 11.34О9О2-78, предлагаемый делитель исключает одновремевдуто установку двух триггеров в состояние 1 прт отсутствии входного сигнала из-за появления помех по цепям питания. Это обеспечивает всыдачу выходнся о сигнала только по одному из вносодов в зависимости от количества входных импульс ж, поступивших на вход делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на три | 1979 |

|

SU784004A1 |

| Преобразователь отношения двух напряжений в код | 1989 |

|

SU1695501A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1732465A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036555C1 |

| Шкальный индикатор | 1989 |

|

SU1647262A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ДЛЯ КОМПЬЮТЕРНОЙ РЕГИСТРАЦИИ СИГНАЛА ИЗОБРАЖЕНИЯ ИНТЕРФЕРОГРАММ | 2012 |

|

RU2489806C1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| Селектор импульсов по длительности | 1981 |

|

SU1001458A2 |

ДЕЛИТЕЛЬ ЧАСТОТЫ НА ТРИ по авт. св. № 784004, о т л и ч а ю ш U и с я тем, что, с целью расширения функционалышх возможностей, в него введены элемент И и в кажоый разряд элемент НЕ в цополшстельный элемент И-НЕ, выход которого соедт1енс входом элемента НЕ, а Первый вход с прямым выходом триггера этого же разряда, второй вход дополнительноххэ элемента И-НЕ второго и третьего разряда - с инверсным выходом триггера предыдущего разряда, а второй вход дополнительного элемента И-НЕ первого разряда соединен с инверсным выходом триггера третьего разряда, прямой выхрд которого соединен с первым входом элемента И,; второй вход которого под клгочен к прямому выхощ триггера второго разряда.

N

«о

ggi ; V

I

X

S) «X

t ix

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Делитель частоты на три | 1979 |

|

SU784004A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-07-07—Публикация

1982-03-17—Подача