Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен делитель частоты [1] содержащий шину входной частоты, счетчик импульсов и дешифратор, входы которого соединены с соответствующими выходами счетчика импульсов, сумматор по модулю два, первый вход которого соединен с шиной входной частоты, второй вход с выходом дешифратора, а выход подключен к счетному входу счетчика импульсов.

Указанный делитель частоты позволяет получать любой коэффициент деления в диапазоне от 2N-1 до 2N, где N число разрядов счетчика импульсов.

Недостатком этого делителя частоты является низкая надежность функционирования, так как использование счетчика импульсов, работающего в позиционном двоичном коде, приводит к существенному искажению его содержимого.

Недостатком данного делителя частоты является также невозможность получения коэффициентов деления менее 2N-1.

Известен делитель частоты [2] содержащий N-разрядный регистр, состоящий из триггеров, блок запуска, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и блока анализа четности, включающий в себя соединенные последовательно (N-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Соответствующие входы блока анализа четности соединены с прямыми выходами триггеров, начиная с второго N-разрядного регистра и с управляющей шиной устройства. Первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с прямым выходом триггера первого разряда N-разрядного регистра. Каждый разряд блока запуска содержит первый и второй элементы совпадения, первые входы которых, кроме первого разряда, соединены с выходом первого элемента совпадения предыдущего разряда. Первые входы элементов совпадения первого разряда соединены с шиной входной частоты. Выход первого элемента совпадения N-го разряда соединен с шиной выходной частоты. Выход второго элемента совпадения каждого разряда соединен со счетным входом триггера соответствующего разряда N-разрядного регистра. Прямой и инверсный выходы триггера каждого разряда N-разрядного регистра с второго по (N-1)-й соединены с вторыми входами соответственно второго и первого элементов совпадения последующего разряда блока запуска. Прямой и инверсный выходы блока анализа четности соединены с вторыми входами соответственно первого и второго элементов совпадения второго разряда блока запуска. Вторые входы первого и второго элементов совпадения первого разряда запуска соединены соответственно с инверсным и прямым выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом триггера второго разряда N-разрядного регистра.

Указанный делитель частоты позволяет получать любой коэффициент деления в диапазоне от 2N-1 до 2N.

Недостатком данного делителя частоты является сложность, связанная с необходимостью использования двухступенчатых счетных триггеров, содержащих большое число логических элементов.

Недостатком данного делителя частоты является также невозможность получения выходной частоты с коэффициентом деления, менее 2N-1.

Наиболее близким к рассматриваемому устройству по технической сущности является делитель частоты в виде счетчика импульсов в коде Грея [3] содержащий управляющий D-триггер, в каждом разряде D-триггер и первый элемент совпадения, в каждом разряде, кроме последнего, второй элемент совпадения и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. В каждом разряде, кроме последнего, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с прямым выходом D-триггера данного разряда, тактовый вход которого соединен с выходом второго элемента совпадения данного разряда, D-вход с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ данного разряда, а инверсный выход с первым входом первого элемента совпадения последующего разряда, второй вход которого соединен с выходом первого элемента совпадения данного разряда. Первый вход второго элемента совпадения соединен с вторым входом первого элемента совпадения данного разряда. В каждом разряде, кроме двух последних, прямой выход D-триггера и второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с вторым входом второго элемента совпадения и выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда. Тактовый вход D-триггера последнего разряда соединен с инверсным выходом первого элемента совпадения предпоследнего разряда, прямой выход с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ предпоследнего разряда, а D-вход с выходом первого элемента совпадения данного разряда и выходной шиной. Прямой и инверсный выходы управляющего D-триггера соединены соответственно с вторым входом второго и первым входом первого элементов совпадения первого разряда, D-вход соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда, а тактовый вход с входной шиной и вторым входом первого элемента совпадения первого разряда.

Указанный счетчик импульсов может использоваться в качестве делителя частоты с коэффициентом деления 2N, где N число разрядов.

Недостатком данного устройства являются ограниченные функциональные возможности в связи с отсутствием возможности получения коэффициентов деления менее 2N.

Цель изобретения расширение функциональных возможностей достигается путем обеспечения возможности задания любого целого коэффициента деления от 1 до 2N при сохранении работы счетчика в одновременном двоичном коде (коде Грея).

Используемая в рассматриваемом устройстве совокупность признаков позволяет расширить функциональные возможности делителя частоты путем обеспечения возможности задания любого целого коэффициента деления от 1 до 2N при сохранении работы счетчика в однопеременном двоичном коде за счет соответствующей настройки дешифратора на заданный коэффициент деления и обеспечения переключения счетчика импульсов от состояния, соответствующего заданному коэффициенту деления, до переполнения во время паузы между счетными импульсами на повышенной частоте, формируемой управляемым генератором.

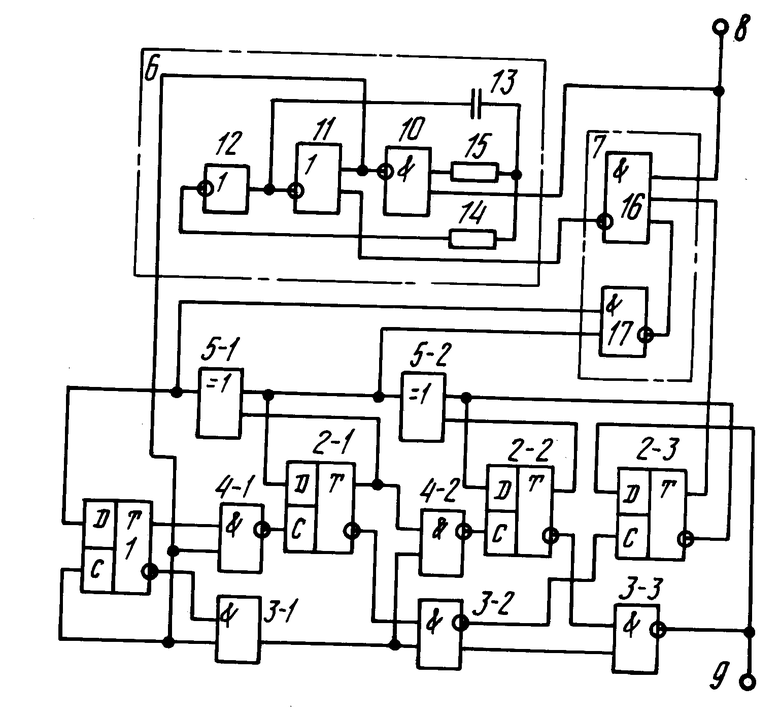

На чертеже приведена электрическая функциональная схема трехразрядного делителя частоты с коэффициентом деления, равным 5.

Делитель частоты содержит управляющий D-триггер 1, в каждом разряде D-триггер 2-k, где k 1,2,3 номер разряда, и первый элемент 3-k совпадения, в каждом разряде, кроме последнего, второй элемент 4-k совпадения и элемент 5-k ИСКЛЮЧАЮЩЕЕ ИЛИ. Делитель содержит также управляемый генератор 6, дешифратр 7, входную шину 8, выходную шину 9. Управляемый генератор 6 содержит элемент 10 И-НЕ, элемент 11 ИЛИ-НЕ, инвертор 12, конденсатор 13, резистор 14 и дополнительный резистор 15. Дешифратор 7 содержит первый 16 и второй 17 элементы И-НЕ.

D-вход управляющего триггера 1 соединен с выходом элемента 5-1 ИСКЛЮЧАЮЩЕЕ ИЛИ, а тактовый вход с первыми входами элементов 3-1 и 4-1 совпадения, вторые входы которых соединены соответственно с инверсным и прямым выходами управляющего триггера 1. Инверсный выход элемента 4-1 совпадения соединен с тактовым входом триггера 2-1, D-вход которого соединен с выходом элемента 5-2 ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом элемента 5-1 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с прямым выходом триггера 2-1 и первым входом элемента 4-2 совпадения, второй вход которого соединен с прямым выходом элемента 3-1 совпадения и с вторым входом элемента 3-2 совпадения, первый вход которого соединен с инверсным выходом триггера 2-1. Инверсный выход элемента 4-2 совпадения соединен с тактовым входом триггера 2-2, D-вход которого соединен с инверсным выходом триггера 2-3 и с вторым входом элемента 5-2 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с прямым выходом триггера 2-2, инверсный выход которого соединен с первым входом элемента 3-3 совпадения, второй вход которого соединен с прямым выходом элемента 3-3 совпадения, инверсный выход которого соединен с тактовым входом триггера 2-3, D-вход которого подключен к инверсному выходу элемента 3-3 совпадения и к выходной шине 9. Информационный вход управляемого генератора 6 подключен к входной шине 8, выход к тактовому входу управляющего триггера 1, а управляющий вход к выходу дешифратора 7, информационные входы которого соединены с входной шиной 8, с выходами элементов 5-1 и 5-2 ИСКЛЮЧАЮЩЕЕ ИЛИ и с прямым выходом триггера 2-3 соответственно.

Информационный вход управляемого генератора 6 соединен с первым входом элемента 10 И-НЕ, второй вход которого через последовательно соединенные резисторы 15 и 14 подключен к выходу инвертора 12, а через последовательно соединенные резистор 15 и конденсатор 13 к входу инвертора 12 и к выходу элемента 11 ИЛИ-НЕ, первый вход которого соединен с управляющим входом управляемого генератора 6, а второй вход с выходами элемента 10 И-НЕ и управляемого генератора 6.

Выход дешифратора 7 соединен с выходом первого элемента 16 И-НЕ, входы которого соединены соответственно с входной шиной 8, прямым выходом триггера 2-3 и выходом второго элемента 17 И-НЕ, входы которого соединены с выходами соответственно элементов 5-1 и 5-2 ИСКЛЮЧАЮЩЕЕ ИЛИ.

Триггеры 1, 2-1, 2-2, 2-3 выполнены на элементах ИЛИ-НЕ микросхем 564ЛЕ5 по известной схеме. Элементы 3-1, 3-2, 3-3, 4-1, 4-2 совпадения, элементы 10, 17 И-НЕ и инвертор 12 выполнены на микросхемах 564ЛА7, прямые выходы элементов совпадения организованы путем установки дополнительных инверторов. Элемент 16 И-НЕ выполнен на микросхеме 564ЛА9. Элементы 5-1 и 5-2 выполнены на микросхеме 564ЛП2. Элемент 11 ИЛИ-НЕ выполнен на микросхеме 564ЛЕ5. В качестве резистора 14 использован резистор С2-33Н-0,125-10 кОм±5% в качестве резистора 15 резистор С2-33Н-0,125-100 кОм ±5% в качестве конденсатора 13 конденсатор К10-17с-а-М750-510 пФ-В.

Логические элементы 1,2,3,4,5,10,11, 12,16,17 могут быть выполнены на КМОП микросхемах других серий, например серий К561, 1526, 1564. В качестве резисторов 14 и 15 могут использоваться резисторы типа С2-23 и другие, в качестве конденсатора 13 конденсатор типа К10-47 и другие.

Делитель частоты работает следующим образом.

В исходном состоянии триггеры 2-1, 2-2, 2-3 находятся в состоянии логического "0", на выходах элементов 5-1 и 5-2 ИСКЛЮЧАЮЩЕЕ ИЛИ и на входной шине 8 присутствует уровень логической "1", на выходе элемента 17 И-НЕ и на прямом выходе триггера 2-3 уровень логического "0". Следовательно, элемент 16 И-НЕ дешифратора 7 находится в состоянии логической "1", на управляющем входе генератора 6 и на выходной шине 9 присутствует уровень логической "1". Элемент 11 ИЛИ-НЕ находится в состоянии логического "0", а инвертор 12 в состоянии логической "1". Уровень логической "1" с выхода инвертора 12 через резисторы 14 и 15 поступает на первый вход элемента 10 И-НЕ. Конденсатор 13 заряжен до напряжения источника питания с выхода инвертора 12. На выходе элемента 10 И-НЕ, на выходе генератора 6, на первых входах элементов совпадения 3-1 и 4-1 и на тактовом входе управляющего триггера 1 присутствует уровень логического "0". Триггер 1 установлен в состояние логической "1" уровнем логической "1", поступающим на его D-вход с выхода элемента 5-1 ИСКЛЮЧАЮЩЕЕ ИЛИ. При этом на втором входе элемента совпадения 3-1 присутствует уровень логического "0", а на втором входе элемента совпадения 4-1 уровень логической "1".

При поступлении на входную шину 8 первого счетного импульса в виде уровня логического "0" элемент 10 И-НЕ генератора 6 устанавливается в состояние логической "1". Уровень логической "1" с выхода генератора 6 поступает на тактовый вход управляющего триггера 1, запрещая его переключение сигналом на D-входе, и на первые входы элементов 3-1 и 4-1 совпадения, переводя элемент 4-1 совпадения в состояние логического "0" и разрешая переключение триггера 2-1 в состояние логической "1" сигналом, поступающим на его D-вход с выхода элемента 5-2 ИСКЛЮЧАЮЩЕЕ ИЛИ. После переключения триггера 2-1 элемент 5-1 ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается в состояние логического "0", а элемент 17 И-НЕ в состояние логической "1". Состояние элемента 16 И-НЕ не изменяется. Счетный импульс заканчивается, на входной шине 8 устанавливается уровень логической "1", элемент 10 И-НЕ переходит в состояние логического "0" сигналом по D-входу. При этом на втором входе элемента совпадения 3-1 устанавливается уровень логической "1", а на втором входе элемента совпадения 4-1 уровень логического "0".

Второй счетный импульс проходит через элементы 3-1 и 4-2 совпадения, вызывая переключение триггера 2-2 в состояние логической "1" сигналом, поступающим на его D-вход с инверсного выхода триггера 2-3. При этом на выходе элемента 5-2 ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается уровень логического "0", а на выходе элемента 5-1 ИСКЛЮЧАЮЩЕЕ ИЛИ уровень логической "1". По окончании второго счетного импульса триггер 1 устанавливается в состояние логической "1".

Третий счетный импульс вызывает переключение триггера 2-1 в состояние логического "0".

Четвертый счетный импульс проходит через элементы 3-1 и 3-2 совпадения на тактовый вход триггера 2-3, вызывая его переключение в состояние логической "1" сигналом, поступающим на его D-вход с инверсного выхода элемента совпадения 3-3. При этом на выходах элементов 5-1 и 5-2 ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается уровень логической "1". Элемент 17 И-НЕ устанавливается в состояние логического "0".

Пятый счетный импульс вызывает переключение триггера 2-1 в состояние логической "1". На выходе элемента 5-1 ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается уpовень логического "0", элемент И-НЕ 17 устанавливается в состояние логической "1". Поэтому по окончании пятого счетного импульса, когда на входной шине 8 устанавливается уровень логической "1", элемент И-НЕ переходит в состояние логического "0".

Уровень логического "0" с выхода дешифратора 7 поступает на управляющий вход генератора 6 и далее на первый вход элемента 11 ИЛИ-НЕ, устанавливая его в состояние логической "1". Положительный перепад напряжения с выхода элемента 11 ИЛИ-НЕ через конденсатор 13 передается в точку соединения резисторов 14 и 15, устанавливая там напряжение, в два раза превышающее напряжение питания. Резистор 15 выполняет функцию защиты входа элемента 10 И-НЕ от повышенного напряжения совместно с диодом схемы защиты входа. Одновременно инвертор 12 устанавливается в состояние логического "0".

В момент окончания пятого счетного импульса на выходе элемента 10 И-НЕ, а следовательно, и на тактовом входе управляющего триггера 1 формируется уровень логического "0",разрешающий его переключение в состояние логического "0" по D-входу уровнем логического "0" с выхода элемента 5-1 ИСКЛЮЧАЮЩЕЕ ИЛИ. Одновременно происходит перезаряд конденсатора 13 управляемого генератора 6 через резистор 14 уровнем логического "0" с выхода инвертора 12 и уровнем логической "1" с выхода элемента 12 ИЛИ-НЕ. При этом напряжение на первом входе элемента 10 И-НЕ уменьшается. По достижении указанным напряжением порога срабатывания управляемый генератор 6 переключается. На выходе элемента 10 И-НЕ устанавливается уровень логической "1", который поступает на тактовый вход триггера 2-2 и вызывает его переключение в состояние логического "0".

Одновременно происходит перезаряд конденсатора 13 уровнем логической "1" с выхода инвертора 12 и уровнем логического "0" с выхода элемента 11 ИЛИ-НЕ. Напpяжение на первом входе элемента 10 И-НЕ повышается. По достижении указанным напряжением порога срабатывания на выходе элемента 10 И-НЕ устанавливается уровень логического "0", который вызывает переключение триггера 1 в состояние логической "1". Поэтому следующий импульс генератора 6 вызывает переключение триггера 2-1 в состояние логического "0". В паузе управляющий триггер 1 переключается в состояние логического "0". Поэтому очередной импульс генератора 6 проходит через элементы 3-1, 3-2, 3-3 совпадения, а также на выходную шину 9, вызывая переключение триггера 2-3 в состояние логического "0". При этом на выходах элементов 5-1 и 5-2 ИСКЛЮЧАЮЩЕЕ ИЛИ устанавливается уровень логической "1" и элемент 17 И-НЕ переводится в состояние логического "0", а элемент 16 И-НЕ в состояние логической "1".

Уровень логической "1" с выхода дешифратора 7 поступает на управляющий вход генератора 6, подтверждает состояние логического "0" элемента 11 ИЛИ-НЕ и состояние логической "1" инвертора 12 и запрещает дальнейшее их переключение. Конденсатор 13 перезаряжается, напряжение на первом входе элемента 10 И-НЕ возрастает. По достижении указанным напряжением порога срабатывания на выходе элемента 10 И-НЕ устанавливается уровень логического "0", триггер 1 переключается в состояние логической "1".

Делитель частоты вернулся в исходное состояние. Шестой счетный импульс, поступающий на входную шину 8, начинает новый цикл работы.

Таким образом, описание работы подтверждает нормальное функционирование делителя частоты и расширение функциональных возможностей путем обеспечения возможности задания любого целочисленного коэффициента деления от 1 до 2N, где N число разрядов, при сохранении работы в однопеременном коде за счет соответствующей настройки дешифратора на заданный коэффициент деления и обеспечения переключения счетчика импульсов от состояния, соответствующего заданному коэффициенту деления, до переполнения во время паузы между счетными импульсами на повышенной частоте, формируемой управляемым генератором.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1991 |

|

RU2036550C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2037958C1 |

| ТРОИЧНОЕ СЧЕТНОЕ УСТРОЙСТВО | 2002 |

|

RU2231921C2 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2042268C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2110146C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2237354C2 |

| ТРЕХСТАБИЛЬНЫЙ СЧЕТНЫЙ ТРИГГЕР (ВАРИАНТЫ) | 1993 |

|

RU2093955C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1993 |

|

RU2040111C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

Применение: устройство относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления. Сущность изобретения: устройство содержит управляющий D-триггер 1, в каждом разряде D-триггер 2-k, где k=1,2,3 - номер разряда, элементы совпадения 3-k, 4-k, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 5-k, управляемый генератор 6, дешифратор 7, элементы И-НЕ 10,16,17, элемент ИЛИ-НЕ 11, инвертор 12, конденсатор 13, резисторы 14,15, входную шину 8, выходную шину 9 с соответствующими связями. 1 з.п. ф-лы, 1 ил.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1982 |

|

SU1101159A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-05-27—Публикация

1991-06-05—Подача