О

ю ел

ел

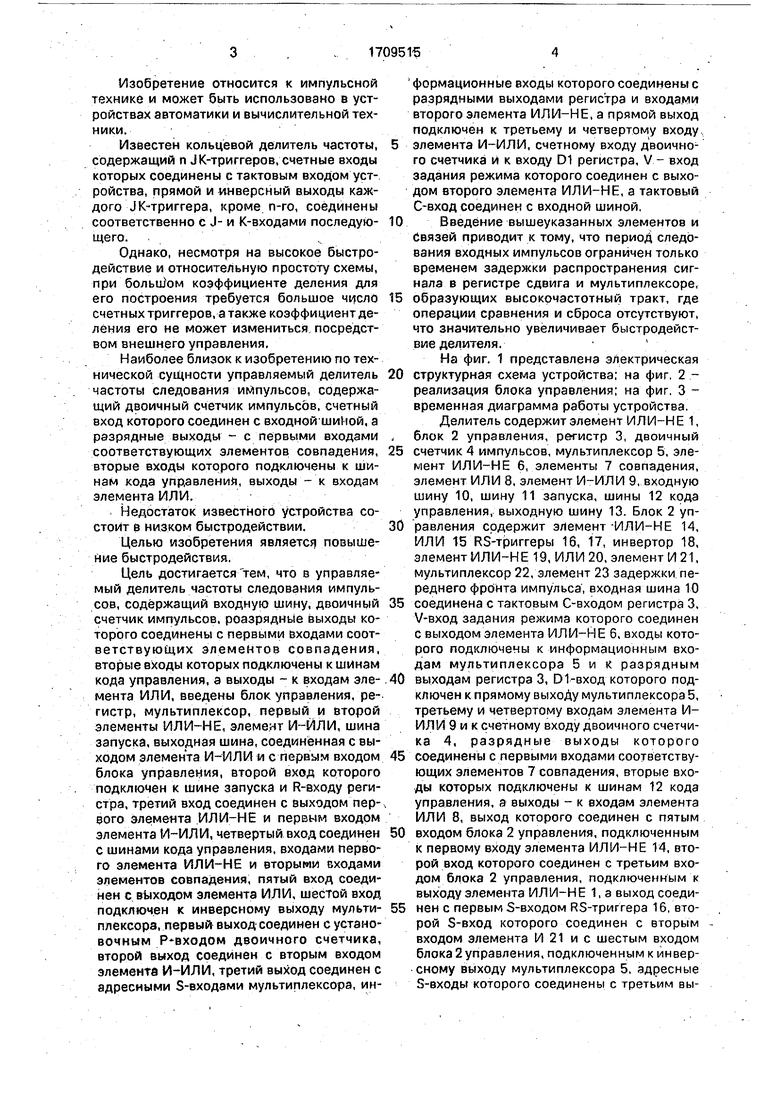

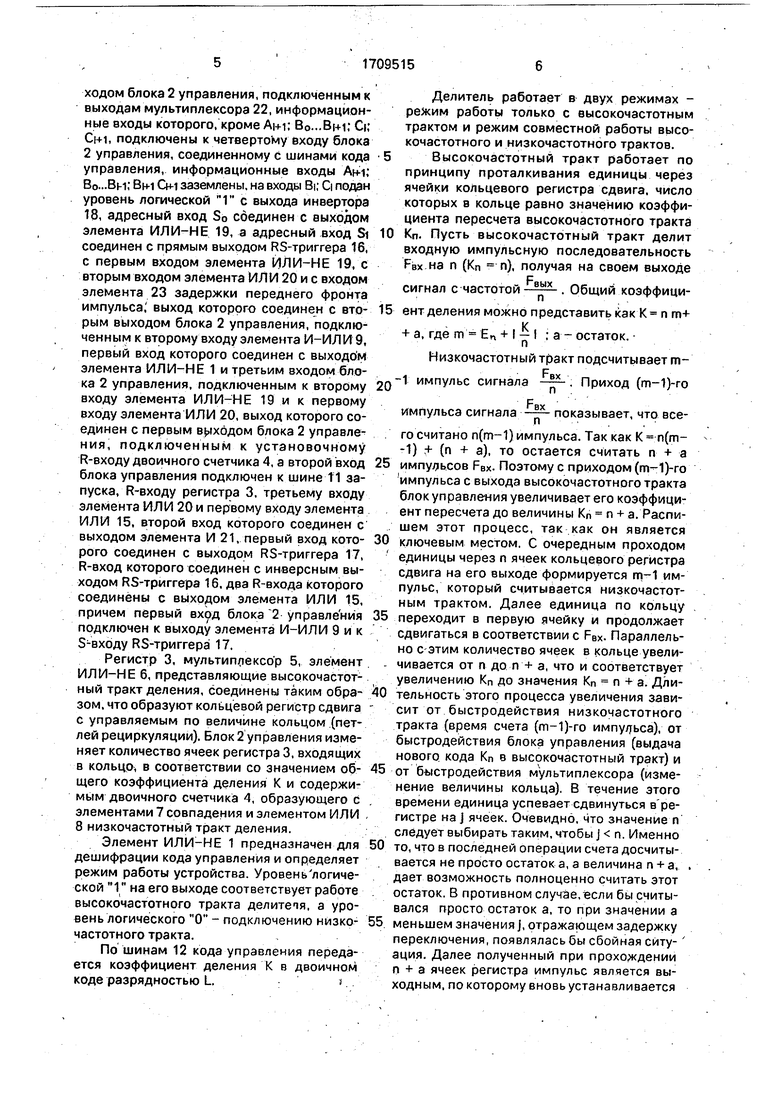

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Известен кольцевой делитель частоты, содержащий п JK-триггеров, счетные входы которых соединены с тактовым входом устройства, прямой и «нверсный выходы каждого ЛК триггера, кроме п-го, соединены соответственно с J- и К-входами последующего. Однако, несмотря на высокое быстродействие и относительную простоту схемы, при большом коэффициенте деления для его построения требуется большое щели счетных триггеров, а также коэффициент деления его не может измениться, посредством внешнего управления. Наиболее близок к изобретению по технической сущности управляемый делитель частоты следования импульсов, содержащий двоичный счетчик импульсов, счетный вход которого соединен с входной шиИой, а разрядные выходы - с первыми входами соответствующих элементов совпадения, вторые входы которого подключены к шинам кода управлений, выходы - к входам элемента ИЛИ. Недостаток известного устройства состоит в низком быстродействии. Целью изобретения является повышение быстродействия. Цель достигается тем, что в управляемый делитель частоты следования импульсов, содержащий входную шину, двоичный счетчик импульсов, роазряднУе йыходы которого соединены с первыми входами соответствующих элементов совпадения, вторые входы которых подключены к шинам кода управления, а выходы - к входам элемента ИЛИ, введены блок управления, регистр, мультиплексор, первый и второй элементы ИЛИ-НЕ, элемент , шина запуска, выходная шина, соединённая с выходом элемента И-ИЛИ и с первым входом блока управления, второй вход которого подключен к шине запуска и R-входу регистра, третий вход соединен с выходом переого элемента ИЛИ-НЕ и первым входом элемента И-ИЛИ, четвертый вход соединен с шинами кода управления, входами первого элемента ИЛИ-НЕ и вторыми входами элементов совпадения, пятый вход соединен с BtixoAOM элемента ИЛИ, шестой вход подключен к инверсному выходу мультиплексора, первый выход соединен с установочным Р входом двоичного счетчика, второй выход соединен с вторым входом элемента И-ИЛИ, третий выход соединен с адресными 5-входами мультиплексора, информационные входы которого соединены с разрядными выходами регистра и входами второго элемента ИЛИ-НЕ, а прямой выход подключен к третьему и четвертому входу элемента И-ИЛИ, счетному входу двоичного счетчика И к входу D1 регистра, V - вход задания режима которого соединен с выходом второго элемента ИЛИ-НЕ, а тактовый С-вход соединен с входной шиной, Введение вышеуказанных элементов и Связей приводит к тому, что периоД следования входных импульсов ограничен только временем задержки распространения сигнала в регистре сдвига и мультиплексоре, образующих высокочастотный тракт, где операции сравнения и сброса отсутствуют, что значительно увеличивает быстродействие делителя. На фиг. 1 представлена электрическая структурная схема устройства; на фиг, 2 реализация блока управления; на фиг, 3 временная диаграмма работы устройства. Делитель содержит элемент ИЛИ-НЕ 1, блок 2 управления, регистр 3, двоичный счетчик 4 импульсов, мультиплексор 5, элемент ИЛИ-НЕ 6, элементы 7 совпадения, элемент ИЛИ 8, элемент И-ИЛИ 9, входную шину 10, шину 11 запуска, шины 12 кода управления, выходную шину 13. Блок 2 управления содержит элемент -ИЛИ-НЕ 14, ИЛИ 15 RS-триггеры 16, 17, инвертор 18, элемент ИЛИ-НЕ 19, ИЛИ 20, элемент И 21, мультиплексор 22, элемент 23 задержки переднего фронта импульса, входная шина 10 соединена с тактовым С-входом регистра 3, V-вход задания режима которого соединен с выходом элемента ИЛИ-НЕ 6, входы которого подключены к информационным входам мультиплексора 5 и к разрядным выходам регистра 3, 01-вход которого подключен к прямому выхоДу мультиплексора 5, третьему и четвертому входам элемента ИИЛИ 9 и к счетному входу двоичного счетчика 4, разрядные выходы которого соединены с первыми входами соответствующих элементов 7 совпадения, вторые входы которых подключены к шинам 12 кода управления, а выходы - к входам элемента 8, выход которого соединен с пятым входом блока 2 управления, подключенным к первому входу элемента ИЛИ-НЕ 14, второй вход которого соединен с третьим входом блока 2 управления, подключенным к выходу элемента ИЛИ-НЕ 1, а выход соединен с первым S-входом RS-тригТера 16, второй S-вход которого соединен с вторым входом элемента И 21 и с шестым входом блока 2управления, подключенным к инверсному выходу мультиплексора 5, адресные S-входы которого соединены с третьим выходом блока 2 управления, подключенным к выходам мультиплексора 22, информационные входы которого, кроме AI+I; Bo...Bi4i, Ск С|+1, подключены к четвертому входу блока 2 управления, соединенному с шинами кода управления, информационные входы Аи, Во...Вц; Ви-1 Сн-1 заземлены, на входы Bi; О подан уровень логической 1 с выхода инвертора 16i адресный вход So соединен с выходом элемента ИЛИ-НЕ 19, а адресный вход Si соединен с прямым выходом RS-триггера 16, с первым входом элемента ИЛИ-НЕ 19, с вторым входом элемента ИЛИ 20 и с входом элемента 23 задержки переднего фронта импульса. выход которого соединен с вторым выходом блока 2 управления, подключенным к второму входу элемента И-ИЛИ 9, первый вход которого соединен с выходом элемента ИЛИ-НЕ 1 и третьим входом блока 2 управления, подключенным к второму входу элемента ИЛИ-НЕ 19 и к первому входу элемента ИЛИ 20, выход которого соединен с первым в 1х6дом блока 2 управления, подключенным к установочному R-входу двоичного счетчика 4, а второй вход блока управления подключен к шине Т1 запуска, R-входу регистра 3, третьему входу элемента ИЛИ 20 и первому входу элемента ИЛИ 15, второй вход которого соединен с выходом элемента И 21, первый вход которого соединен с выходом RS-триггера 17, R-аход которого соединен с инверсным выходом RS-триггера 16, два R-входа которого соединены с выходом элемента ИЛИ 15, причем первый вход блока 2 управления подключен к выходу элемента И-ИЛИ 9 и к S-вxdдy RS-триггера 17.

Регистр 3, мультип/1ексор 5, элемент ИЛИ-НЕ 6, представляющие высокочастотный тракт деления, соединены таким образом, что образуют кольцевой регистр сдвига с управляемым по величине кольцом (петлей рециркуляции). Блок 2 управления изменяет количество ячеек регистра 3, входящих в кольцо, в соответствии со значением общего коэффициента деления К и содержимь1м двоичного счетчика 4, образующего с элементами 7 совпадения и элементом ИЛИ 8 низкочастотный тракт деления.

Элемент ИЛИ-НЕ 1 предназначен для дешифрации кода управления и определяет режим работы устройства. Уровеньлогической 1 на его выходе соответствует работе высокочастотного тракта делитепя, а уровень логического О - подключению низкочастотного тракта.

По шинам 12 кода управления передается коэффициент деления К в двоично/ коде разрядностью L.«

Делитель работает в двух режимах режим работы только с высокочастотным трактом и режим совместной работы высокочастотного и низкочастотного трактов.

5Высокочастотный тракт работает по

принципу проталкивания единицы через ячейки кольцевого регистра сдвига, число которых в кольце равно значению коэффициента пересчета высокочастотного тракта

10 Кп. Пусть высокочастотный тракт делит входную импульсную последовательность FBX на п (Кп п), получая на своем выходе

сигнал с частотой . Общий коэффициент деления можно представить как К п m-iК+ а, где m + I - I ; а - остаток.

Низкочастотный тракт подсчитьшает импульс сигнала -. Приход (m-l)-ro

вх

импульса сигнала

показывает, что всего считано n(m-1) импульса. Так как К n(m-1) (п + а), то остается считать п + а

импуу ьсов FBX. Поэтому с приходом (т--1)-го импульса с выхода высокочастотного тракта блок управления увеличивает его коэффициент пересчета до величины Кп п + а. Распишем этот процесс, так как он является

ключевым местом. С очередным проходом единицы через п ячеек кольцевого регистра сдвига на его выходе формируется т-1 импульс, который считывается низкочастотным трактом. Далее единица по кольцу

переходит в первую ячейку и продолжает сдвигаться в соответствии с FBX. Параллельно с этим количество ячеек в кольце увеличивается от п до п + а, что и соответствует увеличению Кп до значения Кп п + а. Длительность этого процесса увеличения зависит от быстродействия низкочастотного тракта (время счета (m-l)-ro импу/уьса), от быстродействия блока управления (выдача нового кода Кп в высокочастотный тракт) и

от быстродействия мультиплексора (изменение величины кольца). В течение этого времени единица успевает сдвинуться врегистре на j ячеек. Очевидно, что значение п следует выбирать таким, чтобы j п. Именно

то, что в последней операции счета досчитывается не просто остаток а, а величина п + а, , ает возможность полноценно считать этот

остаток. В противном случае.вели бы считывался просто остаток а, то при значении а

меньшем значения j, отражающем задержку переключения, появлялась бы сбойная ситуция. Далее полученный при прохождении П + а ячеек регистра импульс является выодным, по которому вновь устанавливается

Kn пи процедура повторяется в описанном выше порядке/Причем при изменении Кпот значения п + а до значения п, требующего определенного времени, из-за п j не возникает сбойных ситуаций. Если общий коэффициент деления меньше 2-0 (К 2п), тогда деление выполняется только высокочастотным трактом.

Рассмотрим подробнее величину п, которая является минимальным значением коэффициента пересчета Кп высокочастотного тракта. Пусть п 2, где i - число, принимающее только целые значения. Тогда К 2{т-1) + (2 + а). В результате разности быстродействий высокочастотного и низкочастотного трактов за время, необходимое для считывания низкочастотным трактом (т-1)-го импульса с выхода высокочастотного тракта и увеличения в последнем коэффициента пересчета Кп до значения п + а, единица в регистре 3 под действием FBX успеет сдвинуться на j ячеек, Поэтому значение п 2 следует выбирать таким, чтобы } п или j 2 . Таким образом величина i определяет число 2. показывающее, во сколько раз максимально допустимая входная частота (быстродействие) высокочастотного тракта рмакс р мак больше максимально допустимой входной частоты (быстродействия) низкочастотного тракта ,

с макс

Причем 2 . Следовательно,

с макс

I Еп + I ioga (

П.

р макс

,1+1

Пусть коэффициент деления К 2 , тогда деление FBX выполняется только высокочастотным трактом. Если К & 2 подключается низкочастотный тракт. Теперь очевидно, что число i также является номером разряда o6aiero коэффициента деления К, представленного в двоичном коде разрядностью L, и ч тановмтся понятным удобство представления числа п в виде 2.

Рассмотрим более подробно работу предлагаемого устройства. При отсутствии сигнала Пуск, передаваемого по шине 11 запуска, на ней присутствует уровень логической 1, что соответствует блокировке работы высокочастотного и низкочастотного трактов и установке в исходное состояние элементов еинхронизации.

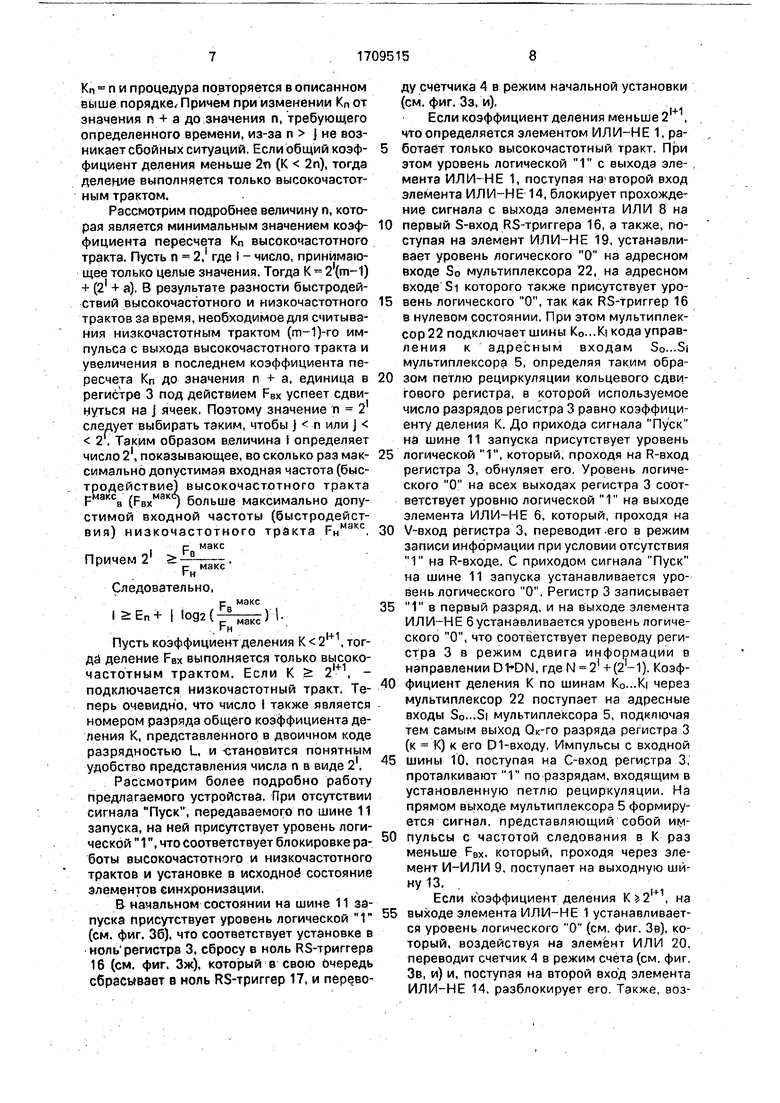

В начальном состоянии на шине 11 запуска присутствует уровень логической Г (см. фиг. 36), что соответствует установке в нольрегистра 3, сбросу в ноль RS-триггера 16 (см. фиг. Зж), кото1зый в свою Очередь сбрасывает в ноль RS-триггер 17, и переводу счетчика 4 в режим начальной установки (см. фиг. Зз, и).

Если коэффициент деления меньше 2 , что определяется элементом ИЛИ-НЕ 1, работает только высокочастотный тракт. При этом уровень логической 1 с выхода элемента ИЛИ-НЕ 1, поступая на второй вход эле(иента ИЛИ-НЕ 14, блокирует прохождение сигнала с выхода элемента ИЛИ 8 на

0 первый S-вход RS-триггера 16, а также, поступая на элемент ИЛИ-НЕ 19, устанавливает уровень логического О на адресном входе So мультиплексора 22, на адресном входе Si которого также присутствует уровень логического О, так как RS-tpиrrep 16 в нулевом состоянии. При этом мультиплексор 22 подключает шины Ко...Ki кода управления к адресным входам So...Si мультиплексора 5, определяя таким образом петлю рециркуляции кольцевого сдви гового регистра, в которой используемое число разрядов регистра 3 равно коэффициенту деления К. До прихода сигнала Пуск на шине 11 запуска присутствует уровень

5 логической 1, который, проходя на R-вход регистра 3, обнуляет его. Уровень логического О на всех выходах регистра 3 соответствует уровню логической 1 на выходе элемента ИЛИ-НЕ 6. который, проходя на

0 V-вход регистра 3, переводит-его в режим записи информации при условии отсутствия 1 на R-входе. С приходом сигнала Пуск на шине 11 запуска устанавливается уровень логического О. Регистр 3 записывает

5 1 в первый разряд, и на выходе элемента ИЛИ-НЕ 6устанавливается уровень логического О, что соответствует переводу регистра 3 в режим сдвига информации в направленииD1 DN, гдеМ 2+(2-1). Коэффициент деления К по шинам Ko...Ki через мультиплексор 22 поступает на адресные входы So...Si мультиплексора 5, подключая тем самым выход Ок-го разряда регистра 3 (к К) к его Dl-входу. Импульсы с входной

5 шины 10. поступая на С-вход регистра 3, проталкивают 1 по разрядам, входящим в установленную петлю рециркуляции. На прямом вь|ходе мультиплексора 5 формируется сигнал, представляющий собой пульсы с частотой следования в К раз меньше FBX, который, проходя через элемент И-ИЛИ 9, поступает на выходную шину 13.

Если коэффициент деления на

5 выходе элемента ИЛИ-НЕ 1 устанавливается уровень логического О (см. фиг. Зв). который, воздействуя на элемент ИЛИ 20. переводит счетчик 4 в режим счета (см. фиг. Зв, и) и, поступая на второй вход элемента ИЛИ-НЕ 14. разблокирует его. Также, воздействуя на элемент ИЛИ-НЕ 19, на адресном входе So мультиплексора 22 уст навливаётся уровень логической 1, что соответствует прохождению на адресные входы S мультиплексора 5 кода числа 2 (см. фи, Зг). С прямого выхода мультиплексора 5 сигнал -у поступает на счетный вход +Г счетчика 4, в первый разряд которого уже записана 1. Информация с выходов Q счетчика 4 сравнивается с разрядами KI...KL кода коэффициента деления с помощью элементов 7 совпадения и элемента ИЛИ 8, на выходе которого при совпадении информации устанавливается уровень логического О (см. фиг. Зе). который через элемент ИЛИ-НЕ 14 поступает на первый S-вход ЯЗтриггера 16, на второй S-вхЬд которого поступает сигналЧ; инверсного выхода мультиплексора 5. Таким образом при исчезновении на выходах мультиплексора 5 последнего импульса сигнала - RS-jp rrep 16 перебрасывается в единичное состояние (см. фиг. Зж), Это приводит к появлению 1 на выходе элемента ИЛИ 20, что соответствует переводу счетчика 4 в режим начальной установки (см. фиг. Зй, а). Также 1 с прямого выхода RS-триггера 16, проходя через элемент 23 задержки переднего фронта импульса, задерживается на время, необходимое для срабатывания мультиплексоров 22 и 5, и поступает на вход элемента И-ИЛИ 9, что соответствует подключению прямого выхода мультиплексора 5 к выходной шине 13, а также к появлению О на адресном входе So мультиплексора 22 и 1 на его адресном входе Si, что соответствует установке на адреснь1х входах S мультиплекс;сра 5 двоичного крда досчета (а++ 2) (см. фиг. Зг), где остаток а передается в двоичном коде по шинам Ko.,.Ki кода управ-; ления. За время, необходимое на выполнение вышеописанных операций, на С-вход регистра 3 поступает J импульсов Fex, причем j 2. На выход мультиплексора 5 и, следовательно, на выходную шину 13 Пройдет {а+2)-й импульс (см. фиг. Зк), которь1й, поступая на S-вxoд RS-триггера 17, перебросит его в единичное состояние. Единица с выхода RS-триггера 17 проходит на первый вход элемента И 21, на втором входе которого установится 1 при исчезновении импульса на выходах мультиплексора5. При этом на выходе элемента И 21 устанавливается уровень логической 1, который, проходя через элемент ИЛИ 15, сбрасывает, RS-триггер 16 (см. фиг. Зж) в ноль, который, в свою очередь, по инверсному выходу сбрасывает в ноль RS-триггер 17. Таким образом элементы синхронизации и управления установлены в исходное состояние и цикл деления повторяется в описанном порядке. На выходной шине 13 формируется сигнал (см. фиг. Зк), представляющий србой импульсы с частотой следования в К раз меньше частоты следования входных импульсов FBX, причемК 2(т-1) + (2+а), где m En + I -т К Длительность выходных импульсов равна периоду следования входных импульсов. В случае использования для построения делителя ИС К 1600 серии элементы ИЛИНЕ 1, 6, 19, 14 и элементы ИЛИ 15, 20 pea- лизуются на ИС К1500ЛМ101, элемент И-ИЛИ 9 реализуется на ИС К1500ЛК117 и К1500ЛМ102, инвертор 18 реализуется на ИС К1500ЛМ102, RS-триггеры 16, 17 реализуются на ИС К1500ТМ130 и К1500ЛК117.. счетчик 4 реализуется на ИС К1500ИЕ136, элементы 7 совпадения и элемент ИЛИ 8 реализуются на ИС К1500ЛП102, мультиплексор 5 реализуется на ИС К1500П164, мультиплексор 22 - на ИС К1500КП155, регистр 3 - на ИС К1500ИР141. Учитывая задержку распространения сигнала в используемых ИС, определяем , Исходя из ТУ на ИС К1500 серии ((5К0.348,673), рассчитаем минимальный период следования входной импульсной последовательности для пре,цложенного делителя и прототипа, для предложенного делителя суммарное время задержки на выполнение операции сдвига информации в регистре сдвига 1,9 не. прохождения информации через мультиплексор 1,8 НС и предустановки по рходу D1 регистра 3 1 не равно 1,9 + 1,8 + 1 4,7 не, т.е. 213МГц. Для прототипа суммарное время задержки невыполнение операции счета счетчикомимпульсов 2,5 НС, срабатывание элементов сравнения кодов 1,3 не, срабатывание элемента НЕ-ИЛИ 1,3 не, выполнение операции сброса счетчика 4,8 не, срабатывание элементов сравнения кодов и элемента НЕ-ИЛИ для снятия сигнала сброса счетчика 1,3 не + 1,3 не 2,6 не равно 2,7+- + 1,3+ 1,3 + 4,8 + 2,6 12,7нс, т.е. 78,7 МГц. . ,. Пусть устройство-прототип реализовано только на счетчике серии К1500ИЕ136, тогда суммарное время задержки на выполнение операции обратного счета и формирование сигнала переноса по-приходу тактового сигнала на вход синхронизации С 5 НС, выполнение операции загрузки по приходе сигнала низкого уровня с выхода переноса ТС на вход управления режимом работы S2 4.8 нс выполнение операции установления режима обратного счета по приходе сигнала высокого с выхода переноса ТС нд вход управления режимом работы S2 4,8 не, после выполнения которой возможен приход следующего тактового сигнала на вход синзхронизации С, равно 5 + 4,8 + 4,8-14,6 НС, т.е. FBX 68.5 МГц. При увеличении числа разрядов рассмотренных ycTpoftcTB-npotoTitnoB потребуется включение нескольких корпусов счетчиков, ЧТО приведет к значительному снижению быстродействия. Заявленное устройство лишено этого недостатка. Таким образом при л юбрм коэффициенте деления быстродействие предложенного управляемого делителя равно быстродействИю его высококачественного тракта, которое значительно выше,быстродействия прототипа. Полученный эффект достигается введением регистра и мультиплексора, об разующих высокочастотный тракт деления, и блока управления, изменяющего его коэффициент пересчета (петлю рециркуляции. Упрощается работа делителя, которая сводится к проталкиванию логической единицы по кольцу рециркуляции и иcключaef такие длительные операции, как загрузка счетчика, изменение его режима работы, формирование сигнала переноса. Ф о р м у л а из об ре тения Управляемый делитель частоты следования импульсов, содержащий двоичный счетчик импульсов, разрядные выходы которого соединены с первыми входами соответствующих элементов совпадения, вторые входы которых подключены к шинам кода управления, выходы - к соответствующим входам элемента ИЛИ, входную и выходную шины,отличающийся тем,что, с целью повышения быстродействия, в него введены блок управления, регистр, мультиплексор, первый и второй элементы ИЛИНЕ, элемент И-ИЛИ и шина запуска, причем выходная шина соединена с выходом элемента И-ИЛИ и с первым входом блока управления, второй вход которого подключен к шине запуска и R-входу регистра, третий вход соединен с выходом первого элемента ИЛИ-НЕ и с первым входом элемента И-ИЛИ, четвертый вход - с шинами кода управления, с соответствующими входами первого элемента ИЛИ-НЕ и с вторыми входами элементов совпадения, пятый вход - с выходом элемента ИЛИ, шестой вход - с И14версным выходом мультиплексора, первый выход блока управления соединен с установочным Р-входом двоичного счетчика импульсов, второй выход- с вторым входом элемента И, третий выход - с адресными З-входами мультиплексора, информационные входы которого соединены с разрядными выходами регистра и с выходами второго элемента ИЛИ-НЕ; прямой выход - с третьим и четвертым входами ,эл(емента И-ИЛИ, со счетным входом двоичного счетЧика импульсов и с последовательным входом Д1 сдвига в сторону старших разрядов регистра, V-вход задания режима которого соединен с выходом второго элемента ИЛИ-НЕ, тактовый С-вход - с входной шиной. ,K n;fn-2;0 -Z a k,A/a jTJ7L,.... S. /х..Ш. / 4/ /гШ/У 1 дl,ix.n.55 e1ы.).8т tIbi rpifr.-iS jPUc. .а/Л кA// //J I / ел:ин cv 2t %лЗ yV ...J LJJlj7 CV.(fn-f)

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| СПОСОБ ФОРМИРОВАНИЯ ИМПУЛЬСОВ КАЧАЮЩЕЙСЯ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2143779C1 |

| Устройство для регистрации аналоговой информации | 1982 |

|

SU1164548A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1983 |

|

SU1149367A2 |

| Устройство для управления шаговым двигателем с дроблением шага | 1982 |

|

SU1061230A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1336108A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Устройство для автоматической поверки счетчиков электроэнергии | 1986 |

|

SU1404998A1 |

| Устройство для отображения графической информации | 1989 |

|

SU1767520A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники.. Цель изобретения — повышение быстродействия - достигается введением блока 2управления, регистра 3, мультиплексора 5, первого и второго элементов ИЛИ- НЕ 1 и 6, элeмeнta И-ИЛИ 9 и шины 11 запуска. Устройство также содержит двоичный счетчик 4 импульсов, элементы 7 совпадения, элемент,ИЛИ 8, входнуй шину 10, шину 12 кода управления, выходную шину 12. Зил.»w^Ё

| Лейнов М.Л | |||

| и др | |||

| Цифровые делители частоты на логических элементах | |||

| М.: Энергия | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-01-30—Публикация

1989-12-19—Подача