(54} ДЕЛИТЕЛЬ VCTOTU НА ТРИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на три | 1982 |

|

SU1027835A2 |

| Делитель частоты на три | 1985 |

|

SU1279061A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036555C1 |

| Кольцевой делитель частоты на три | 1986 |

|

SU1406786A2 |

| Многоканальный формирователь одиночных импульсов | 1985 |

|

SU1243115A1 |

| Устройство для приема последовательного кода | 1980 |

|

SU960893A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 2022 |

|

RU2785274C1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Переключающее устройство | 1985 |

|

SU1256191A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 1993 |

|

RU2041562C1 |

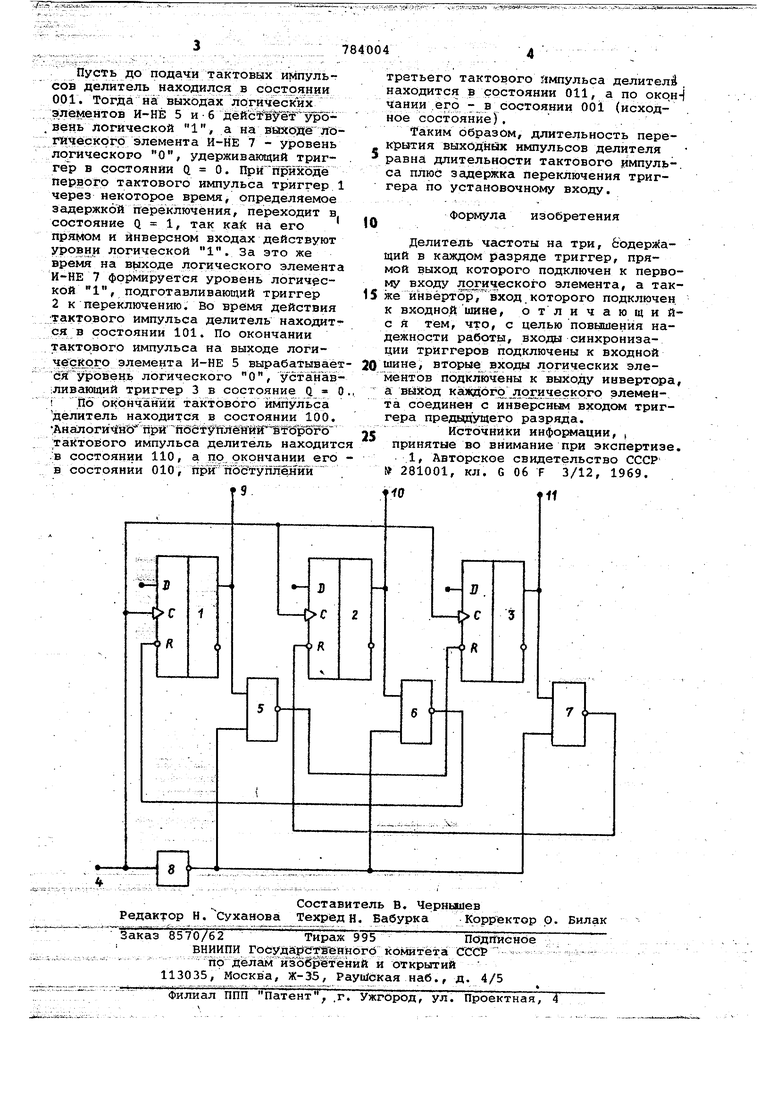

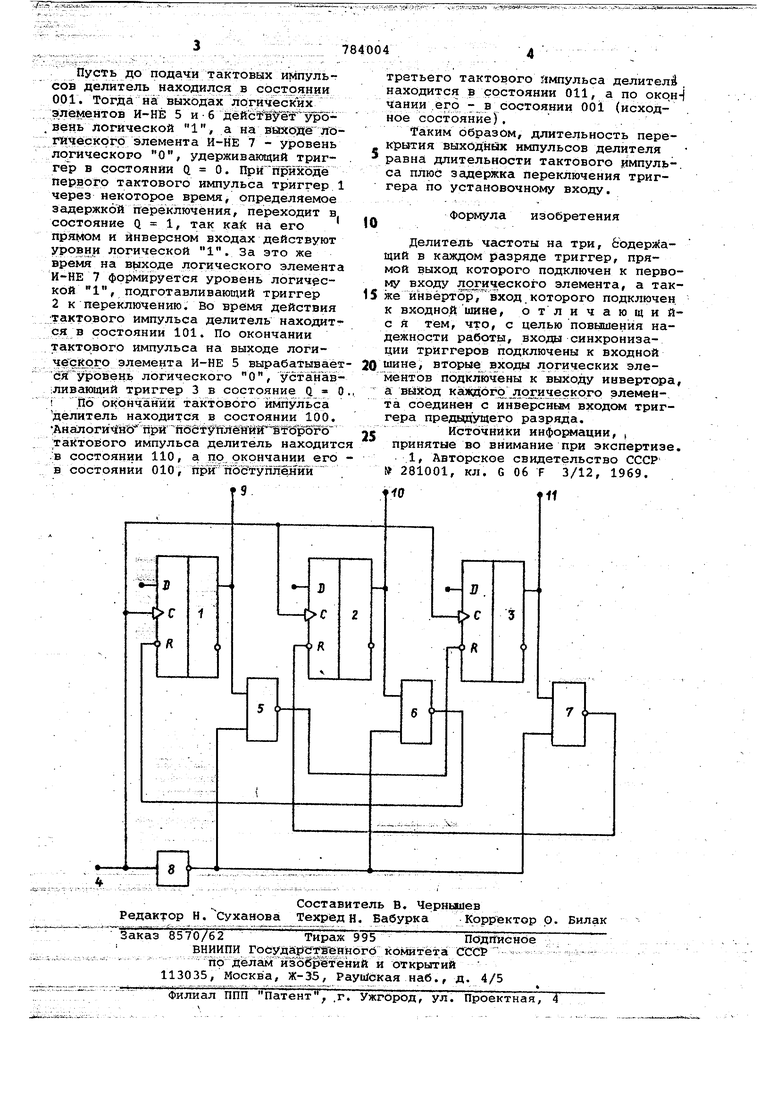

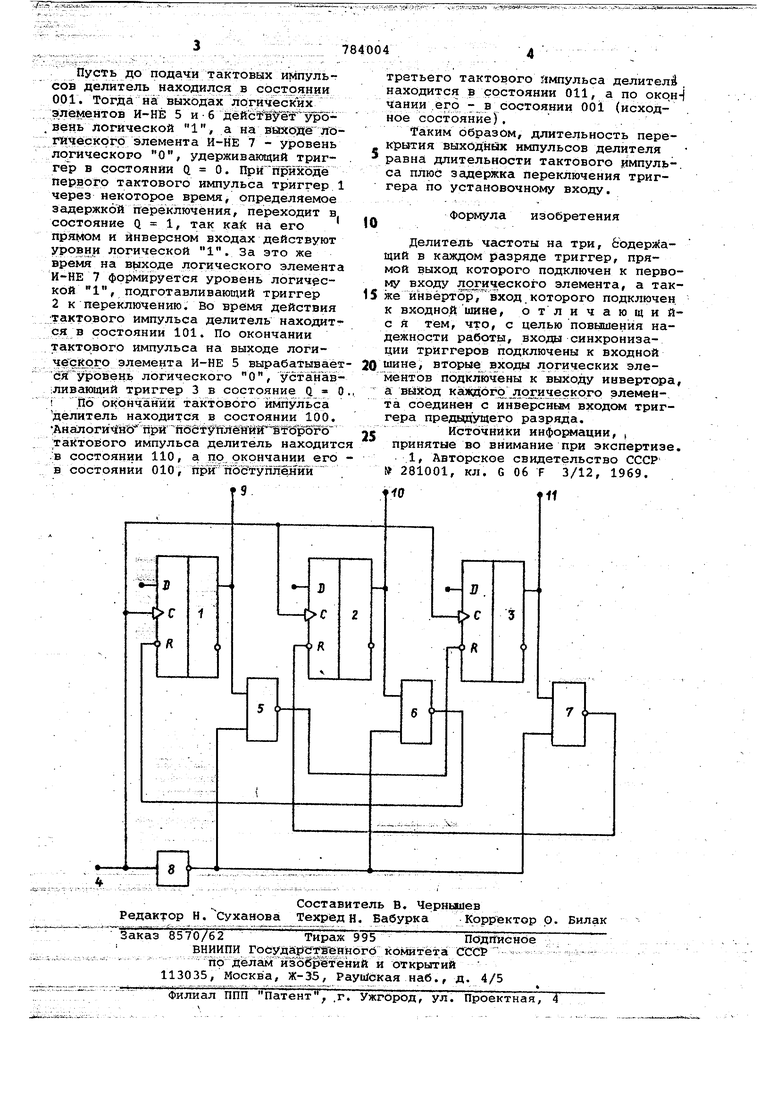

Изобретение относится к импульсн технике и может быть использовано при построении генераторов тактового питания приборов с зарядовой связью. Известен делитель частоты на три содержа1айй в разряде триггер прямой выход которого подключен к первому входу логического элемента, а также инвертор, вход которого под ключей к входной шине }. Однако данный делитель обладает невысол ой надежностью. Целью изобретения является повьяи нйе надежности работы. Для этого в делителе частоты на три, содержащем в каждс 1 разряде триггер, прямой выход которого подключей к первому входу логического элемента, а также инвертор, вход которого подключен к входной шине, входы синхронизации триггеров подкл чены к входной шине, вторые входы л гических элементов подключены к ваходу инвертора; а выход каждого логического элемента соединен с инверсным входом триггера предыдущего разряда. На чертеже представлена структурная электрическая схема делителя часTottjf ни триГ Делитель частоты ка три содержит три триггера 1-3, входы синхронизации Которых подключены к входной шине 4, логические элементы И-НЕ 5-7 н инвертор 8 , вход которого подключен к входной Нине 4. Первые входы логических элементов И-НЕ 5-7 подключены к выходу инвертора 8. Второй вход логического элемента И-НЕ 5 подключен к прямому выходу триггера 1, являющемуся выходной шиной 9. Выход логическ то элемента И-НЕ 5 подключен к инверсному входу триггера 3. Второй вход логического элемента и-НЕ 6 подключен к прямому выходу триггера 2, являюцемуся выходной шиной 10. Выход логического элемента И-НЕ 6 подключен к инверсному входу триггера 1. Второй вход логнческогр элемента И-НЕ 7 подключен к прямому выходу триггера 3, являющемуся выходной шиной 11. Выход логического элемента И-НЕ 7 подключен к инверсно входу триггера 2. Делитель частоты на три работает следукяцим образом.

Пусть до подачи тактовых импульсов делитель находился в состряуии 001. Тогда на выхбдах логических элементов И-НЕ 5 и б дёйс вТёТ Уровень логической 1, а. на внхойё лбгйчёскргб элемента И-НЕ 7 - уровень логического О, удерживающий триггер в СОСТОЯНИИ и 0. Прип;руиходё первого тактового импульса триггер 1 через некоторое время, определяемое задержкой переключения, переходит в. состояние Q 1, так каЛ на его прямом и инверсном входах действуют ypOBjHH логической 1. За это же время на логического элемента И-НЕ 7 формируется уровень логической 1, подготавливающий триггер 2 к переключению. Во время действия iTaKTOBoro импульса делитель находится в состоянии 101. По окончании тактового импульса на выходе логиче скр.Го элемента И-НЕ 5 вырабатываетсГя у1ровень логического О, устанав:ливающий триггер 3 в состояние Q 0 По окончаний тактового импульса делитель находится в состоянии 100. Аналоги«ЕШт1рй й©ет01йШйГ t5p6r6 тактового импульса делитель находитс ,в состоянии 110, а по окончании его в состоянии 010, прй пЬсТуплеяйи .

S

5

третьего тактового импульса делители находится в состоянии 011, а по OKOH-J чании его - в состоянии 001 (исходное состояние)..

Таким образом, длительность перекрытия выходных импульсов делителя равна длительности тактового импуль-. са плюс задержка переключения триггера по установочному входу.

формула изобретения

Делитель частоты на три, бодерясащий в каждом разряде триггер, прямой выход которого подключен к первому входу логического элемента, а также инвертор, вход которого подключен, к входной шине, отличающийс я тем, что, с целью повышения надежности работы, входы синхронизации триггеров подключены к входной 0 шине вторые заходы лргических элементов подключены к выходу инвертора, а выхъд кгиедбго jiqEH4ecKprp элемента соединен с инверсным входс л триггера предеадущего разряда.

Источники инфОЕмации, , принятые во внимание при экспертизе.

1, Авторское свидетельство СССР 281001, кл. G 06 F 3/12, 1969.

f-fO

11

С

6

Авторы

Даты

1980-11-30—Публикация

1979-01-22—Подача