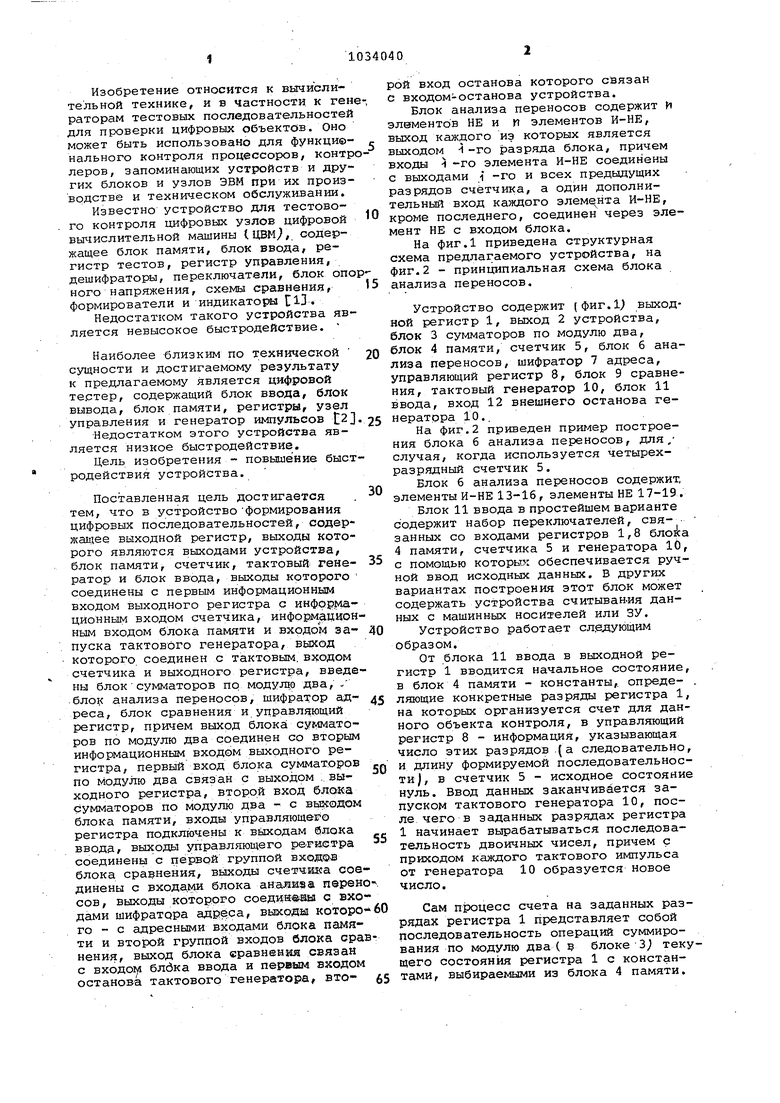

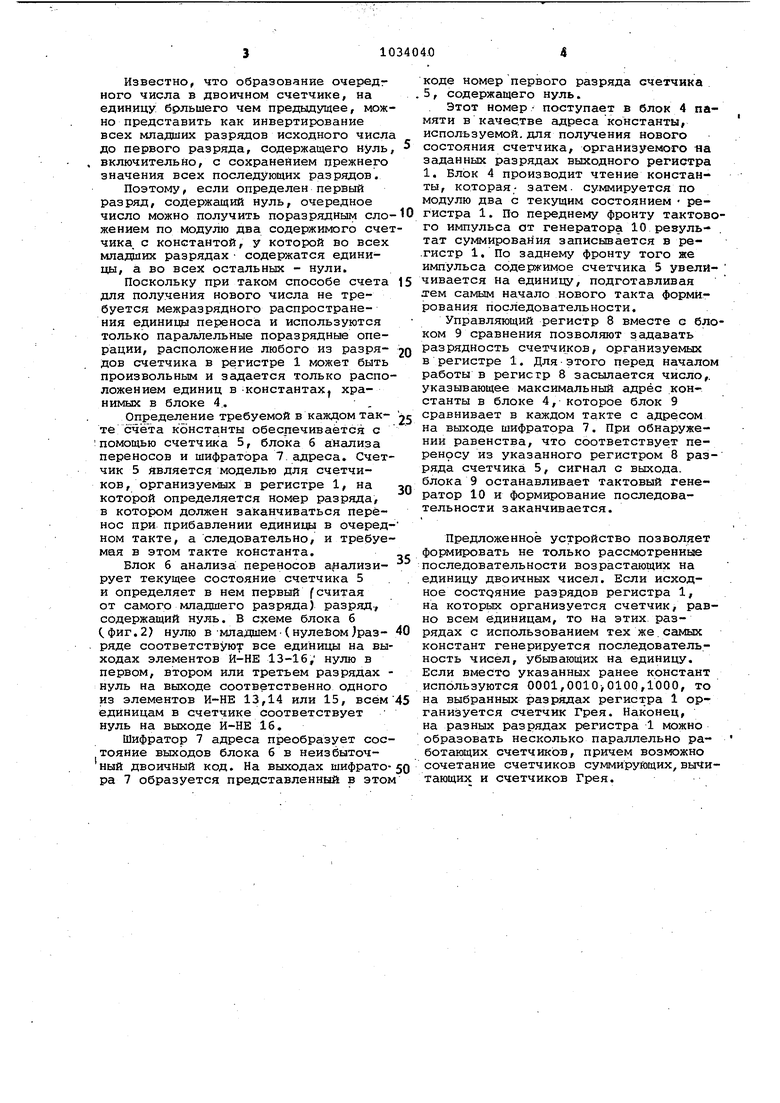

Изобретение относится к вычислительной технике, и в частности к ген раторам тестовых последовательностей для проверки цифровых объектов, оно может быть использовано для функциенального контроля процессоров, контр леров, запоминающих устройств и других блоков и узлов ЭВМ при их производстве и техническом обслуживании. Известно устройство для тестового контроля цифровых узлов цифровой вычислительной машины (ЦВМ,. содержащее блок памяти, блок ввода, регистр тестов, регистр управления, дешифраторы, переключатели, блок опо ного напряжения, схемы сравнения, формирователи и индикатора tl3. Недостатком такого устройства является невысокое быстродействие. Наиболее близким по технической сущности и достигаемому результату к предлагаемому является цифровой тестер, содержащий блок ввода, блок вывода, блок памяти, регистры, узел управления и генератор импульсов tSj Недостатком этого устройства является низкое быстродействие. Цель изобретения - повышение быст родействия устройства. Поставленная цель достигается , тем, что в устройствоформирования цифровых последовательностей, содержад1ее выходной регистр, выходьа которого являются выходами устройства, блок памяти, счетчик, тактовый генератор и блок ввода, выходы которого соединены с первым информационным входом выходного регистра с информационным входом счетчика, информацион ным входом блока памяти и входом запуска тактового генератора, выход которого, соединен с тактовым, входом счетчика и выходного регистра, введе ны блок сумматоров по. модул1р два, блок анализа переносов, шифратор адреса, блок сравнения и управляющий регистр, причем выход блока сугдааторов по модулю два соединен со вторым информационным входом выходного регистра, первый вход блока сумматоров по модулю два связан с выходом „ выходного регистра, второй вход блока сумматоров по модулю два - с выходом блока памяти, входы управляющего регистра подключены к вьссодам блока ввода, выходы управляющего ре-гйетра соединены с первой группой вхояэ® блока сравнения, выходы счетчика сое динены с входами блока анадаж а гlepeн сов, выходы которого соедиа- йи с вхо дами шифратора адреса, выхряы которо го - с адресными входами блока памяти и второй группой входов блока сра нения, выход блока сравнения связан с входог блбка ввода и первам входом останова тактового генератора второй вход останова которого связан с входом останова устройства. Блок анализа переносов содержит И элементов НЕ и и элементов И-НЕ, выход каждого иэ которых является выходом -i -го разряда блока, причем входы -го элемента И-НЕ соединены с выходами i -го и всех предыдущих разрядов счётчика, а один дополнительный вход каждого элемента И-НЕ, кроме последнего, соединен через элемент НЕ с входом блока. На фиг.1 приведена структурная схема предлагаемого устройства, на фиг.2 - принципиальная схема блока анализа переносов. Устройство содержит (фиг.1) выходной регистр 1, выход 2 устройства, блок 3 сумматоров по модулю два, блок 4 памяти, счетчик 5, блок б анализа переносов, шифратор 7 адреса, управляющий регистр 8, блок 9 сравнения, тактовый генератор 10, блок 11 ввода, вход 12 внешнего останова генератора 10.. На фиг,2 приведен построения блока 6 анализа переносов, для/ случая, когда используется четырехразрядный счетчик 5. Блок 6 анализа переносов содержит, элементы И-НЕ 13-16, элементы НЕ 17-19. Блок 11 ввода в простейшем варианте содержит набор переключателей, связанных со входами регистров 1,8 4 памяти, счетчика 5 и генератора 10, с помощью которых обеспечивается ручной ввод исходных данных, В других вариантах построения этот блок может содержать устройства считыван-ия данных с машинных носителей или ЗУ. Устройство работает следующим образом. От блока 11 ввода в выходной регистр 1 вводится начальное состояние, в блок 4 памяти - константы,, опреде- . ляющие конкретные разряды регистра 1, на которых организуется счет для данного объекта контроля, в управляющий регистр 8 - информация, указывающая число этих разрядов .(а следовательно, и длину формируемой последовательности), в счетчик 5 - исходное состояние нуль. Ввод данных заканчивается запуском тактового генератора 10, после чего в заданных разрядах регистра 1 начинает вырабатываться последовательность двоичных чисел, причем с приходом каждого тактового импульса от генератора 10 образуется новое число. Сам процесс счета на заданных разрядах регистра 1 представляет собой последовательность операций суммирования по модулю два ( в блоке 3,J текущего состояния регистра 1 с константами, выбираемыми из блока 4 памяти. Известно, что образование очередг ного числа в двоичном счетчике, на единицу большего чем предыдущее, мож но представить как инвертирование всех младших разрядов исходного числ до первого разряда, содержащего нуль включительно, с сохранением прежнего значения всех последующих разрядов. Поэтому, если определен первый разряд, содержащий нуль, очередное число можно получить поразрядным ело жением по модулю два содержимого сче чика, с константой, у которой во всех младщих разрядах содержатся единицы, а во всех остальных - нули. Поскольку при таком способе счета для получения нового числа не требуется межразрядного распространения единицу переноса и используются только параллельные поразрядные операции, расположение любого из разрядов счетчика в регистре 1 может быть произвольным и задается только распо ложением единиц в -константах хранимых в блоке 4.., Определение требуемой в каждом такте счёта константы обеспечивается с :помощью счетчика 5, блока б анализа переносов и шифратора 7.адреса. Счет чик 5 является моделью для счетчиков, организуемых в регистре 1, на которой определяется номер разряда, в котором должен заканчиваться перенос при прибавлении единицы в очеред ном такте, а следовательно, и требуе мая в этом такте константа. Блок б анализа переносов а 1ализирует текущее состояние счетчика 5 и определяет в нем первый fсчитая от самого младшего разряда) разряд., содержащий нуль. В схеме блока б (. фиг. 2) нулю в -младшем ( нулевом )разряде соответствуют все единицы на вы ходах элементов Й-НЕ 13-16, нулю в первом, втором или третьем разрядах нуль на выходе соответственно одного из элементов И-НЕ 13,14 или 15, всем единицам в счетчике соответствует нуль на выходе И-НЕ 16, Шифратор 7 адреса преобразует состояние выходов блока б в неизбыточный двоичный код. На выходах шифратора 7 образуется представленный в этом коде номер первого разряда счетчика 5, содержащего нуль. Этот номер поступает в блок 4 памяти в качестве адреса константы, используемой, для получения нового состояния счетчика, организуемого яа заданных разрядах выходного регистра 1. Блок 4 производит чтение константы, которая- затем, суммируется по модулю два с текущим состоянием регистра 1. По переднему фронту тактового импульса от генератора 10 результат суммирования записывается в ре.гистр 1, По заднему фронту того же импульса содержимое счетчика 5 увеличивается на единицу, подготавливая ем самым начало нового такта формирования последовательности. Управляющий регистр 8 вместе с блоком 9 сравнения позволяют задавать разрядность счетчиков, организуемых в регистре 1. Для этого перед началом работы в регистр 8 засылается число,, указывающее максимальный адрес константы в блоке 4, которое блок 9 сравнивает в каждом такте с адресом на выходе шифратора 7. При обнаружении равенства, что соответствует переносу из указанного регистром 8 разряда счетчика 5, сигнал с выхода, блока 9 останавливает тактовый генератор 10 и Формирование последовательности заканчивается. Предложенное устройство позволяет формировать не только рассмотренные последовательности возрастающих на единицу двоичных чисел. Если исходное состс}яние разрядов регистра 1, на которых организуется счетчик, равно всем единицам, то на этих разрядах с использованием тех же.самых констант генерируется последовательность чисел, убывающих на единицу. Если вместо указанных ранее констант используются 0001,0010)0100,1000, то на выбранных разрядах регистра 1 организуется счетчик Грея. Наконец, на разных разрядах регистра 1 можно образовать несколько параллельно работающих счетчиков, причем возможно сочетание счетчиков cyм Iиpyющиx, вычитающих и счетчиков Грея.

Фаг. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

1. УСТРОЙСТВО ДЛЯ ФОРМИРО.ВАНИЯ ЦИФРОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащее выходной регистр, выходы которого являются выходами устрбйства, блок памяти, счетчик, тактовый генератор и блок ввода, выходы которого соединены с первым информацион-. ным входом выходного регистра/ с информационным входом счетчика, с -информационным входом блока памяти и. входом запуска тактового генератора выход которого соединен с тактовым входом счетчика и выходного регистра, отличан щееся тем, что, с целью повышения быстродействия устройства, в него введены блок сумматоров по модулю два, блок ангшиэа переносов, шифратор адреса, блок сравнения и управляющий регистр, причем выход блока сумматоров по модулю два соединён с вторым информационным вхЬдом выходного регистра,- первый вход блока сумматоров по модулю два связан с выходом выходного регистра, зв то рой ВХОД: блока сумматоров по модулю два - с выходом блока памяти, входы управЛЖОЩ0ГО регистра подключены к выходам блока вводаf выходы управляющего регистра соединены с перовой группой входов блока сравнений, выхода счетчика соединены с входами блока анализа переносов, выходы которрго. соединены с входами шифратора адреса, ВБРСОДЫ которого - с адресными входами блока памяти и второй fpjTiпой входов блока сравнения, выход блока сравнения связан с входом бло- ка ввода и первым входом останова так® тового генератора, второй вход оста- -нойа KOTopoio связан с входом оста- . Г/1 нова устройства. : 2. Устрр твр по П.1, о т л ич а ю 14 ё е с я тем, что в нем блок анализа переносов содержит И элементов НЕ ИИ элементов И-НЕ, выход каждого из которых является выходом i-го разряда блока, причем в.ходы - S i -го элемента И-НЕ соединены с : выхода Jj, .ми i-ro и всех предьщ5т1их разрядов ЬМ (Счетчика, а один дополнительный вход каждого элемента И-НЕ кроме последнего, соединен через элемент НЕ с вхо;дом блока.

Авторы

Даты

1983-08-07—Публикация

1982-02-16—Подача