/

/

ч

(J

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

Устройство относится к вычислительной технике и м.б. использовано для контроля блоков ЭВМ. Цель изобретения - повышение достоверности контроля. Псевдослучайное число, сформированное генератором 5 псевдослучайных чисел, поступает через коммутатор 6 на входы контролируемого 2 и эталонного 3 блоков, считывается с выходов этих блоков через коммутатор 6 и обрабатывается в арифметико- логическом блоке 4. Синхронизация осуществляется генератором 7 и блоком 1 микропрограммного управления. Устройство работает в режимах: автоматического кодирования входов/выходов, получения обобщенной сигнатуры, получения сигнатур для каждого из выходных контактов, самопроверки, сравнения с эталоном. 1 з.п. ф-лы, 11 ил. 1 табл.

/(

(

о: а о; х ос

/

.

1

; ИзоОретение относится к вычислительной технике и может быть использовано для кЬнтроля логических блоков автоматики и цифровой вычислительной техники.

Цель изобретения - повышение достоверности контроля.

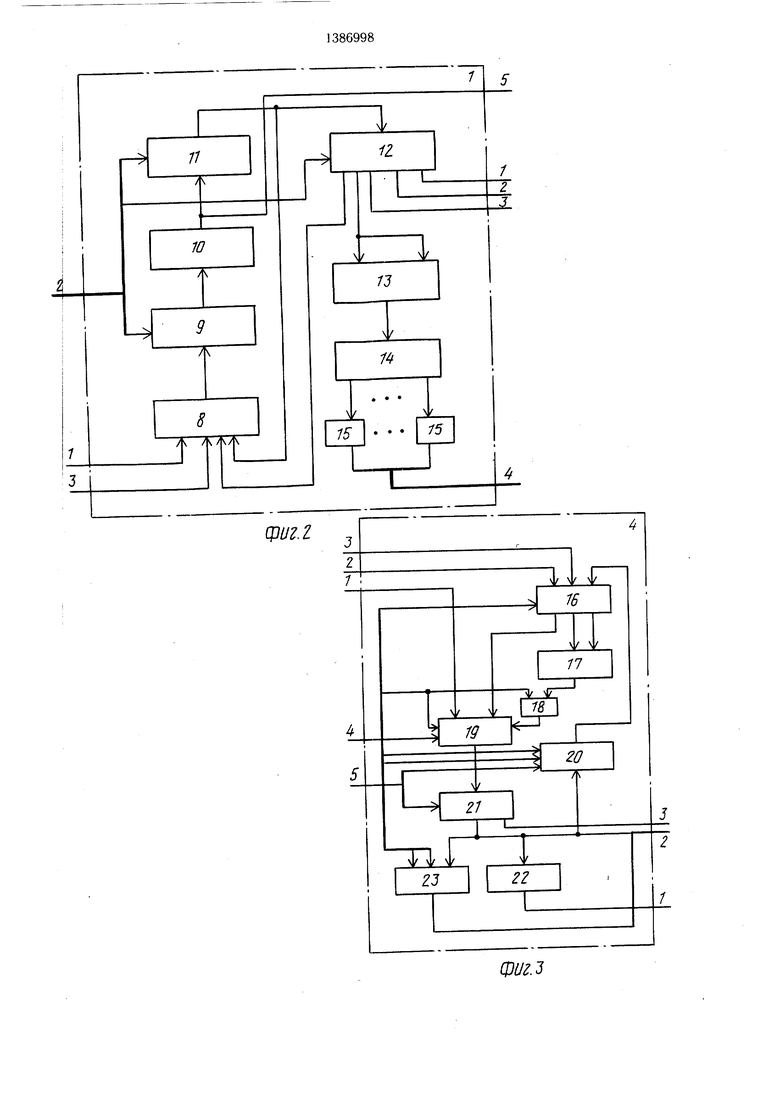

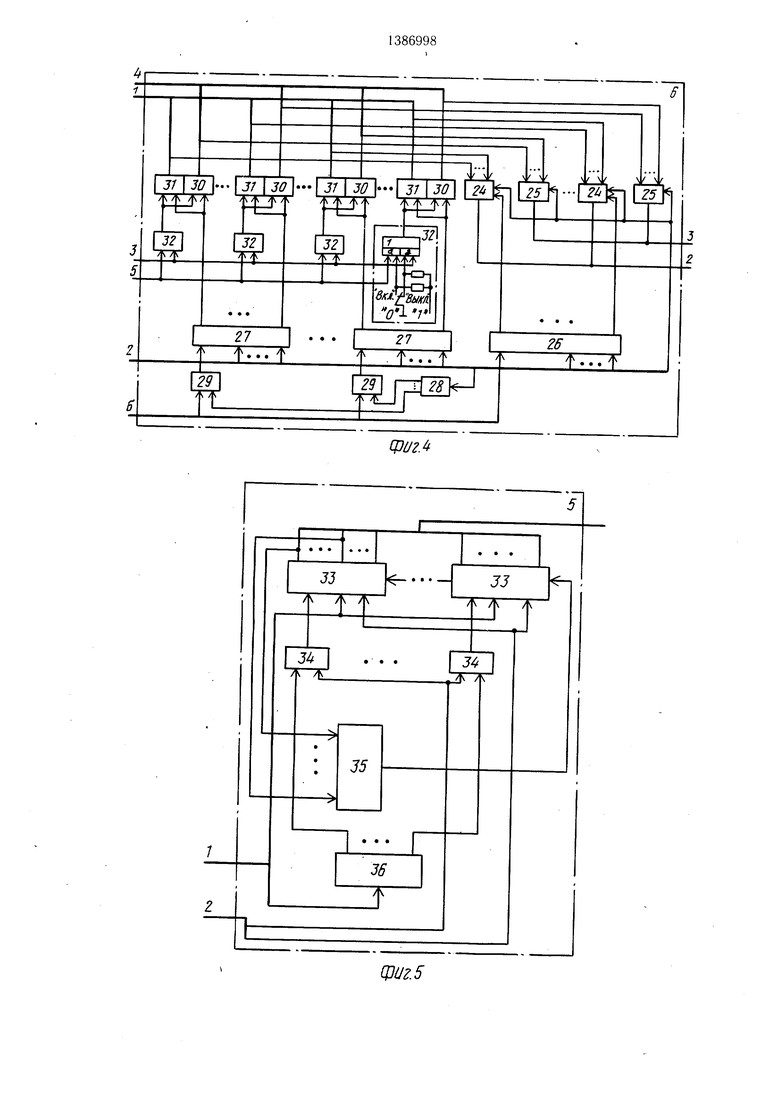

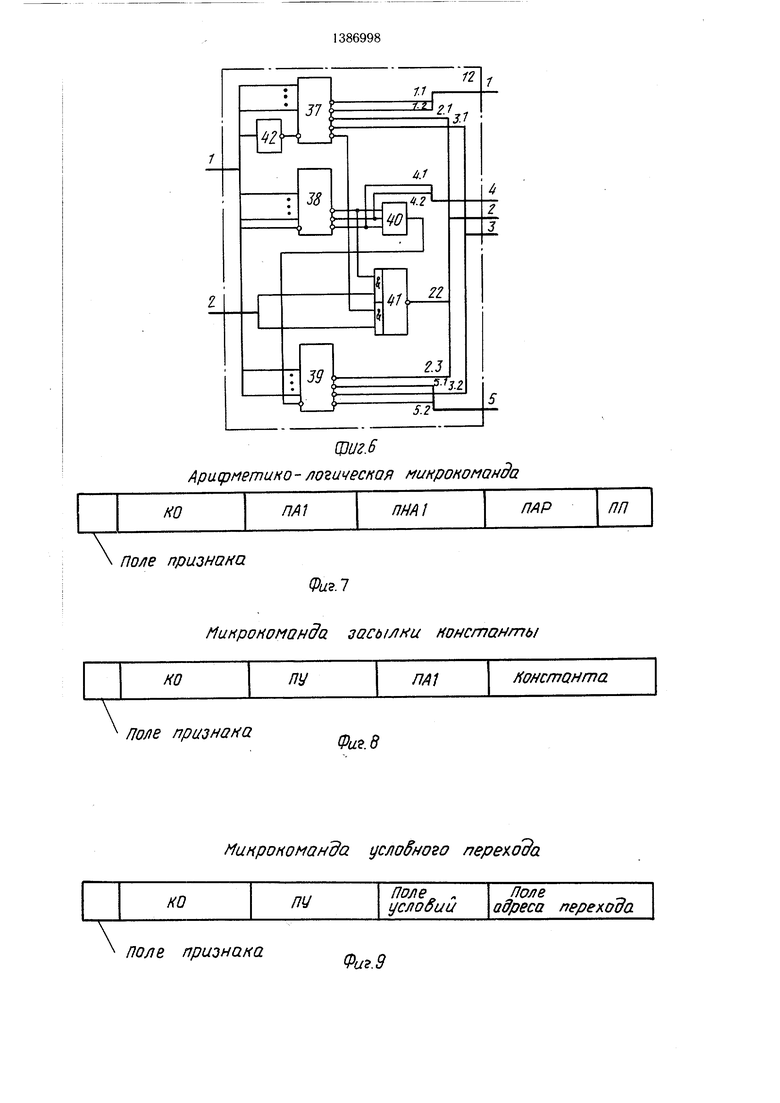

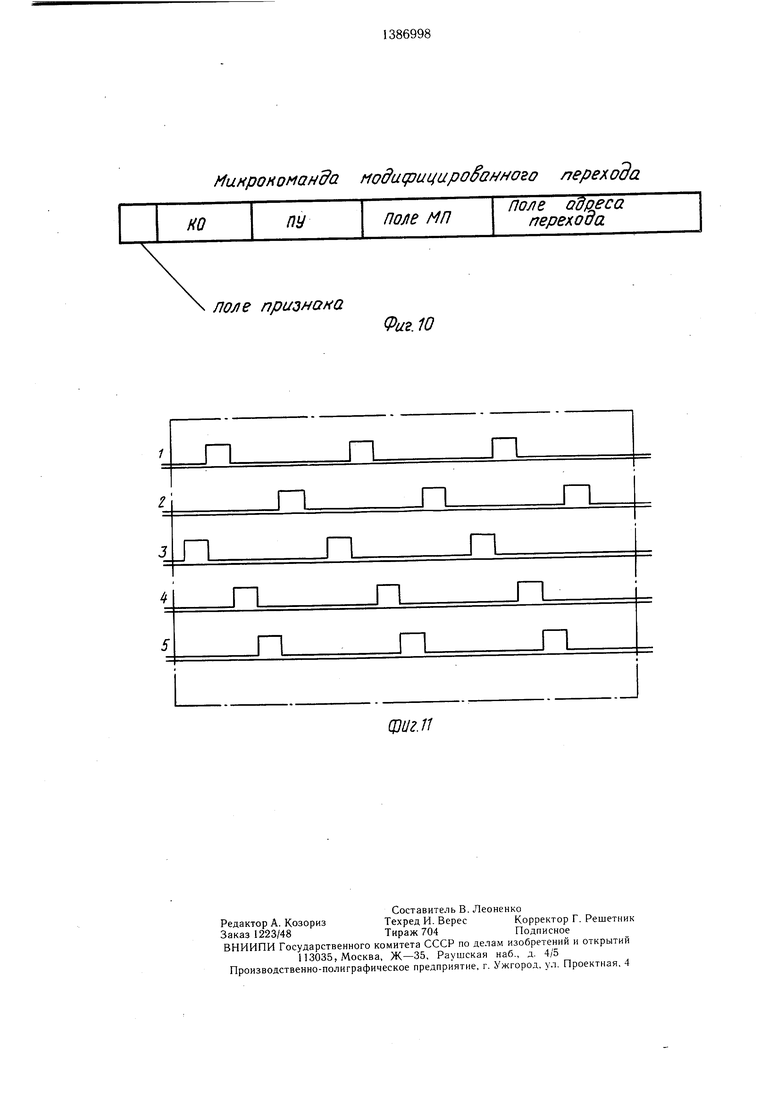

На фиг. 1 представлена схема устройства для контроля логических блоков; на фиг. 2 - схема блока управления; на фиг. 3 - схема арифметико-логического блока; на фиг. 4 - схема коммутатора; на фиг. 5 - с|сема генератора псевдослучайных чисел; н фиг. 6 - схема дешифратора управ- сигналов; на фиг. 7 - структура арифметико-логической микрокоманды; на фиг. 8 - структура микрокоманды засы- константы; на фиг. 9 - структура мик- р жоманды условного перехода; на фиг. 10 - структура микрокоманды модифицирован- HJoro перехода; на фиг. 11 - временная диаграмма блока выработки синхросигналов и: выполнения микрокоманд.

Устройство (фиг. 1) содержит блок 1 управления, контролируемый 2 и эталонный 3| блоки, арифметико-логический блок 4, генератор 5 псевдослучайных чисел, комму- 6, генератор 7 тактовых импульсов.

10

1386998

2

формирования сигналов записи информации в одну из групп регистра 27 выходов п m элементов И 30, предназначенных для передачи информации на п- m контактов эталонного блока 3, п- m элементов И 31, предназначенных для передачи информации на п- m контактов контролируемого блока 2, п- m элементов 2И-ИЛИ 32, предназначенных для передачи на п- m элементов И 30 и 31 информации с генератора 5 псевдослучайных чисел или взаимоисключающих синхросигналов с четвертых выходов (гнезд) блока 1 управления путем коммутации.

Генератор 5 псевдослучайных чисел

г (фиг. 5) содержит регистр 33 сдвига, состоящий из п групп по m разрядов каждая, п элементов И 34, сумматор 35 по модулю два, предназначенный для формирования младшего разряда, поступающего в регистр 33 сдвига, в зависимости от преды20 дущего состояния регистра 33 сдвига и дешифратор 36.

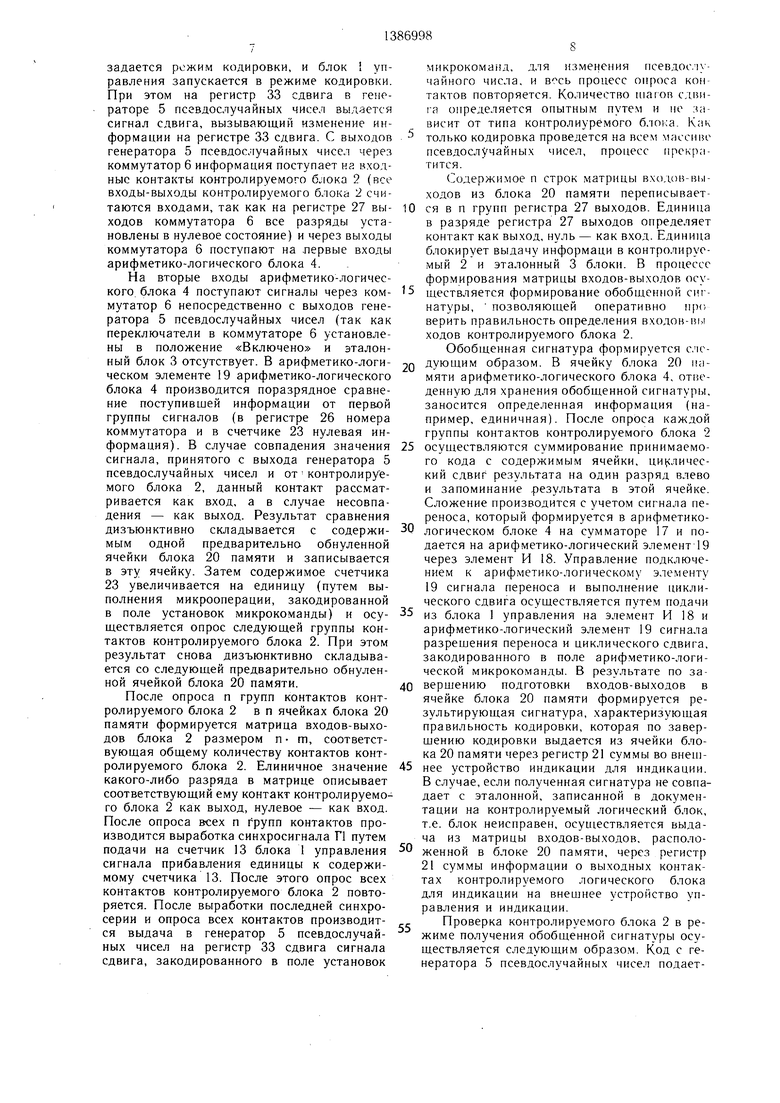

Дешифратор 12 формирования управляющих импульсов (фиг. 6) содержит дешифраторы 37-39, предназначенные соответственно для расшифровки поля адреса реБлок 1 управления (фиг. 2) содержит - зультата в арифметико-логической микрокоб|пок 8 модификации адреса, регистр 9 адреса микрокоманд, блок 10 памяти микрокоманд, регистр 11 микрокоманд, дешифратор 12 управляющих сигналов, счетчик 13, дешифратор 14, группу 15 формирователей импульсов.

Арифметико-логический блок 4 (фиг. 3) содержит коммутатор 16, сумматор 17 по модулю два, предназначенный для формирования переноса в зависимости от преды30

манде, типа микрокоманды и поля установок в микрокомандах засылки констант условного и модифицированного переходов, элемент И 40, на первый вход которого поступает признак микрокоманды засылки константы, на второй и третий входы - соответственно признаки микрокоманд условного и модифицированного переходов с выхода дешифратора 38, элемент 2И-ИЛИ 41, на первый вход которого поступает признак микдущеи суммы и используемый при получе-рокоманды засылки константы с выхода

н|ии сигнатуры, элемент И 18, арифметико-дешифратора 38, на второй и четвертый

логический элемент 19, выполняющий наборвходы поступает сигнал записи, формируеарифметико-логических операций, в том чис-мый генератором 7 тактовых импульсов.

циклический сдвиг на один разряд, блок 2b памяти, регистр 21 суммы, дешифратор 22 нуля, счетчик 23.

Коммутатор 6 (фиг. 4) содержит m мультиплексоров 24 на п входов каждый для последовательного приема информаци от п групп контактов контролируемого блока 2, m мультиплексоров 25 на п входов каждый для последовательного приема инфор- мации от п групп контактов эталонного блока 3, т-разрядный регистр 26 номера мультиплексора, разрешающий прохождение информации через мультиплексоры 24 от

на третий вход - сигнал с выхода дешифратора 37, определяющий запись в блок 20 40 памяти арифметико-логического блока 4, элемент НЕ 42, на вход которого поступает сигнал с поля признака микрокоманды регистра 11 микрокоманд блока 1 управления, выход элемента НЕ 42 соединен с управляющим инверсным входом дешифратора 37, на который поступает инверсный .признак арифметико-логической микрокоманды.

Входы 1 и 2 блока 4 соединены соответственно с первыми и вторыми выходами

контролируемого блока 2, регистр 27 выхо-коммутатора 6, по входу 1 поступает индов, состоящий из п групп по m разрядов каждая (единичное значение разрядов описывает соответствующий контакт контролируемого 2 и эталонного 3 блоков как выход, нулевое значение как вход), дещифформация с группу выходных контактов контролируемого блока 2, по входу 2 - с группы выходных контактов эталонного блока 3, группа контактов задается счетчиком 23, вход 3 соединен с выходом поля управратор 28, определяющий одну из п групп 55 ления блока 1, по микрокоманде засылки регистра 27 выходов (номер группы ре-константы из блока 10 памяти микрокоманд

гистра выходов задается на счетчике 23), п элементов И 29, предназначенных для

константа записывается через коммутатор 16, арифметико-логический элемент 19

0

манде, типа микрокоманды и поля установок в микрокомандах засылки констант условного и модифицированного переходов, элемент И 40, на первый вход которого поступает признак микрокоманды засылки константы, на второй и третий входы - соответственно признаки микрокоманд условного и модифицированного переходов с выхода дешифратора 38, элемент 2И-ИЛИ 41, на первый вход которого поступает признак мик

на третий вход - сигнал с выхода дешифратора 37, определяющий запись в блок 20 0 памяти арифметико-логического блока 4, элемент НЕ 42, на вход которого поступает сигнал с поля признака микрокоманды регистра 11 микрокоманд блока 1 управления, выход элемента НЕ 42 соединен с управляющим инверсным входом дешифратора 37, на который поступает инверсный .признак арифметико-логической микрокоманды.

Входы 1 и 2 блока 4 соединены соответственно с первыми и вторыми выходами

коммутатора 6, по входу 1 поступает информация с группу выходных контактов контролируемого блока 2, по входу 2 - с группы выходных контактов эталонного блока 3, группа контактов задается счетчиком 23, вход 3 соединен с выходом поля управления блока 1, по микрокоманде засылки константы из блока 10 памяти микрокоманд

константа записывается через коммутатор 16, арифметико-логический элемент 19

и регистр 21 суммы в блок 20 памяти, адрес ячейки блока 20 памяти задается в поле микрокоманды и поступает на адресные входы блока 20 непосредственно с поля микрокоманды, синхровход соединен с третьим выходом поля установки блока 1, на коммутатор 16 поступают разряды поля направления первого операнда, на арифметико-логический элемент 19 - разряды кода операции арифметико-логической микрокоманды, на элемент И 18 поступает сигнал переноса, а в арифметико-логический элемент 19 - сигнал циклического сдвига с поля признака разрешения переноса и циклического сдвига, на первый вход блока 20 поступают разряды с поля адреса первого операнда, на второй вход - сигнал записи с выхода 2 дешифратора 12 управляющих сигналов, второй стробирующий вход (пятый на фиг. 3) соединен с первым выходом генератора 7 тактовых импульсов, на вход блока 20 памяти поступает сигнал чтения; на регистр 21 суммы поступает сигнал записи. Выход 1 соединен с первым входом логических условий блока 1 регистра 21 суммы, на блок 8 модификации передается признак нуля с арифметико-логического блока 4, выход 2 соединен с группой адресных входов коммутатора бис группой инфор мационных входов (первый на фиг. 5) генератора 5 псевдослучайных чисел.

При большом количестве контактов контролируемого 2 и эталонного 3 логических блоков для сокращения аппаратурных затрат разрядность арифметико-логического блока выбирается ш-разрыдной и обработка ведется последовательно п группами.

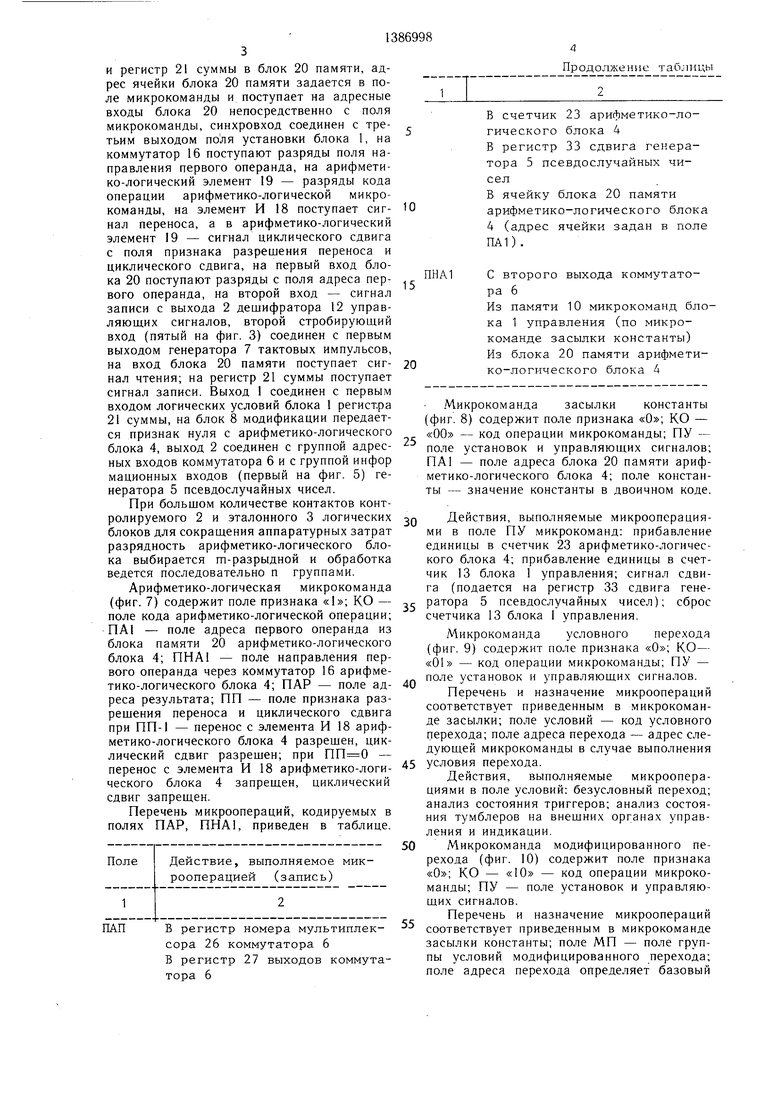

Арифметико-логическая микрокоманда (фиг. 7) содержит поле признака КО - поле кода арифметико-логической операции; ПА1 - поле адреса первого операнда из блока памяти 20 арифметико-логического блока 4; ПНА1 - поле направления первого операнда через коммутатор 16 арифметико-логического блока 4; ПАР - поле адреса результата; ПП - поле признака разрешения переноса и циклического сдвига при ПП-1 - перенос с элемента И 18 арифметико-логического блока 4 разрешен, циклический сдвиг разрешен; при - перенос с элемента И 18 арифметико-логического блока 4 запрещен, циклический сдвиг запрещен.

Перечень микроопераций, кодируемых в полях ПАР, ПНА1, приведен в таблице.

ПАП В регистр номера мультиплек- сора 26 коммутатора 6 В регистр 27 выходов коммутатора 6

Продолжение таблицы

В счетчик 23 арифметико-логического блока 4 В регистр 33 сдвига генератора 5 псевдослучайных чисел

В ячейку блока 20 памяти арифметико-логического блока 4 (адрес ячейки задан в поле ПА1) .

5

0

5

0

5

0

5

0

ПНА1С второго выхода коммутатора 6

Из памяти 10 микрокоманд блока 1 управления (по микрокоманде засылки константы) Из блока 20 памяти арифметико-логического блока 4

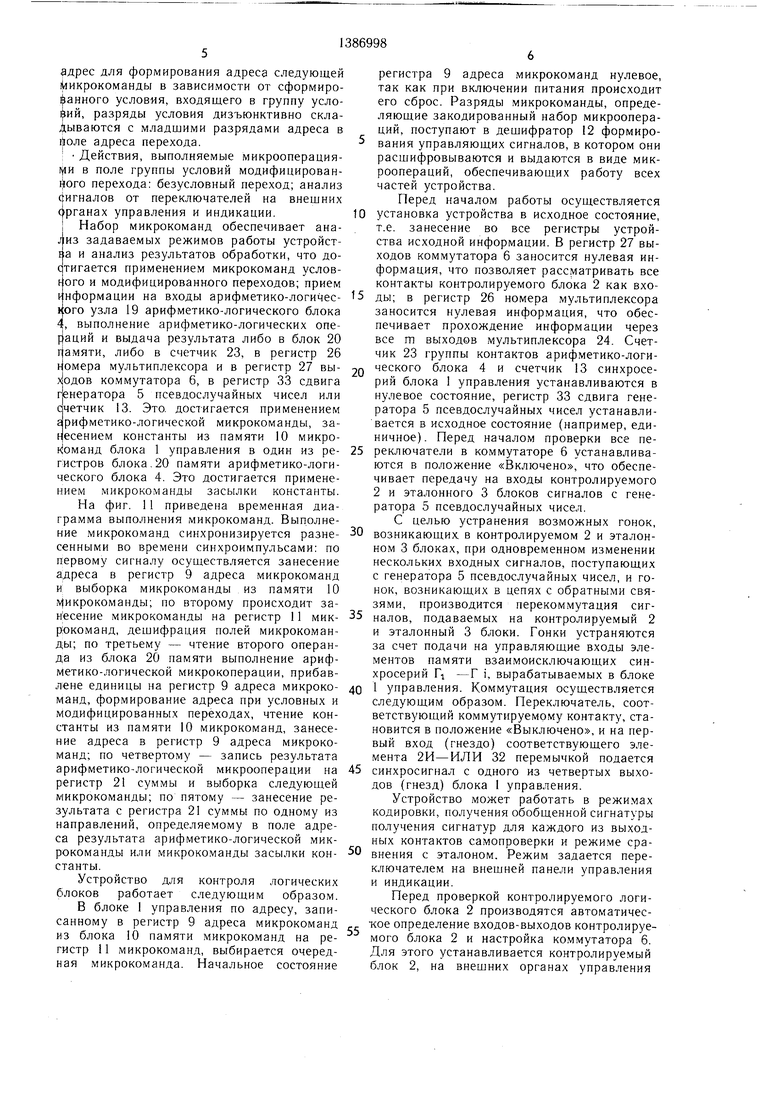

Микрокоманда засылки константы (фиг. 8) содержит поле признака КО - «00 - код операции микрокоманды; ПУ - поле установок и управляющих сигналов; ПА1 - поле адреса блока 20 памяти арифметико-логического блока 4; поле константы - значение константы в двоичном коде.

Действия, выполняемые микрооперациями в поле ПУ микрокоманд: прибавление единицы в счетчик 23 арифметико-логического блока 4; прибавление единицы в счетчик 13 блока 1 управления; сигнал сдвига (подается на регистр 33 сдвига генератора 5 псевдослучайных чисел); сброс счетчика 13 блока I управления.

Микрокоманда условного перехода (фиг. 9) содержит поле признака КО- «01 - код операции микрокоманды; ПУ - поле установок и управляющих сигналов.

Перечень и назначение микроопераций соответствует приведенным в микрокоманде засылки; поле условий - код условного перехода; поле адреса перехода - адрес следующей микрокоманды в случае выполнения условия перехода.

Действия, выполняемые микрооперациями в поле условий: безусловный переход; анализ состояния триггеров; анализ состояния тумблеров на внешних органах управления и индикации.

Микрокоманда модифицированного перехода (фиг. 10) содержит поле признака КО - «10 - код операции микрокоманды; ПУ - поле установок и управляющих сигналов.

Перечень и назначение микроопераций соответствует приведенным в микрокоманде засылки константы; поле МП - поле группы условий модифицированного перехода; поле адреса перехода определяет базовый

адрес для формирования адреса следующей Микрокоманды в зависимости от сформиро- фанного условмя, входящего в группу усло- , разряды условия дизъюнктивно складываются с младшими разрядами адреса в иоле адреса перехода.

Действия, выполняемые микрооперация- гу1И В поле группы условий модифицирован- rtoro перехода: безусловный переход; анализ Сигналов от переключателей на внещних Органах управления и индикации.

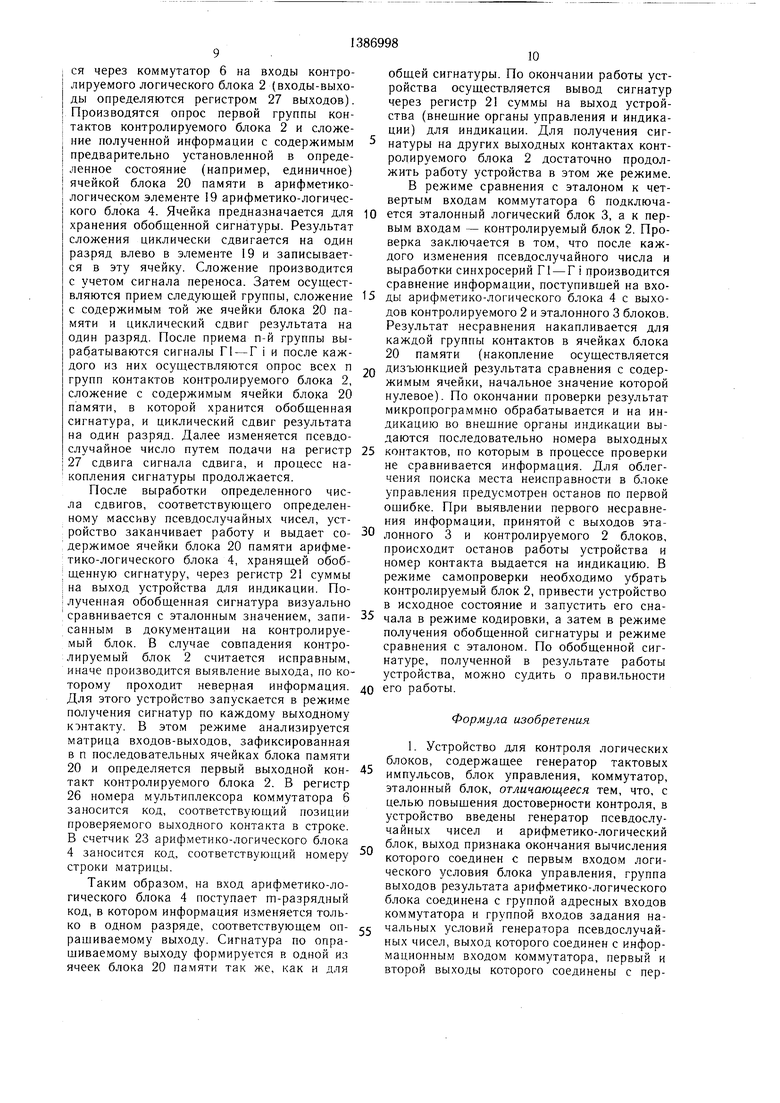

I Набор микрокоманд обеспечивает анализ задаваемых режимов работы устройст- Е.а и анализ результатов обработки, что достигается применением микрокоманд услов- еого и модифицированного переходов; прием Информации на входы арифметико-логичес- 5 ijoro узла 19 арифметико-логического блока 4, выполнение арифметико-логических операций и выдача результата либо в блок 20 памяти, либо в счетчик 23, в регистр 26 юмера мультиплексора и в регистр 27 вы- 2о Ходов коммутатора 6, в регистр 33 сдвига фнератора 5 псевдослучайных чисел или ачетчик 13. Это. достигается применением арифметико-логической микрокоманды, занесением константы из памяти 10 микрорегистра 9 адреса микрокоманд нулевое, так как при включении питания происходит его сброс. Разряды микрокоманды, определяющие закодированный набор микроопераций, поступают в дешифратор 12 формиро5 вания управляющих сигналов, в котором они расшифровываются и выдаются в виде микроопераций, обеспечивающих работу всех частей устройства.

Перед началом работы осуществляется

to установка устройства в исходное состояние, т.е. занесение во все регистры устройства исходной информации. В регистр 27 выходов коммутатора 6 заносится нулевая информация, что позволяет рассматривать все контакты контролируемого блока 2 как входы; в регистр 26 номера мультиплексора заносится нулевая информация, что обеспечивает прохождение информации через все m выходов мультиплексора 24. Счетчик 23 группы контактов арифметико-логического блока 4 и счетчик 13 синхросе- рий блока 1 управления устанавливаются в нулевое состояние, регистр 33 сдвига генератора 5 псевдослучайных чисел устанавливается в исходное состояние (например, единичное). Перед началом проверки все пеКоманд блока 1 управления в один из ре- 25 реключатели в коммутаторе 6 устанавливагистров блока-20 памяти арифметико-логического блока 4. Это достигается применением микрокоманды засылки константы. На фиг. 11 приведена временная диаграмма выполнения микрокоманд. Выполнение микрокоманд синхронизируется разнесенными во времени синхроимпульсами: по первому сигналу осуществляется занесение адреса в регистр 9 адреса микрокоманд и выборка микрокоманды из памяти 10 Микрокоманды; по второму происходит за- н есение микрокоманды на регистр 11 микрокоманд, дешифрация полей микрокоманды; по третьему - чтение второго операнда из блока 20 памяти выполнение арифметико-логической микрокоперации, прибавются в положение «Включено, что обеспечивает передачу на входы контролируемого 2 и эталонного 3 блоков сигналов с генератора 5 псевдослучайных чисел.

С целью устранения возможных гонок,

30 возникающих в контролируемом 2 и эталонном 3 блоках, при одновременном изменении нескольких входных сигналов, поступающих с генератора 5 псевдослучайных чисел, и гонок, возникающих в цепях с обратными связями, производится перекоммутация сиг35 налов, подаваемых на контролируемый 2 и эталонный 3 блоки. Гонки устраняются за счет подачи на управляющие входы элементов памяти взаимоисключающих син- хросерий Г-1 -Г i, вырабатываемых в блоке

л«не единицы на регистр 9 адреса микроко- 40 1 управления. Коммутация осуществляется манд, формирование адреса при условных и следующим образом. Переключатель, соотмодифицированных переходах, чтение константы из памяти 10 микрокоманд, занесение адреса в регистр 9 адреса микрокоманд; по четвертому - запись результата арифметико-логической микрооперации на 45 регистр 21 суммы и выборка следующей микрокоманды; по пятому - занесение результата с регистра 21 суммы по одному из направлений, определяемому в поле адреса результата арифметико-логической микрокоманды или микрокоманды засылки константы.

Устройство для контроля логических

50

ветствующии коммутируемому контакту, становится в положение «Выключено, и на первый вход (гнездо) соответствующего элемента 2И-ИЛИ 32 перемычкой подается синхросигнал с одного из четвертых выходов (гнезд) блока 1 управления.

Устройство может работать в режимах кодировки, получения обобщенной сигнатуры получения сигнатур для каждого из выходных контактов самопроверки и режиме сравнения с эталоном. Режим задается переключателем на внешней панели управления и индикации.

Перед проверкой контролируемого логического блока 2 производятся автоматичесблоков работает следующим образом. В блоке 1 управления по адресу, записанному в регистр 9 адреса микрокоманд г определение входов-выходов контролируе- из блока 10 памяти микрокоманд на ре- мого блока 2 и настройка коммутатора 6. гистр 11 микрокоманд, выбирается очередная микрокоманда. Начальное состояние

Для этого устанавливается контролируемый блок 2, на внещних органах управления

регистра 9 адреса микрокоманд нулевое, так как при включении питания происходит его сброс. Разряды микрокоманды, определяющие закодированный набор микроопераций, поступают в дешифратор 12 формирования управляющих сигналов, в котором они расшифровываются и выдаются в виде микроопераций, обеспечивающих работу всех частей устройства.

Перед началом работы осуществляется

установка устройства в исходное состояние, т.е. занесение во все регистры устройства исходной информации. В регистр 27 выходов коммутатора 6 заносится нулевая информация, что позволяет рассматривать все контакты контролируемого блока 2 как входы; в регистр 26 номера мультиплексора заносится нулевая информация, что обеспечивает прохождение информации через все m выходов мультиплексора 24. Счетчик 23 группы контактов арифметико-логического блока 4 и счетчик 13 синхросе- рий блока 1 управления устанавливаются в нулевое состояние, регистр 33 сдвига генератора 5 псевдослучайных чисел устанавливается в исходное состояние (например, единичное). Перед началом проверки все переключатели в коммутаторе 6 устанавливаются в положение «Включено, что обеспечивает передачу на входы контролируемого 2 и эталонного 3 блоков сигналов с генератора 5 псевдослучайных чисел.

С целью устранения возможных гонок,

возникающих в контролируемом 2 и эталонном 3 блоках, при одновременном изменении нескольких входных сигналов, поступающих с генератора 5 псевдослучайных чисел, и гонок, возникающих в цепях с обратными связями, производится перекоммутация сигналов, подаваемых на контролируемый 2 и эталонный 3 блоки. Гонки устраняются за счет подачи на управляющие входы элементов памяти взаимоисключающих син- хросерий Г-1 -Г i, вырабатываемых в блоке

1 управления. Коммутация осуществляется следующим образом. Переключатель, соот

ветствующии коммутируемому контакту, становится в положение «Выключено, и на первый вход (гнездо) соответствующего элемента 2И-ИЛИ 32 перемычкой подается синхросигнал с одного из четвертых выходов (гнезд) блока 1 управления.

Устройство может работать в режимах кодировки, получения обобщенной сигнатуры получения сигнатур для каждого из выходных контактов самопроверки и режиме сравнения с эталоном. Режим задается переключателем на внешней панели управления и индикации.

Перед проверкой контролируемого логического блока 2 производятся автоматичес ое определение входов-выходов контролируе- мого блока 2 и настройка коммутатора 6.

определение входов-выходов контролируе- мого блока 2 и настройка коммутатора 6.

Для этого устанавливается контролируемый блок 2, на внещних органах управления

задается режим кодировки, и блок управления запускается в режиме кодировки. При этом на регистр 33 сдвига в генераторе 5 псевдослучайных чисел выдается сигнал сдвига, вызывающий изменение информации на регистре 33 сдвига. С выходов генератора 5 псевдослучайных чисел через коммутатор 6 информация поступает на входные контакты контролируемого блока 2 (все входы-выходы контролируемого блока 2 считаются входами, так как на регистре 27 выходов коммутатора 6 все разряды установлены в нулевое состояние) и через выходы коммутатора 6 поступают на лервые входы арифметико-логического блока 4.

На вторые входы арифметико-логичес10

микрокоманд, для изменения псевдос.чу- чайного числа, и весь процесс опроса кон тактов повторяется. Количество тагов сдви- |-а определяется опытным путем и не зависит от типа контролиуремого бло1;а. Как только кодировка проведется на всем массмио псевдослучайных чисел, процесс прекратится.

Содержимое п строк матрицы вход() ходов из блока 20 памяти переписывается в п групп регистра 27 выходов. Единица в разряде регистра 27 выходов определяет контакт как выход, нуль - как вход. Единица блокирует выдачу информаци в контролируемый 2 и эталонный 3 блоки. В процессе формирования матрицы входов-выходов осукого. блока 4 поступают сигналы через ком-15 ществляется формирование обобщенной сигмутатор 6 непосредственно с выходов гене-натуры, позволяющей оперативно про

ратора 5 псевдослучайных чисел (так какверить правильность определения входов-вы

переключатели в коммутаторе б установле-ходов контролируемого блока 2.

20

30

ны в положение «Включено и эталонный блок 3 отсутствует. В арифметико-логическом элементе 19 арифметико-логического блока 4 производится поразрядное сравнение поступивщей информации от первой группы сигналов (в регистре 26 номера коммутатора и в счетчике 23 нулевая информация). В случае совпадения значения 25 сигнала, принятого с выхода генератора 5 псевдослучайных чисел и от контролируемого блока 2, данный контакт рассматривается как вход, а в случае несовпадения - как выход. Результат сравнения дизъюнктивно складывается с содержимым одной предварительно обнуленной ячейки блока 20 памяти и записывается в эту ячейку. Затем содержимое счетчика 23 увеличивается на единицу (путем выполнения микрооперации, закодированной в поле установок микрокоманды) и осуществляется опрос следующей группы контактов контролируемого блока 2. При этом результат снова дизъюнктивно складывается со следующей предварительно обнуленной ячейкой блока 20 памяти.

После опроса п групп контактов контролируемого блока 2 в п ячейках блока 20 памяти формируется матрица входов-выходов блока 2 размером п т, соответствующая общему количеству контактов контролируемого блока 2. Единичное значение 45 какого-либо разряда в матрице описывает соответствующий ему контакт контролируемого блока 2 как выход, нулевое - как вход. После опроса всех п групп контактов производится выработка синхросигнала Г1 путем

Обобщенная сигнатура формируется с.че- дующим образом. В ячейку блока 20 пгь мяти арифметико-логического блока 4, отведенную для хранения обобщенной сигнатуры, заносится определенная информация (например, единичная). После опроса каждой группы контактов контролируемого блока 2 осуществляются суммирование принимаемого кода с сод,ержимым ячейки, ци личec- кий сдвиг результата на один разряд влево и запоминание результата в этой ячейке. Сложение производится с учетом сигнала переноса, который формируется в арифметико- логическом блоке 4 на сумматоре 17 и подается на арифметико-логический элемент 19 через элемент И 18. Управление подключением к арифметико-логическому элементу 19 сигнала переноса и выполнение циклического сдвига осуществляется путем подачи

3 из блока 1 управления на элемент И 18 и арифметико-логический элемент 19 сигнала разрещения переноса и циклического сдвига, закодированного в поле арифметико-логической микрокоманды. В результате по за40 верщению подготовки входов-выходов в ячейке блока 20 памяти формируется результирующая сигнатура, характеризующая правильность кодировки, которая по завершению кодировки выдается из ячейки б,то- ка 20 памяти через регистр 21 суммы во внешнее устройство индикации для индикации. В случае, если полученная сигнатура не совпадает с эталонной, записанной в документации на контролируемый логический блок, т.е. блок неисправен, осуществляется выдача из матрицы входов-выходов, располоподачи на счетчик 13 блока 1 управления 50 женной в блоке 20 памяти, через регистр сигнала прибавлени единицы к содержи-21 суммы информации о выходных контакблока

мому счетчика 13. После этого опрос всех контактов контролируемого блока 2 повторяется. После выработки последней синхро- серии и опроса всех контактов производится выдача в генератор 5 псевдослучайных чисел на регистр 33 сдвига сигнала сдвига, закодированного в поле установок

55

тах контролируемого логического для индикации на внешнее устройство управления и индикации.

Проверка контролируемого блока 2 в режиме получения обобщенной сигнатуры осуществляется следующим образом. Код с генератора 5 псевдослучайных чисел подает0

микрокоманд, для изменения псевдос.чу- чайного числа, и весь процесс опроса кон тактов повторяется. Количество тагов сдви- |-а определяется опытным путем и не зависит от типа контролиуремого бло1;а. Как только кодировка проведется на всем массмио псевдослучайных чисел, процесс прекратится.

Содержимое п строк матрицы вход() ходов из блока 20 памяти переписывается в п групп регистра 27 выходов. Единица в разряде регистра 27 выходов определяет контакт как выход, нуль - как вход. Единица блокирует выдачу информаци в контролируемый 2 и эталонный 3 блоки. В процессе формирования матрицы входов-выходов осу5 ществляется формирование обобщенной сиг0

0

5

5

Обобщенная сигнатура формируется с.че- дующим образом. В ячейку блока 20 пгь мяти арифметико-логического блока 4, отведенную для хранения обобщенной сигнатуры, заносится определенная информация (например, единичная). После опроса каждой группы контактов контролируемого блока 2 осуществляются суммирование принимаемого кода с сод,ержимым ячейки, ци личec- кий сдвиг результата на один разряд влево и запоминание результата в этой ячейке. Сложение производится с учетом сигнала переноса, который формируется в арифметико- логическом блоке 4 на сумматоре 17 и подается на арифметико-логический элемент 19 через элемент И 18. Управление подключением к арифметико-логическому элементу 19 сигнала переноса и выполнение циклического сдвига осуществляется путем подачи

из блока 1 управления на элемент И 18 и арифметико-логический элемент 19 сигнала разрещения переноса и циклического сдвига, закодированного в поле арифметико-логической микрокоманды. В результате по за0 верщению подготовки входов-выходов в ячейке блока 20 памяти формируется результирующая сигнатура, характеризующая правильность кодировки, которая по завершению кодировки выдается из ячейки б,то- ка 20 памяти через регистр 21 суммы во внешнее устройство индикации для индикации. В случае, если полученная сигнатура не совпадает с эталонной, записанной в документации на контролируемый логический блок, т.е. блок неисправен, осуществляется выдача из матрицы входов-выходов, располо0 женной в блоке 20 памяти, через регистр 21 суммы информации о выходных контакблока

тах контролируемого логического для индикации на внешнее устройство управления и индикации.

Проверка контролируемого блока 2 в режиме получения обобщенной сигнатуры осуществляется следующим образом. Код с генератора 5 псевдослучайных чисел подаетI ся через коммутатор 6 на входы контролируемого логического блока 2 (входы-выходы определяются регистром 27 выходов). Производятся опрос первой группы контактов контролируемого блока 2 и сложение полученной информации с содержимым предварительно установленной в определенное состояние (например, единичное) ячейкой блока 20 памяти в арифметико- логическом элементе 19 арифметико-логичесобщей сигнатуры. По окончании работы устройства осуществляется вывод сигнатур через регистр 21 суммы на выход устройства (внешние органы управления и индикации) для индикации. Для получения сигнатуры на других выходных контактах контролируемого блока 2 достаточно продолжить работу устройства в этом же режиме. В режиме сравнения с эталоном к четвертым входам коммутатора 6 подключакого блока 4. Ячейка предназначается дляю ется эталонный логический блок 3, а к перхранения обобщенной сигнатуры. Результатвым входам - контролируемый блок 2. Просложения циклически сдвигается на одинверка заключается в том, что после кажразряд влево в элементе 19 и записывает-дого изменения псевдослучайного числа и

ся в эту ячейку. Сложение производитсявыработки синхросерий Г1 - Г i производится

с учетом сигнала переноса. Затем осущест-сравнение информации, поступившей на вховляются прием следующей группы, сложение15 ды арифметико-логического блока 4 с выхо|с содержимым той же ячейки блока 20 па-дов контролируемого 2 и эталонного 3 блоков.

I мяти и циклический сдвиг результата наРезультат несравнения накапливается для

один разряд. После приема п-й группы вы-каждой группы контактов в ячейках блока

рабатываются сигналы Г1 - Г i и после каж-20 памяти (накопление осуществляется

дого из них осуществляются опрос всех п дизъюнкцией результата сравнения с содергрупп контактов контролируемого блока 2,жимым ячейки, начальное значение которой

сложение с содержимым ячейки блока 20нулевое). По окончании проверки результат

памяти, в которой хранится обобщеннаямикропрограммно обрабатывается и на инсигнатура, и циклический сдвиг результатадикацию во внещние органы индикации вына один разряд. Далее изменяется псевдо-даются последовательно номера выходных

случайное число путем подачи на регистр25 контактов, по которым в процессе проверки

27 сдвига сигнала сдвига, и процесс на-не сравнивается информация. Для облегкопления сигнатуры продолжается.чения поиска места неисправности в блоке

После выработки определенного чис-управления предусмотрен останов по первой

ла сдвигов, соответствующего определен-ошибке. При выявлении первого несравненому массиву псевдослучайных чисел, уст-ния информации, принятой с выходов этаройство заканчивает работу и выдает со-30 лонного 3 и контролируемого 2 блоков,

держимое ячейки блока 20 па.мяти арифме-происходит останов работы устройства и

тико-логического блока 4, хранящей обобщенную сигнатуру, через регистр 21 суммы на выход устройства для индикации. По- I лученная обобщенная сигнатура визуально сравнивается с эталонным значением, запи- 35 санным в документации на контролируемый блок. В случае совпадения контролируемый блок 2 считается исправным, иначе производится выявление выхода, по которому проходит неверная информация, дд его работы. Для этого устройство запускается в режиме получения сигнатур по каждому выходному к )нтакту. В этом режиме анализируется матрица входов-выходов, зафиксированная в п последовательных ячейках блока памяти

номер контакта выдается на индикацию. В режиме самопроверки необходимо убрать контролируемый блок 2, привести устройство в исходное состояние и запустить его сначала в режиме кодировки, а затем в режиме получения обобщенной сигнатуры и режиме сравнения с эталоном. По обобщенной сигнатуре, полученной в результате работы устройства, можно судить о правильности

Формула изобретения

целью повыщения достоверности контроля, в устройство введены генератор псевдослучайных чисел и арифметико-логический

26 номера мультиплексора коммутатора 6 заносится код, соответствующий позиции проверяемого выходного контакта в строке.

В счетчик 23 арифметико-логического блокаблок, выход п ризнака око нчания вьшислен ия

4 заносится кол. соответствующий Hoiweov которого соединен с первым входом логического условия блока управления, группа выходов результата арифметико-логического блока соединена с группой адресных входов коммутатора и группой входов задания на- ко в одном разряде, соответствующем оп- чальных условий генератора псевдослучай- рашиваемому выходу. Сигнатура по опра-ных чисел, выход которого соединен с инфорщиваемому выходу формируется в одной измационным входом коммутатора, первый и

ячеек блока 20 памяти так же, как и длявторой выходы которого соединены с пер4 заносится код, соответствующий номеру строки матрицы.

Таким образом, на вход арифметико-логического блока 4 поступает т-разрядный код, в котором информация изменяется тольобщей сигнатуры. По окончании работы устройства осуществляется вывод сигнатур через регистр 21 суммы на выход устройства (внешние органы управления и индикации) для индикации. Для получения сигнатуры на других выходных контактах контролируемого блока 2 достаточно продолжить работу устройства в этом же режиме. В режиме сравнения с эталоном к четвертым входам коммутатора 6 подключается эталонный логический блок 3, а к перпроисходит останов работы устройства и

его работы.

номер контакта выдается на индикацию. В режиме самопроверки необходимо убрать контролируемый блок 2, привести устройство в исходное состояние и запустить его сначала в режиме кодировки, а затем в режиме получения обобщенной сигнатуры и режиме сравнения с эталоном. По обобщенной сигнатуре, полученной в результате работы устройства, можно судить о правильности

.

Формула изобретения

целью повыщения достоверности контроля, в устройство введены генератор псевдослучайных чисел и арифметико-логический

блок, выход п ризнака око нчания вьшислен ия

вым и вторым информационными входами арифметико-логического блока соответственно, третий информационный вход которого соединен с первым выходом поля управления блока управления, второй выход поля управления блока управления соединен с управляющим входом коммутатора, третий выход поля управления блока управления соединен с синхровходом арифметико-логического блока, четвертый выход поля управления блока управления соединен с синхро- входом генератора псевдослучайных чисел, вход пуска устройства соединен с вторым входом логического условия блока управления, первый выход генератора тактовых импульсов соединен со стробирующим входом арифметико-логического блока, второй выход генератора тактовых импульсов соединен с синхровходом блока управления, пятый выход поля управления которого соединен с синхровходом коммутатора, первая группа входов-выходов которого соединена с группой входов-выходов эталонного блока, вторая группа входов-выходов коммутатора является группой входов-выходов устройства для подключения к контролируемому блоку, причем блок управления содержит блок модификации адреса перехода, регистр адре- са микрокоманды, блок памяти микрокоманд, регистр микрокоманд, дешифратор сигналов управления, счетчик, дешифратор, группу формирователей импульсов, причем первый вход логического условия блока управления соединен с первым входом блока модифи- кации адреса, второй вход логического условия блока управления соединен с вторым входом блока модификации адреса, выход которого соединен с информационным входом регистра адреса микрокоманды, синхровход которого соединен с синхро- входом блока управления и с синхровхо- дами регистра микрокоманды и дешифратора сигналов управления, выход регистра адреса микрокоманды соединен с адресными входами блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманды и первым выходом поля управления блока управления, группа выходов регистра микрокоманды соединена с группой информационных входов блока модификации адреса и дешифратора сигналов управления, первый, второй и третий выходы которого являются вторыми, третьими и четвертыми выходами поля управления блока управления соответственно, четвертый выход дешифратора сигналов управления соединен со стро- бируюшим входом блока модификации адреса, пятый выход дешифратора сигналов управления соединен со счетным входом счетчика, разрядные выходы которого соединены с информационным входом дешифратора, выходы которого через соот- ветствуюшие формирователи импульсов группы образуют пятый выход поля управления блока управления.

фиг.:

(pU2.

Ц и г. 5

37

г

38

39

фиг. 6 Арадзметино-логическая минрономанда

Поле признано.

Минрономанди засылни нонстоиты

Лоле признана

Фа.В

Минрономаида дслодно о перехода

поле, признана

Фи.9

П

.2

«/

22

МинрономанУа ноди1рициро анного перехода

Лоле признака

ГТ

П.

П

п.

П

Фиг. Ю

П.

П

ГТ

П

П

п.

П

.J

щиг.Т1

| Устройство для контроля логических блоков | 1983 |

|

SU1149266A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1154672, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-02—Подача