которого соединен с третьим входом четвертого элемента И-НЕ, выход которого соединен с V-входом третьего DV-триггера и с пятнадцатым входом блока формирования результата шестнадцатый вход которого соединен с S-входом четвертого RS- триггера, прямой и инверсный выходы суммы третьег DV-триггера подключены соответственно к R и S-входам четвертого RS-триггера, первый и второй выходы бцока формирования результата являются соответственно выходами прямых и ин-. верснИх значений результата устройства

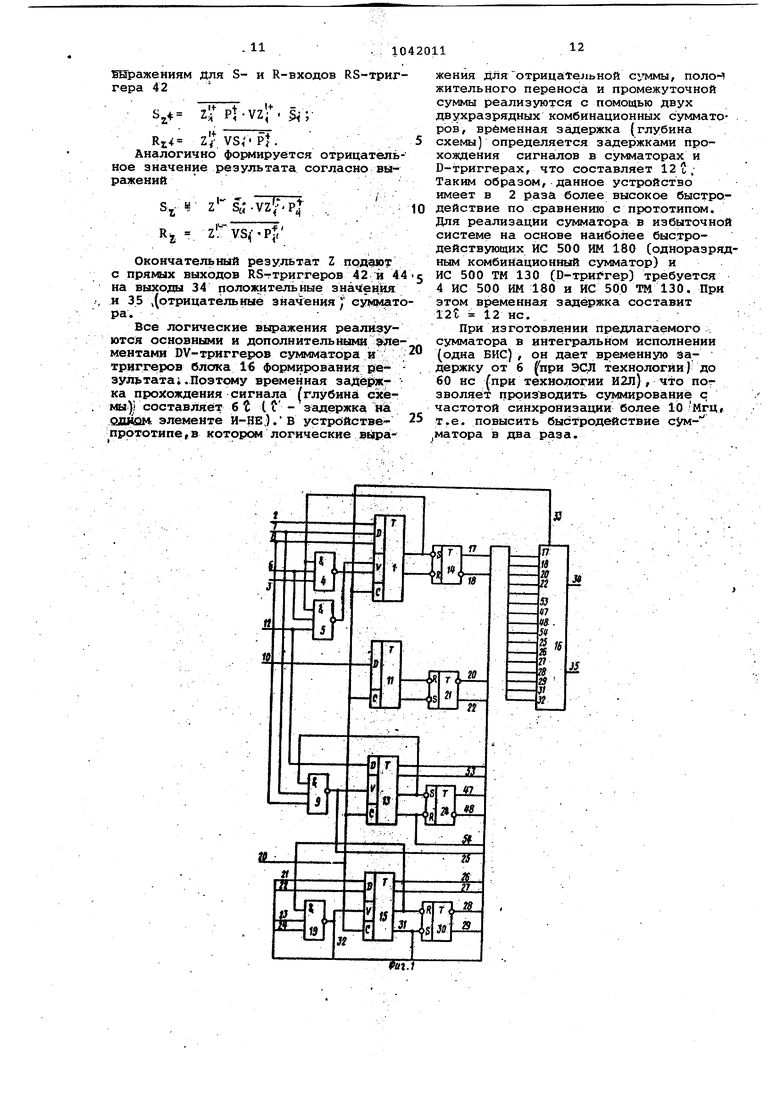

2. Сумматор по П.1, о т л и ч аю щи и с я тем, что блок формирования результата содержит два DV-триггера, два RS-триггера и десять элементов И-НЕ, причем С-входы DV-триггеров подключены к первым входам первых шести элементов и к входу синхронизации блокаформирования результата, первый и второй входы которого подключены соответственно к первым D -входам первого и второго DV-триггеров, вторые D-входы которых подк.точены соответственно к третьему и четвертому входам блока формирования результата, пятый вход которого подключен к вторым входам третьего и шестого элементов И-НЕ, а шестой вход - к вторым входам второго и пятого элементов И-НЕ, седьмой вход блока формирования результата подключен к первым входам седьмого и вось мого элементов И-НЕ, а восьмой вход блока формирования результата - к первым входам девятого и десятого элементов И-НЕ, вторые :входы седьмого и девятого элементов И-НЕ соединены с инверсным выходом переноса первого DV-триггера, вторые входы восьмого и десятого элементов И-НЕ соедидинены с инверсным выходом переноса второго DV-триггера, девятый вход блока формирования результата подключен к второму входу первого и третьему входу шестого элементов И-НЕ, десятый вход блока формирования результата подключен к третьему входу первого и четвертому входу шестого элементов И-НЕ, одиннадцатый вход блока формирования результата подключен к третьему входу третьего и второму входу четвертого элементов И-НЕ, двенадцатый вход блока формирования результата подключен к четвертому и пятому входам первого элемента И-НЕ, к первому V-входу первого DV-триггера, к третьему входу второго элемента И-НЕ и к пятому входу шестого элемента И-гНЕ, тринадцатый вход блока формирования результата подключен к третьим входам восьмого и девятого элементов И-НЕ, третьи входы седьмого и десятого элементов И-НЕ соединены с четырнадцатым входом блокэ формирования результата, пятнадцатый вход которого подключен к четвертому входу второго и третьему входу пятого элементов И-НЕ, а шестнадцатый вход блока формирования результата подключен к пятому входу второго и к четвертому входу пятого элементов И-НЕ, шестые входы первого и второго элементов И-НЕ подключены к выходу седьмого элемента И-Н.Е и к второму . V-входу первого DV-rтриггера, прямой

выход суммы которого подключен к первому Rrвxoдy первого RS-триггера и к седьмьи входам первого и второго элементов И-НЕ, восьмые входы которых 9°единены с прямым выходом переноса первого DV-триггера, выход девятого элемента И-ЧЕ соединен с третьим входом второго элемента И-НЕ, первого и второго элементов И-НЕ подключены соответственно к первому и второму S-входам первого RS-триггера, второй R-вход которого соединен с выходом третьего блока формирования результата, выход десятого элемента И-НЕ соединен с первым V- входом второго DV-триггера, с третьим входом четвертого и с пятым входом пятого элементов И-НЕ, выход восьмого элемента И-НЕ подключен к второму V-входу второго DV-триггера, к четвертому входу четвертого и шестому входу пятого элементов И-НЕ, прямой выход переноса второго DV-триггера подключен к пятому входу четвертого и седьмому входу пятого

элементов И-НЕ, прямой выход суммы второго DV-триггера соединен с шестым входом четвертого и восьмым входом пятого элементов И-НЕ и с первым R-входом вторЬго RS-триггера, второй jl-вход КОТОРОГО подключен к выходу liuecToro элемента И-НЕ, первый и второй S-входы соединены с выходами соответственно четвертого и пятого элементов И-НЕ, а прямой выход является вторым выходом блока формирования результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения в избыточной двоичной системе счисления | 1981 |

|

SU1587494A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| Многофункциональный настраиваемый триггер | 1984 |

|

SU1238205A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Устройство для обнаружения и исправления ошибок сумматора | 1982 |

|

SU1038946A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

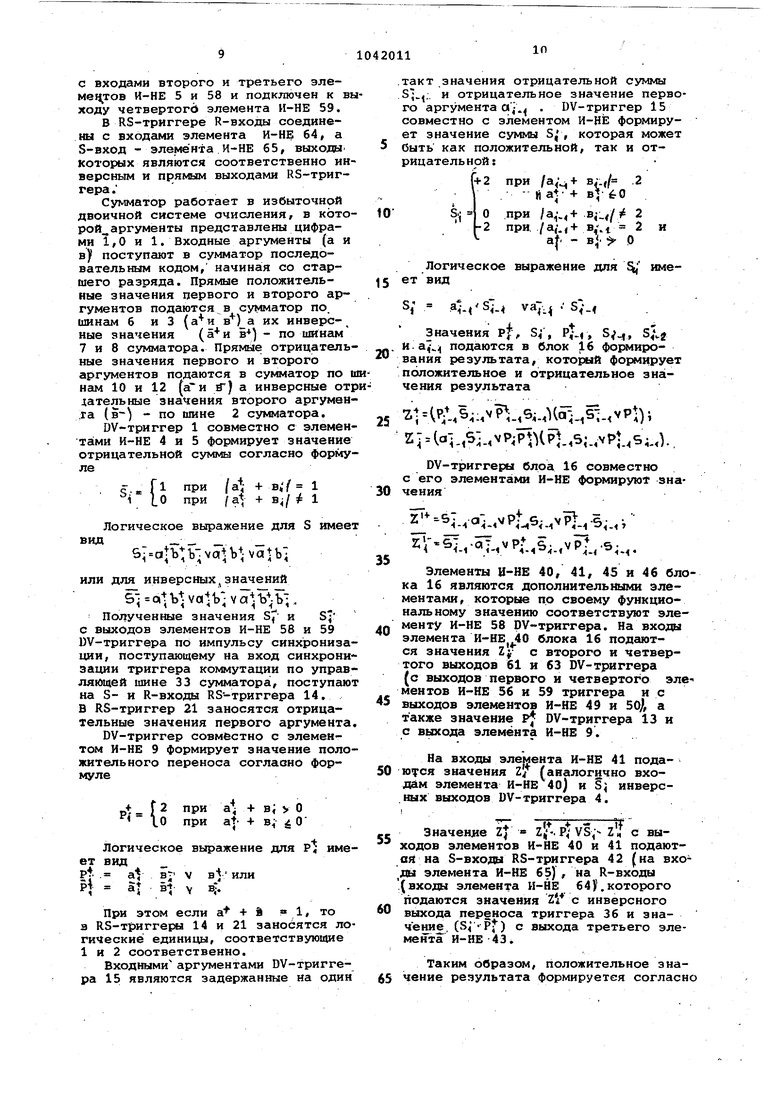

1. СУМ14АТОР В ИЗБЫТОЧНОЙ ДВОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ, содержащий -блок формирования результата, . два DV-триггера, D-триггер и три RS-триггера, причем вход|Ь1 синхронизации блока формирования результата, DV-триггеров,и D-триггера подктаочег ны к шине синхронизации устройства, S- .и R-вхбды первого, второго и трртьего RS-триггеровподключены соответственно к прямому и инверсном выходам суммы первого DV-триггера, D-триггера и второго ВУ-триггера, D-вход D-триггера подключен к входу прямьас отрицательных значений пер-; вого слагаемого, отличают ийс я тем, что, с целью повышения быстродействия за счет уменьшения количества каскадов, в цепи получения суммы, сумматор содержит третий DV-триггер, четвертый RS-триггер и четыре элемента И-НЕ, причем вход; прямых положительных значений слагаемого устройства соединён с rtepвым входом первого элемента К-НЕ к .о первым входом второго элемента И-НВ, второй вход которого соединен с D-входом второго DV-триггера и с входом прямых отрицательных значений-второго слагаемого устройства, входы инверсных положительных значений первого и второго слагаемых устройств сое.динены, соответственно с первым и вторым входами третьего элемента И-НЕ и с первым и вторым D-входами первого DV Tpnrrepa, третий U-вход которого .соединен с входом инверсных отрицательйых значений второго слагаемого устройства, вход прямых положительных значений второго слагаемого устройства соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым V-входом первого DV-триггера, второй V-вход которого соединен с выходом второго элемента И-НЕ, третий вход которого соединен с третьим входом первого элемента И-НЕ и с S-входом первого RS-триггера, прямой выход которого соединен с первым В-входом третьего DV-триггера и с первым входе блока формирования результата, второй вход § которого подключен к инверсному .выходу первого RS-триггера и к первО му входу четвертого элемента И-НЕ, второй вход которого соединен с прямым выходом второго RS-триггера и с третьим входом блока формирования результата, четвертый вход которого , соединен с вторым О-входом третьего DV-триггера, прямой и инверсный выхо ды переноса которого подключены соответственно к пятому и шестому вхо.дам блока формирования результата, седьмой и восьмой входы которого сое | динены соответственно с прямым и инверсным выходами третьего RS-триггера, R-вход которого соединен с девятым входом блока формирования ре зультата, десятый вход которого соединен с V-вхрдом второго DV-триггера и с. выходом третьего элемента И-НЕ, третий вход которого подклйчен к S-входу третьего RS-триггера, прямой и инверсный выходы переноса второго DV-триггера соединены соответственно с одиннадцатым и двенад- цатым входами .блока формирования результата, тринадцатый и четырнадцатый входы которого соединены соответственно с инверсным и прямым выходами четвертого RS-триггера, R-вход

1

Изобретение относитсгя к вычислительной технике и может быть использовано в вычислительных машинах и

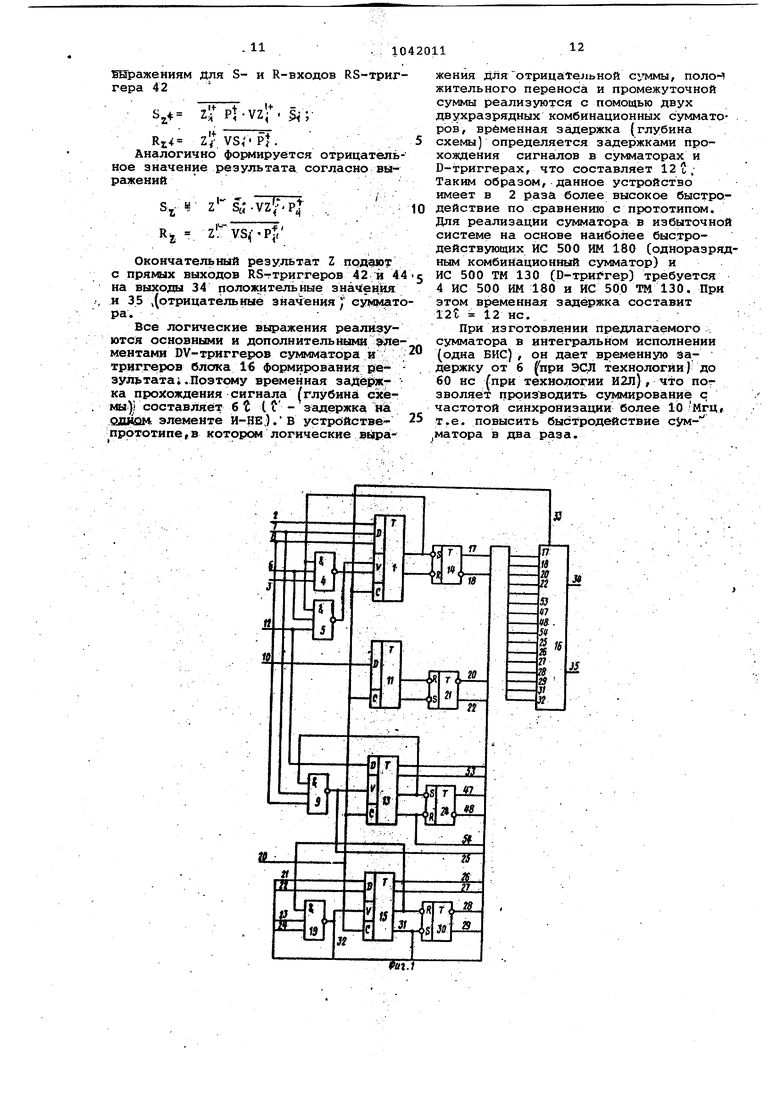

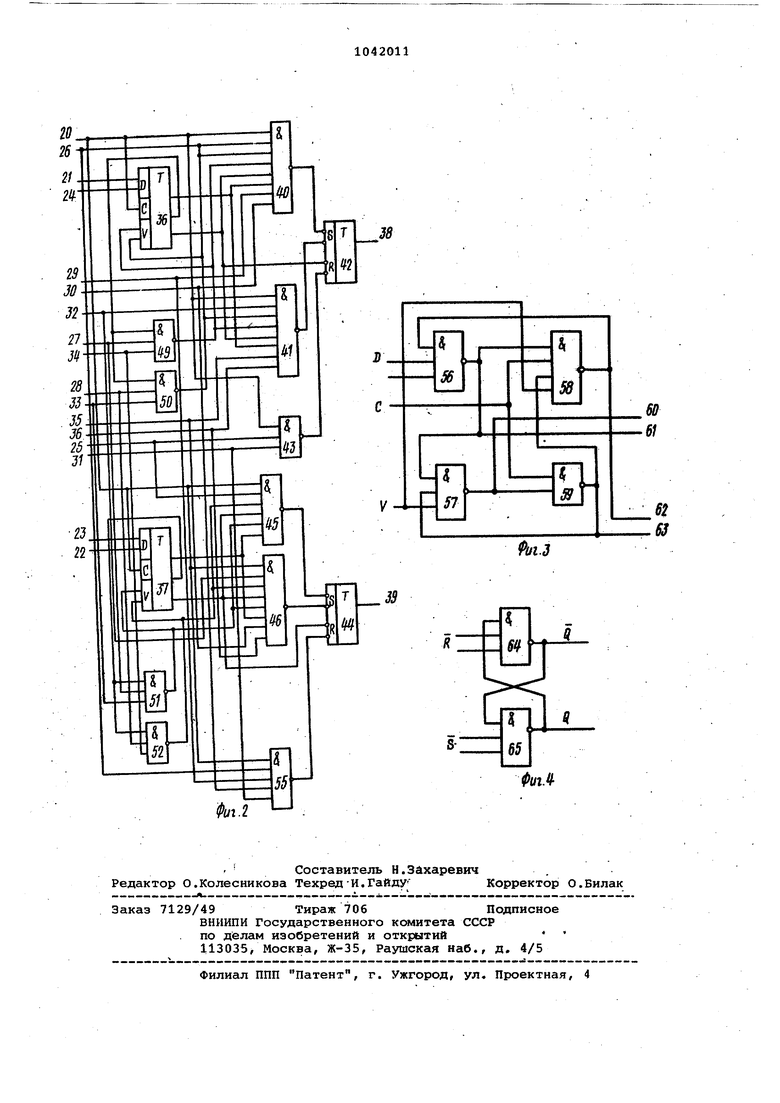

устройствах, работающих в избыточной двоичной системе счисления с цифрами 1,0 и 1. Известно устройство для параллельного сложения двух чисел в избыточно двоичной системе счисления, содерж4щее в каждом разряде блоки формирова ния отрицательной суммы, положител ной суммы, отрицательного переноса, положительного переноса и результатаЫ. Недостатком известного устройства является большое количество оборудова ния, требуемого для его реализации, и кроме того, недостаточное быстродействие, определяемое задержками.срс тавных частей устройства (глубино схемы). . Наиболее близким к изобретению ЯВляется устройство Для сложения в избыточной двоичной системе счисленил/ содержащее блоки формирования отрицательной суммы и положительного nepeTio са, входы которых соединенй с входными шинами положительных значений п рвого и второго аргументов и отрицательных значений второго аргумента первый и второй элементы задержки, входы которых подключены соответствен но к выходу блока формирования отщцательной суммы и к входной шине отрицательных значений первсзго аргумента, блоки формирования положите ль нрй суммы и отрицательного переноса/ ,. входы которых подключены к выходам блока формирования положительного переноса, первого и второго элементов задержки, третий элемент задерж-г ки, вход которого соединен с выходом блока формирования положительной суммы/ и блок Формирования результата соединенный с выходами блока формирования отрицательного переноса и третьего элемента задержки з.. Однако это устройство отличается недостаточно высоким быстродейстг вием, определяемым задержками логических элементов к триггеров устрой ства (глубина схемы равна Ю). Цель изобретения - повышение . быстродействия сумматора. Для достижения поставленной цели сумматор в избыточной двоичной системе счисления, содержащий блок формирования результата, два ВУ-триг repa/D-триггер и три КЗ гтрип ера, . причем входы синхронизации блока мироваиия результата, ВУ-триггвроэ #Г и D-триггера подключены к шиие сиц; с т ронизации устройства, S- и К-вх6да| IliepBoro/ второго и третьего RS-Tpi геров подключены соответственно к Ijпрямому и инверсному выходам суммы первого DV-триггера:/ D-триггера, и второго DV-триггера, D-вход D-триггера подключен к входу пря- ( мых отрицательных значений первого слагаемого/- содержит третий -РУ-трййггер, четвертый RS-триггер.и четыре элемента И-НЕ, причем вход пря1«ос положительных значений первого емого устройства соединен с первим входом первого элемента И-НЕ и с первым входом второго элемента И-НЕ второй вход которого соединен с D-входом второго 1)V-триггера и с входом прямых отрицательных значений второго слагаемого устройства, входы инверсных положительных значений первого и второго слагаемых устройства соединены соответственно с первым и вторым входами третьего элемента И-НЕ и с первым и вторым D-входами первого DV-триггера, третий D-вход которого соединен с входом инверсных отрицательных значений второго слагаемого устройства, вход прямых положительных значений второго слагаемого устройства соединен с вторым входом первого элемента И-НЕ, выход которого соединен с первым V-входом первого DV-триггера, второй V-вход которого соединен с выходом второго элемента И-НЕ, третий вход которого соединен с третьим входом первого элемента И-НЕ и с S-входом первого RS-триггера, прямой выход которого соединен с первым D-вхойом третьего DV-триггера и с первым входом блока формирования результата, второй вход которого подключен к инверсному выходу первого .RS-триггера и к первому входу четвертого элемента И-НЕ, второй вход которого соединен с прямым ВЫХОДСЯ4 второго RS-триггера и с третьим входом блока формирования результата, четвертый вход которого соединен с вторым D-вхбдом третьего DV-триггера, прямой и инверсный выходы переноса которого подключены соответственно к пятому и шестому входам блока формирования результата, седьмой и восьмой входы которого соединены соответственнее с прямым и инверсным выходами третьего RS-триггера, R-вход которого соединен с девятым входом блока формиро-. вания результата/ десятый вход которого соединен с V-входом второго DV-триггера и с выходом третьего элемента И-НЕ, третий вход которого подключен к S-входу третьего RS-триггера, прямой и инверсный выходи переноса второго DV-триггёра соединены соответственно с одиннадцатым и двенадцатым входами блока формироба йия результата/ тринадцатый и.четырнадцатый входы которого соединены .со, ответственно с инверсным и прямым выходами четвертого RS-триггера/ R-бход которого соединен с третьим входом четвертого элемента И-НЕ, выход которого соединен с V-входом третьего DV-триггера и с пятнадцатым входом блока формирования результата, шестнадцатый выход которого соединен с S-входОм четвёртого RS-триггера, прямой и-инверсный вы- ходы суммы третьего DV-триггера подключены соответственно к R и 6-входам четвертого RS-триггера, первый и второй выходы блока фЬрмиро вания результата являются соответственно выходами прямых и инверсных значений результата устройства. Кррме того, блок формирования ре зультата содержит два pv-триггера, два RS-триггера и десять элементов И-НЕ, причем С-входы DY-триггеров подключены к первым входам первых шести элементов И-НЕ и к входу синхронизации блока формирования результата, первый и второй входы которого подключены соответственно, К первым D-входам первого и второго DV-триггеров, вторые D-входы которых подключены соответственно.к третьему и четвертому входам блокад формирования результата, пятый вход которого подключен к вторым входам третьего и шестого элементов И-НЁ, а шестой вход - к вторым входам вто рого и пятого элементов И-НЕ, седьм вход блока формирования результата подключен, к первым входам седьмо го и восьмого элементов И-НЕ, а вос мой вход блока формирования результата - к первым входам девятого и десятого элементов И-НЕ, вторые вхо ды седьмого и девятого элементов И-НЕ соединены с инверсным шлходом переноса первого DV-триггера, вторы входы восьмого и десятого элементов И-НЕ соединены с инверсным выходом переноса второго DV-триггера, девятый вход блока .формирования результата подключен к второму входу перв го и третьему входу шестого элементов И-НЕ, десятый вход блока формирования результата подключен к трет ему входу первого и четвертому вход шестого элементов И-НЁ, одиннадцаты вход блока формирования результата подключен к третьему входу третьего и второму входу четвертого элементов И-НЕг двенадцатый вход блока формирования результата подключен к четвертому и пятому входам первого элемента И-НЕ, к первому V-входу первого DV-триггера, к третьему входу второго элемента И-НЕ и к пятому входу шестого элемента И-НЕ, тринадцатый вход блока формирования результата подключен х третьим входам восьмого и девятого элемен-г; тов И-НЕ, третьи входы седьмого и десятого элементов И-НЕ соединены с четырнадцатым входом блока форми- рования результата, пятнадцатый вход которого подключен к четвертр(му входу второго и третьему входу пя того элементов И-НЕ, а шестнадцатый вход блока формирования результата подключен к пятому входу второго и к четвертому входу пятого элементов И-НЕ, шесты е входы первого и второг элементов И-НЕ подключены к выходу седьмого элемента И-НЕ и к второму V-входу первого DV-триггера, прямой выход суммы которого подключен к первому R-входу первого RS-триггера и к седьмым входам первого и второго элементрв И-НБ, восьмые входы которых соединены с прямым выходомпереноса первого DV-триггера, выход девятого элемента И-НЕ соединен с третьим входом второго элемента И-НЕ, выходы лервого и второго, элементов И-НЕ подключены соответственно к первому и вторсму Б-входам первого RS-триггера, второй R-вход которого соединен с выходом третьего блока формирования результата, выход десятого элемента И-НЕ соединен с первым V-входом второго DV-триггера, с третьим входом четвертого и q. пятым входом пятого элементов: И-НЕ,. выход восьмого элемента И-НЕ подключен .к второму V-входу второго DV-триггера, к четвертому входу четвертого и шестому входу пятого элементов И-НЕ, прямой выход переноса второго DV-триггера подключен к пятому входу четвертого и седьмому входу пятого элементов И-НЕ, прямой выход суммы второго DV-триггера соединен с шестым входом четвертого, восьмым входом пятого элементрв И-НЕ, и с первым R-входом второго RS-триггера, второй R-вход которого подключен к выходу шестого элемента И-НЕ, первый и второй S-входы соединены с выходами соответственно четвертого ипятого элементов И-НЕ, а прямой выход является вторым выходом блока формирования результата. На фиг.1 приведена структурная схема сумматора; на фиг.2 - функциональная схема блока формирования результата, на фиг.З и.фиг.4 - функциональные схемы DV-триггера и RS-триггера. Первый D-вход первого DV-триггера 1 соединен с входной шиной 2 инверсных отрицательных значений второго слагаемого. Входная шина 3 прямых положительных значений второго слагаемого подключена к второму входу первого элемента И-НЕ 4, первый вход которого соединен с первым входом второго элемента И-НЕ 5 и с входной шиной б прямых положительных значений первого слагаемого. Входные шины 7 и 8 инверсных положительных значений первого и второго слагаемых подключены к второму и третьему D-входам т DV-триггера 1 и к nepBOv му и второму входам третьего элемента И-НЕ 9. Входная-шина 10 прямых отрицательных значений первого слагаемого подключена к О-входу D-триггера 11, а входная Шина 12 прямых отрицательных значений второго слага емого подключена к второму входу второго элемента И-НЕ 5 и к D-входу второго DV-триггера 13. Выходы перво го и второго элементов И-НВ 4 и 5 соединены с входами DV-триггера 1, прямой выход суммы которого соединен с третьими входами элементов И-НЕ 4 и 5 и с S-входом RS-триггера 14, R-вход которого соединен с, инверсным выходом cymta ВУ-триггера 1. Первый D-вход т1риггера 15 соединен с первым входом блока 16 формирования результата и с прямым выхо дом 17 RS-триггера 14, инверсный выход 18 которого подключен к первому входу четвертого элемента И-НБ 19 и к второму входу блока 16 формирования результата, четвертым входом сое диненного со вторым Й-входом DV-триг гера 15 и с инверсным выходом 20 RS-триггера 21, прямой выход 22 которого соединен с третьим входсян бло ка 16 формирования результата и с вт рым входом четвертого элемента И-НЕ 19. Третий вход которого соединен с R-входом RS-триггера 23 и с прямым выход(%1 суммы DV-триггера 15. Прямой и инверсный выходы суммы триггера 11 соединены соответственно с R- и S-вxoдclми RS-триггера 21, а прямой выход суммы триггера 13 соединен с S-входами RS-триггера 24 и с треть им входом третьего элемента И-НЕ 9.. Одиннадцатый и двенадцатый входы блока 16 формирования результата сое динены с. прямьзм и инверсным выходами RS-триггера 24. V-вход DV-триггера 13 соединен с выходом 25 третье го элемента И-НЕ 9 и с десятым входо блока 16 формирования результата, пятый и шестой входы которого соеди-л нены соответственно с. прямым и инвер ным выходами переноса 26 и 27 блока 4 Инверсный и прямой выходы 28 и 29 RS-триггера 30 соединены соответатвенно с тринадцатым и четырнадцатым входами блока 16 формирования резуль тата, шестнадцатым входом соединенного с S-входом RS-триггера 30 и с инверсным выходом суммы 31 триггера 15, прямой выход суммы котороголч соеданен с R-входом RS-триггера 30 и с лервым входом четвертого элемента И-НЕ 19,выход 32 которого подключен к пятнадцатсаду вхбду блока 16 формирования результата и к V-входу DV-триггера 15. Входы синхронизации DV-триг геров соединены с шиной 33 управления импульсов сукматора. Выходы 33, 34 и 35 блока 16 формирования ре-Г зультата являются выводами соответрственно положительных и отрицательных значений результата сумматораПервый и вто1рой входы 17 и 18 бло ка 16 формирования результата сое- ... динены с первыми D-входами DV-триг-. геров 36 к 37, третий и четвертый входы 20 и 22 блока 16 подключены к вторым D-входам DV-триггербв соответственно 37 и 36. Прямой выход суммы триггера 36 соединен с первыми входами седьмого и девятого эле ментов И-НЕ 38 и 39, выходы которых соединены с входами первого и второго элементов И-НЕ 40 и 41 и с V-входами DV-триггера 36, инверсный выход суммы которого соединен с входами первого и второго элементов И-НЁ 40 и 41 и с вторым R-входом RS-триггера 42, первый R-вход которого соединен с выходом третьего элемента И-НЕ 43, а его S-входы подключены к выходам первого и второго элементов И-НЕ 40 .и 41. Инверсный выход переноса триггера 36 соединен с вхо- . дами первого и второго элементов И-НЕ 40 и 41, а его вход синхронизации .соединен с первыми входами первого и второго и третьего элементов И-НЕ 40, 41 и 43 и подключен к входу синхронизации 33 блока, выходы .34 и 35 которого являются П.РЯМЫМИ ВЫХО,дами RS-триггеров 42 и 44 соответственно. Одиннадцатый вход блока 16 формирования результата соединен с входом первого элемента И-НЕ 45 и с третьим входом пятого элемента И-НЕ 43. второй вход которого соединен с пятым входом 28 ;блока. 16 и с входом шестого элемента И-НЕ 46. Входы элементов И-НЕ 41 и 46 переключены к шестому, шестнадцатому и пятнадцатому входам 27, 31 и 32 блока 16, седьмой и восьмой входаа 47, 48 KOTopot-o подключены к вторым входам соответственно седьмого, восьмого и девятого, десятого элементов И-НЕ 49,50, 51, 52. Двенадцатый, девятый и десятый входы 53, 54 и 25 блока 16 подключены соответственно к четвертому, вторси у и третьему входам первого элемента И-НЕ 40 .и к Пятому, третьему и четвертому входам шестого элемента И-НЕ 55, третий вход восьмого элемента И-НЕ 50 соединен с тринадцатым .входом 28 блока 16 и с третьим входом девятого элемента И-Н 51, третий вход седьмого элемента И-НЕ 49 соединен с третьим входом десятого элемента И-НЕ 52 и с iчетырнадцатым входом 29 блока 16. В каждом DV-триггере второй и третий входы его первого элемента И-НЕ 56 являются D-входами триггера, его V-входы соединены с входами второго и третьего элементов И-НЕ 57 и 58, а вход синхро11изации триггера соединен с входами третьего и четвертого элементов И-НЕ 58 и 59. Выход второго элемента И-НЕ 57 подключен к входу четвертого элемента И-НЕ 59 и соединен с прямым выходом 60 переноса триггера, инверсный выход переноса 61 которого соединен с входами второго и третьего элементов И-НЕ 57 и 58 и подключен к выходу первого элемента И-НЕ 56. Выход третьего элемента И-НЕ 58 соединен с первым входом первого элемента И-НЕ 56 и подключен к. прямому выходу суммы 62 триггера, инверсный выход суммы 63 которого соединен с входами второго и третьего элемецтов И-НЕ 5 и 58 и подключен к в ходу четвертого элемента И-НЕ 59. В RS-триггере R-входы соединены с входами элемента И-НЕ 64, а S-вход - элемента И-НЕ 65, выходы которых являются соответственно ин версным и п{эямьш выходами RS-триггера. Сумматор работает в избыточной двоичной системе счисления, в кото рой аргументы представлены цифрами 1,0 и 1. Входные аргументы (а и вУ поступают в сумматор последовательным кодом, начина:я со старшего разряда. Прямые положительные значения первого и второго аргументов подаются в сумматор по. шинам 6 и 3 ( в ) а их инверс-, ные значения ( i) - по шинам 7 и 8 сумматора. Прямые отрицатель ные значения первого и второго аргументов подаются в сумматор по нам 10 и 12 и ) а инверсные от дательные значения второго аргумен та (в) - по шине 2 сумматора. DV-триггер 1 совместно с элемен тами И-НЕ 4 и 5 формирует значение отрицательной суммы согласно форму ле при + в,/ 1 v{J О при Iа + Ф 1 Логическое выражение для S имее Q S aXV va vatbили для инверсных,значений ,tb alblv V. Полученные значения S и S; с выходов элементов И-НЕ 58 и 59 UV-триггера по импульсу синхрониза ции, поступгиощему на вход синхрони зации триггера коммутации по управ ляющей шине 33 сумматора, поступаю на S- и R-входы RS-триггера 14. В RS-триггер 21 заносятся отрицательные значения первого аргумента DV-триггер совместно с элементом И-НЕ 9 формирует значение поло жительного переноса согласно формулеа + Bi у О at. -1- В4 гОЛогическое выражение для Р име ет вид at V BJ или Р| аГ Y . При этом если а + « 1, то а RS-триггеры 14 и 21 заносятся ло гические единицы, соответствующие 1 и 2 соответственно. Входными аргументами DV-триггера 15 являются задержанные на один такт значения отрицательной суммы S,:. и отрицательное значение первого аргумента а| . DV-триггер 15 совместно с элементом И-НЕ формирует значение csммы S, , которая может быть как положительной, так и отрицательной:при (а ц+в;.,/ .2 - И а)- +в -0 S.| О при /а,., jt 2 -2 при /а,.,+B,-,t 2 и af. -в. D Логическое выражение для имеет вид S, .a -«S;. va7i4 57.4 Значения pf, S|, Р.,, S,,, Sj.j и.а,н подаются в блок 16 формирования результата, который формирует положительное и отрицательное значения результата Zi HPiMS :.vP.,,S.,№.,S;.,vPl)i 2: (a.,S::.,vP ptHpJ.,5;.,vPb5;-)., DV-триггеры блоа 16 совместно с его элементами И-НЕ формируют значения - -«-4 4- м Р н ч- «г I п- .. г« .. . + ,.o,;,,vP.s.,vp;,.5..,, Элементы И-НЕ 40, 41, 45 и 46 блока 16 являются дополнительными элементами, которые по своему функциональному значению соответствуют элементу И-НЕ 58 pV-триггера. На входы элемента И-НЕ| 40 блока 16 подаются значения Zj- с второго и четвертого выходов 61 и 63 DV-триггера (с выходов первого и четвертого элементов И-НЕ 56 и 59 триггера и с выходов элементов И-НЕ 49 и 50, а также значение pj DV-триггера 13 и с выхода элемента И-НЕ 9. На входы элемента И-НЕ 41 подаются значения Zy (аналогично входам элемента И-НЕ 40) и Sj инверсных выходов DV-триггера 4. Значение Z « . Р; VS,-Z, с выходов элементов И-НЕ 40 и 41 подаются на S-входы RS-триггера 42 (на входы элемента И-НЕ 65), на R-входы (входы элемента И-НЕ б4).которого подаются значения Z/ с инверсного выхода переноса триггера 36 и значение, (S,) с выхода третьего элемента И-НЕ 43. Таким образом, положительное значение результата формируется согласно ВНражениям для S- и R-входов RS-триг гера 42 Sj,4: zJT pt-vz;. 1 ;Rj;4 Zlr VS;P|. . . Аналогично формируется отрицатель ное значение результата согласно вйраженийS. и Z SM-VZ/ . Z. Ri. Окончательный результат Z подают с прямых выходов RS-триггеров 42 и 4 на выходы 34 положительные значецил и 35 (ртрицательные значения ) ра. - . . , . . - , Все логические выражения реализуются основными и дополнительными 9fie ментами DV-триггеров суммматора и : триггеров блсжа 16 формирования результата; .Поэтому временная )жка прохождения сигнала (глубина схемы) составляет 6 t 1C - з адержка на ОДЯОЗЛ элементе И-НЕ.).В устройствепрототипе,в котором логические выражения дляотрицательной суммы, положительного переноса и промежуточной суммы реализуются с помощью двух двухразрядных комбинационных сумматоров, временная задержка {глубина схемы) определяется задержками прохождения сигналов в сумматорах и D-триггерах, что составляет 12с,, Таким образом, данное устройство имеет в 2 раза более высокое быстродействие по сравнению с прототипсни. Для реализации сумматора в избыточной системе на основе наиболее быстродействующих ИС 500 ИМ 180 (одноразрядным комбинационный сумматор) и ИС 500 ТМ 130 (О-триГгер) требуется 4 ИС 500 ИМ 180 и ИС 500 ТМ 130. При этом временная задержка составит 12 12 НС. При изготовлении предлагаемого , сумматора в интегральном исполнении (одна БИС), он дает временную Задержку от 6 (при ЭСД технологии) до 60 НС /при технологии И2Л), что пот зволяет производить су Ф ирование с частотой синхройизации более 10 Mjtti т.е. повысить быстрод ствие сум,матора в два раза.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 1971 |

|

SU453691A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сложения в избыточной двоичной системе | 1977 |

|

SU717763A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-15—Публикация

1982-03-19—Подача