1

(2) 3366798/18-24 (22) 21.12.81 (46) 23.08.90. Бюл. № 31

(71)Таганрогский радиотехнический .институт им. В.Д. Калмыкова

(72)В.А. Телековец, А.И. Гречишников и А.Ю. Арцатбаиов

(53) 681.325 (088.8)

(56)I. Ангорское свидетельство СССР

N 717763, кл. G 06 F 7/49, 1979.

2. Авторское свидетельство СССР N° 824201, кл. С 06 F 7/49, 1981. (54) (57) УСТРОЙСТВО ДЛЯ СЛОЖНИЯ В ИЗБЫТОЧНОЙ ДВОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ, содержащее блок формирования результата, выпол генный на двух D- триггерах, и четыре входных D-триг- гера,11ервый и второй входы признака блока формирования результата соединены соответственно с нркуым и инверсным выходами первого входного D-тригге- ра, а первый и второй, входы признака Г блока формирования результата подключены соотнетстяенно к прямому и инверсному выходам второго входного D-триггера, прямой выход которого подключен к D-входу третьего входного D-триггера,пряхой и инверсный выходы которого соединены соответственно с первым и вторым входами признака О блока формирования результата, третий и четвертый входы признака О которого подключены соответственно к прямому и инверсному выходам четвертого входного D-триггера, первый и второй выходы блока формирования результата соединены с шинами соответственно отрицательных и положительных значений результата устройства, причем каждый D-триггер содержит первый элемент

И-НЕ, второй элемент И-НЕ, первый и второй входы которого соединены соответственно с С-входом D-триггера и с выходом первого элемента И-НЕ, третий элемент И-НЕ, первый вход которого соединен с первым входом первого . элемента И-НЕ, второй и третий входы которого являются соответственно первым и вторым D-входами D-триггера, и с выходом второго элемента И-НЕ, четвертый элемент И-НЕ, первый вход которого соединен с выходом первого элемента И-НЕ, пятый элемент И-НЕ, первый и второй входы которого соеди- Heibi соответственно с С-входом D-триггера и с выходом четвертого элемента И-НЕ,и шестой элемент И-НЕ,первый вход которого соединен с третьим входом второго элемента И-НЕ, с вторым входом четвертого элемента И-НЕ и с выходом пятого элемента И-НЕ, а второй вход шестого элемента И-НЕ подключен к выходу третьего элемента И-НЕ и к прямому выходу D-триггера, инверсный выход которого соединен с выходом шестого элемента И-НЕ и с вторым входом третьего элемента И-НЕ, отличающееся тем, что, с целью повьш1ения быстродействия, С-входы всех входных .D-тригге- ров подключены к шине синхронизации устройства, первые D-входы первого и второго входных Б-триггеров подключены к шине прямых положительных значений первого слагаемого устройства, вторые D-входы первого и второго входных D-триггеров подклю- .чены к шине инверсных отрицательных значений второго слагаемого устройства, и к первому информационному входу блока формирования результата,третьи

S

S

СЛ

D-входы. пр-рвого и второг о (едиых D-триггеров подключены к шине прямых положителы& х .значений второго слагаемого устройства, четвертые D-входы первого и второго входных U-триг- геров подключены к шине инверс}1ых отрицательных значений первого слагаемого устройства и к второму информационному, входу блока формирования результата, пятый D-вход второго входного D-триггера н первый четвертого входного D-триггера подключены к типе прямых отрицательных значений первого слагаемого устройства и к третьему информационному входу блока формирования результата, шестой D-вход второго входного D- триггера и BTopoii D-вход четвертого входного D-триггера подключены к шине инверсных положительных значений второго слагаемого устройства, седьмой D-вход второго входного D-триггера и третий D-вход четвертого входно о D-триггера подключены к шине нрямых отрицательных значений второго слагаемого устройств;-} и к четвертому информационному входу блока формирования результата, вход синхронизации которого подключен к шине синхронизации устройства, восьмой D-вход второго входного D-триггера и четвертый D-пход, четвертого входного D-триггера нод- ключены к шине инверсных положительных значений первого слагаемого устройства, первые D-входы первого и второго D-триггеров блока формирова- шя результата являются соответственно первым и вторым входами .признака 1 блока формирования результата, С-входы первого и второго : D-триггеров блока формирования результата подключен1з1 к входу синхронизации блока формирования результата, их инверсные выходл,ы являются соответственно первым и вторым выходами блока формирования результата, а вторые D-ВХОДЫ первого и второго D-триггеров блока формирования оезу.гп.тата подключены к второму входу признака 1 блока формирования результата, блок формирования результата содержи две группы по три элемента И-НЕ, причем первые входы элементов И-НЕ первой и второ й групп подключены к первым входам первых элементов И-НЕ соответственно первого и второго D-три

геро блока формирования pe3yj bTaTa, второй вход первого элемента И-НК первой группы подключен к третьему вхоДУ признака О блока формирования результата, четвертьй вход приз,нака О которого соединен с вторыми входами второго элемента И-НЕ первой группы и первого элемента И-НЕ второй группы, третий вход первого эле;- мента И-НЕ первой группы подключен к третьему входу первого элемента И-НЕ второй группы и к первому входу признака О блока формирования

результата, третий вход второго элемента И-НЕ первой группы подключен к второму входу признака О блока фор№ рования результата, вторые входы третьего элемента И-НЕ первой

группы и второго и третьего элементов И-НК второй группы подключены к первому входу признака 1 блока формирования результата, третий и четвертый входы третьего элемента И-Ilfi первой

гриппы подключены соответственно к

первому и второму информационным входам блока формирования результата, третьи входы второго и третьего элементов И-НЕ второй группы подключены

соответственно к третьему и четвертому информационным входам блока формирования результата,выход первого элемента И-НЕ, каждой группы соединен с четвертым входом второго элемента

И-НЕ соответствующего D-триггера блока формирования результата и с третьим входом четвертого элемента И-НЕ,того же D-триггера, выход второго элемента И-НЕ каждой группы подключен

к пятому входу второго элемента И-НЕ соответствующего D-триггера блока формирования результата и к четвертому входу четвертого элемента И-НЕ того же D-триггера, выход третьего элемен- та М-НЕ каждой грушты подключен к шестому входу второго элемента И-НЕ соответствующего D-триггера блока фор- мировани я результата и к пятому входу четвертого элемента И-НЕ того же D-трнггера, первый, второй и четвертый входные D-триггеры содержат седьмой элемент И-НЕ, пе.рвьц вход которого соединен с первым входом первого элемента И-НЕ, а второй и третий входы седьмого элемента И-НЕ являются третьим и четв.ертым D-входа- ми входного D-триггера соответственно, выход седьмого элемента И-НЕ подключен к четвертому входу второго элемента И-НЕ и к третьему входу четвертого элемента И-НЕ, второй входной D-триггер содержит восьмой и девятый элементы И-НЕ, первые входы которых подключены к первому входу седьмого элемента И-НЕ, второй вход восьмого элемента И-НЕ является -пятым D-входом входного .D-триг- гера, третий вход восьмого элемента И-НЕ подключен к четвертому входу первого элемента И-НЕ и является шестым D-входом входного D-триг- гера, четвертый вход восьмого элемента И-НЕ подключен к третьему вхо- У первого элемента И-НЕ, второй

5874946вхбд девятого элемента И-НЕ является седьмым D-входом входного D-тригге- ра, третий вход девятого элемента И-НЕ подключен к четвертому входу седьмого элемента И-НЕ и является восьмью D-входом входного D-тригге- ра, четвертый вход девятого элемента И-НЕ подключен к третьему входу 10 седьмого элемента И-НЕ, -выход восьмого элемента И-НЕ подключен к пяте-) му входу второго элемента И-НЕ и к четвертому входу четвертого элемента И-НЕ, выход девятого элемента И-НЕ J5 соединен с шестым входом второго элемента И-НЕ и с пятым входом четвертого элемента И-НЕ ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор в избыточной двоичной системе счисления | 1982 |

|

SU1042011A1 |

| Устройство для сложения в избыточнойдВОичНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824201A1 |

| Последовательный сумматор | 1985 |

|

SU1663610A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1174923A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП ЕДИНИЧНЫХ БИТ И МАКСИМАЛЬНОЙ ГРУППЫ В БЛОКАХ ДАННЫХ | 2023 |

|

RU2800039C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| ДУБЛИРОВАННАЯ СИСТЕМА С ДИНАМИЧЕСКОЙ ЗАДЕРЖКОЙ | 1999 |

|

RU2153786C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

Цель изобретения - повышение быстродействия. Устройство содержит блок формирования результата, выполненный на двух D-триггерах, и четырех входны D-триггера. Каждый D-триггер содержит первый элемент И - НЕ, второй элемент И - НЕ, третий элемент И - НЕ, четвертый элемент И - НЕ, пятый элемент И - НЕ и шестой элементы И - НЕ.

Изобретение относится к вычислительной технике и может быть использовано в избыточной двоичной систем счисления с цифрами 1,0 и I.

, Известно устройство для сложения в избыточной двоичной системе, содежащее блоки формирования положитель 1ЮЙ и отрицательной сумм, блоки формирования результата и три элемента задержки ll.

Это устройство требует для своей реализации небольшого количества оборудования, однако обладает недостаточно высоким быстродействием, так как велика временная задержка составных частей устройства.

Наиболее близким к изобретению является устройство для сложения в избыточной двоичной системе счисления, содержащее четыре элемента И с прямым и инверсным выходами, вхо- .ды которых являются входами устройства, элемент 2И-ШШ, входы которо- го соединены с выходами третьего и четвертого элементов И, первый и второй D-триггеры, входы которых подключены к инверсным выходам соответственно первого и второго элементов И, третий D-триггер, вход которого лодключен к выходу элемента 2И-Ш1И четвертьш D-т.риггер, вход которого соединен с прямым выходом третьего D-триггера и два элемента 4И-Ш1И, выходы которых являются выходами устройства, а входы соединены с прямыми

и инверсными выходами первого элемента И и D-триггеров 21.

Недостатком известного устройства является плохое быстродействие, обусловленное задержками логических элементов и триггеров устройства. 30 Цель изобретения - повьшение быстродействия устройства.

Дпя достижения поставленной цели в устройстве для сложетя в избы- точной двоичной системе счисления J3 содержащем блок формирования результата, вьтолненный на двух D-триг- герах и четырех входных D-триггерах, первый и второй входы признака 1 блока формирования результата соединены соответственно с прямым и инверс- Hbw выходами первого входного D-триг- гера а первый и второй входы признака 1 блока формирования результата подключены соответственно к прямому и инверсному выходам второго входного D-триггера, прямой выход которого подключен к D-входу третьего входного D-триггера, прямой и инверсный входы которого соединены соответственно с первым и вторым входами признака

и блока формирования результата третий и четвертый входы признака О которого подключены соответственно к прямому и инверсному выходам четвертого входного D-триггера, первый и второй вьрсоды блока формирования результата соединены с шинами соответственно отрицательных и положительных значений результата устройства, причем каждьй D-триггер и каждый входной D-триггер содержат элемент И-НЕ, второй элемент И-НЕ, первый и второй входы которого соединены соответственно с С-входом D-триг гера и с выходом первого элемента И-НЕ, третий элемент И-НЕ, первый вход которого соединен с первым входом первого элемента И-НЕ, второй-и третий входы которого являются соответственно первым и вторым D-входа- ми D-триггера, и с выходом второго элемента И-НЕ, четвертый элемент И-НЕ первый вход которого соединен с выходом первого элемента И-НЕ, пятый элемент И-НЕ, первый и второй входы которого соединены соответственно с С-входом D-триггера и с выходом четвертого элемента И-НЕ, и шестой элемент Р1-НЕ, первьш вход которого соединен с третьим входом второго элемента И-НЕ, с вторым входом четвертого элемента И-НЕ и с выходом пятого элемента И-НЕ, а второй вход шестого элемента И-НЕ подключен к выходу третьего элемента и к прямому выходу D-триггера, инверсный выход которого соединен с выходом шестого элемента И-НЕ и с вторьм входом третьего элемента И-НЕ, С-входы всех входных триггеров подключены к шине синхронизации устройства, первые D-входы первого и второго входных D-триггеров подключены к шине прямых положительных значений первого слагаемого устройства, вторые D-входы первого и второго входных D-тригг.е- ров подключены к шине инверсных отрицательных значений второго слагаемого устройства и к.первому информационному входу блока формирования результата, третьи D-входы первого и второго входных D-триггеров подключены к шине прямых положительных значений второго слагаемого устройства, четвертые D-входы первого и второго входных D-триггеров подклю- . чены к шине инверс1шх отрицательных значений первого слагаемого устройства и к второму информационному вхо ДУ блока формирования результата, пяты D-ВХОД второго входного D-триггера и первый D-вход четвертого входного D-тригг.ера подключены к шине прямых отрицательных значений первого слагаемого устройства и к третьему информационному входу блока фор-

5

0

5

0

5

0

5

50

55

мирования результата, шестой D-вход второго входного D-триггера и второй D-вход четвертого входного D-триггера подключены к шине инверсных положительных значений второго слагае- мого устройства, седьмой . D-вход второго входного D-триггера и третий D-ВХОД четвертого входного D-триггера подключены к шине прямых отрицательных значений второго слат а- емого устройства и к четвертому информационному входу блока формирования результата, вход синхронизации которого подключен к шине синхронизации устройства, восьмой D-вход второго входного D-триггера и четвертый D-вход четвертого входного D-триггера подключены к шине инверсных положительных значений прряого слагаемого устройства, первые D-входы первого и второго D-триггеров блока формирования результата являются соответственно первым и вторьм входами признака 1 блока формирова-- ния результата, С-входы первого и второго D-триггеров подключены к входу синхронизации блока формирования результата, их инверсные выходы являются соответственно первым и вторым выходами блока формирования результата, а вторые D-входы первого и второго D-триггеров блока формирования результата подключены к второму входу признака 1 блока формирования рез ультата. Последний содержит две группы по три элемента И-НЕ, причем первые входы элементов И-НЕ первой и второй групп подключены к первым входам первых элементов И-НЕ соответственно первого и второго D-триггеров, второй вход первого элемента И-НЕ первой группы подключен к третьему входу признака О блока формирования результата, четвертый вход признака О которого со- единен с вторыми входами второго элемента И-НЕ первой группы и первого элемента И-НЕ второй группы. Третий вход первого элемента И-НЕ первой группы подключен к третьему входу первого, элемента И-НЕ второй группы и и к первому входу признака О блока формирования результата, третий вход второго элемента И-НЕ первой группы подключен к второму входу признака О блока формирования результата, вторые входы третьего элемента И-НЕ первой группы и второго и третьего .

элементов И-НЕ второй группы подключены к первому входу признака 1 блока формирования результата, третий и четвертьй входы третьего элемента И-НЕ первой группы подключены соответственно к первому и второму инфор-. мационным входам блока формирования результата, третьи входы второго и третьего элементов И-Н второй группы подключены соответственно к третьему и четвертому информационным входам блока формирования результата, выход первого элемента И-НЕ каждой группы соединен с четвертым входом второго элемента И-НЕ соответствующего D-триггера и третьим входом четвертого элемента И-НЕ того же D-триггера, выход второго элемента И-НЕ каждбй группы подключен к пятому входу второго элемента И-НЕ соответствующего D-триггера и четвертому входу четвертого элемента И-НЕ того же D- тригг.ера, выход третьего элемента И-НЕ каждой группы подключен к шестому входу второго элемента И-НЕ соответствующего D-триггера и пятому входу четвертого элемента И-НЕ того же D-триггера, первый, второй и четвертый входные D-триггеры содержат седьмой элемент И-НЕ, причем первый вход седьмого элемента И-НЕ соединен с первым входом первого элемента И-НЕ, л второй и третий входы седьмого элемента являются третьим и четвертым D-входами входного D-триггера соответственно, выход седьмого элемента И-НЕ подключен к четвертому входу второго элемента И-НЕ и к третьему входу четвертого элемента И-НЕ, второй входной D-триг- гер содержит восьмой и девятый элементы И-НЕ, первые входы которых подключены к первому входу седьмого элемента И-НЕ, второй вход восьмого элемента И-НЕ является пятым D-BXO- дом входного О-триггера, третий вход восьмого элемента И-НЕ подключен к четвертому входу первого элемента И-НЕ и является шестым D-BXO- дом входного D-триггера, четвертый вход восьмого элемента. И-НЕ подклюен к третьему входу первого элеента И-НЕ, второй вход девятого элеента И-НЕ является седьмым D-BXO- ом входного D-триггера, третий ход девятого элемента подклюен к четвертому входу седьмого элеента И-НЕ и является восьмым D-BXO8749410.

дом входного D-триггера, четвертый вход девятого элемента И-НЕ подключен к третьему входу седьмого элемента И-НЕ, выход восьмого элемента И-НЕ подключен к пятому входу второго элемента И-НЕ и к четвертому входу четвертого элемента И-НЕ, выход девятого элемента И-НЕ соединен с 10 шестым входом второго элемента И-НЕ и с пятым входом четвертого элемента И-НЕ.

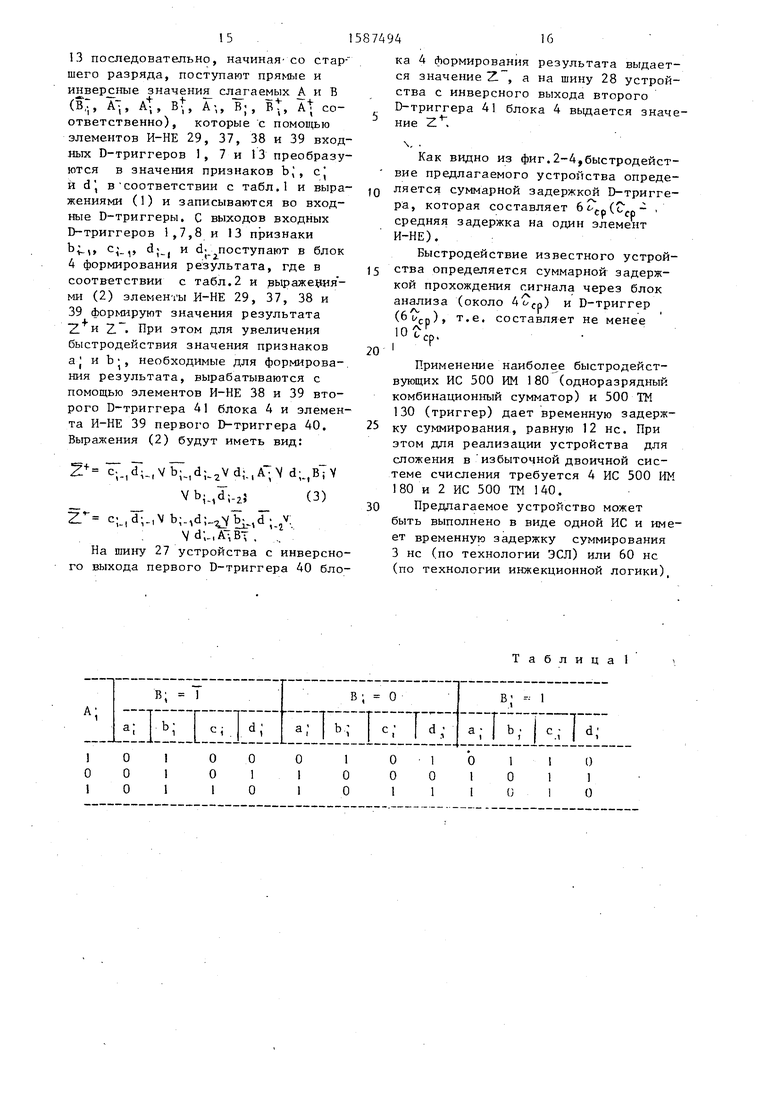

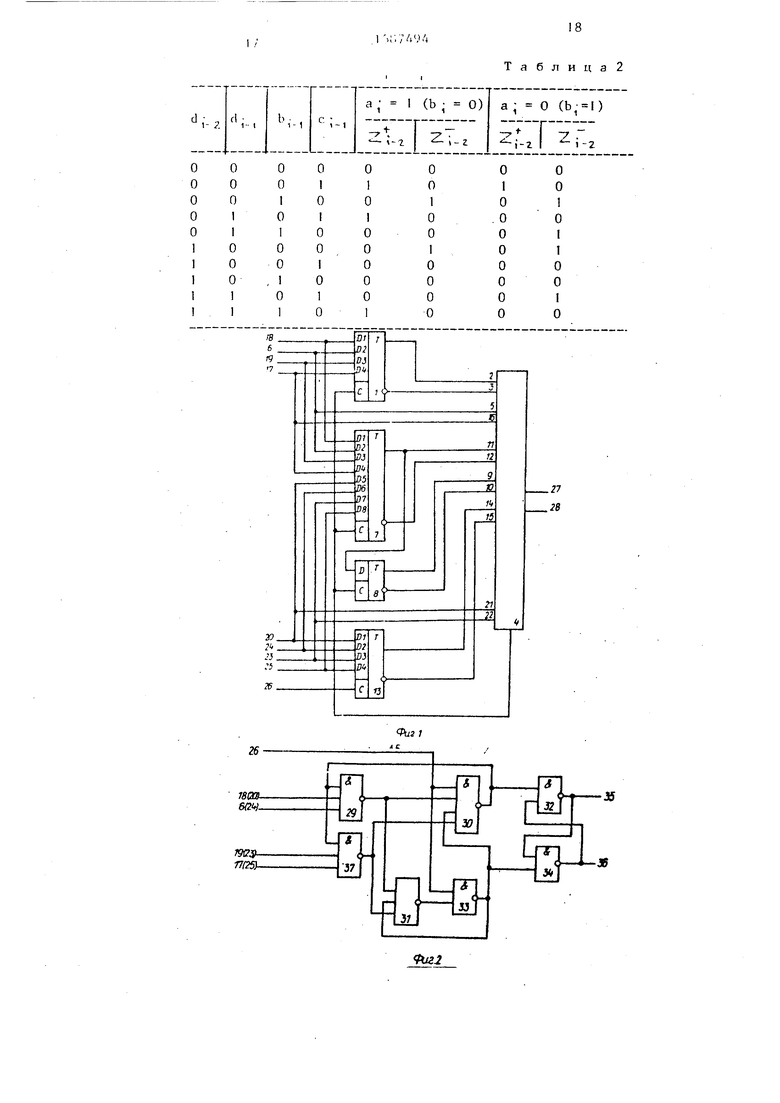

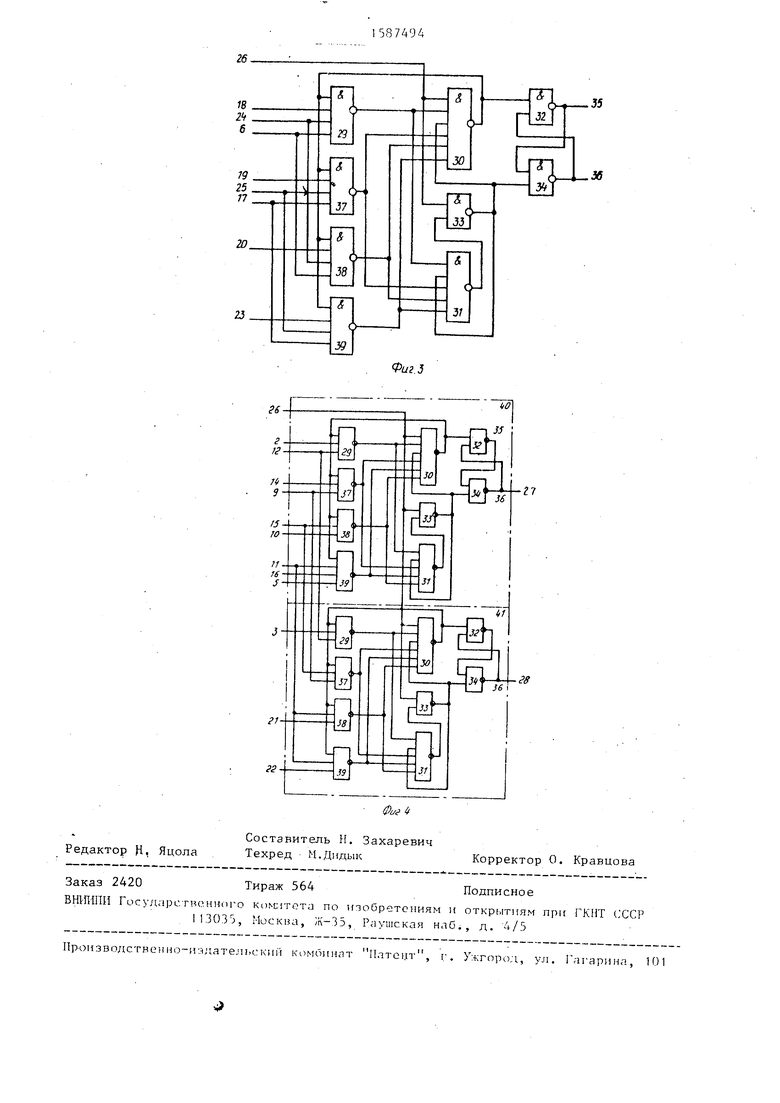

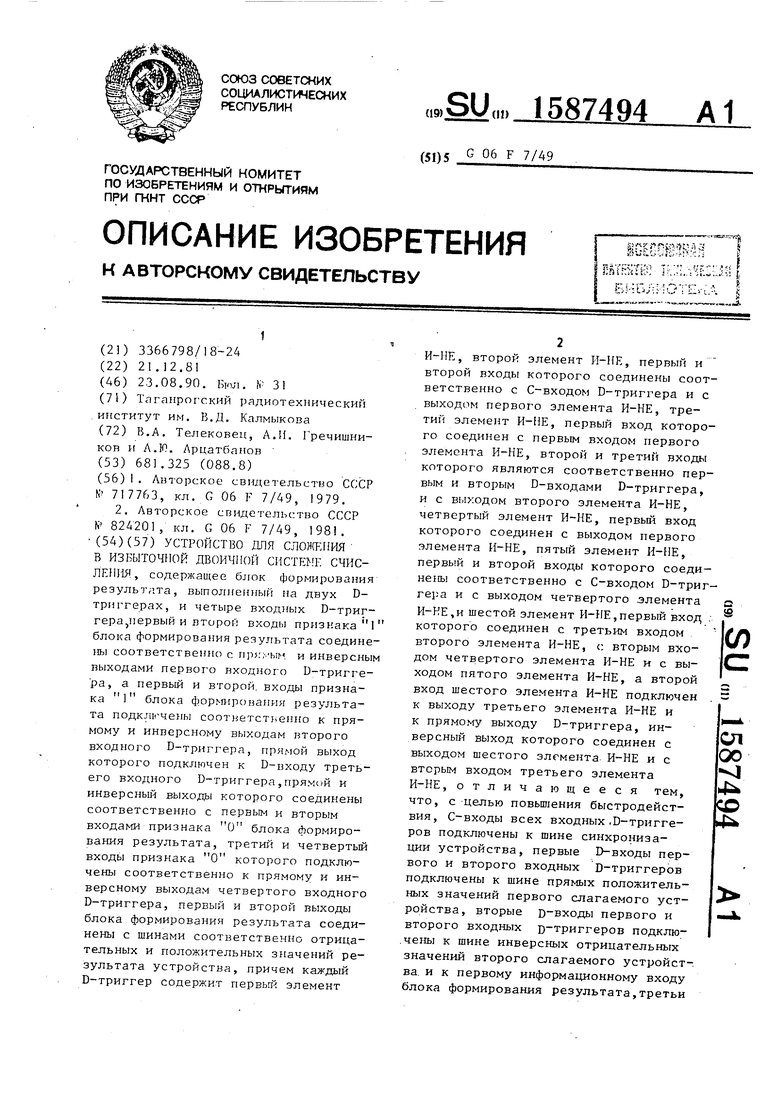

На фиг.1 показана структурная схема устройства; на фиг.2 - функцио- 15 нальная схема первого и четвертого входных D-триггеров; на фиг.З - функциональная схема второго входного D-триггера; на фиг.4 - функциональная схема блока формирования ре- 20 зультата.

Прямой и инверсный выходы первого входного D-триггера I подключены к первому и второму входам 2 и 3 признака 1 блока 4 формирования резуль25 тата, первый информационный вход 5

которого подключен к второму D-BXO- ду первого входного D-триггера 1, к входной шине 6 инверсных отрицательных значений второго слагаемого () 30 и к второму D-входу второго входного D-триггера 7, прямой выход которого соединен с D-входом третьего входного D-триггера 8, прямой и инверсный выходы которого подключены соответственно к первому и второму входам 9 и 10 признака О блока 4. первый т. второй входы II и 12 приз- нака 1 которого подключены соответственно к прямому и инверсному 40 выходам второго входного D-триггера 7. Прямой и инверсный выходы четвертого входного D-триггера 13 подключены соответственно к третьему и четвертому входам 14 и 15 призна- 5 . блока 4, второй информационный вход 16 которого подключен к четвертому D-входу первого входного D-триггера 1, к входной шине 17 .инверсных отрицательных значений пер- 0 вого слагаемого (А) и к четвертому D-входу второго входного D-триггера 7, первый D-вход которого соединен с первым D-входом первого входного D-триггера 1 и с входной, шиной 5 18 прямых положительных значений первого слагаемого (А). Входная шина 19 прямых положитепьных значений второго слагаемого () подключена к третьим D-входам первого и второго

входных D-триггеров 1 и 7., Входная шина 20 прямых отрицательных значени первого слагаемого (А) подключена к пятому D-входу второго входного D-триггера 7, к первому D-входу четвертого входного D-триггер.а 13 и к третьему информационному входу 21 блока 4, четвертый информационный вход 22 которого соединен с третьим D-.входом четвертого входного D-триггера 13, с седьмым D-входом второго входного D-триггера 7 и с входной шиной 23 прямых отрицательных значений второго слагаемого (В). Входная шина 24 инверсных положительных значений второго слагаемого (В) подключена к шестому D-входу второго входного D-триггера 7 и к второму D-входу четвертого входного D-триггера 13, четвертый D-вход которого соединен с восьмым D-входом второго входного D-триггера 7 и с входной шиной 24 инверсных положительных значений первого слагаемого (A). Шина

26синхронизации устройства подключена к С-входам входных D-триггеров 1,7,8 и 13. Первый и второй выходы

27и 28 блока 4 подключены к шинам отрицательных и положительных значений результата устройства соответственно.

В каждом из D-триггеров выход первого элемента И-НЕ 29 соединен с входами второго и четвертого элементов И-НЕ 30 и 31.Выход второго элемента И-НЕ 30 подключен к первому, входу первого элемента И-НЕ 29 и к первому входу третьего элемента И-НЕ 32. Выход четвертого элемента И-НЕ 31 соединен с вторым входом пятого элемента И-НЕ 33, выход которого подключен к третьему входу второго элемента И-НЕ 30, к второму входу четвертого элемента И-НЕ 31 и к второму входу шестого элемента И-НЕ 34, первый вход которого соединен с прямым выходом 35 D-триггера и с выходом третьего элемента И-НЕ 32, вторым входом соединенного с инверсным выходом 36 D-триггера и с выходом шестого элемента И-НЕ 34. Выходы первого 37, второго 38 и третьего 39 дополнительных элементов И-НЕ подключены к входам второго и четвертого элементов И-НЕ 30 и 31, а их первые входы соединены с выходом второго элемента И-НЕ 30. Первые входы второго

й 25

10

5

15

20

0

5

0

5

0

5

и пятого элементов И-НЕ подключены к шине 26 синхронизации устройства.

Входная шина 6 устройства (В) соединена с третьим входом первого элемента И-НЕ 29 первого входного D-триггера 1 и с четвертыми входами соответственно первого элемента И-НЕ 29 и восьмого элемента И-НЕ 38 второго входного D-триггера 7. Входная шина 17 устройства (Л) соединена с третьим входом седьмого элемента И-НЕ 37 .первого входного Т -триггкра 1 и с четвертыми входами соответственно седьмого и девятого элементов И-ПЕ 37 и 39 второго входного триггера 7. Входная шина 18 устройства () соединена с вторыми входами первого элемента И-НЕ 29 первого и второго входных D-триггеров 1 и 7, вторые входы седьмого элемента 37 которых подключены к входной шине 19 устройства (В). Входная шина 20 устройства (А) подключена к вторым входам соответственно первого элемента И-НЕ 29 четвертого входного D-триггера 13 и восьмого элемента И-НЕ 38 второго входного D-триггера 7. Входная шина 23 устройства (В) соединена с вторыми входами соответственно девятого дополнительного элемента И-НЕ 39 второго входного D-триггера 7 и седьмого элемента И-НЕ 37 четвертого входного D-триггера 13. Входная шина 24 устройства (В) соединена с третьим входом первого элемента И-НЕ 29 четвертого входного D-триггера 13 и с третьими входами соответственно первого элемента И-НЕ 29 восьмого элемента И-НЕ 38 второго входного D-триггера 7, третьи входы седьмого и девятого элементов И-НЕ 37 и 39 которого соединены с третьим входом

седьмого элемента и-НЕ 37 четвертого входного D-триггера П и с входной шиной. 25 устройства (А) .

В блоке 4 формирования результата первый и второй его входы 2 и 3 признака 1 подключены к вторым входам первого элемента И-НЕ 29 соответ-: ственно первого и второго D-триггеров 40 и 41, первый и второй информационные входы блока 4 подключены к третьему и четвертому входам девятого элемента Й-НЕ 39 первого D-триггера 40, первый вход 11 признака 1 блока 4 соединен с вторьтш входами-девятых элементов И-НЕ 39

первого и BToiioro D-триггеров 40 и 41 и с втopы FixonoM восьмого элемента И-НЕ 38 второго D-триггера , второй вход признака 1 блока 4 соединен с третьими входами первого элемента H-fiK 29 первого и второго D-триггеров 40 и 41, первый и второй входы 9 и 10 признака О блока 4

Признаки , с;, d;, поступа в блок 4 формирования результата, кроме того, признак d ,-, задержива ся дополнительно .на один такт тре

соединены с третьими входами соответ- ,Q им входным . D-триггером 8 и также ственно седьмого элемента И-НЕ 37 первого и второго D-триггеров 40 и 41 и восьмого элемента И-НЕ 38 первого D-триггера 40. Третий вход 14 признака О блока 4 соединен с вторым (5

входом седьмого элемента И-НЕ 37 первого D-триггерл 40, четвертый вход 15 признака О блока 4 соединен с вторыми входами восьмого и седьмого элементов И-НЕ 38 и 37 соответствен- 20 но первого и второго D-триггеров 40 и 41, третий и четвертьз информационные входы 21 и 22 блока 4 соединены с третьими входами соответственно восьмого и девятого элементов И-НЕ 25 38 и 39 первого и второгс D-триггеров 40 и 41. Инверсные, выходы 36 первого и второго D-триггеров 40 и 4.1 подключены соответственно к шинам 27 и 28 отрицательных и положительных ЗО значений результата устройства.

Входная логика входных D-триггеров 1 , 7 и 13 преобг азует значения слагаемых А и -В в значения признаков а, Ь, с и d в соответствии с табл.1

поступает в блок А формирования р зультата. В зависимости от наличи признаков а;, Ь;, Ь-.,, с;., ,d;, ,d блок 4 формирования результата выд ет значение суммы Z входных арг ментов в соответствии с табл.2.

Например, для входных аргументо А 001I, В 1110, по табл.1 и 2 получим:

А 001100

В Ь;

с

1

d

f

b1 I 1000 100100 011000 I 10100 010010

35

C| 001100 1010

d; .001101 Z; 000001

Определим сумму при непосредстве ном сложении:

Ha основании таблицы получим:

50

признак отсутствия I во вход-дз ных аргументах;

признак наличия 1 хотя бы в одном из входных аргументов;

признак наличия 1 хотя бы в одном из входных аргументов;

признак равенства нулю только одного из аргументов. одах первого и четвертого D-TpHr,repOB 1 и 13 получаем инверсное значения признаи Ь;, соответственно Нп выходах второго входно55

го D-триггера 7 имеем прямое и инверсное значения признака б;,(фиг.З). Признак а; формируется в блоке 4 формирования результата.

Признаки , с;, d;, поступают в блок 4 формирования результата, кроме того, признак d ,-, задерживается дополнительно .на один такт третьим входным . D-триггером 8 и также

им входным . D-триггером 8 и также

поступает в блок А формирования результата. В зависимости от наличия признаков а;, Ь;, Ь-.,, с;., ,d;, ,d- блок 4 формирования результата выдает значение суммы Z входных аргументов в соответствии с табл.2.

Например, для входных аргументов А 001I, В 1110, по табл.1 и 2 получим:

А 001100

1 I 1000 100100 011000 I 10100 010010

C| 001100 1010

d; .001101 Z; 000001

Определим сумму при непосредственном сложении:

А О О 1 1 В 1110

О О О 1

Таким образом, получим правильный результат (со сдвигом на два разряда вправо).

На основании табл. 2 получим;

S-,,d;-zVdi.,b;Vb,-.,d,-.,;

-

. Z- C;,d;..,Nb;,,d;.Y b;- id;.,Yd;,a,.,

Значения Z. и Z вырабатываются на шинах 27 и 28 блока 4 формирования результата (фиг.4).

Устройство для сложения в избыточной двоичной системе работает следующим образом.

По входным шинам 6, 17 - 20 и 23 - 25 на входы D-триггеров 1,7 и 15

13 последовательно, начиная- со старшего разряда, поступают прямые и инвер сные значения сл гаемых А и В (ВТ, А-:, At, Bt, А-, ; , в|. At со- ответственно), которые с помощью элементов И-НЕ 29, 37, 38 и 39 входных D-триггеров 1, 7 и 13 преобразуются в значения признаков bj, с и d , в соответствии с табл.1 и выражениями (1) и записываются во входные D-триггеры. С выходов входных D-триггеров 1,7,8 и 13 признаки bv( с,,, и ё| поступают в блок 4 формирования результата, где в соответствии с табл.2 и эыраже 1ия - ми (2) элементы И-НЕ 29, 37, 38 и 39 формируют значения результата Z и Z . При этом для увеличения быстродействия значения признаков а j и b, необходимые для формирования результата, вырабатываются с помощью элементов И-НЕ 38 и 39 второго D-триггера 41 блока 4 и элемента И-НЕ 39 первого D-триггера 40. Выражения (2) будут иметь вид:

Z -/;-,Vbi:,d;,d,-.,A-: d;.,BTV

Vb..,;.; (3) Z c;,d,Vb;.,d;. b,d ; v;

: vd;.,A-,BT. ,.

Ha шину 27 устройства с инверсного выхода первого D-триггера 40 бло58749416

ка 4 формирования результата выдается значение Z , а на шину 28 устройства с инверсного выхода второго D-триггера 41 блока 4 выдается значе- ние Z

Как видно из фиг.2-4,быстродействие предлагаемого устройства опреде- 10 ляется суммарной задержкой D-триггера, которая составляет , средняя задержка на один элемент

И-НЕ).;

Быстродействие известного устрой- 15 ства определяется суммарной задержкой прохождения сигнала через блок

20

анализа (около 4о;р) и D-триггер

(6, 10 с),

Р т.е. составляет не менее

-РПрименение наиболе е быстродействующих ИС 500 ИМ 180 (одноразрядньш; комбинационный сумматор) и 500 ТМ 130 (триггер) дает временную задержку суммирования, равную 12 не. При этом для реализации устройства для сложения в избыточной двоичной системе счисления требуется 4 ИС 500 ИМ 180 и 2 ИС 500 ТМ 140.

Предпагаемое устройство может

быть выполнено в виде одной ИС и имеет временную задержку суммирования 3 НС (по технологии ЭСЛ) или 60 не (по технологии инжекционной логики).

Т а б л и ц а 1

Т a б л и ц a 2

Авторы

Даты

1990-08-23—Публикация

1981-12-21—Подача