Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики. Известны способы суммирования двоично-десятичных чисел, заключающиеся в последовательном выполнении элементарных операций (ЭО) приема слагаемых, формирования сигналов переноса и суммы в каждом разряде и занесении этой суммы в триггеры одного из регистров. Если устройство выполнено на основе логических элементов (ЛЭ) И, ИЛИ, НЕ и содержит в каждом двоичном разряде три RS - триггера, комбинационный сумматор (КС), то для выполнения операции сложения чисел, представленных в двоичном коде (ДК), требуется три временных такта. Для сложения чисел, представленных в двоично-десятичном коде (ДДК), потребуется затратить время в 2-3 раза больше, чем для сложения чисел в ДК. Способы выполнения указанных операций подробно рассмотрены в книге Е.А.Дроздова, В.А., Комарницкого и А.П.Пятибратова «Электронные вычислительные машины Единой системы», Москва, «Машиностроение», 1981, стр.59-68. Так, например, при сложении двоично-десятичных чисел и использовании оборудования для сложения двоичных чисел требуется затратить в три раза больше времени (см. пример сложения в указанном источнике, стр.66, Пример 2.12). Это является недостатком известного способа суммирования. В предложенном способе исключается этот недостаток. Предложен способ суммирования двоично-десятичных чисел, отличающийся тем, что представляют каждую десятичную цифру четырьмя двоичными разрядами - тетрадами - и по первому временному такту принимают второе слагаемое в первый триггерный регистр, при этом первое слагаемое хранится во втором триггером регистре, по второму такту с помощью комбинационных сумматоров на три входа формируют сигналы переноса и суммы в двоичных разрядах каждой тетрады, одновременно формируют сигналы дополнительных переносов, если код суммы тетрады равен 1010, 1011, 1100, 1101, 1110 и 1111, кроме того, при наличии основного сигнала переноса из старшего разряда тетрады с помощью первой корректирующей схемы прибавляют к коду суммы тетрады код 0110, а при наличии дополнительного сигнала переноса, выработанного в данной тетраде, с помощью второй корректирующей схемы из кода суммы тетрады вычитают код 1010, по третьему такту заносят парафазным кодом откорректированный результат суммирования в триггеры второго регистра, в случае отсутствия основного и дополнительного сигналов переноса тетрады значение кода суммы тетрады передается во второй трштерный регистр без изменения.

Целью предложенного способа является повышение быстродействия сложения двоично-десятичных чисел при минимальных затратах оборудования. Указанная цель достигается в совмещении во времени выполнения формирования переносов и суммы с корректировкой этой суммы, т.е. добавлением кода 0110 при наличии основного переноса (ОП) из старшего разряда тетрады и вычитании кода 1010 из суммы тетрады, если имеется дополнительный перенос (ДП). Кроме того, достигается повышение быстродействия при многократном сложении (умножении) чисел, представленных в ДК и в ДДК (таблица 2). Последовательность формирования откорректированной суммы для двоично-десятичных чисел приведена в таблице 1.

** _ J - потребление тока одним триггером.

Для реализации способа сложения двоично-десятичных чисел предложено устройство, ближайшим прототипом которого является двоично-десятичный сумматор комбинационного типа, принцип работы которого рассмотрен в книге М.А.Карцева. «Арифметика цифровых машин», издательство «Наука», М., 1969 г., стр., 168-173, рис 2-19. Однако указанный прототип имеет ряд недостатков: требуется иметь в составе устройства три триггерных регистра (два для хранения слагаемых и один регистр для хранения результата сложения), каждая операция многократного сложения второго слагаемого с частными значениями суммы требует трех временных тактов (прием результата предыдущего суммирования в один из регистров, формирование переносов и суммы, занесение результата в регистр результата сложения). Кроме того, устройство не обеспечивает выполнение сложения чисел в ДК, а построение схемы коррекции суммы при сложении ДДК требует около 30 входов логических элементов, что также является недостатками прототипа.

Предложено устройство, отличающееся тем, что каждый двоичный разряд содержит первый и второй RS - триггеры, комбинационный сумматор на три входа, информационный вход, подключенный к единичному входу первого RS - триггера, вход исполнительного импульса приема кода во второй триггер, схему приема кода во второй RS - триггер с элементами задержки сигнала с выхода этого триггера, содержащую четыре элемента И, два элемента ИЛИ, четыре элемента НЕ, при этом первый вход первого элемента И соединен с выходом комбинационного сумматора, выход первого элемента И через первый элемент ИЛИ соединен с вторым входом третьего элемента И и с входом первого элемента НЕ, выход которого соединен с вторым входом второго элемента И, третьи входы второго и третьего элементов И связаны с входом и выходом четвертого элемента НЕ соответственно, первые входы упомянутых элементов И связаны с входом исполнительного импульса приема кода во второй триггер, выходы второго и третьего элементов И через второй и третий элементы НЕ соединены с нулевым и единичным входами второго триггера соответственно, единичный выход которого соединен с первым входом второго элемента ИЛИ, второй выход которого связан с выходом второго элемента И, выход второго элемента ИЛИ связан с первым входом четвертого элемента И, второй его вход связан с выходом третьего элемента НЕ, а его выход соединен с входом четвертого элемента НЕ и первым входом комбинационного сумматора, второй и третий входы которого связаны с единичным выходом первого RS - триггера и входом переноса из младшего разряда соответственно, а выход переноса сумматора соединен с третим входом сумматора старшего разряда; в каждую тетраду устройства введена первая схема коррекции кода суммы тетрады, содержащая пятый, шестой и седьмой элементы И, при этом выход переноса из старшего разряда тетрады соединен с первым входом пятого элемента И, второй его вход связан с входом управления выполнением операции двоично-десятичного сложения, выход упомянутого элемента И соединен с первыми входами шестого и седьмого элементов И, второй вход шестого элемента И связан с выходом сумматора второго разряда тетрады, а его выход подключен к второму входу первого элемента ИЛИ четвертого разряда, второй вход седьмого элемента И соединен с инверсным выходом сумматора второго разряда, а выход этого элемента подключен к вторым входам первых элементов ИЛИ второго и третьего разрядов второго регистра; введена схема формирования дополнительного переноса в старшую тетраду при значении суммы тетрады, равной 1010, 1011, 1100, 1101, 1110 и 1111, содержащая третий и четвертый элементы ИЛИ и восьмой элемент И, при этом выход сумматора третьего разряда связан с первым входом третьего элемента ИЛИ, второй его вход соединен с выходом сумматора второго разряда, а выход подключен к первому входу восьмого элемента И, второй и третий входы которого соединены с выходом сумматора четвертого разряда и входом управления выполнением операции двоично-десятичного сложения, выход этого элемента И соединен с вторым входом четвертого элемента ИЛИ, первый вход которого соединен с выходом основного переноса из четвертого разряда сумматора, а выход четвертого элемента ИЛИ является выходом переноса в старшую тетраду; также введена вторая схема коррекции кода суммы тетрады, содержащая девятый и десятый элементы И, при этом выход восьмого элемента И соединен с первыми входами девятого и десятого элементов И, вторые входы этих элементов связаны с выходом сумматора второго разряда и с инверсным выходом сумматора второго разряда тетрады соответственно, третий вход девятого элемента И подключен к выходу сумматора третьего разряда, а выходы девятого и десятого элементов И соединены с третими входами первых элементов ИЛИ третьего и второго разрядов второго регистра соответственно; введены одиннадцатый элемент И и пятые элементы ИЛИ и НЕ, при этом первый вход пятого элемента ИЛИ соединен с входом управления выполнением операции двоичного сложения, второй его вход соединен с выходом одиннадцатого элемента И, входы которого соединены с выходом пятого элемента НЕ и с входом управления выполнением двоично-десятичного сложения, выход пятого элемента ИЛИ подключен к вторым входам первых элементов И второго, третьего и четвертого разрядов второго регистра, а вход пятого элемента НЕ связан с выходом четвертого элемента ИЛИ.

Это устройство позволяет выполнить сложение чисел, представленных как в ДК, так и в ДДК, обеспечивает исключение из состава оборудования одного триггерного регистра и повышает быстродействие операции многократного сложения в 1,5 раза. Операция многократного сложения требуется при выполнении операции умножения чисел. Основные технические характеристики предложенного устройства приведены в таблице 2.

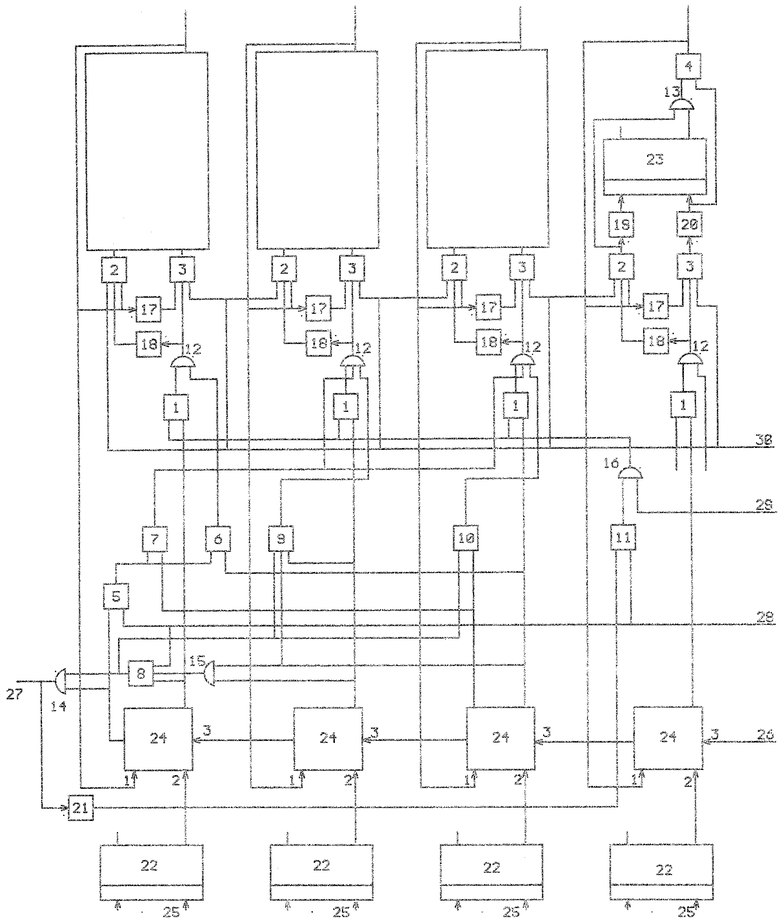

Для пояснения работы предлагаемого устройства на чертеже приведена функциональная схема четырех двоичных разрядов. На чертеже приняты следующие обозначения: логические элементы И 1-11, ИЛИ 12-16, НЕ 17-21, RS - триггеры (Тr) 22, 23, комбинационный сумматор (КС) 24, информационный вход - 25, вход переноса в старший разряд - 26, выход переноса из тетрады 27, вход управления (ВУ) выполнением операции сложения в ДДК - 28, ВУ выполнением операции сложения в ДК 29, вход управления приемом суммы парофазным кодом во второй RS - триггер 30.

Предложенное устройство осуществляется следующим образом. В каждом двоичном разряде информационный вход 25 подключен к единичному входу Тr 22, его единичный выход соединен с вторым входом КС 24, первый и третий входы которого связаны с выходом И4 и входом 26 соответственно, а выход суммы КС-24 соединен с входом И1, выход которого через ИЛИ 12 соединен с вторым входом И3 и через НЕ 18 с вторым входом И2, первые входы этих элементов соединены с ВУ 30, третьи входы И 2, 3 связаны с входом и выходом НЕ 17. Выходы И2, 3 через НЕ 19, 20 соединены с нулевым и единичным входами Тr 23 соответственно, единичный выход которого подключен к входу ИЛИ 13, второй вход этого элемента соединен с выходом И2. Выход ИЛИ 13 подключен к И4, второй вход которого связан с выходом НЕ 20. Выход И4 соединен с входами НЕ 17, И2 и первым входом КС24. Выход НЕ 17 связан с третьим входом И3. В каждом десятичном разряде (тетраде) выход основного переноса из старшего разряда КС 24 соединен с входами ИЛИ 14, И 5, выходы суммы КС 24 второго и третьего разрядов тетрады соединены с ИЛИ 15, выход которого соединен с входом И8, второй и третий входы которого соединены с выходом суммы КС24 четвертого разряда и ВУ 28. Выход И8 подключен к второму входу ИЛИ14 и к входам И 9, 10. Второй и третий входы И9 соединены с выходами суммы КС 24 второго и третьего разрядов, второй вход И 10 подключен к инверсному выходу суммы КС 24 второго разряда. Второй вход И5 связан с ВУ 28, выход И5 соединен с входами И6, 7, второй вход И6 подключен к выходу суммы КС 24 второго разряда, выход И6 соединен с вторым входом ИЛИ 12 четвертого разряда, выход И7 соединен с вторыми входами ИЛИ 12 второго и третьего разрядов тетрады, выходы И 9, 10 соединены с третьими входами ИЛИ 12 третьего и второго разрядов тетрады, выход ИЛИ 14 соединен с входом НЕ 21, выход которого подключен к первому входу И 11, второй вход которого подключен к ВУ 28. Выход И 11 соединен с входом ИЛИ 16, второй его вход связан с ВУ 29. Выход ИЛИ 16 подключен к вторым входам И 1 второго, третьего и четвертого разрядов тетрады, в первом разряде тетрады вторые входы И 1, ИЛИ 12 свободны от управляющих входов.

Рассмотрим работу устройства при выполнении операции сложения чисел, представленных в ДК и ДДК.

1. Операция сложения чисел, представленных в ДК. Потенциал операции подается по ВУ 29, который через ИЛИ 16 поступает на входы И 1 второго, третьего и четвертого разрядов тетрады. Операция выполняется за три временных такта. По первому временному такту код второго слагаемого поступает по информационным входам 25 и принимается в Tr 22 тетрады второго слагаемого. Код первого слагаемого хранится в Тr 23 как результат выполнения предыдущей операции сложения. Второй временной такт отводится для формирования сигналов сквозного переноса и суммы во всех разрядах устройства. По этому же временному такту значение суммы каждого двоичного разряда по цепи выход суммы КС 24, И 1, ИЛИ 12 поступает на входы И 3, НЕ 18. По третьему временному такту исполнительный импульс, поступивший по ВУ 30, поступит на третьи входы И 2, 3 и занесет значение суммы разряда в Тr 23. Если значение суммы разряда равно нулю, то Тr 23 будет установлен в нуль. При установке Тr 23 в единицу потенциал с выхода И 4 будет задержан на время длительности сигнала, поступившего на ВУ 30. При установке Тr 23 в нуль значение высокого потенциала с выхода И 4 будет поддерживаться неизменным на время длительности сигнала на ВУ 30. В случае выполнения операции многократного сложения кода, принятого в Тr 22, каждая операция сложения выполняется за два такта, что обеспечивает повышение быстродействия по сравнению с известными устройствами в 1,5 раза.

2. Операция сложения чисел, представленных в ДДК. Потенциал операции поступает по ВУ 28. По первому временному такту в Тr 22 принимается код второго слагаемого, при этом каждые четыре двоичных разряда представляют код одного десятичного разряда. Второй временной такт отводится для формирования основного или дополнительного сигналов переноса и формирования суммы и формирования некорректированной и корректированной суммы в тетрадах.

Если код суммы тетрады равен или меньше 9 (1001), то на выходе ИЛИ 14 будет отсутствовать высокий потенциал. С выхода НЕ 21 на вход И 11 поступит разрешающий потенциал, который через ИЛИ 16 поступит на вход И1 всех разрядов тетрады, кроме первого, и разрешит передачу суммы тетрады в Тr 23 без корректировки.

Если в старшем разряде тетрады выработан основной перенос в старшую тетраду, то к коду суммы добавляется 6 (0110), при этом, если сумма второго разряда КС 24 равна нулю, то потенциал основного переноса по цепи И 5, 7 поступает на входы ИЛИ 12 второго и третьего разрядов тетрады второго регистра. В том случае, если сумма второго разряда равна единице, то потенциал с выхода И 5 через И 6 поступит на вход ИЛИ 12 и далее, на вход И3 четвертого разряда тетрады второго регистра. По третьему такту откорректированные коды тетрад будут занесены в Тr 23, где ранее хранился код первого слагаемого.

Если код суммы равен или больше 10 (1010), то на выходе И 8 будет выработан потенциал дополнительного переноса, который через ИЛИ 14 поступит на вход КС 24 младшего двоичного разряда старшей тетрады и на входы И 9, 10. При коде суммы, равной 14 (1110) или 15 (1111), с выхода И 9 через ИЛИ 12 на вход И 3 третьего разряда поступит высокий потенциал, соответствующий откорректированному коду суммы тетрады. При коде суммы, равной 12 (1100) или 13 (1101), с выхода И 10 на вход ИЛИ 12 второго разряда поступит высокий потенциал, соответствующий откорректированному коду суммы тетрады. Заметим, что корректировка суммы тетрады путем сложения кода 0110 или вычитания кода 1010 выполняется одновременно с формированием переносов и требует минимальных затрат оборудования в каждом десятичном разряде устройства.

По третьему такту откорректированный код суммы будет занесен в Тr 23, при этом высокий потенциал по цепи вход 30, И 3 поступит на единичный вход триггера того разряда, в который на вход ИЛИ 12 поступил высокий потенциал, соответствующий единице откорректированного кода суммы. В случае отсутствия высокого потенциала на входах ИЛИ 12, Тr 23 второго, третьего и четвертого разрядов будут установлены в нуль. Заметим, что в Тr 23 первого разряда тетрады будет занесена единица, если код КС 24 этого разряда будет равен единице.

Таким образом, предложенные способ и устройство для выполнения операций суммирования обеспечивают повышение быстродействия выполнения операций сложения ДДК за счет совмещения во времени формирования сигналов переноса и суммы с корректировкой суммы, упрощение устройства за счет исключения одного RS - триггера в каждом двоичном разряде, повышение быстродействия выполнения многократных операций сложения с трех до двух тактов, т.е. на 30%, и расширение функциональной гибкости устройства за счет выполнения операций сложения как двоичных, так и двоично-десятичных кодов. Указанные преимущества обеспечиваются при минимальных затратах оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ДВОИЧНЫХ КОДОВ | 2010 |

|

RU2410746C1 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2388041C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ЕДИНИЦ | 2014 |

|

RU2540787C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2014 |

|

RU2551414C1 |

| СПОСОБ И УСТРОЙСТВО СЧЕТА ИМПУЛЬСОВ | 2013 |

|

RU2538949C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Техническим результатом является упрощение устройства и повышение его быстродействия. Устройство содержит в каждом двоичном разряде тетрады четыре элемента И, два элемента ИЛИ, четыре элемента НЕ, два RS - триггера, комбинационный сумматор, каждая тетрада имеет две схемы коррекции кода суммы тетрады, схему формирования дополнительного переноса. 1 ил., 2 табл.

Устройство суммирования двоично-десятичных чисел, в котором каждая десятичная цифра представлена четырьмя двоичными разрядами - тетрадами, отличающееся тем, что каждый двоичный разряд содержит первый и второй RS-триггеры, комбинационный сумматор на три входа, информационный вход, подключенный к единичному входу первого RS-триггера, вход исполнительного импульса приема кода во второй RS-триггер, схему приема кода во второй RS-триггер с элементами задержки сигнала с выхода этого триггера, содержащую четыре элемента И, два элемента ИЛИ, четыре элемента НЕ, при этом первый вход первого элемента И соединен с выходом комбинационного сумматора, выход первого элемента И через первый элемент ИЛИ соединен с вторым входом третьего элемента И и с входом первого элемента НЕ, выход которого соединен с вторым входом второго элемента И, третьи входы второго и третьего элементов И связаны с входом и выходом четвертого элемента НЕ соответственно, первые входы упомянутых элементов И связаны с входом исполнительного импульса приема кода во второй RS-триггер, выходы второго и третьего элементов И через второй и третий элементы НЕ соединены с нулевым и единичным входами второго триггера соответственно, единичный выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого связан с выходом второго элемента И, выход второго элемента ИЛИ связан с первым входом четвертого элемента И, второй его вход связан с выходом третьего элемента НЕ, а его выход соединен с входом четвертого элемента НЕ и первым входом комбинационного сумматора, второй и третий входы которого связаны с единичным выходом первого RS-триггера и входом переноса из младшего разряда соответственно, а выход переноса комбинационного сумматора соединен с третьим входом комбинационного сумматора старшего двоичного разряда; в каждую тетраду устройства введена первая схема коррекции кода суммы тетрады, содержащая пятый, шестой и седьмой элементы И, при этом выход переноса из старшего двоичного разряда тетрады соединен с первым входом пятого элемента И, второй вход которого связан с входом управления выполнением операции двоично-десятичного сложения, выход упомянутого элемента И соединен с первыми входами шестого и седьмого элементов И, второй вход шестого элемента И связан с выходом комбинационного сумматора второго двоичного разряда тетрады, а его выход подключен к второму входу первого элемента ИЛИ четвертого двоичного разряда тетрады, второй вход седьмого элемента И соединен с инверсным выходом комбинационного сумматора второго двоичного разряда тетрады, а выход этого элемента подключен к вторым входам первых элементов ИЛИ второго и третьего двоичных разрядов тетрады; введена схема формирования дополнительного переноса в старшую тетраду при значении суммы тетрады, равной 1010, 1011, 1100, 1101, 1110 и 1111, содержащая третий и четвертый элементы ИЛИ и восьмой элемент И, при этом выход комбинационного сумматора третьего двоичного разряда тетрады связан с первым входом третьего элемента ИЛИ, второй его вход соединен с выходом комбинационного сумматора второго двоичного разряда тетрады, а выход подключен к первому входу восьмого элемента И, второй и третий входы которого соединены с выходом комбинационного сумматора четвертого двоичного разряда тетрады и входом управления выполнением операции двоично-десятичного сложения, выход этого элемента И соединен со вторым входом четвертого элемента ИЛИ, первый вход которого соединен с выходом комбинационного сумматора четвертого двоичного разряда тетрады, а выход четвертого элемента ИЛИ является выходом переноса в старшую тетраду; также введена вторая схема коррекции кода суммы тетрады, содержащая девятый и десятый элементы И, при этом выход восьмого элемента И соединен с первыми входами девятого и десятого элементов И, вторые входы этих элементов связаны с выходом комбинационного сумматора второго двоичного разряда тетрады и с инверсным выходом комбинационного сумматора второго двоичного разряда тетрады соответственно, третий вход девятого элемента И подключен к выходу комбинационного сумматора третьего двоичного разряда тетрады, а выходы девятого и десятого элементов И соединены с третьими входами первых элементов ИЛИ третьего и второго двоичных разрядов соответственно; введены одиннадцатый элемент И и пятые элементы ИЛИ и НЕ, при этом первый вход пятого элемента ИЛИ соединен с входом управления выполнением операции двоичного сложения, второй его вход соединен с выходом одиннадцатого элемента И, входы которого соединены с выходом пятого элемента НЕ и с входом управления выполнением двоично-десятичного сложения, выход пятого элемента ИЛИ подключен к вторым входам первых элементов И второго, третьего и четвертого двоичных разрядов, а вход пятого элемента НЕ связан с выходом четвертого элемента ИЛИ.

| КАРЦЕВ М.А | |||

| Арифметика цифровых машин | |||

| - М.: Наука, 1969, раздел 2.3 | |||

| Двоично-десятичный сумматор | 1984 |

|

SU1241233A1 |

| DE 3440333 A1, 22.05.1986 | |||

| Устройство для упрочняющей обработки зубчатых колес | 1982 |

|

SU1031613A1 |

Авторы

Даты

2010-10-27—Публикация

2007-12-14—Подача