объединен с седьмым входом блока поразрядного контроля переносов и подключен к выходу блока формирования параллельных переносов, третий вход которого объединен с третьим входом блока поразрядного контроля переносов и подключен к входу переноса устройства, шестой вход блока поразрядного контроля переносов является инверсным входом переноса устройства.

2, Устройство по П.1, отличающееся тем, что блок поразрядного контроля переносов содержит .элемент ИЛИ-НЕ, группу элементов И, группу элементов ИЛИ, элемент И и элемент ИЛИ, выход которого является выходом блока, первые шесть входов элемента ИЛИ подключены к выходам соответствую1цих элементов И группы, а седьмой вход подключен.к выходу элемента И, первые входы элементов И группы объединены и подключены к выходу элемента ИЛИ-НЕ, вход которого объединен с первым входом элемента И и является седьмым входом блока, 1 -е входы i-х элементов И группы (i 2,3,...,6) образуют первый вход блока ,(j+1)входы J-X элементов И группы образ |от второй вход блока, второй вход второгоэлемента И группы объединен с вторыми входами 1. -х элементов И группы (к 3, , 5, 6), третий вход третьего элемента И группы объединен с третьими входами к-х элементов И группы (к 4, 5, 6), четвертый вход четвертого элемента И группы объединен с четвертыми входами k-х элементбв И группы (к 5,6), пятые входы пятого и шестого элементов И группы объединены между собой, i -е входы J-X элементов ИЛИ группы ({ 1,2,... ,5; j i , i +1 ,... , 6) со ответственно объединены и образуют четвертый вход блока,(i+1)-е входь1 i -X элементов ИЛИ группы ( 1 ,3, и второй вход эле,мента И образуют третий вход блока, выходы элементов ИЛИ группы подключены к соответствующим входам элемента И, седьмой вход шестого элемен та И группы и шестой вход пятого элемента ИЛИ группы являются соответственно пятым и шестым входами блока.

3- Устройство по П.1, о т л и чающееся тем, что блок исправления переносов содержит группу элементов ИЛИ, счетчик, первый и второй элементы ИЛИ, первый и второй элементы И-НЕ, группу элементов И, выходы первых семи из которых образуют первый выход блока, выход восьмого элемента И группы и первого

элемента И-НЕ являются соответственно вторым и третьим выходами блока, первые входы элементов И группы подключены к соответствующим выходам счетчика, первый вход первого элемента И-НЕ подключен к выходу восьмого разряда счетчика, вторые входы элементов И группы и первого элемента И-НЕ объединены и подключены к выходу второго элемента ИЛИ, вхо;ДЫ которого подключены к выходам соответственно первого элемента ИЛИ .и второго элемента И-НЕ, входы которых соответственно попарно объединены и образуют второй вход блока,первые входы элементов ИЛИ группы образуют третий вход блока, вторые входы соответственно объединены с соответствующими входами первого элемента ИЛИ, выходы элементов ИЛИ группы подклю- - установочным входам счетчика, счетный вхоД которого является первым входом блока. 4. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок исправления разрядных сумм содержит группу Элементов ИЛИ, счетчик, первый и второй элементы ИЛИ, группу элементов И, элемент И-НЕ, выход которого подключен к первому входу второго элемента ИЛИ, второй вход - к выходу первого элемента ИЛИ, выходы элементов И группы образуют первый выход блока, первые входы элементов И группы подключены к соответствующим выходам счетчика, вторые входы объединены между собой, соединены с выходом второго элемента ИЛИ и образуют второй выход блока,первые входы элементов ИЛИ группы образуют первый вход блока, а вторые входы объединены с соответствующими входами первого элемента ИЛИ и элемента И-НЕ, выходы э/1ементов ИЛИ группы подключены к соответствующим установочным входам счетчика, счетный вход которого является управляющим входом блока.

Изобретение относится к вычислительной технике и цифровой автоматике и предназначено для контроля ариф. метических устройств, использующих сумматоры, формирующие разрядные переносы параллельным способом.

Известен сумматор с контролем по четности, содержащий в каждом разряде блок формирования параллельного переноса и блок формирования разрядной суммы, используя для формирования переносов и разрядных сумм функции генерации и передачи переноса l J.

Недостатками сумматора являются невозможность обнаружения ошибок, вызываемых неисправностью в блоке формирования параллельных переносов из-за отсутствия контроля этого блока, обнаружение лишь одиночных ошибок в блоках форкжрования разрядных сумм, а также невозможность исправления ошибок сумматора.

Наиболее близким к предлагаемому является устройство для обнаружения и исправления ошибок сумматора, со держащее первый блок сложения по модулю два , элемент ИЛИ, блок формирования дополнительных сумм и группу схем сравнения, входы первого блока сложе ;ния по модулю два соединены с выходами суммы контролируемого суммаiTopa, информационные входы блока формирования дополнительных сумм соедине ны с входами операндов сумматора, вход переноса с предыдущих разрядов сумматора является управляющим входом устройства, - выход первого блока сложения по модулю два является первым выходом устройства, выход элемента ИЛИ является вторым выходом устройства, выходы каждой схемы сравнения группы соединены с соответству;ющим входом элемента ИЛИ,а также второй блок сложения по модулю два, выход которого соединен с (п + 1)-м входом первого блока сложения по модулю два, каждый нечетный выход блока формирования дополнительной суммы соединен с первым входом соответствующей схемы сравнения, второй вход каждой схемы сравнения соединен с соответствующим нечетным входом суммы контролируемого сумматора, выход блока формирования дополнительных сумм соединен с соответствующим входом второго блока сложения по модулю два 12 .

Основными недостатками известного устройства являются большой объем

контролирующе11 аппаратуры вследствие необходимости дублирования разрядных сумм, а также из-за наличия N-разрядного и ( N+1J-разрядного блоков сложения по модулю два, на построение которых при достаточно большой разрядности и высоком быстродействии уходит значительная часть оборудования-устройства; низкая эффективность контроля сумматора вследствие невозможности исправле ния ошибок сумматора из-за отсутствия необходимой для этой цели аппаратуры, введение которой в устройство приведет к еще большим аппаратурным затратам.

Цель изобретения - уменьшение объема оборудования при одновременном повышений эффективности контроля..

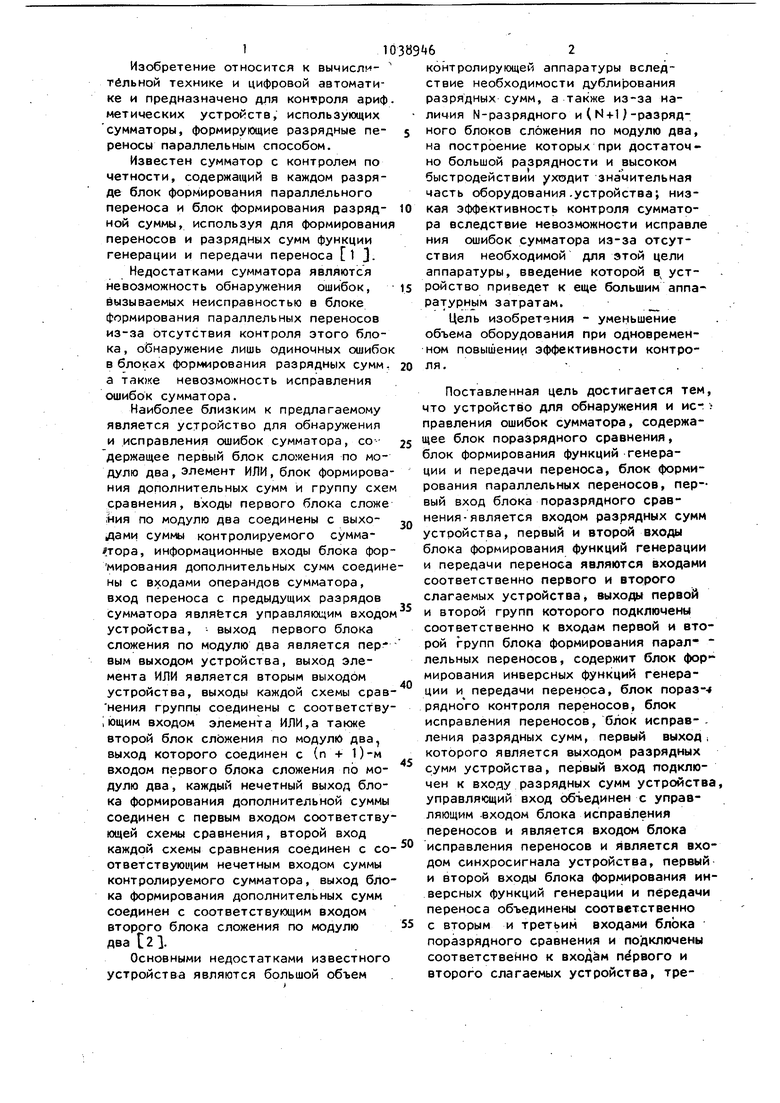

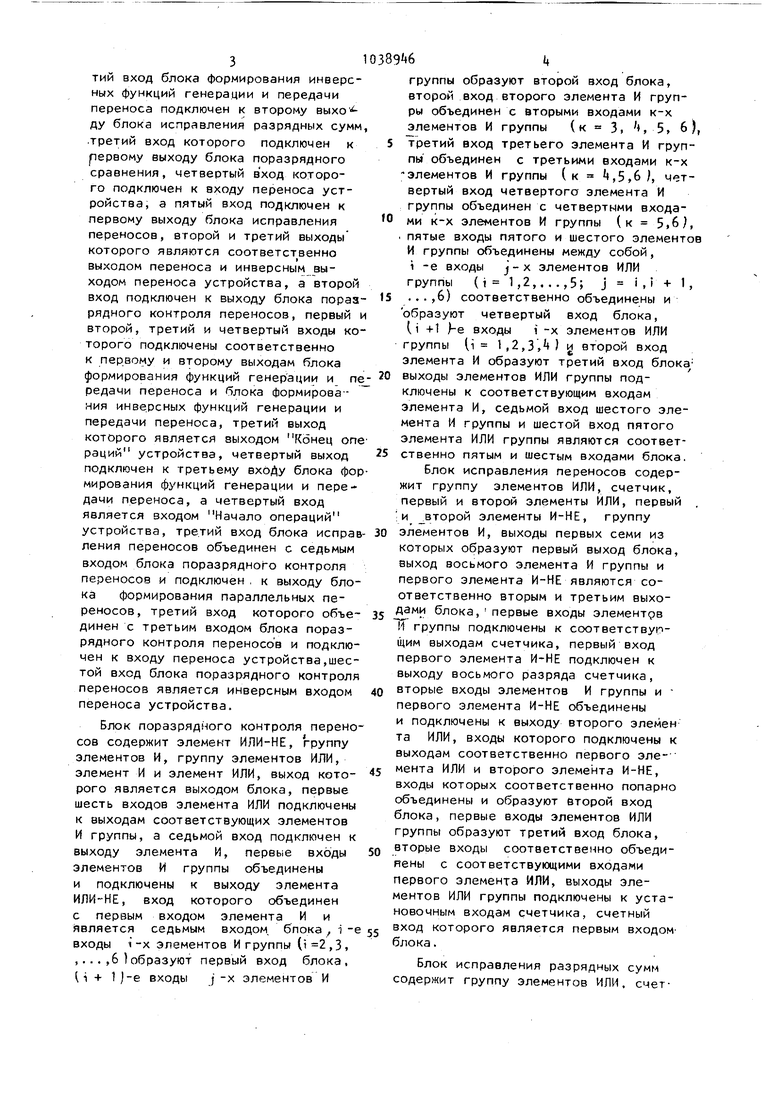

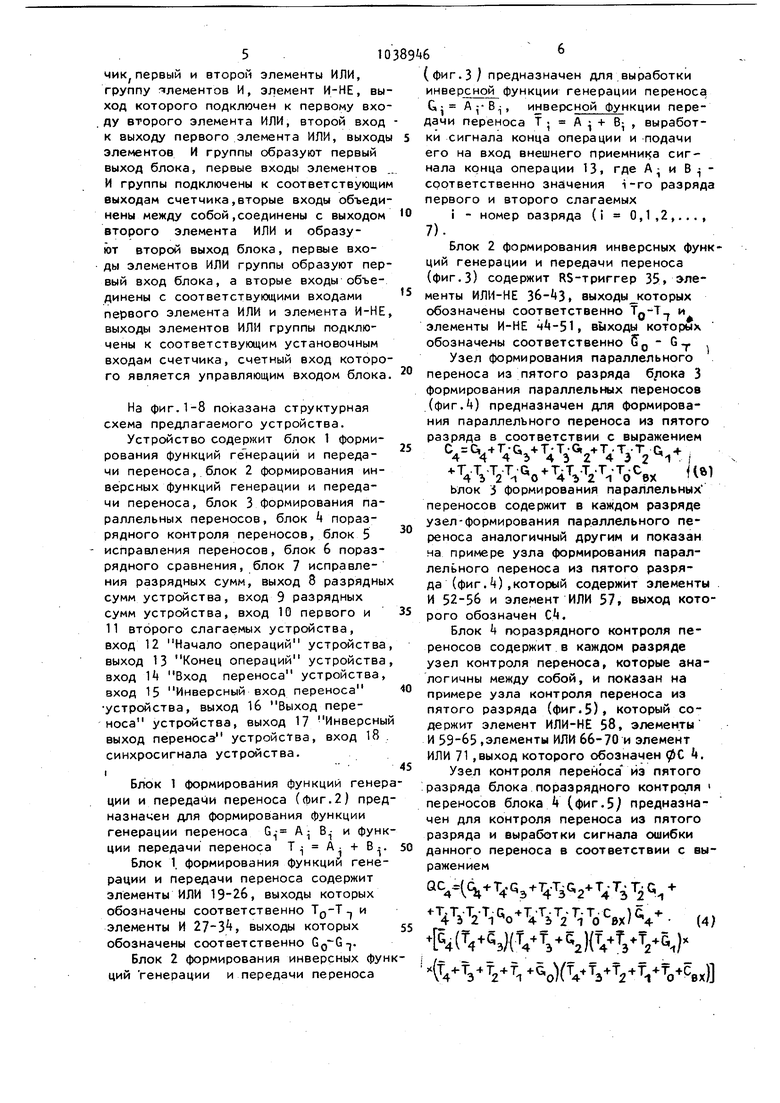

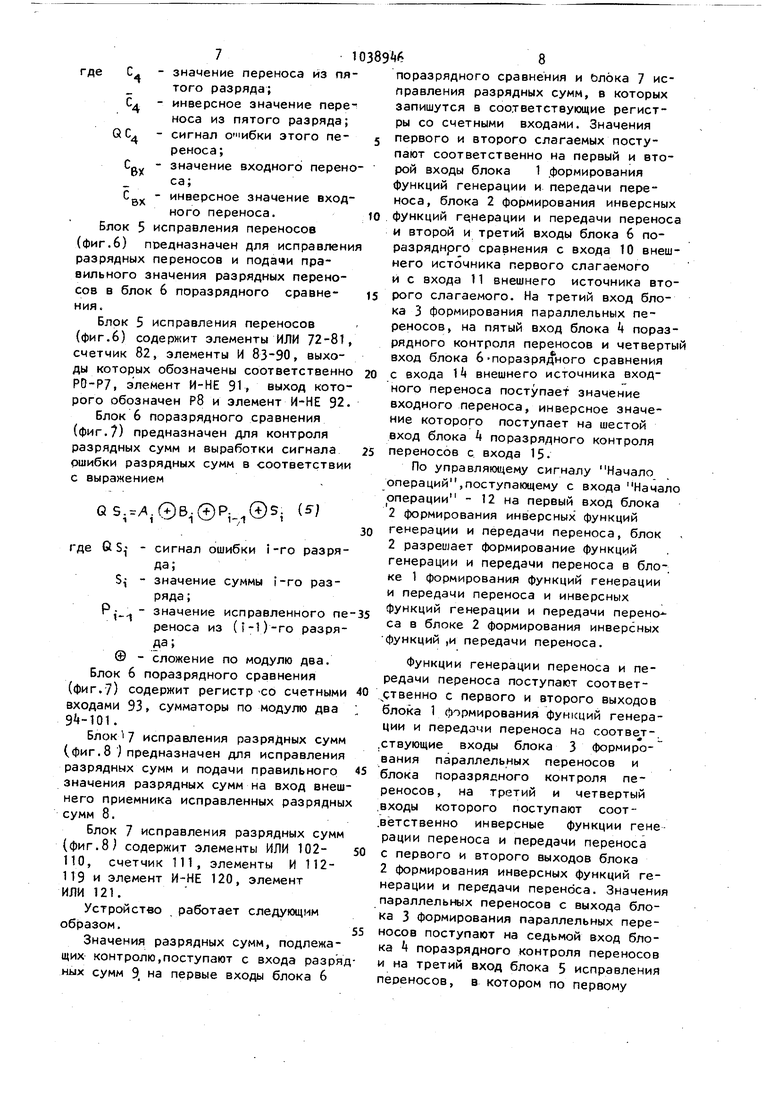

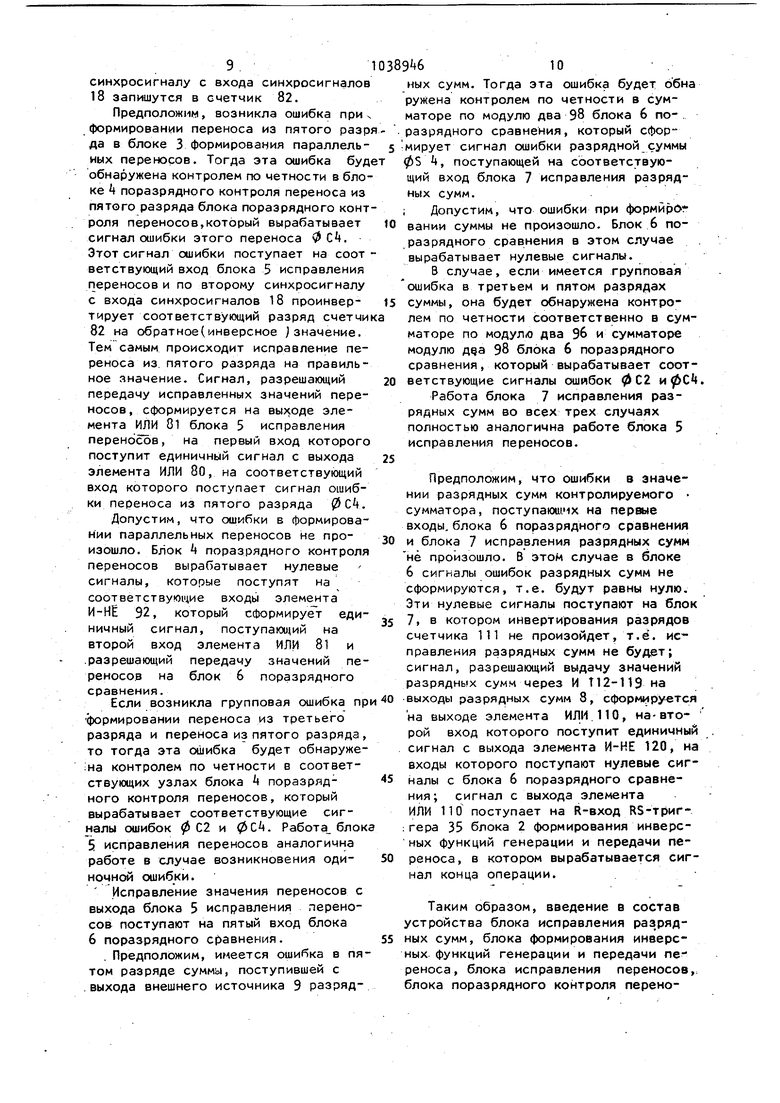

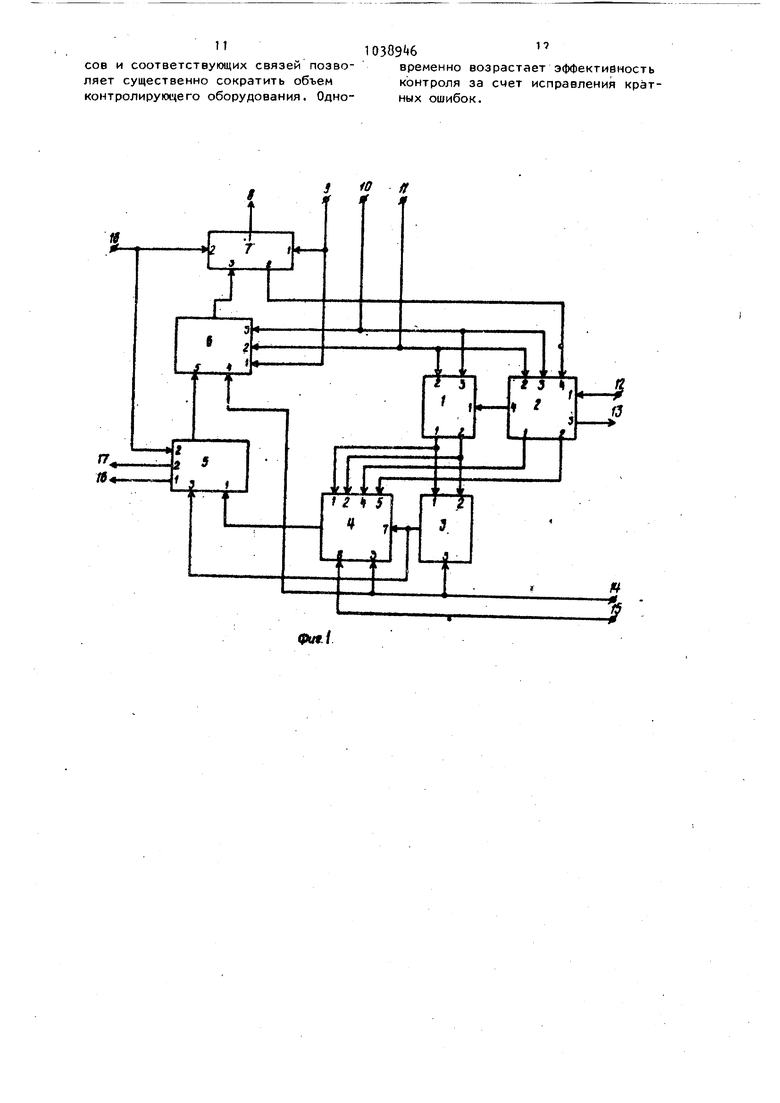

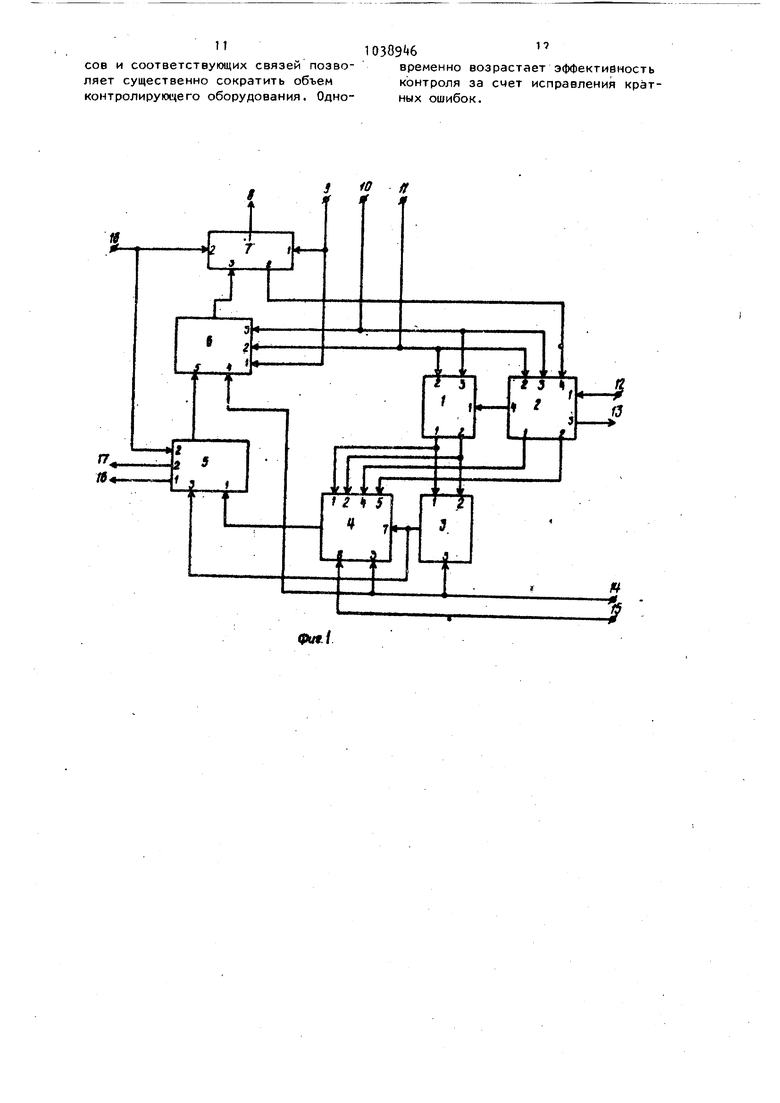

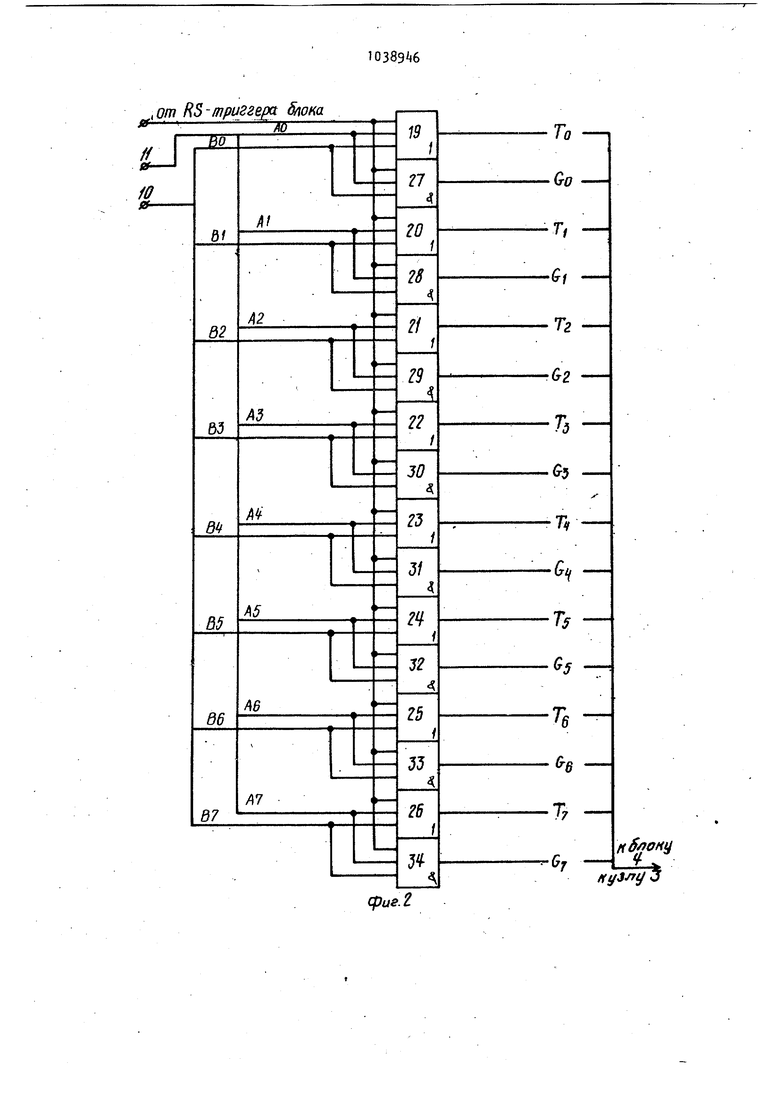

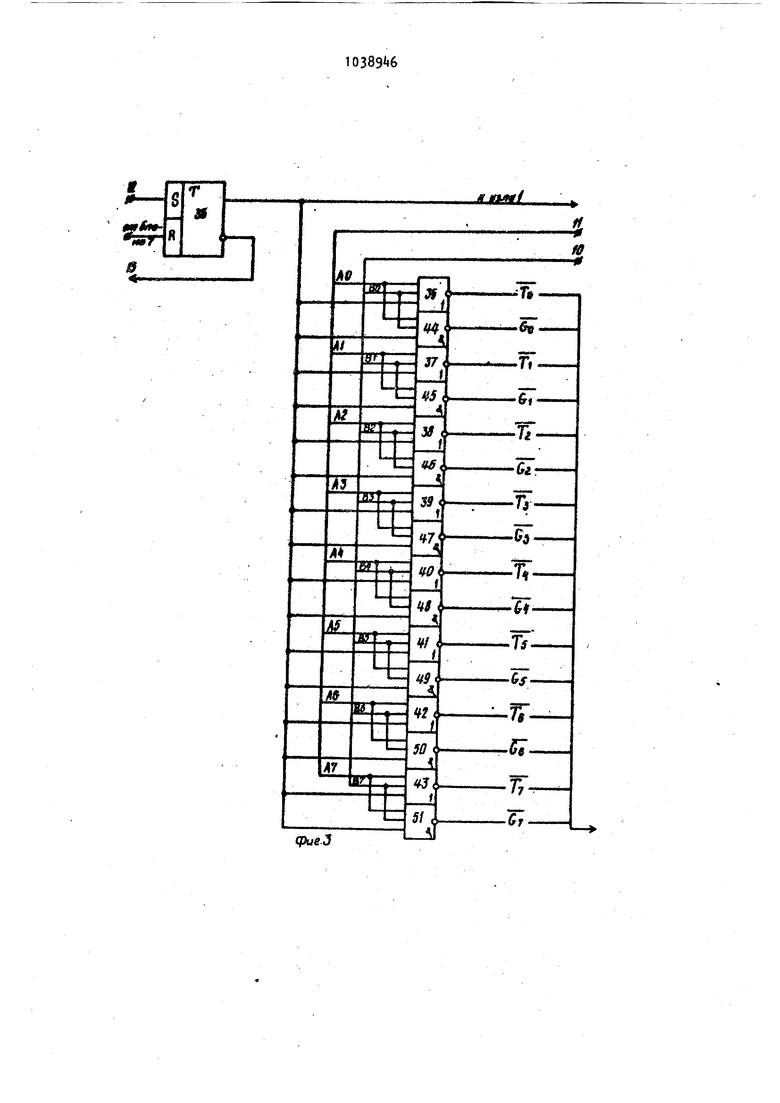

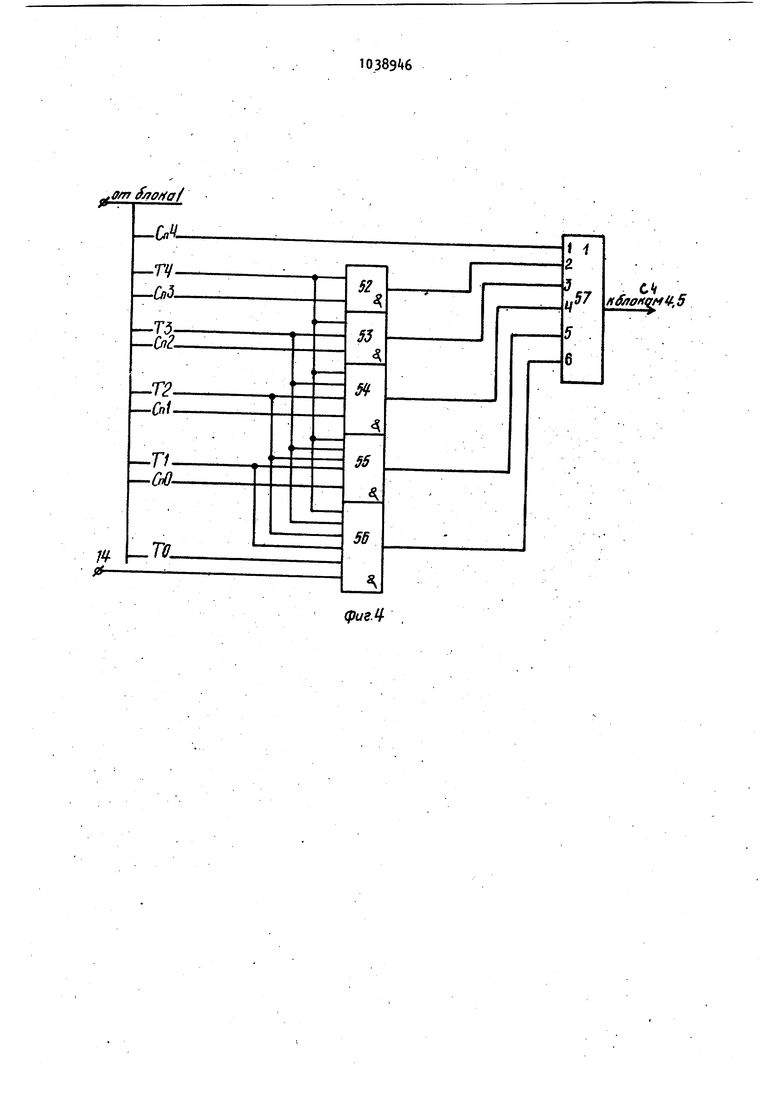

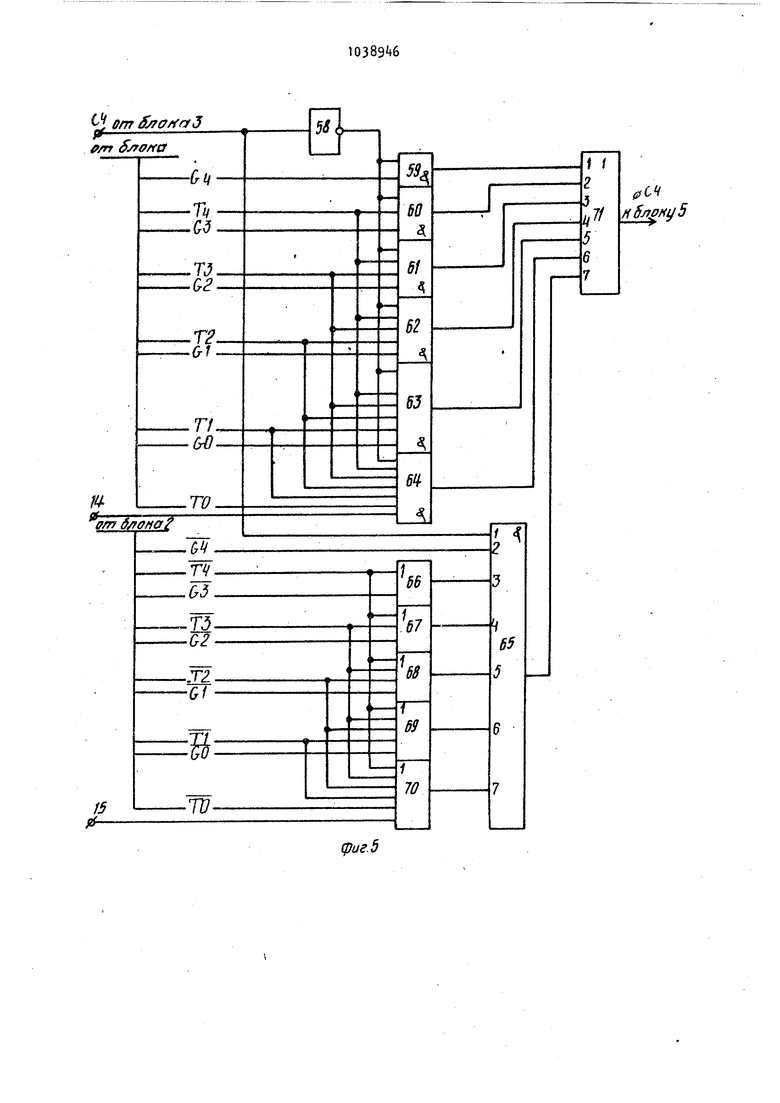

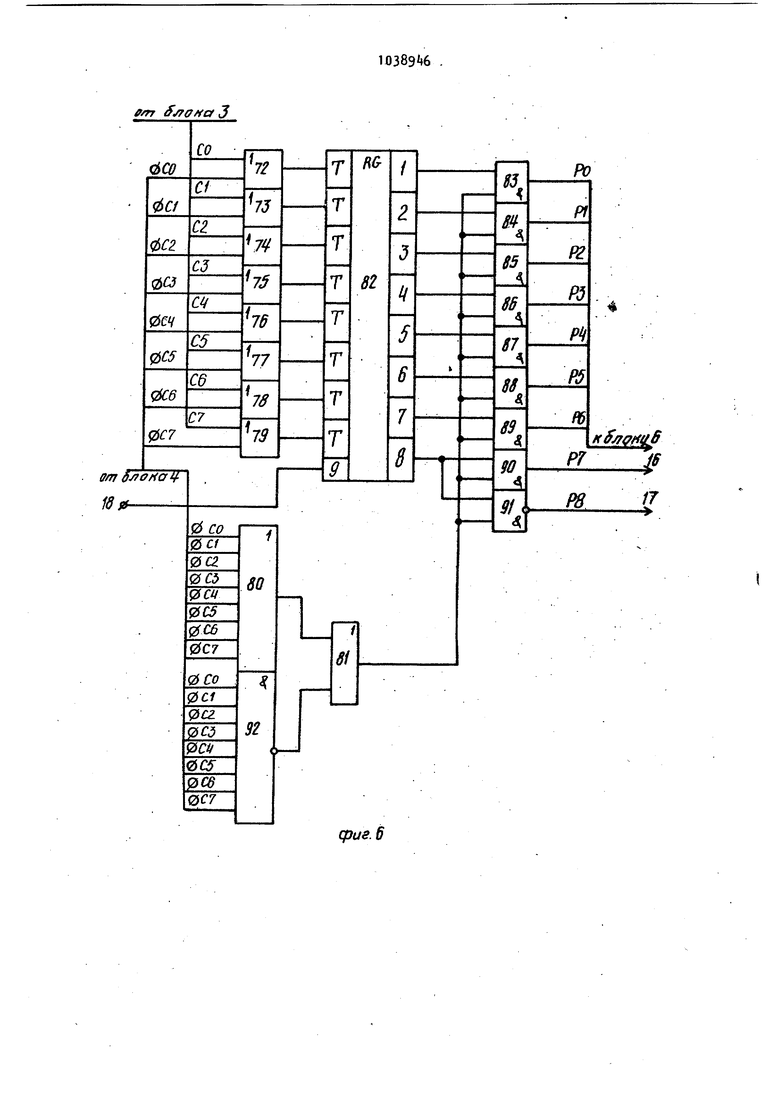

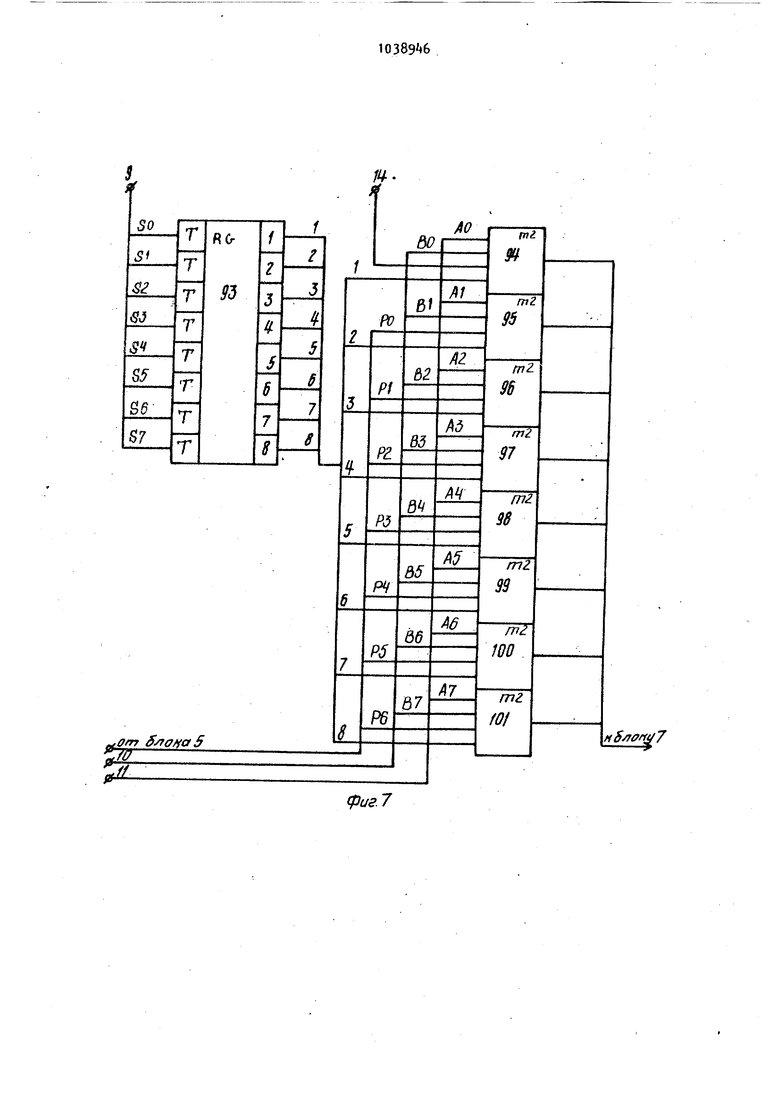

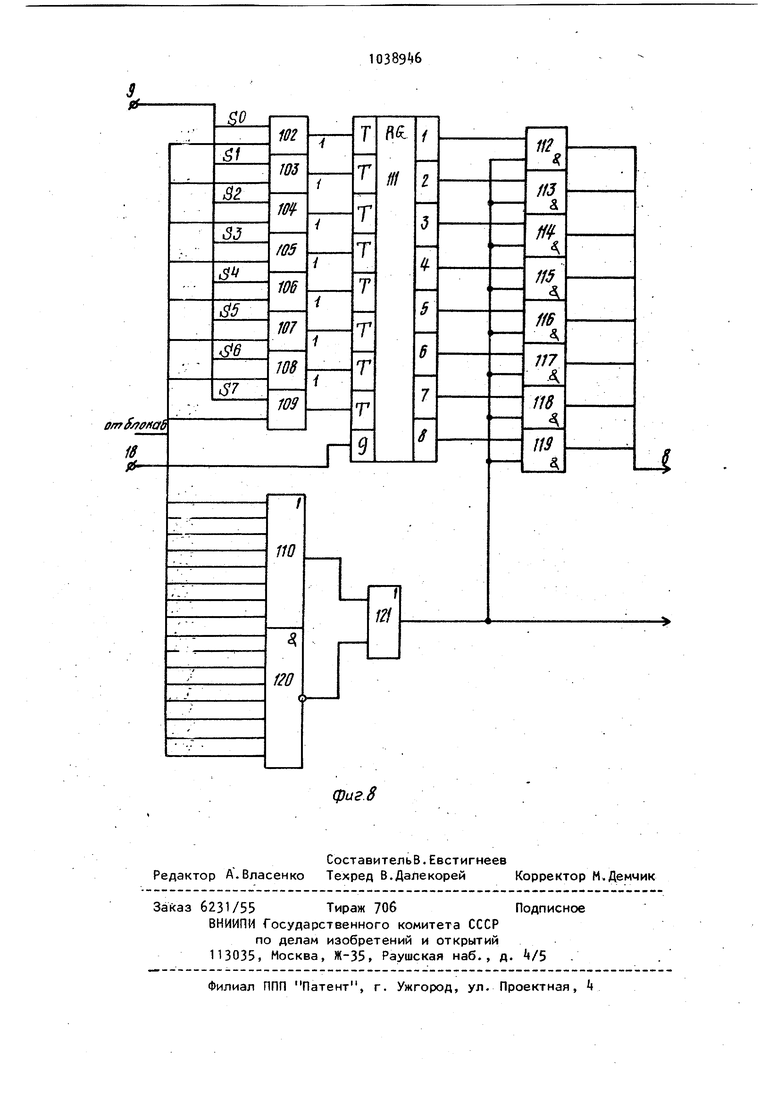

Поставленная цель достигается тем, что устройство для обнаружения и исг правления ошибок сумматора, содержащее блок поразрядного сравнения, блок формирования функций генерации и передачи переноса, блок формирования параллельных переносов, первый вход блока поразрядного сравнения -является входом разрядных сумм устройства, первый и второй входы блока формирования функций генерации и передачи переноса являются входами соответственно первого и второго слагаемых устройства, выходы первой и второй групп которого подключены соответственно к входам первой и второй групп блока формирования парал лельных переносов, содержит блок формирования инверсных функций генерации и передачи переноса, блок пораз-- рядного контроля переносов, блок исправления переносов, блок исправ-. ления разрядных сумм, первый выход которого является выходом разрядных сумм устройства, первый вход подключен к входу разрядных сумм устройства, управляющий вход объединен с управляющим -входом блока исправления переносов и является входом блока исправления переносов и является входом синхросигнала устройства, первый и второй входы блока формирования инверсных функций генерации и передачи переноса объединены соответственно с вторым и третьим входами блока поразрядного сравнения и подключены соответственно к входам первого и второго слагаемых устройства, третий вход блока формирования инверсных функций генерации и передачи переноса подключен к второму выхо ду блока исправления разрядных сумм .третий вход которого подключен к рервому выходу блока поразрядного сравнения, четвертый вход которого подключен к входу переноса устройства, а пятый вход подключен к первому выходу блока исправления переносов, второй и третий выходы которого являются соответственно выходом переноса и инверсным выходом переноса устройства, а второй вход подключен к выходу блока пораз рядного контроля переносов, первый второй, третий и четвертый входы ко торого подключены соответственно к первому и второму выходам блока формирования функций генерации и пе редачи переноса и блока формироаания инве.рсных функций генерации и передачи переноса, третий выход которого является выходом Конец опв раций устройства, четвертый выход подключен к третьему вхоДу блока фо мирования функций генерации и передачи переноса, а четвертый вход является входом Начало операций устройства, третий вход блока исправ ления переносов объединен с седьмым входом блока поразрядного контроля переносов и подключен , к выходу блока формирования параллельных переносов, третий вход которого объедииен с третьим входом блока поразрядного контроля переносов и подключен к входу переноса устройства,шестой вход блока поразрядного контроля переносов является инверсным входом переноса устройства, Блок поразрядного контроля переио сов содержит элемент ИЛИ-НЕ, группу элементов И, группу элементов ИЛИ, ,t ,.пи элемент И и элемент ИЛИ, выход которого является выходом блока, первые шесть входов элемента ИЛИ подключены к выходам соответствующих элементов И группы, а седьмой вход подключен к выходу элемента И, первые входы элементов И группы объединены и подключены к выходу элемента ИЛИ-НЕ, вход которого объединен с первым входом элемента И и является седьмым входом, блока , i входы i-x элементов И группы (,3, ,... ,6 )образуют первый вход блока, i + 1)-е входы ) -X элементов И 461+ группы образуют второй вход блока, второй вход второго элемента И групры объединен с вторыми входами к-х элементов И группы (к 3, , 5, 6), Третий вход третьего элемента И группы объединен с третьими входами к-х элементов И группы (к ,5,6 ), четвертый вход четвертого элемента И группы объединен с четвертыми входами к-х элементов И группы (к 5,6, . пятые входы пятого и шестого элементов И группы объединены между собой, i -е входы J-X элементов ИЛИ группы (i 1,2,...,5; j i,i + 1, ...,6) соответственно объединены и образуют четвертый вход блока, (i +1 -е входы i -х элементов ИЛИ группы (i 1,2,3, ) второй вход элемента И образуют третий вход блока выходы элементов ИЛИ группы подключены к соответствующим входам элемента И, седьмой вход шестого элемента И группы и шестой вход пятого элемента ИЛИ группы являются соответственно пятым и шестым входами блока, Блок исправления переносов содержит группу элементов ИЛИ, счетчик, первый и второй элементы ИЛИ, первый ;и второй элементы И-НЕ, группу элементов И, выходы первых семи из которых образуют первый выход блока, выход восьмого элемента И группы и первого элемента И-НЕ являются соответственно вторым и третьим выхо5 блока, первые входы элементдв группы подключены к соответствующим выходам счетчика, первый вход первого элемента И-НЕ подключен к выходу восьмого разряда счетчика, вторые входы элементов И группы и первого элемента И-НЕ объединены °2пС ° И, входы которого подключены к выходам соответственно первого элемента ИЛИ и второго элемента И-НЕ, входы которых соответственно попарно объединены и образуют второй вход блока, первые входы элементов ИЛИ группы образуют третий вход блока, вторые входы соответственно объединены с соответствующими входами первого элемента ИЛИ, выходы элементов ИЛИ группы подключены к установочным входам счетчика, счетный которого является первым входомблока. Блок исправления разрядных сумм содержит группу элементов ИЛИ, счетчик первый и второй элементы ИЛИ, группу -члементов И, элемент И-НЕ, выход которого подключен к первому вхо. ду второго элемента ИЛИ, второй вход к выходу первого элемента ИЛИ, выходы элементов И группы образуют первый выход блока, первые входы элементов И группы подключены к соответствующим выходам счетчика,вторые входы объединены между собой,соединены с выходом второго элемента ИЛИ и образуют второй выход блока, первые входы элементов ИЛИ группы образуют первый вход блока, а вторые входы объединены с соответствующими входами первого элемента ИЛИ и элемента И-НЕ выходы элементов ИЛИ группы подключены к соответствующим установочным входам счетчика, счетный вход которого является управляющим входом блока На фиг.1-8 показана структурная схема предлагаемого устройства. Устройство содержит блок 1 формирования функций генераций и передачи переноса, блок 2 формирования инверсных функций генерации и передачи переноса, блок 3 Формирования параллельных переносов, блок поразрядного контроля переносов, блок 5 - исправления переносов, блок 6 поразрядного сравнения, блок 7 исправления разрядных сумм, выход 8 разрядных сумм устройства, вход 9 разрядных сумм устройства, вход 10 первого и 11 второго слагаемых устройства, вход 12 Начало операций устройства ВЫХОД 13 Конец операций устройства вход 1 Вход переноса устройства, вход 15 Инверсный вход переноса устройства, выход 16 Выход переноса устройства, выход 17 Инверсный выход переноса устройства, вход 18 синхросигнала устройства. Блок 1 формирования функций генер ции и передачи переноса (фиг.2) пред назна1;ен для формирования функции генерации переноса А ,, и функ Т, А. + В. ции передачи переноса Блок 1. формирования функции генерации и передачи переноса содержит элементы ИЛИ 19-26, выходы которых обозначены соответственно TQ-T-J и элементы И 27-3, выходы которых обозначены соответственно . Блок 2 формирования инверсных фун ций генерации и передачи переноса 10 6 (фиг.З) предназначен для выработки инверсной функции генерации переноса 0- , инверсной функции передачи переноса Т - А : + В , , выработки сигнала конца операции и подачи его на вход внешнего приемника сигнала конца операции 13, где А- и В соответственно значения i-ro разряда первого и второго слагаемых i - номер оазряда (1 0,1,2,..., 7). Блок 2 формирования инверсных функций генерации и передачи переноса (фиг.З) содержит RS-триггер 35,лементы ИЛИ-НЕ Зб-43 выходы которых обозначены соответственно Тд-Т и элементы И-НЕ чА-51, выходы которых обозначены соответственно Я - GУзел формирования параллельного переноса из пятого разряда б/юка 3 формирования параллельных переносов (фиг.4) предназначен для формирования параллельного переноса из пятого разряда в соответствии с выражением ., Ьлок 3 формирования параллельных переносов содержит в каждом разряде узел-формирования параллельного переноса аналогичный другим и показан на примере узла формирования параллельного переноса из пятого разряда (фиг. ) , который содержит элементы И 52-56 и элемент ИЛИ 57, выход которого обозначен СА. Блок k поразрядного контроля переносов содержит в каждом разряде узел контроля переноса, которые аналогичны между собой, и показан на примере узла контроля переноса из пятого разряда (фиг.5), Который содержит элемент ИЛИ-НЕ 58, элементы И 59-65.элементы ИЛИ 66-70 и элемент ИЛИ 71 .выход которого обозначен 0С 4. Узел контроля переноса из пятого разряда блока поразрядного контроля переносов блока V (фиг.5 предназначен для контроля переноса из пятого разряда и выработки сигнала ошибки данного переноса в соответствии с выражениемQVlS- - 4-S-T4-T3 2- T4- 3 2. V3VTi o- - 3; ;i oSx)(4-S)(.) , S)() +t,+T.+t,+C где С - значение переноса из пя того разряда; Сд - инверсное значение пере носа из пятого разряда; Q С. - сигнал онибки этого переноса;Со - значение входного перено Сг, - инверсное значение вход од ного переноса. Блок 5 исправления переносов (фиг.6) предназначен для исправлени разрядных переносов и подачи правильного значения разрядных переносов в блок 6 поразрядного сравнения. Блок 5 исправления переносов {фиг.6) содержит элементы ИЛИ 72-81 сметчик 82, элементы И 83-90, выходы которых обозначены соответственно РО-Р/, элемент И-НЕ 91, выход кото рого обозначен Р8 и элемент И-НЕ 92 Блок 6 поразрядного сравнения (фиг.7) предназначен для контроля разрядных сумм и выработки сигнала ошибки разрядных сумм в соответствии с выражением Qs./.©B.0P,©s (Я где GS, Si сигнал ошибки i-ro разря да; значение суммы i-ro разряда ; значение исправленного пе реноса из (t-l)-ro разряда;сложение по модулю два. Блок 6 поразрядного сравнения (фиг.7) содержит регистр -со счетными входами 93, сумматоры по модулю два . Блок 1 7 исправления разрядных сумм (фиг.8 )предназначен для исправления разрядных сумм и подачи правильного значения разрядных сумм на вход внеш него приемника исправленных разрядны сумм 8. Блок 7 исправления разрядных сумм (фиг.З содержит элементы ИЛИ 102110, счетчик 111, элементы И 112119 и элемент И-НЕ 120, элемент ИЛИ 121. Устройство работает следующим образом. Значения разрядных сумм, подлежащих контролю,поступают с входа разря ных сумм 9. на первые входы блока 6 поразрядного сравнения и блока 7 исправления разрядных сумм, в которых запишутся в соответствующие регистры со счетными входами. Значения первого и второго слагаемых поступают соответственно на первый и второй входы блока 1 формирования функций генерации и передачи переноса, блока 2 формирования инверсных функций генерации и передачи переноса и второй и третий входы блока 6 поразряднрго сравнения с входа 10 внешнего источника первого слагаемого и с входа 11 внешнего источника второго слагаемого. На третий вход блока 3 формирования параллельных переносов, на пятый вход блока 4 поразрядного контроля переносов и четвертый вход блока 6-поразрядного сравнения с входа 1 внешнего источника входного переноса поступает значение входного переноса, инверсное значение которого поступает на шестой вход блока 4 поразрядного контроля переносов с входа 15 По управляющему сигналу Начало операций,поступающему с входа Начало операции - 12 на первый вход блока 2 формирования инверсных функций генерации и передачи переноса, блок 2 разрешает формирование функций генерации и передачи переноса в бло-. ке 1 формирования функций генерации и передачи переноса и инверсных функций генерации и передачи переноса в блоке 2 формирования инверсных функций ,и передачи переноса. Функции генерации переноса и передачи переноса поступают соответственно с первого и второго выходов блока 1 формирования функций генерации и передачи переноса на соответ-. ствующие входы блока 3 формирования параллельных переносов и блока поразрядного контроля переносов, на третий и четвертый входы которого поступают соотвётственно инверсные функции генерации переноса и передачи переноса с первого и второго выходов блока 2 формирования инверсных функций генерации и передачи переноса. Значения параллельных переносов с выхода блока 3 формирования параллельных переносов поступают на седьмой вход блока k поразрядного контроля переносов и на третий вход блока 5 исправления переносов, в котором по первому синхросигналу с входа синхросигналов 18 запишутся в счетчик 82. Предположим, возникла ошибка при формировании переноса из пятого разр да в блоке 3 формирования параллельиых переносов. Тогда эта ошибка буд обнаружена контролем по четности в бло ке поразрядного контроля переноса из пятого разряда блока поразрядного конт роля переносов,который вырабатывает сигнал ошибки этого переноса 00. Этот сигнал ошибки поступает на соот ветствующий вход блока 5 исправления переносов и по второму синхросигналу с входа синхросигналов 18 проинвертирует соответствующий разряд счетчи 82 на обратное(инверсное jзначение. Тем самым происходит исправление переноса из. пятого разряда на правильное значение. Сигнал, разрешающий передачу исправленных значений переносов, сформируется на выходе элемента ИЛИ 81 блока 5 исправления переносов, на первый вход которого поступит единичный сигнал с выхода элемента ИЛИ 80, на соответствующий вход которого поступает сигнал ошибки переноса из пятого разряда . Допустим, что ошибки в формировании параллельных переносов не произошло. Блок А поразрядного контроля переносов вырабатывает нулевые сигналы, которые поступят на соответствующие входь элемента И-НЁ 92, который сформирует единичный сигнал, поступаюи ий на второй вход элемента ИЛИ 81 и .разрешающий передачу значений переносов на блок 6 поразрядного сравнения. Если возникла групповая ошибка пр формировании переноса из третьего разряда и переноса из пятого разряда, то тогда эта ошибка будет обнаруже:на контролем по четности в соответствующих узлах блока 4 поразрядного контроля переносов, который вырабатывает соответствующие сигналы ошибок 0 С2 и 0С4. Работа. блок 5исправления переносов аналогична работе в случае возникновения одиночной ошибки. Исправление значения переносов с выхода блока 5 исправления переносов поступают на пятый вход блока 6поразрядного сравнения. Предположим, имеется ошибка в пятом разряде суммы, поступившей с .выхода внешнего источника 9 разрядных сумм. Тогда эта ошибка будет обна ружена контролем по четности в сумматоре по модулю два 98 блока 6 поразрядного сравнения, который сфор мирует сигнал ошибки разрядной суммы 0S, поступающей на соответствующий вход блока 7 исправления разрядных сумм. ; Допустим, что ошибки при формйрО вании суммы не произошло. Блок 6 поразрядного сравнения в этом случае вырабатывает нулевые сигналы. 8 случае, если имеется групповая ошибка в третьем и пятом разрядах суммы, она будет обнаружена контролем по четности соответственно в сумматоре по модулю два 9б и сумматоре модулю д§а 98 блока 6 поразрядного сравнения, который вырабатывает соответствующие сигналы ошибок 0С2 . Работа блока 7 исправления разрядных сумм во всех трех случаях полностью аналогична работе блока 5 исправления переносов. Предположим, что ошибки в значении разрядных сумм контролируемого сумматора, поступающих на первые входы, блока 6 поразрядного сравнения и блока 7 исправления разрядных сумм не произошло. В этом случае в блоке 6 сигналы ошибок разрядных сумм не сформируются, т.е. будут равны нулю. Эти нулевые сигналы поступают на блок 7, в котором инвертирования разрядов счетчика 111 не произойдет, т.е. исправления разрядных сумм не будет; сигнал, разрешающий выдачу значений разрядных сумм через И Т12-119 на выходы разрядных сумм 8, сформируется на выходе элемента ИЛИ 110, на-второй вход которого поступит единичный сигнал с выхода элемента И-НЕ 120, на входы которого поступают нулевые си1 налы с блока 6 поразрядного сравнения; сигнал с выхода элемента ИЛИ 110 поступает на R-вход RS-триггера 35 блока 2 формирования инверсных функций генерации и передачи переноса, в котором вырабатывается си1 нал конца операции. . Таким образом, введение в состав устройства блока исправления разрядных сумм, блока формирования инверсных функций генерации и передачи переноса, блока исправления переносов,: блока поразрядного койтроля переносов и соответствующих связей позволяет существенно сократить объем контролирующего оборудования. Одно10389 6временно возрастает эффективность контроля за счет исправления кратных ошибок.

То -1 Go -

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор с контролем по четности | 1982 |

|

SU1121674A1 |

| Параллельный сумматор с контролем по четности | 1984 |

|

SU1187168A1 |

| Параллельный сумматор с контролем по четности | 1983 |

|

SU1124283A1 |

| Многоразрядное устройство для сложения с контролем по четности | 1981 |

|

SU1035598A1 |

| Сумматор с функциональной зависимостью сумм от переносов и с контролем по четности | 1977 |

|

SU767763A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство вычисления функции @ @ с исправлением ошибок | 1984 |

|

SU1288690A1 |

| Устройство для деления | 1982 |

|

SU1086427A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для контроля цифровых данных | 1985 |

|

SU1381718A1 |

Т

&1

Тг &г - П -

5

П G

7 - 0s

П &б - Т

Н 6лО Hit

7

fft/3-frt/ 5

cpus.Z

,ffm ло/fa/

фиеЛ

С t(SftoKqMif;5

Вт а(уЗ

ff/n

-tV

-TV -CJ

.TJ, .

.r.

.6-r.r/. 6.

П

,7P.

gw (a7

fiH.j.

.7;). ..

St/:5

Ъ

TV/5

}iSf / 2

6V

nSjwf yS

5 б

7

62

63

pi

3

f/

5 7

ff/n . 3

срие.6

фиг.7

Авторы

Даты

1983-08-30—Публикация

1982-02-17—Подача